JP4499089B2 - デジタル加入者線アクセス・マルチプレクサのスタッキングの方法および装置 - Google Patents

デジタル加入者線アクセス・マルチプレクサのスタッキングの方法および装置 Download PDFInfo

- Publication number

- JP4499089B2 JP4499089B2 JP2006500811A JP2006500811A JP4499089B2 JP 4499089 B2 JP4499089 B2 JP 4499089B2 JP 2006500811 A JP2006500811 A JP 2006500811A JP 2006500811 A JP2006500811 A JP 2006500811A JP 4499089 B2 JP4499089 B2 JP 4499089B2

- Authority

- JP

- Japan

- Prior art keywords

- dslam

- slave

- master

- dslams

- communication

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 10

- 238000004891 communication Methods 0.000 claims abstract description 79

- 241001522296 Erithacus rubecula Species 0.000 claims abstract description 21

- 230000009977 dual effect Effects 0.000 claims description 11

- 230000008672 reprogramming Effects 0.000 claims description 4

- 238000013507 mapping Methods 0.000 claims description 3

- 101150012579 ADSL gene Proteins 0.000 description 8

- 102100020775 Adenylosuccinate lyase Human genes 0.000 description 8

- 108700040193 Adenylosuccinate lyases Proteins 0.000 description 8

- 238000010586 diagram Methods 0.000 description 7

- 238000013459 approach Methods 0.000 description 3

- 230000002457 bidirectional effect Effects 0.000 description 3

- 238000001514 detection method Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 235000013550 pizza Nutrition 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/64—Hybrid switching systems

- H04L12/6418—Hybrid transport

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L2012/5603—Access techniques

- H04L2012/5604—Medium of transmission, e.g. fibre, cable, radio

- H04L2012/5606—Metallic

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L2012/5603—Access techniques

- H04L2012/5609—Topology

- H04L2012/561—Star, e.g. cross-connect, concentrator, subscriber group equipment, remote electronics

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L2012/5625—Operations, administration and maintenance [OAM]

- H04L2012/5627—Fault tolerance and recovery

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L2012/5638—Services, e.g. multimedia, GOS, QOS

- H04L2012/5665—Interaction of ATM with other protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/64—Hybrid switching systems

- H04L12/6418—Hybrid transport

- H04L2012/6424—Access arrangements

- H04L2012/6427—Subscriber Access Module; Concentrator; Group equipment

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/64—Hybrid switching systems

- H04L12/6418—Hybrid transport

- H04L2012/6478—Digital subscriber line, e.g. DSL, ADSL, HDSL, XDSL, VDSL

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04M—TELEPHONIC COMMUNICATION

- H04M11/00—Telephonic communication systems specially adapted for combination with other electrical systems

- H04M11/06—Simultaneous speech and data transmission, e.g. telegraphic transmission over the same conductors

- H04M11/062—Simultaneous speech and data transmission, e.g. telegraphic transmission over the same conductors using different frequency bands for speech and other data

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13039—Asymmetrical two-way transmission, e.g. ADSL, HDSL

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/1305—Software aspects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13109—Initializing, personal profile

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13145—Rerouting upon failure

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13164—Traffic (registration, measurement,...)

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13166—Fault prevention

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13167—Redundant apparatus

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13204—Protocols

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/1329—Asynchronous transfer mode, ATM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2213/00—Indexing scheme relating to selecting arrangements in general and for multiplex systems

- H04Q2213/13298—Local loop systems, access network

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Time-Division Multiplex Systems (AREA)

Description

Claims (15)

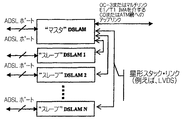

- デジタル加入者線アクセス・マルチプレクサ(DSLAM)をスタックするためのアーキテクチャにおいて、

1つのマスタDSLAMであって、1つの制御回路と、前記マスタDSLAMと隣接して回路が相互接続される2つのDSLAMと通信するための2つの低電圧差分信号(LVDS)回路とを有する、前記マスタDSLAMと、

1つのプログラマブルの制御回路と、隣接して仮想的に回路が相互接続される2つのDSLAMと通信するための2つのLVDS回路とを、それぞれが有する複数のスレーブDSLAMと、

各スレーブDSLAMの前記制御回路を選択的にプログラミングして、第1の選択されたモードにおいてラウンド・ロビンとして、そして第2の選択されたモードにおいてスプリット・パスとして、前記各スレーブDSLAMの前記LVDS回路における通信の方向を制御するためのプログラミング手段と

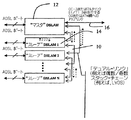

を備えるDSLAMをスタックするためのアーキテクチャ。 - 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記マスタDSLAMに隣接して回路が接続されている前記2つのDSLAMは、リング構造を形成する最初のスレーブDSLAMと最後のスレーブDSLAMとである、DSLAMをスタックするためのアーキテクチャ。

- 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記マスタDSLAMに隣接して回路が接続されている前記2つのDSLAMは、前記第2の選択されたモードにおける前記スプリット・パスに関しては、デュアル・リンク構造を形成する最初のスレーブDSLAMと中間のスレーブDSLAMとである、DSLAMをスタックするためのアーキテクチャ。

- 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記スレーブDSLAMを選択的にプログラミングする前記プログラミング手段は、仮想ボックスIDおよび仮想パス/回路IDに基づいての、データおよび管理メッセージに関するプロキシ・スキームを使用する、DSLAMをスタックするためのアーキテクチャ。

- 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記スレーブDSLAMを選択的にプログラミングする前記プログラミング手段は、仮想ボックスIDおよび仮想パス/回路IDに基づく、データおよび管理メッセージのためのトラフィック中継およびスタッキングI/Oテーブルを使用するものであり、前記テーブルは、仮想チャネルとボックスIDのマッピングを行うためのものである、DSLAMをスタックするためのアーキテクチャ。

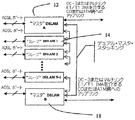

- 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記スレーブDSLAMのうちの1つスレーブDSLAMの故障を検出するための手段を更に含み、選択的にプログラミングする前記プログラミング手段は、前記故障を検出するための手段に応答して、前記1つのマスタDSLAMを通じてのみの通信を維持しつつ、ラウンド・ロビンの通信から、故障が生じた前記スレーブDSLAMを回避するスプリット・パスの通信へと再プログラミングすることを可能にする、DSLAMをスタックするためのアーキテクチャ。

- 請求項6に記載のDSLAMをスタックするためのアーキテクチャであって、予備のマスタDSLAMを更に備え、前記1つのマスタDSLAMが故障したときに、前記予備のマスタDSLAMは、制御回路と、中央局へのアップリンク通信回路と、マスタDSLAMと隣接して回路が相互接続される2つのDSLAMと通信するための2つの低電圧差分信号(LVDS)回路とを有する1つのマスタDSLAMとして動作することが可能にされるものであり、選択的にプログラミングする前記プログラミング手段は、新たな1つのマスタDSLAMとしての前記予備のマスタDSLAMを通じての通信を維持しつつ、ラウンド・ロビンの通信から、故障が生じた前記1つのマスタDSLAMを回避するスプリット・パスの通信へと再プログラミングするものであり、前記スプリットは、前記予備のマスタDSLAMを通じての通信のために、前記予備のマスタDSLAMと隣接した所望される仮想的回路相互接続において選択的にプログラムされるものである、DSLAMをスタックするためのアーキテクチャ。

- デジタル加入者線アクセス・マルチプレクサ(DSLAM)をスタックするためのアーキテクチャであって、

制御回路と、中央局へのアップリンク通信回路と、1つのマスタDSLAMと隣接して回路が相互接続される2つのDSLAMと通信するための2つの低電圧差分信号(LVDS)回路とを有する、前記1つのマスタDSLAMと、

プログラマブルの制御回路と、隣接して仮想的に回路が相互接続される2つのDSLAMと通信するための2つのLVDS回路とを、それぞれが有する複数のスレーブDSLAMと、

各スレーブDSLAMの前記制御回路を選択的にプログラミングして、第1の選択されたモードにおいてラウンド・ロビンとして、そして第2の選択されたモードにおいてスプリットとして、前記各スレーブDSLAMの前記LVDS回路における通信の方向を制御するための、選択的にプログラミングするプログラミング手段であって、前記スプリットは、前記1つのマスタDSLAMを通じての通信のために、前記1つのマスタDSLAMと隣接した所望される仮想的回路相互接続において選択的にプログラムされるものである、プログラミング手段と

前記スレーブDSLAMのうちの1つスレーブDSLAMの故障を検出するための手段であって、選択的にプログラミングする前記プログラミング手段が、故障を検出するための手段に応答して、前記1つのマスタDSLAMを通じての通信を維持しつつ、ラウンド・ロビンの通信から、故障が生じた前記スレーブDSLAMを回避するスプリット・パスの通信へと再プログラミングすることを可能にするものである、故障を検出するための手段と、

予備のマスタDSLAMであって、前記1つのマスタDSLAMが故障したときに、前記予備のマスタDSLAMは、制御回路と、中央局へのアップリンク通信回路と、マスタDSLAMと隣接して回路が相互接続される2つのDSLAMと通信するための2つの低電圧差分信号(LVDS)回路とを有する1つのマスタDSLAMとして動作することが可能にされるものであり、選択的にプログラミングする前記プログラミング手段は、新たな1つのマスタDSLAMとしての前記予備のマスタDSLAMを通じての通信を維持しつつ、ラウンド・ロビンの通信から、故障が生じた前記1つのマスタDSLAMを回避するスプリット・パスの通信へと再プログラミングするものであり、前記スプリットは、前記予備のマスタDSLAMを通じての通信のために、前記予備のマスタDSLAMと隣接した所望される仮想的回路相互接続において選択的にプログラムされるものである、予備のマスタDSLAMと

を備えるDSLAMをスタックするためのアーキテクチャ。 - 請求項1に記載のDSLAMをスタックするためのアーキテクチャであって、前記マスタDSLAMは中央局へのアップリンク通信回路を含む、DSLAMをスタックするためのアーキテクチャ。

- デジタル加入者線アクセス・マルチプレクサ(DSLAM)をスタックするためのアーキテクチャを操作する方法において、

マスタDSLAMの制御回路を用いて、複数のスレーブDSLAMのそれぞれにおける制御回路を選択的にプログラミングして、それぞれの前記スレーブDSLAMの低電圧差分信号(LVDS)回路における通信の方向を、第1の選択されたモードにおいてラウンド・ロビンとして制御するステップと、

前記マスタDSLAMの前記制御回路を用いて、前記複数のスレーブDSLAMのうちの特定のものにおける前記制御回路を選択的にプログラミングして、前記LVDS回路における通信の方向を、第2の選択されたモードにおいてスプリット・パスとして制御するステップと、

を備える方法。 - 請求項10に記載の方法であって、前記マスタDSLAMに隣接して回路が接続されている2つの前記DSLAMは、リング構造を形成する最初のスレーブDSLAMと最後のスレーブDSLAMとである、方法。

- 請求項10に記載の方法であって、前記マスタDSLAMに隣接して回路が接続されている2つの前記DSLAMは、前記第2の選択されたモードにおける前記スプリット・パスに関しては、デュアル・リンク構造を形成する最初のスレーブDSLAMと中間のスレーブDSLAMとである、方法。

- デジタル加入者線アクセス・マルチプレクサ(DSLAM)をスタックするためのアーキテクチャにおいて、

1つのマスタDSLAMであって、1つの制御回路と、前記マスタDSLAMと隣接して回路が相互接続される2つのDSLAMと通信するための2つの低電圧差分信号(LVDS)回路とを有する、前記マスタDSLAMと、

1つのプログラマブルの制御回路と、隣接して仮想的に回路が相互接続される2つのDSLAMと通信するための2つのLVDS回路とを、それぞれが有する複数のスレーブDSLAMと、

を備え、

前記マスタDSLAMの前記制御回路は、それぞれの前記スレーブDSLAMの前記LVDS回路における通信の方向を、第1の選択されたモードにおいてラウンド・ロビンとして制御し、第2の選択されたモードにおいてスプリット・パスとして制御するように、それぞれの前記スレーブDSLAMの前記制御回路を選択的にプログラミングするように構成される、

DSLAMをスタックするためのアーキテクチャ。 - 請求項13に記載のアーキテクチャであって、前記マスタDSLAMに隣接して回路が接続されている2つの前記DSLAMは、リング構造を形成する最初のスレーブDSLAMと最後のスレーブDSLAMとである、アーキテクチャ。

- 請求項13に記載のアーキテクチャであって、前記マスタDSLAMに隣接して回路が接続されている2つの前記DSLAMは、前記第2の選択されたモードにおける前記スプリット・パスに関しては、デュアル・リンク構造を形成する最初のスレーブDSLAMと中間のスレーブDSLAMとである、アーキテクチャ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/346,485 US7116674B2 (en) | 2003-01-16 | 2003-01-16 | Method and apparatus for digital subscriber line access multiplexer stacking |

| PCT/US2004/000262 WO2004066107A2 (en) | 2003-01-16 | 2004-01-06 | Method and apparatus for digital subscriber line access multiplexer stacking |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006518950A JP2006518950A (ja) | 2006-08-17 |

| JP2006518950A5 JP2006518950A5 (ja) | 2007-03-01 |

| JP4499089B2 true JP4499089B2 (ja) | 2010-07-07 |

Family

ID=32712160

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006500811A Expired - Fee Related JP4499089B2 (ja) | 2003-01-16 | 2004-01-06 | デジタル加入者線アクセス・マルチプレクサのスタッキングの方法および装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7116674B2 (ja) |

| EP (1) | EP1584150B1 (ja) |

| JP (1) | JP4499089B2 (ja) |

| AT (1) | ATE524889T1 (ja) |

| WO (1) | WO2004066107A2 (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7009977B1 (en) * | 2000-06-09 | 2006-03-07 | Conklin Corporation | Method and system for expanding services in a digital loop carrier system |

| EP1762055A4 (en) * | 2004-03-10 | 2010-03-17 | Scaleout Software Inc | EVOLVING ARCHITECTURE OF HIGH-AVAILABILITY CLUSTER ELEMENTS |

| US7346051B2 (en) * | 2004-06-25 | 2008-03-18 | Matsushita Electric Industrial Co., Ltd. | Slave device, master device and stacked device |

| US7433365B1 (en) * | 2004-08-31 | 2008-10-07 | Adtran, Inc. | System architecture for linking channel banks of a data communication system |

| US7440393B2 (en) * | 2004-12-09 | 2008-10-21 | Scalent Systems, Inc. | Method and system for managing communication in a data network |

| CN100361470C (zh) * | 2004-12-30 | 2008-01-09 | 华为技术有限公司 | 数字用户线路接入中采用从框实现组播的方法 |

| JP4106632B2 (ja) * | 2005-01-31 | 2008-06-25 | 富士通株式会社 | 通信装置及び通信制御方法 |

| US20070097870A1 (en) * | 2005-11-01 | 2007-05-03 | Bakri Aboukarr | Remote control and control redundancy for distributed communication equipment |

| US8005879B2 (en) | 2005-11-21 | 2011-08-23 | Sap Ag | Service-to-device re-mapping for smart items |

| US8156208B2 (en) | 2005-11-21 | 2012-04-10 | Sap Ag | Hierarchical, multi-tiered mapping and monitoring architecture for service-to-device re-mapping for smart items |

| US7860968B2 (en) * | 2005-11-21 | 2010-12-28 | Sap Ag | Hierarchical, multi-tiered mapping and monitoring architecture for smart items |

| DE102005058982B4 (de) * | 2005-12-09 | 2008-02-28 | Infineon Technologies Ag | Bündelungsschaltung für eine Leitungstreiberkarte und Verfahren zum Bündeln von Datenfragmenten |

| US8522341B2 (en) | 2006-03-31 | 2013-08-27 | Sap Ag | Active intervention in service-to-device mapping for smart items |

| US8065411B2 (en) | 2006-05-31 | 2011-11-22 | Sap Ag | System monitor for networks of nodes |

| US8131838B2 (en) * | 2006-05-31 | 2012-03-06 | Sap Ag | Modular monitor service for smart item monitoring |

| US8296413B2 (en) | 2006-05-31 | 2012-10-23 | Sap Ag | Device registration in a hierarchical monitor service |

| DE102006033639A1 (de) * | 2006-07-20 | 2008-01-24 | Robert Bosch Gmbh | Elektronische Vorrichtung zum Anschluss an einen optischen Datenbus und Verfahren |

| US8396788B2 (en) | 2006-07-31 | 2013-03-12 | Sap Ag | Cost-based deployment of components in smart item environments |

| CN101507319A (zh) * | 2006-09-06 | 2009-08-12 | 三菱电机株式会社 | 数据重传方法、网络控制装置、移动台及基站 |

| US20080080391A1 (en) * | 2006-09-29 | 2008-04-03 | Sbc Knowledge Ventures, L.P. | Method and apparatus for supporting an asymmetric transport network |

| US8259707B2 (en) * | 2006-10-17 | 2012-09-04 | Generonix, Inc. | Wireless access point network system supported through existing transmission lines |

| US8363660B2 (en) * | 2006-11-09 | 2013-01-29 | Telefonaktiebolaget Lm Ericsson (Publ) | Arrangement and method relating to identification of hardware units |

| US8527622B2 (en) * | 2007-10-12 | 2013-09-03 | Sap Ag | Fault tolerance framework for networks of nodes |

| US8780915B2 (en) | 2009-06-26 | 2014-07-15 | Telekom Malaysia Berhad | Method and system for tagging packets routed to customer premises devices via clusters of dedicated customer interfaces |

| CN103780496B (zh) | 2012-10-17 | 2017-07-14 | 新华三技术有限公司 | 应用于星型堆叠系统中的报文转发方法和设备 |

| CN106550060B (zh) * | 2016-10-28 | 2020-09-11 | 新华三技术有限公司 | 一种网络管理接口地址分配方法及装置 |

| KR20210029615A (ko) * | 2019-09-06 | 2021-03-16 | 에스케이하이닉스 주식회사 | 반도체장치 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5914957A (en) * | 1996-12-19 | 1999-06-22 | Otis Elevator Company | Automatic node configuration with identical nodes |

| JP2000312207A (ja) * | 1999-04-27 | 2000-11-07 | Mitsubishi Electric Corp | 通信システム |

| US6801533B1 (en) * | 1999-12-09 | 2004-10-05 | Cisco Technology, Inc. | System and method for proxy signaling in a digital subscriber line access multiplexer (DSLAM) |

| US6680904B1 (en) * | 1999-12-27 | 2004-01-20 | Orckit Communications Ltd. | Bi-directional chaining of network access ports |

| US6834038B1 (en) * | 2000-08-11 | 2004-12-21 | Orckit Communications Ltd. | Protection against master unit failure in remote network access multiplexing |

| US6822944B1 (en) * | 2000-11-08 | 2004-11-23 | Orckit Communications Ltd. | Management interface for a network access multiplexing system |

| US7009939B2 (en) * | 2001-05-21 | 2006-03-07 | Lucent Technologies Inc. | Adaptive resource management in a communication system |

-

2003

- 2003-01-16 US US10/346,485 patent/US7116674B2/en not_active Expired - Lifetime

-

2004

- 2004-01-06 AT AT04700392T patent/ATE524889T1/de not_active IP Right Cessation

- 2004-01-06 JP JP2006500811A patent/JP4499089B2/ja not_active Expired - Fee Related

- 2004-01-06 WO PCT/US2004/000262 patent/WO2004066107A2/en active Application Filing

- 2004-01-06 EP EP04700392A patent/EP1584150B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US7116674B2 (en) | 2006-10-03 |

| WO2004066107A3 (en) | 2005-04-28 |

| JP2006518950A (ja) | 2006-08-17 |

| US20040141609A1 (en) | 2004-07-22 |

| ATE524889T1 (de) | 2011-09-15 |

| EP1584150A2 (en) | 2005-10-12 |

| WO2004066107A2 (en) | 2004-08-05 |

| EP1584150B1 (en) | 2011-09-14 |

| EP1584150A4 (en) | 2006-10-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4499089B2 (ja) | デジタル加入者線アクセス・マルチプレクサのスタッキングの方法および装置 | |

| US9106523B2 (en) | Communication device and method of controlling the same | |

| EP1708379B1 (en) | Communication system having backup function for several series devices and method for carrying out the function of switching | |

| JPS60176346A (ja) | リング型信号伝送ネツトワ−ク | |

| CN101146014B (zh) | 容错以太网 | |

| CN1885959B (zh) | 用于电信系统的容错单平面交换结构 | |

| US20070067462A1 (en) | Information processing apparatus, communication load decentralizing method, and communication system | |

| JP2006518950A5 (ja) | ||

| WO2004102902A1 (ja) | ノード冗長制御方法およびノード冗長制御装置 | |

| JPWO2006114809A1 (ja) | 伝送装置、および伝送装置とレイヤ2スイッチ間の冗長方法 | |

| CN1330473A (zh) | 反向复用业务中的备用冗余 | |

| JP4705492B2 (ja) | リングノード装置及びリングノード冗長方法 | |

| US6603736B1 (en) | Communication device for transmitting message signals | |

| US6895024B1 (en) | Efficient implementation of 1+1 port redundancy through the use of ATM multicast | |

| JP2000512112A (ja) | Atmセルの双方向伝送のための伝送装置を代替え的に切り換えるための方法 | |

| JP2003124979A (ja) | 交換機におけるセレクタおよび回線冗長方法およびそのシステム | |

| JP3881716B2 (ja) | 通信信号伝送用の通信ネットワーク | |

| JP2001268101A (ja) | ネットワークシステム | |

| JPH1065696A (ja) | 通信ネットワークおよび障害通知方法 | |

| JP3575432B2 (ja) | 回線切替装置及び回線切替方法 | |

| JP2000201159A (ja) | 2重化呼制御装置 | |

| JP3046118B2 (ja) | 時分割通話路方式 | |

| JP2001244935A (ja) | Atm交換機におけるnms制御による迂回制御方式 | |

| JPH07327053A (ja) | 多重化装置及び中継装置及び集線装置 | |

| JP2000244505A (ja) | パケット通信ネットワークシステム及びその制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070109 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090824 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090828 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20091125 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20091202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100226 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100318 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100414 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130423 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4499089 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130423 Year of fee payment: 3 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D04 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130423 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140423 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |