JP4472064B2 - Manufacturing method of semiconductor device - Google Patents

Manufacturing method of semiconductor device Download PDFInfo

- Publication number

- JP4472064B2 JP4472064B2 JP24075899A JP24075899A JP4472064B2 JP 4472064 B2 JP4472064 B2 JP 4472064B2 JP 24075899 A JP24075899 A JP 24075899A JP 24075899 A JP24075899 A JP 24075899A JP 4472064 B2 JP4472064 B2 JP 4472064B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor

- gate wiring

- substrate

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

- H10D30/6715—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions

- H10D30/6719—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions having significant overlap between the lightly-doped drains and the gate electrodes, e.g. gate-overlapped LDD [GOLDD] TFTs

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、結晶性半導体薄膜を用いて半導体装置を作製する方法に関する。なお、本発明の半導体装置は、薄膜トランジスタのような素子単体だけでなく、薄膜トランジスタで構成された半導体回路を有する電子機器や、代表的にはアクティブマトリクス基板を用いた液晶表示装置や、イメージセンサー等を備えたパーソナルコンピュータやデジタルカメラ等の電子機器をもその範疇とする。

【0002】

【従来の技術】

薄膜トランジスタ(TFT)は各種集積回路に利用されているが、TFTはガラスや石英など絶縁性基板に作製できることから、特にアクティブマトリクス型液晶表示装置のマトリクス回路のスイッチング素子として好適である。

【0003】

TFTの半導体層としては非晶質シリコン膜や多結晶シリコン膜が一般的に用いられている。TFTでマトリクス回路のドライバ回路を構成するには、高移動度な多結晶シリコン膜を半導体層に用いる必要がある。一般に、半導体層に用いられる多結晶シリコン膜を形成するには、非晶質シリコン膜を成膜し、この非晶質シリコン膜を熱処理する熱結晶化、又はエキシマレーザ光を照射するレーザ結晶化が用いられている。

【0004】

現在、アクティブマトリクス基板に用いられるガラス基板の耐熱性のため、結晶化のプロセス温度の上限を600℃程度にすることが要求されている。結晶化の低温化のために、熱結晶化には20時間以上要してしまう。

【0005】

他方、エキシマレーザによるレーザ結晶化技術はプロセスの低温化、時短化を可能にした技術の1つである。エキシマレーザ光のエネルギーは非晶質シリコンの極表面、深さ10nm程度で吸収され熱に変換されるので、基板に熱的な影響を殆ど与えずに、1000℃前後の熱アニールに匹敵するエネルギーを短時間で非晶質シリコン膜に与えることができ、また高い結晶性の半導体膜を形成することができる。

【0006】

また、TFTの構造として、代表的にボトムゲート型(代表的には、逆スタガ型)とトップゲート型(代表的には、コプラナ型)が知られている。ボトムゲート型は基板上にゲート配線(電極)、ゲート絶縁膜、半導体層がこの順序で積層され、トップゲート型は逆に半導体層、ゲート絶縁膜、ゲート配線(電極)の順で積層されている。

【0007】

図18を用いて、従来の逆スタガ型の多結晶シリコンを用いたTFTの製造工程を簡単に説明する。図18はチャネル長(ゲート長)に沿ったTFTの断面図である。

【0008】

ガラス基板1上に、スパッタ法でCr、Ta等の厚さ300〜500nmの金属膜を成膜し、テーパー状にパターニングしてゲート配線2を形成する。次に、CVD法でゲート絶縁膜3としてSiNy(窒化シリコン) 、SiO2 (酸化シリコン)を100〜200nmの厚さに成膜する。次に、CVD法で50〜100nmの厚さの非晶質シリコン膜4を成膜する。(図18(A))

【0009】

エキシマレーザ光を照射して結晶化し、多結晶シリコン膜5を形成する。(図18(B))

【0010】

この多結晶シリコン膜5をパターニングして半導体層6を形成する。次に、半導体層6にドナー又はアクセプタとなる不純物を選択的に添加して、ソース領域6S、ドレイン電極6D、チャネル形成領域6Cをそれぞれ形成する。(図18(C))

【0011】

次に、層間絶縁膜7として、CVDでSiO2 を成膜し、層間絶縁膜7にコンタクトホールを形成し、ソース電極8、ドレイン電極9を形成する。(図18(D))

【0012】

【発明が解決しようとする課題】

図18に示すように、多結晶シリコンを用いた逆スタガ型のTFTの製造工程では、ゲート配線の膜厚は300〜500nm程度であり、他方ゲート絶縁膜の膜厚は100〜200nmであるため、図18(A)に示すように、非晶質シリコン膜4表面はゲート配線2の形状を反映した凹凸が生ずる。

【0013】

一般に、レーザ結晶化では、エキシマレーザ光を線状ビーム又は矩形状ビームに整形し、このビームを走査して照射している。しかしながら、非晶質シリコン膜3表面の高低差のために、場所ごとにビームの焦点位置が異なっており、非晶質シリコン膜3に与えられるエネルギーが場所ごとに異なってしまう。この高低差に合わせてビームの焦点距離を変化させることは殆ど困難であるので、多結晶シリコン膜5にはレーザ光の焦点のずれによる結晶化のばらつきが発生してしまう。結晶化のばらつきはTFTのしきい値電圧がばらつく原因となっている。

【0014】

また、多結晶シリコンを用いたTFTでは、オフ電流が大きいことが問題となっている。オフ電流の原因は、TFTがオフ状態の時に、ドレイン電極9に印加された電圧が、チャネル形成領域6C、ドレイン領域6Dとの接合部に集中するために、この接合部分でトラップを介して電流が漏れるためだと考えられている。

【0015】

更に、多結晶シリコンを用いたTFTでは、ゲート絶縁膜3が非晶質シリコンを用いた場合よりも薄く、100〜200nmであるため、ゲート配線2の縁部2a(図18(D)参照)での段差被覆性が問題となる。縁部2aでは、CVD法によりSiNy 、SiO2 が成長しづらいので、ゲート絶縁膜2の膜厚が薄くなってしまう。そのため、端部2aでは、ゲート配線2と半導体層6がショートしたり、ゲート絶縁膜3に電子やホールが注入されることで、しきい値電圧がシフトしたり、さらにゲート絶縁膜3が静電破壊しやすくなって、これらのことがTFTの信頼性が劣化させる原因となっている。

【0016】

本発明の目的は、上述した問題点を解消し、ゲート配線、ゲート絶縁膜、半導体層の順に積層したボトムゲート型の半導体素子を備えた半導体装置において、レーザ結晶化を均一化する構造、及びその作製方法を提供することにある。これと同時に、オフ電流を低減し、信頼性を向上させたボトムゲート型の半導体素子の構造及びその作製方法を提供することにある。

【0017】

【課題を解決するための手段】

上述の課題を解決するために、本発明の半導体装置は、絶縁表面に形成されたゲート電極と、前記ゲート電極を覆って形成され、絶縁性有機樹脂でなる平坦化膜と絶縁性無機膜とでなる積層膜を有するゲート絶縁膜と、前記ゲート絶縁膜を覆う半導体層とが積層された半導体装置であって、前記半導体層は結晶性半導体膜で形成されていることを特徴とする。

【0018】

更に、本発明は上記の積層構造を有する半導体装置の製造方法であって、

絶縁表面にゲート配線を形成する工程と、

前記ゲート配線を覆って絶縁性有機樹脂でなる平坦化膜を形成する工程と、

前記平坦化膜に接して絶縁性無機膜を形成する工程と、

前記絶縁性無機膜を覆って非晶質成分を有する半導体膜を形成する工程と、

前記非晶質成分を有する半導体膜を結晶化して結晶性半導体膜を形成する工程とを少なくとも有することを特徴とする。

【0019】

なお、本明細書中において、ゲート電極はゲート配線が半導体層と交差する部分を指すこととする。また、ソース/ドレイン配線とソース/ドレイン電極においても、ゲート配線とゲート電極の関係と同様とする。

【0020】

上記の構成において、ゲート電極、ゲート配線の段差は平坦化膜で埋められるため、ゲート絶縁膜の表面は平坦になる。よって、非晶質成分を有する半導体膜を平坦な表面に形成することができるので、半導体膜自体を平坦な膜に成膜できる。そのため、レーザ光を照射して結晶化しても、部分ごとに焦点位置が異なることがないため、結晶化を従来例よりも均一にすることができる。

【0021】

また、絶縁性有機樹脂膜は一般に塗布法で成膜可能であり、塗膜はCVD法の気相法で形成される絶縁性無機膜よりも非常に段差被覆性が優れている。よって、絶縁性樹脂膜がゲート配線の端部で有機樹脂膜が薄くなることがないため、上述した、ゲート配線と半導体層とのショートや、ゲート絶縁膜の絶縁破壊を防ぐことができ、半導体装置の信頼性、安定性を向上させることができる。

【0022】

また、有機樹脂膜は絶縁性無機膜よりも比誘電率が小さいため、ゲート絶縁膜を積層膜としても寄生容量を小さくすることができる。

【0023】

絶縁性無機膜はCVD法などの化学気相法やスパッタ法などの物理気相法で形成されるため、有機樹脂膜よりも不純物の混入が少なく、また不純物の大きさも小さいので、絶縁性有機樹脂膜と絶縁性無機膜との積層膜を有することにより、ゲート絶縁膜のピンホールを低減することができ、有機樹脂膜上に半導体層を形成するよりも、半導体層とゲート絶縁膜の界面準位を下げることができる。

【0024】

なお、上記構成において、非晶質成分を有する半導体膜とは、結晶性のない非結晶性半導体膜、又は結晶性を有するが100nm以上のオーダーの結晶粒が殆どない半導体薄膜であって、具体的には非晶質半導体膜、微結晶半導体膜を指す。微結晶半導体膜は、数nm〜数十nmの大きさの結晶粒を含む微結晶と非晶質との混相状態の半導体膜である。

【0025】

より具体的には、非晶質成分を有する半導体膜は非晶質シリコン膜、微結晶シリコン膜、非晶質ゲルマニウム膜、微結晶ゲルマニウム膜、非晶質Six Ge1-x (0<x<1)であり、これらの半導体膜はプラズマCVD法、減圧CVD法等の化学気相法やスパッタ法などの物理気相法で成膜される。また、半導体膜の膜厚は10nm〜150nm程度とする。

【0026】

【発明の実施の形態】

図1〜図3を用いて本発明の実施の形態を説明する。本実施形態は、逆スタガ型TFTをアクティブマトリクス基板のマトリクス回路のスイッチング素子、いわゆる画素TFTに用いた例である。

【0027】

[実施形態1] 図1を用いて、本実施形態を説明する。

【0028】

図1(A)に示すように、基板10用意し、基板10表面に下地膜11を形成する。基板10にはガラス基板、石英基板、セラミック基板、樹脂基板等の絶縁性基板、単結晶シリコン基板、更にステンレス基板、Cu基板、Ta、W、Mo、Ti、Cr等の高融点金属材料又はこれら合金系(例えば、窒素系合金)からなる基板等の導電性基板を用いることができる。

【0029】

また、ボトムゲート型TFTの製造工程で用いられている裏面露光工程を用いる場合には、基板10は露光に用いられる光に対して透過性を有するものを用いる。代表的には、ガラス基板や石英基板、セラミック基板、樹脂基板を用いることができる。

【0030】

下地膜11は、半導体膜に基板から不純物が拡散するのを防ぐための膜である。ボトムゲート型の半導体素子はゲート絶縁膜によって、基板から半導体層が隔てられるため、絶縁性基板を用いた場合には形成しなくともよいが、下地膜11を形成することにより、基板10上に形成される絶縁膜や金属膜の密着性を高めることができる。

【0031】

下地膜10には、CVD法などで成膜した酸化シリコン(SiO2 )膜や、窒化シリコン(SiNy )膜、窒化酸化シリコン(SiOx Ny )膜等の絶縁性無機膜が使用できる。例えば、シリコン基板を使用した場合には、熱酸化によってその表面を酸化して下地膜を形成することができる。また、石英基板やステンレス基板などの耐熱性基板を用いた場合には、非晶質シリコン膜を成膜し、このシリコン膜を熱酸化してもよい。

【0032】

なお、裏面露光工程を用いない場合には、下地膜11として、タングステン、クロム、タンタル等の高融点金属の被膜や、窒化アルミニウム膜等の高い伝導度を有する被膜を下層に、上記の絶縁性無機膜を上層に積層した積層膜を用いてもよい。この場合には、半導体装置で発生した熱が下地膜11の下層の被膜から放射されるため、半導体装置の動作が安定できる。

【0033】

下地膜11上に、導電性膜を成膜しパターニングしてゲート配線12を形成する。ゲート配線12を形成する導電性材料は、Alを主成分とする材料、又はTa、W、Mo、Ti、Cr等の高融点金属合やこれらの合金(例えば、高融点金属同士の合金、高融点金属と窒素との合金などを用いることができる。また、列記した材料の積層膜で形成することができる。例えば、Scを数重量%含有するAl膜と、Ta膜との2層膜や、Ta膜を窒化タンタル合金膜で挟んだ3層膜を用いることができる。

【0034】

また、ボトムゲート型TFTの製造工程で用いられている裏面露光工程を用いる場合には、ゲート配線材料は露光に用いられる光に対して遮光性を有する材料を用いる。

【0035】

次に、ゲート配線12を覆って、ゲート絶縁膜13を形成する。まず、スピンコータを用いて、平坦化膜13aとして絶縁性有機樹脂膜を形成する。次に、スパッタ法又はCVD法により、平坦化膜13a上に絶縁性無機膜13bを積層する。(図1(A))

【0036】

平坦化膜13aに用いられる有機樹脂材料は、その表面に直接スパッタ法又はCVD法で絶縁性無機膜13bが堆積可能な膜であり、また、後の工程の基板温度を300℃程度まで上昇させることができることが可能な材料を選択する。例えば、ベンゾシクロブテン(BCB)、ポリイミド、アクリルを用いることが可能である。

【0037】

絶縁性無機膜13bとしては、酸化シリコン(SiO2)膜、窒化シリコン(SiNy )膜、酸化窒化シリコン(SiOx Ny )膜の単層膜、又はこれらの積層膜を用いることができる。

【0038】

絶縁性有機樹脂膜は塗布法で成膜可能なため、平坦化膜13aによってゲート配線12よる段差を埋めて、平坦な表面を有するゲート絶縁膜13を得ることができる。平坦化膜13aを塗布法で形成することにより、従来のようにゲート配線12の端部で平坦化膜13aの厚さが薄くなることがなくなる。よって、ゲート配線12と半導体層がショートしたり、ゲート絶縁膜13に電子やホールが注入されることで、しきい値電圧がシフトしたり、さらにゲート絶縁膜13が静電破壊したりすることが防止できる。

【0039】

従来では、ゲート絶縁膜の被覆性を高めるため、ゲート配線12をテーパー状にパターニングしているが、、テーパー状にパターニングしなくとも、ゲート配線12を十分な厚さの平坦化膜13aにより被覆することが可能である。従って、複雑なテーパーエッチング工程を用いずにすむ。

【0040】

また平坦化膜13a上に絶縁性無機膜13bを積層して形成したため、ゲート絶縁膜13のピンホール密度を低減することができ、しきい値電圧のシフトが低減できる。

【0041】

なお、ゲート絶縁膜13において、平坦化膜13aの厚さはゲート配線12の最も高い部分と絶縁性無機膜13bとで挟まれている部分が10nm〜0.1μmとし、絶縁性無機膜13bの膜厚は50nm〜0.1μmとする。

【0042】

次に、プラズマCVD、減圧CVD法、熱CVD等の気相法で非晶質成分を有する半導体膜15を成膜する。半導体膜15は平坦なゲート絶縁膜13表面に形成されるため、従来のようにゲート配線12の形状を反映した高低差が生じない。(図1(B))

【0043】

次に、400nm以下の波長のレーザ光又は、400nm以下の波長の強光を照射して、半導体膜15を結晶化して結晶性半導体膜16を形成する。例えば、非晶質シリコン膜を結晶化した場合には、多結晶シリコン膜が形成される。(図1(C))

【0044】

結晶化に使用する光源はエキシマレーザを用いることができる。例えばKrFエキシマレーザー(波長248nm)、XeClエキシマレーザー(波長308nm)、XeFエキシマレーザー(波長351、353nm)、ArFエキシマレーザー(波長193nm)等を用いることができる。また、400nm以下の波長を発する光源として水銀ランプを用いることができる。

【0045】

本発明では、半導体膜15は従来と比較して平坦に成膜される。よって、結晶化工程で照射されるレーザ光又は強光の焦点距離が、部分ごとに異なることがなくなり、半導体膜に与えられる光エネルギーが均一になるので、結晶化のばらつきを小さくできる。

【0046】

次に、得られた結晶性半導体膜16を島状にパターニングする。そして、ドナー又はアクセプターとなる導電型を付与する不純物を、島状の半導体膜に選択的に添加して、ソース領域17、ドレイン領域18を形成する。実質的に真性な半導体層部はチャネル形成領域19である。

【0047】

図1(B)、図1(C)又は半導体膜16のパターニング工程後、しきい値制御をするために不純物を半導体膜26又は半導体層28に添加する工程を加えて、チャネル形成領域19が真性な半導体層で形成されるようにするとよい。

【0048】

なお、本明細書中で真性とは、シリコンのフェルミレベルを変化させうる不純物を一切含まない領域を指す。実質的に真性な半導体とは、電子と正孔が完全に釣り合って導電型を相殺させた領域、即ち、しきい値制御が可能な濃度範囲(SIMS分析で1×1014〜1×1017atoms/cm3 )でドナー又はアクセプターとなる導電型を付与する不純物を含む領域、または意図的に逆導電型の不純物を添加することにより導電型を相殺させた半導体を示す。

【0049】

そして、半導体層をSiO2 等でなる層間絶縁膜20で覆い、ソース/ドレイン領域17、18に対するコンタクトホールを開口して、信号線として機能するソース配線21、ドレイン電極22を形成する。更に、ソース配線21、ドレイン電極22を覆って層間絶縁膜23を形成する。層間絶縁膜23には、セルギャップを均一にするため、BCB、ポリイミド、アクリルなどの平坦化膜を少なくとも1層形成するのが好ましい。次に、ドレイン電極22対するコンタクトホールを形成し、ITOやAlでなる画素電極24を形成する。

【0050】

図1では、一画素に配置された画素TFTのみを図示したが、実際は基板10上に行列状に配置されている。

【0051】

[実施形態2] 図2、図3を用いて、本実施形態を説明する。本実施形態も実施形態1と同様に、ボトムゲート型のTFTをマトリクス回路の画素TFTに適用した例に関するものである。

【0052】

一般に、1つのマトリクス回路には100万個以上の画素TFTが形成されるが、全ての画素TFTの特性を均一に、特にしきい値電圧を均一にすることが要求されている。しきい値電圧をシフトさせる大きな要因の1つは、チャネルとゲート絶縁膜との界面状態にある。

【0053】

そこで、本実施形態では、半導体層のチャネル形成領域とこれに接する絶縁膜との界面を清浄保つことを可能にした製造方法を示す。

【0054】

実施形態1と同様、基板20を用意し、基板20表面に下地膜21を形成する。下地膜21表面に、上述した導電性材料でなる膜を成膜し、テーパー状にパターニングして、ゲート配線22を形成する。次に、ゲート配線22を覆って、ゲート絶縁膜23を形成する。まず、スピンコータを用いて、平坦化膜23aとして、BCB、ポリイミド、アクリルなどの絶縁性有機樹脂膜を形成する。次に、スパッタ法又はCVD法により、平坦化膜23a上にSiO2膜、SiNy膜、SiOxNy膜等の絶縁性無機膜23bを積層する。(図2(A))

【0055】

次に、非晶質成分を有する半導体膜24と、SiO2、SiNy、又はSiOxNyでなる保護膜25を大気開放しないで積層する。成膜手段としては、CVD法、スパッタ法を用いることができる。大気に曝さないことで、半導体膜24−保護膜25界面にも大気からの汚染物質が付着しないようにする。半導体膜24、保護膜25は同一チャンバーで連続成膜してもよいし、マルチタスク型のスパッタ装置又はCVD装置を用いて、それぞれ専用のチャンバーで成膜してもよい。

【0056】

もしくは、ゲート絶縁膜23−半導体膜24−保護膜25それぞれの界面を清浄に保つために、絶縁性無機膜23b、半導体膜24、保護膜25を大気開放しないで積層することが好ましい。(図2(B))

【0057】

保護膜25の膜厚は5〜50nm、代表的には10〜20nmとする。この保護膜25は、大気中の不純物による汚染から初期半導体膜24の表面を保護したり、半導体膜24に直接フォトレジストを形成しないようにして、半導体膜24が汚染しないようにするためのものである。また、保護膜25はフォトレジストとの密着性を高める効果もある。

【0058】

こうして図2(B)の状態が得られたら、半導体膜24に対して、実施形態1で述べたように400nm以下の波長のレーザ光又はそれと同等な強光を照射して、結晶性半導体膜26を形成する。この工程では、レーザ光又はそれと同等な強光は保護膜25を介して照射されるので、保護膜25−結晶性半導体膜26の界面は清浄に保たれる。

【0059】

次に、同一のフォトレジストマスクを用いて、保護膜25、結晶性半導体26を島状にパターニングして、保護膜27、半導体層28を形成する。このように、半導体層28の上面を保護膜27で覆ったままの状態を維持することで、半導体層28を大気の汚染から保護できる。(図2(D))

【0060】

なお、図2(C)または図2(D)の工程後、しきい値制御をするために不純物を半導体膜26又は半導体層28に添加する工程を加えてもよい。

【0061】

次に、フォトレジストを塗布し、基板20の裏面から露光して、ゲート配線22をマスクとするレジストマスク30を自己整合的に形成する。ここでは、チャネル長方向のゲート電極幅とマスク30幅が一致するように、即ち、ゲート電極22の側面とマスク30側面が一致するように露光光量を調節する。

【0062】

次に、このフォトレジストマスク30を用いて、ドナー又はアクセプターとなる不純物を保護膜27を介して、半導体層28に添加して、N型又はP型の不純物領域31、32を形成する。領域31、32はソース/ドレイン領域となる部分である。(図3(A))

【0063】

マスク30を剥離した後、再びフォトレジストを塗布して、基板20の裏面から露光して、ゲート配線22をマスクとしてレジストマスク34を自己整合的に形成する。この場合には、先の裏面露光よりもオーバー露光して、チャネル長方向のゲート電極幅よりもマスク34幅を細らせ、マスク34の側面をゲート配線22よりも内側にする。このマスク34により、低濃度不純物領域(LDD)の長さ、チャネル長が規定される。

【0064】

フォトレジストマスク34を用いて、保護膜27を介してドナー又はアクセプタとなる不純物を添加して、N型又はP型のソース領域35、N型又はP型のドレイン領域36、N- 型又はP- 型の低濃度不純物領域38、39を形成する。2回の不純物添加工程で不純物が添加されなかった真性な領域がチャネル形成領域37となる。不純物添加工程後、添加した不純物の活性化するため、エキシマレーザ光を照射してアニールする。

【0065】

本形態では、TFTをLDD構造とすることでオフ電流を下げる効果がより高くすることができる。更に、ゲート配線22をテーパー状にし、ゲート絶縁膜23が平坦化膜23a、絶縁性無機膜23bでなる積層膜を有することにより、よりオフ電流を低減できる構造となっている。

【0066】

つまり、平坦化膜23aはゲート配線22の段差を埋めるように形成されているために、平坦化膜23aの膜厚は、ゲート配線22のテーパーの斜面部(ほほ、低濃度不純物38、39の下に存在している部分)と、平坦部(チャネル形成領域37の下に存在している部分)を覆っている膜厚が異なり、前者のほうが厚くなる。つまり半導体層28とゲート配線22間のゲート寄生容量は部分ごとに容量が異なり、チャネル形成領域37はゲート寄生容量が高く、低濃度不純物領域38、39は寄生容量が低くなる。

【0067】

この構造により、オフ状態ではゲート寄生容量が低いほうにより大きな電界が印加されるので、チャネル形成領域37端部に集中する電界を低濃度不純物領域38、39に形成される低容量部に分散させることができる。この結果、オフ電流を低減させることができ、また、ゲート絶縁膜23の劣化を抑制できる。

【0068】

次に、SiO2、SiNy又はSiOxNyから選ばれた絶縁膜の単層膜又は多層膜でなる層間絶縁膜40を形成し、ソース/ドレイン領域35、36に対するコンタクトホールを形成し、金属膜を成膜しパターニングして、信号線となるソース配線41、ドレイン電極42を形成する。

【0069】

更に、ソース配線41、ドレイン電極42を覆う層間絶縁膜43を形成する。層間絶縁膜43には、セルギャップを均一にするため、BCB、ポリイミド、アクリルなどの平坦化膜を少なくとも1層形成するのが好ましい。そして層間絶縁膜43にソース配線41、ドレイン電極42に対するコンタクトホールを形成した後、ITOやAlでなる画素電極44を形成する。

【0070】

【実施例】

以下、図4〜図17を用いて、本発明の実施例を説明する。

【0071】

[実施例1] 本実施例では、逆スタガ型TFTでCMOS回路を作製するための製造工程を説明する。なお、本実施例では一つのCMOS回路に注目して説明を行うが同一基板上に複数の回路を形成することもできることは言うまでもない。

【0072】

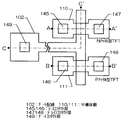

図4〜図6を用いて、本実施例を説明する。図4はCMOS回路の概略の上面図を示す。図4において、102はゲート配線、110はNチャネル型TFTの半導体層、111はPチャネル型TFTの半導体層である。145、146は半導体層110、111とソース配線のコンタクト部であり、147、148は半導体層110、111とドレイン配線とのコンタクト部である。149はゲート配線102と取出し配線とのコンタクト部(ゲートコンタクト部)である。

【0073】

図5、図6を用いて、TFTの製造工程を説明する。なお図5、図6において左側にNチャネル型TFTの断面図を示し、右側にPチャネル型TFTの断面図を示す。各TFTの断面図は図4の鎖線A−A’、鎖線B−B’で切断した断面図に対応する。

【0074】

まず、コーニングス社製1737ガラス基板を基板100として用いる。ガラス基板100表面に下地膜101として200nm厚のSiNy を成膜する。次に、窒化タンタル膜(30nm)/タンタル膜(300nm)/窒化タンタル(300nm)でなる積層膜をスパッタ法で成膜し、CF4 とO2 との混合ガスによりドライエッチングして、テーパー状の断面を有するゲート配線102を形成する。

【0075】

次に、ゲート絶縁膜となる平坦化膜103、絶縁性無機膜104の積層膜をゲート配線102上に形成する。なお、ゲート絶縁膜を形成する前に、ゲート配線102を酸化してもよい。酸化方法としては、プラズマ酸化法、陽極酸化法又は熱酸化法のいずれかの手段を用いれば良い。スループットを考慮するとプラズマ酸化法が好ましい。

【0076】

平坦化膜103としてBCB膜を形成する。まず、スピンコータにより、BCBの溶液をスピンコーティングし、さらにコータを回転させて溶媒を蒸発させる。次に、加熱炉において、窒素などの不活性雰囲気や減圧雰囲気等で、200〜250℃で焼成して、基板全面にBCB膜103を形成する。ゲート配線102上のBCBの膜厚は50〜200nmとすればよい。次に、絶縁性無機膜104として、BCB膜103に接して60nmの厚さのSiOx Ny 膜を成膜し、絶縁性無機膜104上に55nm厚の非晶質シリコン膜105、保護膜106として100nm厚のSiOx Ny 膜を成膜する。

【0077】

本実施例では、BCB膜103の焼成からSiOx Ny でなる保護膜106の成膜を1つのCVD装置で行い、基板を大気に曝さないないようにして、膜103−膜106間の界面状態を良好にする。

【0078】

図7は、本実施例で使用するCVD装置の概略の構成図である。図7(A)は上面図であり、図7(B)は図7(A)の鎖線X−X'による断面図である。

【0079】

図7において、300は処理基板、301は共通室、302、303はロードロック室、304〜306はCVD室であり、307は加熱室である。各室302〜307のチャンバーにはゲート弁311〜316により、気密性を保持して共通室301に連結されている。また、各室には減圧状態にするための排気系や、雰囲気を制御用のガスや反応ガスを供給するためのガス供給系が接続されている。

【0080】

共通室301には処理基板300を移動するためのロボットアーム310を有する。ロボットアーム310は矢印で示すように3次元的に移動自在とされている。ロードロック室302、303は処理基板300を装置外部に搬入・搬出するためのカセットが配置されている。

【0081】

各CVD室304〜306はほぼ構成を有し、本実施例では、接地電位に接続された上部電極341と、RF電源343に接続された下部電極342を有する平行平板型のプラズマCVD装置とする。なお、他の構成でもよい。

【0082】

加熱室307には、処理基板300を設置するための基板ホルダー351、加熱ランプ352、353を有する。

【0083】

以下、図7に示す装置を用いて、膜103〜106の積層膜を形成する方法を説明する。まず、スピンコータでBCB溶液を塗布・乾燥処理済みの基板を加熱室307に移動する。加熱室307を窒素雰囲気とし、250℃で焼成して、BCB膜103を形成する。次に、ロボットアーム310により基板をCVD室304へ移動し、原料ガスにSiH4とN2Oを反応ガスに用いて、基板温度300℃でSiOxNy膜(絶縁性無機膜)104を成膜する。そして、SiH4だけを供給して、基板温度300℃で非晶質シリコン膜105を成膜する。再び、SiH4とN2Oを供給して、基板温度300℃でSiOxNy膜(保護膜)106を成膜する。成膜済みの基板をロードロック室302又は303へと移動して、装置から搬出する。

【0084】

ここでは、1つのCVD室304で膜104〜106を連続成膜して、基板移動に伴う温度変化や汚染を回避するようにしたが、工程のスループットや装置のガス供給系等の設計などを鑑みて、絶縁性無機膜104、半導体膜105、保護膜105を個別のCVD室で成膜してもよい。また、半導体膜である非晶質シリコン膜105と、絶縁膜である無機膜104を保護膜106とで成膜するCVD室を分けてもよい。

【0085】

図5(A)に示すように、下地膜101上にゲート配線102、BCB膜103、SiOx Ny 膜104、非晶質シリコン膜105、SiOx Ny 膜107を積層した構成が得られたら、非晶質シリコン膜105にKrFエキシマレーザー光を照射し、結晶化させて、多結晶シリコン膜107を形成する。照射条件は、パルス周波数が30Hz、レーザーエネルギー密度を100〜500mJ/cm2 、本実施例では350mJ/cm2とする。また、ここではレーザ光を光学系により5mm×12cmの線状整形し、走査しながら照射する。(図5(B))

【0086】

なお、本実施例ではレーザー照射前の段階(成膜段階)で、非晶質成分を有する半導体膜103が非晶質シリコン膜であったので、結晶化という用語を用いたが、成膜段階で多結晶シリコン膜や微結晶シリコン膜であった場合には不適切である。その場合には、結晶性の改善化といった方が適切であろう。即ち、レーザー照射を行うことにより、より高い結晶性を有する半導体膜に変化するというのが適当である。

【0087】

次に、同じフォトレジストマスクを用いて、SiOx Ny でなる保護膜106、多結晶シリコン膜107を島状にパターニングして、保護膜108、109、半導体層110、111を形成する。(図5(C))

【0088】

先のフォトレジストマスクを剥離した後、フォトレジストを塗布し基板100裏面から露光し、ゲート配線102をマスクにしてフォトレジストマスク112を自己整合的に形成する。フォトレジストマスク112がゲート配線102と同じパターンになるように、露光光量を調節する。そして、フォトレジストマスク112を用いて保護膜108、109をパターニングして、保護膜113、114を形成する。(図5(D))

【0089】

フォトレジストマスク112が存在する状態で、N型を付与する不純物イオンとしてリンイオンをプラズマドーピング法により、半導体層110、111に添加する。半導体層110、111にはN型の不純物領域115S、115D、116S、116Dが形成される。(図5(E))

【0090】

フォトレジストマスク112を剥離した後、再びフォトレジストを塗布し裏面から露光し、ゲート配線102をマスクにしてフォトレジストマスク117を形成する。この場合には、先の裏面露光よりも露光光量を大きくして、即ちオーバー露光して、ゲート配線102の幅よりもマスク112を細らせて、マスク117の側面がゲート配線102の側面よりも内側になるようにする。マスク117のチャネル長方向の幅がTFTのチャネル量を決定し、またマスク117側面がゲート配線102の内側にずれた長さが低濃度不純物領域の長さを決定する。ここでは、1μmほどマスク117が内側にくるようにする。

【0091】

フォトレジストマスク117、保護膜113、114をマスクにして、再びリンイオンを半導体層110、111に添加する。この添加工程では、前回よりも低濃度に添加し、また保護膜113、114をリンイオンが通過するように加速電圧を大きくする。半導体層110、111にN+ 型領域121S、121D、123S、123D、N- 型領域122S、122D、124S、124Dが形成される。(図6(A))

【0092】

半導体層110において、N+ 型領域121S、121Dがソース/ドレイン領域となり、N- 型領域122S、122Dが低濃度不純物領域となる。また2回のリン添加工程で、リンが添加されなかった領域、即ちマスク117に覆われていた領域121Cがチャネル形成領域となる。

【0093】

本実施例では、保護膜113が存在した状態で不純物を添加して、低濃度不純物領域122S、122Dを形成するようにしたため、低濃度不純物領域122S、122Dに添加させるリン濃度の制御が容易である。また、ソース/ドレイン領域121S、121Dには保護膜113が存在していない状態で不純物を添加しているので、高濃度にリンを添加することが容易である。

【0094】

次に、フォトレジストマスク117を残存させたまま、Nチャネル型TFTを覆うフォトレジストマスク125を形成する。フォトレジストマスク117、保護膜114をマスクにして、半導体層111にボロンイオンを添加する。この添加工程で半導体層111に形成されたN型領域の導電型が反転され、ソース/ドレイン領域となるP+ 型領域131S、131Dが形成される。マスク117で覆われた領域131Cはチャネル形成領域となる。(図6(B))

【0095】

なお、ボロン添加工程で、加速電圧、ドーズ量、ドーピング回数等の条件を適宜設定することにより、P+ 型領域131S、131Dのうち保護膜114で覆われている領域のボロン濃度を小さくして、P- 型領域とすることもできる。

【0096】

以上、ソース/ドレイン領域を形成したら、エキシマレーザ光を照射して、添加したリン、ボロンを活性化する。次に、半導体層を覆う層間絶縁膜140を形成する。ここでは、50nm厚のSiNy 膜と、900nm厚のSiO2 膜とでなる積層膜を形成する。SiNy 膜は半導体層に対するパッシベーション膜として機能する。SiO2 膜は段差被覆性のよいTEOSガスを原料にして成膜するとよい。なお、SiO2 膜の代わりに、平坦性の優れたBCB、ポリイミド、アクリルなどの有機樹脂膜や、SOG、PSG、BPSG等の酸化シリコン系の塗布膜で形成してもよい。

【0097】

層間絶縁膜140にコンタクト部145〜149(図4参照)にコンタクトホールを形成し、更に、ゲートコンタクト部149に対してBCB膜103、SiOx Ny 膜104にコンタクトホールを形成する。次に、150nm厚のTi膜/300nm厚のAl膜/100nm厚のTi膜でなる積層膜を形成しパターニングして、配線141〜143及び取出し電極144を形成する。(図6(C))

【0098】

CMOS回路の鎖線C−C’(図4参照)で切った断面図を図6(D)に示す。本実施例では、TFTごとに分断してから(図5(C))、ゲート配線をマスクに用いて自己整合的にパターニングして(図5(D))、保護膜113、114を形成したため、ゲート配線102を共有しているTFTでも、保護膜113、114はTFTで独立している。また、チャネル幅方向の保護膜113、114の長さは半導体層110、111と同じに、即ちチャネル幅と同じになっている。他方チャネル長方向の長さはゲート配線102の幅と同じになっている。

【0099】

本実施例では、ゲート配線102をテーパー状にしたため、実施形態2で述べたようにゲート配線102の傾斜部と平面部ではBCB膜103の膜厚が異なるので、ゲート寄生容量がチャネル形成領域から外側になるほど小さくなる。よって、オフ状態において、チャネル形成領域121C、131Cに印加されている電圧を寄生容量が小さい部分に分散させることができる。特に、Pチャネル型TFTではゲート配線102にオーバーラップしているが、このオーバーラッブ部分の寄生容量はチャネル形成領域131Cよりも小さいため、チャネル形成領域131Cとソース/ドレイン領域131S、131Dの接合部に集中する電圧を緩和することができ、オフ電流を小さくすることができる。

【0100】

[実施例2] 本実施例は実施例1の変形例である。実施例1では、結晶性半導体膜を島状にパターニングした後、ソース/ドレイン領域を形成したが、本実施例の製造工程では、ソース/ドレイン領域を形成した後に、結晶性半導体膜をパターニングする。

【0101】

本実施例を図8、図9を用いて説明する。図8、図9において、図5、図6と同じ符号は同じ構成要素を示す。また、CMOS回路の上面図は図4に対応し、図8、図9の断面図はチャネル長方向に沿った(図4の鎖線A−A’、B−B’)TFTの断面図である。

【0102】

まず、実施例1に示す工程に従って、図5(B)の工程までを行う。そして、フォトレジストを塗布し、基板100裏面から露光して、ゲート配線102をマスクにしてフォトレジストマスク151を自己整合的に形成する。フォトレジストマスク151がゲート配線102と同じパターンになるように露光量を調節する。そして、フォトレジストマスク151を用いてSiOx Ny でなる保護膜106をパターニングし、保護膜152を形成する。(図8(A))

【0103】

なお図8では、保護膜152は分断されているが、保護膜152はゲート配線102と同一パタンであり、2つのTFTで共通である。

【0104】

フォトレジストマスク151、保護膜152をマスクにして、リンイオンをプラズマドーピング法により添加して、多結晶シリコン膜にN型の不純物領域153を選択的に形成する。(図8(B))

【0105】

フォトレジストマスク151を剥離した後、再びフォトレジストを塗布して裏面から露光し、ゲート配線102をマスクにしてフォトレジストマスク155を自己整合的に形成する。この場合には、先の裏面露光よりも露光光量を大きくし、即ちオーバー露光する。即ち、ゲート配線102の幅よりもフォトレジストマスク155を細らせて、マスク155の側面がゲート配線102の側面よりも内側になるようにする。マスク155のチャネル長方向の幅がTFTのチャネル長を決定し、またマスク155側面がゲート配線102の内側にずれた長さが低濃度不純物領域の長さになる。ここでは、1μmほどマスク155側面を内側にずらす。

【0106】

フォトレジストマスク155、保護膜152をマスクにして、再びリンイオンを添加する。この添加工程では、前回よりも低濃度に添加し、また保護膜152をリンイオンが通過するように加速電圧を大きくして、N+ 型領域156、N- 型領域157を多結晶シリコン膜107に形成する。(図8(C))

【0107】

フォトレジストマスク155を残存させたまま、Nチャネル型TFTを覆うフォトレジストマスク160を形成する。フォトレジストマスク155、保護膜152を用いて、多結晶シリコン膜107にボロンイオンを添加する。この添加工程でPチャネル型TFT部のN型領域156、157の導電型が反転され、ソース/ドレイン領域となるP+ 型領域161が形成される。(図8(D))

【0108】

なお、ボロン添加工程で、加速電圧、ドーズ量、ドーピング回数等の条件を適宜設定することにより、P+型領域161のうち保護膜152で覆われている領域のボロン濃度を小さくして、P−型領域とすることもできる。

【0109】

フォトレジストマスク155、160を剥離した後、エキシマレーザ光を照射して、添加したリン、ボロンを活性化する。

【0110】

次に、多結晶シリコン膜107をTFTごとに島状にパターニングして、N型領域、P型領域を分断する。また、このパターニングにより、保護膜152もTFTごとに分断され、保護膜165、166が形成される。

【0111】

Nチャネル型TFTの半導体層には、N+ 型領域156でなるソース/ドレイン領域171S、171Dと、N- 型領域157でなる低濃度不純物領域172S、172Dと、マスク155に覆われていた領域でなるチャネル形成領域171Cとが形成される。他方、Pチャネル型TFTの半導体層には、P+ 型161でなるソース/ドレイン領域181S、181Dと、マスク155で覆われていた領域でなるチャネル形成領域181Cが形成される。(図9(A))

【0112】

次に、半導体層を覆う層間絶縁膜190を形成する。ここでは、50nm厚のSiNy膜と、900nm厚のSiO2膜とでなる積層膜を形成する。層間絶縁膜190にソース/ドレイン領域に対するコンタクトホールと、ゲートコンタクト部に対してコンタクトホールを形成する。更に、ゲートコンタクト部において、SiOxNyでなる絶縁性無機膜104、BCBでなる平坦化膜103をエッチングしてゲート配線102に達するコンタクトホールを形成する。次に、150nm厚のTi膜/300nm厚のAl膜/100nm厚のTi膜でなる積層膜を形成しパターニングして、配線191〜193、及び取出し電極194を形成して、CMOS回路を完成する。(図9(B))

【0113】

図9(B)のチャネル幅方向で切ったNチャネル型TFTの断面図を図9(C)に示す。本実施例の保護膜165、166も実施例1の保護膜113、114と同様に、チャネル幅方向の長さはチャネル幅と同じになっており、チャネル長方向の長さはゲート配線102幅と同じになっている。

【0114】

[実施例3] 本実施例は実施例2の変形例である。実施例2では保護膜152がソース/ドレイン領域上に存在していなく、その上面は露出される。本実施例では、半導体層上面を露出しないようにした例である。また、本実施例では、Nチャネル型TFTのソース/ドレイン領域がゲート配線とオーバーラップしないように製造する工程を示す。このオーバーラップをなくすことにより、TFTの劣化を抑制することができる。

【0115】

本実施例を図10、図11を用いて説明する。まず、実施例1に示す工程に従って、ガラス基板200上に、厚さ200nmのSiO2 でなる下地膜201を形成する。下地膜201表面に500nm厚のCr膜を成膜しテーパー状にエッチングして、ゲート配線202を形成する。なお、本実施例のCMOS回路も図4の上面図に対応し、ゲート配線202は2つのTFTで共通である。

【0116】

次に、スピンコータでBCB溶液を塗布し、溶媒を乾燥させる。そして、窒素雰囲気、250℃でBCB膜203を焼成する。ゲート配線202上のBCBの膜厚は50〜200nmとする。その表面に、厚さ50nmのSiNy 膜204、厚さ50nmの非晶質シリコン膜205、保護膜206として厚さ50nmのSiNy 膜の積層膜を成膜する。

【0117】

本実施例も実施例1と同様に、図7に示す装置を用いて、BCB膜203の焼成工程から、保護膜206の成膜までを大気開放せずに行い、基板表面を大気に曝さないようにする。なお、本実施例では、保護膜206を介して、ソース/ドレイン領域に不純物を添加するため、その膜厚は実施例1、2よりも薄く、10〜60nmが好ましい。(図10(A))

【0118】

非晶質シリコン膜205にKrFエキシマレーザー光を照射して結晶化させて、多結晶シリコン膜207を形成する。照射条件はパルス周波数が30Hz、レーザーエネルギー密度を300mJ/cm2とし、光学系により5mm×12cmの線状に整形して照射する。(図10(B))

【0119】

次にフォトレジストを塗布し、裏面からの露光によりゲート配線202をマスクにして、フォトレジストマスク208を自己整合的に形成する。この場合には、オーバー露光して、ゲート配線202の幅よりもマスク208を細らせて、マスク208側面がゲート配線202の側面よりも内側になるようにする。マスク208のチャネル長方向の幅がTFTのチャネル長を決定し、またマスク208側面がゲート配線202の内側にずれた長さが低濃度不純物領域の長さを決定する。ここでは、1μmほどマスク208側面を内側にシフトさせる。

【0120】

引き続き、Pチャネル型TFT部を覆うフォトレジストマスク209を形成する。そして、リンを多結晶シリコン膜207に添加して、N- 型領域210を形成する。(図10(C))

【0121】

フォトレジストマスク208、209を剥離した後、フォトレジストを塗布し、基板200裏面から再び露光して、ゲート配線202をマスクにしてフォトレジストマスク212を自己整合的に形成する。フォトレジストマスク212がゲート配線202と同じパターンになるように、露光量を調節する。マスク212をもちいて、リンイオンをプラズマドーピング法により添加して、多結晶シリコン膜にN+ 型領域領域213、N型領域領域215を選択的に形成する。(図10(D))

【0122】

次に、フォトレジストマスク212を残存させたまま、Nチャネル型TFTを覆うフォトレジストマスク216を形成する。そして、フォトレジストマスク212を用いて、多結晶シリコン膜207にボロンイオンを添加し、ソース/ドレイン領域となるP+ 型領域217を形成する。(図11(A))

【0123】

フォトレジストマスク212、216を剥離した後、フォトレジストマスクを形成し、これを用いて保護膜206をTFTごとに島状にパターニングして、保護膜235、236を形成する。引き続き同じフォトレジストマスクを用いて多結晶シリコン膜207を島状にパターニングして、N型領域、P型領域を分断する。

【0124】

Nチャネル型TFTの半導体層には、N+ 型領域213でなるソース/ドレイン領域221S、221Dと、N- 型領域210でなる低濃度不純物領域222S、222Dと、マスク208に覆われていた領域でなるチャネル形成領域221Cが形成される。他方、Pチャネル型TFTの半導体層には、P+ 型217でなるソース/ドレイン領域231S、231Dと、マスク208で覆われていた領域でなるチャネル形成領域231Cが形成される。(図11(B))

【0125】

次に、半導体層を覆う層間絶縁膜240を形成する。ここでは、50nm厚のSiNy 膜と、900nm厚のSiO2 膜とでなる積層膜を形成する。層間絶縁膜240にソース/ドレイン領域対するコンタクトホールと、ゲートコンタクト部に対してコンタクトホールを形成する。更に、ゲートコンタクト部において、SiNy 膜204、BCB膜203をエッチングしゲート配線202に達するコンタクトホールを形成する。次に、150nm厚のTi膜/300nm厚のAl膜/100nm厚のTi膜でなる積層膜を形成し、導電膜をパターニングして配線241〜243及び取出し電極244を形成して、CMOS回路を完成する。(図11(C))

【0126】

チャネル幅方向で切ったNチャネル型TFTの断面図を図11(D)に示す。実施例1、2と異なり、本実施例の保護膜235、236は、TFTの島状半導体層と同じパターンになっている。

【0127】

[実施例4] 本実施例では、実施例1で説明したTFTをアクティブマトリクス基板に適用したものである。本実施例のアクティブマトリクス基板は液晶表示装置や、EL表示装置などの平板型の電気光学装置に用いられる。

【0128】

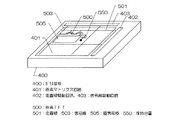

図12〜図14を用いて、本実施例を説明する。図12〜図14で同じ符号は同じ構成要素を示す。図12は本実施例のアクティブマトリクス基板の概略斜視図である。アクティブマトリクス基板は、ガラス基板400上に形成された、画素マトリクス回路401、走査線駆動回路402、信号線駆動回路403で構成される。走査線駆動回路402、信号線駆動回路403はそれぞれ走査線501、信号線503によって画素マトリクス回路401に接続され、これら駆動回路402、403は、CMOS回路で主に構成されている。

【0129】

走査線501は画素マトリクス回路401の行ごとに形成され、信号線503は列ごとに形成されている。走査線501、信号線の交差部近傍には、配線501、503に接続された画素TFT500が形成されている。画素TFT500には画素電極505、コンデンサーである保持容量550が接続されている。

【0130】

まず、実施例1のTFTの製造工程に従って、駆動回路402、403のNチャネル型TFT、Pチャネル型TFT、画素マトリクス回路401の画素TFT500を完成する。

【0131】

図13(A)は画素マトリクス回路401の上面図であり、ほぼ1画素の上面図である。図13(B)は駆動回路402、403を構成するCMOS回路の上面図である。図14はアクティブマトリクス基板の断面図であり、画素マトリクス回路401、CMOS回路の断面図である。画素マトリクス回路401の断面図は図13(A)の鎖線D−D’ に沿った断面図であり、CMOS回路の断面図は図13(B)の鎖線E−E’に沿った断面図である。

【0132】

画素マトリクス回路401の画素TFT500はNチャネル型TFTである。下地膜410上には、第1層目の配線である走査線501、絶縁性有機樹脂膜でなる平坦化膜420、絶縁性無機膜430、「U」字型(馬蹄型)に屈曲した半導体層502がこの順序で積層されている。

【0133】

半導体層502には、N+ 型領域511〜513、2つのチャネル形成領域514、515、低濃度不純物領域(N- 型領域)516〜519が形成されている。N+ 型領域511、512はソース/ドレイン領域である。半導体層502上に保護膜509、510が形成される。

【0134】

CMOS回路においては、平坦化膜420、絶縁性無機膜430を挟んで、1本のゲート配線601が2つの半導体層602、603と交差している。半導体層602には、ソース/ドレイン領域(N+ 型領域)611、612、チャネル形成領域613、低濃度不純物領域(N- 型領域)614、615が形成されている。半導体層603には、ソース/ドレイン領域(P+ 型領域)621、622、チャネル形成領域623が形成されている。

【0135】

半導体層502、602、603にソース/ドレイン領域を形成した後、基板全面に層間絶縁膜440が形成される。層間絶縁膜440上には第2層目の配線・電極として、信号線503、ドレイン電極504、ソース電極631、632、ドレイン電極633が形成される。半導体層602、603上に保護膜609、610が形成される。

【0136】

走査線501と信号線503は層間絶縁膜440を挟んで、図13(A)に示すように直交している。ドレイン電極504はドレイン領域512を画素電極505に接続させるための取出し電極である共に、保持容量550の下部電極である。保持容量550の容量を大きくするため、ドレイン電極504は開口率を低下させない限りにおいて、できるだけ広くなるようにしている。

【0137】

図13(B)に示すように、CMOS回路のドレイン電極633は他のTFTのゲート配線604(第1層目の配線)に接続される。

【0138】

第2層目の配線・電極上に、平坦化膜を有する層間絶縁膜450が形成されている。本実施例では窒化シリコン(50nm)/酸化シリコン(25nm)/アクリル(1μm)の積層膜を層間絶縁膜450として利用する。平坦化膜として、アクリルの他にポリイミド、ベンゾシクロブテン(BCB)を用いることができる。

【0139】

次に、層間絶縁膜450上に、第3層目の配線としてチタンやクロム等の遮光性導電膜でなるソース配線641、ドレイン電極642、ドレイン配線643、ブラックマスク520が形成されている。図13(A)に示すようにブラックマスク520は画素マトリクス回路401で一体であり、画素電極505の周辺とオーバーラップして、表示に寄与しない部分を全て覆うように形成されている。なお、図13(A)に点線で示すようにいる。またブラックマスク520の電位は所定の値に固定される。

【0140】

これら第3層目の配線641、642、520の形成に先立って、層間絶縁膜450をエッチングして、最下層の窒化シリコン膜のみを残した凹部530をドレイン電極504上に形成する。

【0141】

凹部530では、ドレイン電極504とブラックマスク520とが窒化シリコン膜のみを挟んで対向しているので、凹部530おいてドレイン電極504、ブラックマスク520を電極に、窒化シリコン膜を誘電体とする保持容量550が形成される。窒化シリコンは比誘電率が高く、しかも膜厚を薄くすることでより大きな容量を確保できる。

【0142】

第3層目の配線641、642、530上に層間絶縁膜460が形成されている。層間絶縁膜460は1.5μm厚のアクリルで形成する。アクリルの他に、ポリイミドやBCB等の他の平坦化膜で形成してもよい。層間絶縁膜460を平坦化膜で形成することにより、保持容量550のために形成された段差を平坦化できる。

【0143】

層間絶縁膜450、460にコンタクトホールを形成し、ITOや酸化スズ等の透明導電膜からなる画素電極505を形成する。こうしてアクティブマトリクス基板が完成する。

【0144】

本実施例のアクティブマトリクス基板を液晶表示装置に利用する場合には、基板全面を覆って図示しない配向膜を形成する。必要に応じて配向膜にラビング処理が施される

【0145】

なお、画素電極505として反射率の高い導電膜、代表的にはアルミニウムまたはアルミニウムを主成分とする材料を用いれば、反射型AMLCD用のアクティブマトリクス基板を作製することもできる。

【0146】

また、本実施例では画素TFT500をダブルゲート構造としているが、シングルゲート構造でも良いし、トリプルゲート構造等のマルチゲート構造としても構わない。本実施例のアクティブマトリクス基板の構造は本実施例の構造に限定されるものではない。

【0147】

[実施例5] 本実施例では実施例4で示したアクティブ基板を用いた電気光学装置の一例として、アクティブマトリクス方式の液晶表示装置(AMLCDと記す)を構成した例について説明する。

【0148】

本実施例のAMLCDの外観を図15に示す。図15(A)において図12と同じ符号は同じ構成要素を示す。アクティブマトリクス基板は、ガラス基板400上に形成された画素マトリクス回路401、走査線駆動回路402、信号線駆動回路403を有する。

【0149】

アクティブマトリクス基板と対向基板700とが貼り合わされている。これら基板の隙間に液晶が封止されている。ただし、アクティブマトリクス基板には、TFTの製造工程で外部端子が形成されており、この外部端子が形成された部分は対向基板700と対向していない。外部端子にはFPC(フレキシブル・プリント・サーキット)710が接続され、FPC710を介して外部信号、電源が回路401〜403へ伝達される。

【0150】

対向基板700は、ガラス基板上全面にITO膜等の透明導電膜が形成されている。透明導電膜は画素マトリクス回路401の画素電極に対する対向電極であり、画素電極、対向電極間に形成された電界によって液晶材料が駆動される。更に、対向基板700には必要であれば配向膜や、カラーフィルタが形成されている。

【0151】

本実施例のアクティブマトリクス基板には、FPC710を取り付ける面を利用してICチップ711、712が取り付けられている。これらのICチップはビデオ信号の処理回路、タイミングパルス発生回路、γ補正回路、メモリ回路、演算回路などの回路をシリコン基板上に形成して構成される。図15(A)ではICチップを2個取り付けたが、1個でも良いし、3個以上であっても良い。

【0152】

あるいは図15(B)の構成も可能である。図15(B)において図15(A)と同一の構成要素は同じ符号を付した。ここでは図15(A)でICチップが行っていた信号処理を、同一基板上にTFTで構成されたロジック回路720によって行う例を示している。この場合、ロジック回路720も駆動回路402、403と同様にCMOS回路を基本として構成されている。

【0153】

本実施例では、ブラックマスクをアクティブマトリクス基板に設ける構成(BM on TFT)を採用するが、それに加えて対向側にブラックマスクを設ける構成とすることも可能である。

【0154】

また、カラーフィルターを用いてカラー表示を行っても良いし、ECB(電界制御複屈折)モード、GH(ゲストホスト)モードなどで液晶を駆動し、カラーフィルターを用いない構成としても良い。また、特開平8−15686号公報に記載されたように、マイクロレンズアレイを用いる構成にしても良い。

【0155】

[実施例6] 実施例1〜3で示したTFTは、AMLCD以外にも他の様々な電気光学装置や半導体回路に適用することができる。

【0156】

AMLCD以外の電気光学装置としてはEL(エレクトロルミネッセンス)表示装置やイメージセンサ等を挙げることができる。

【0157】

また、半導体回路としては、ICチップで構成されるマイクロプロセッサの様な演算処理回路、携帯機器の入出力信号を扱う高周波モジュール(MMICなど)が挙げられる。

【0158】

この様に本発明は絶縁ゲイト型TFTで構成される回路によって機能する全ての半導体装置に対して適用することが可能である。

【0159】

[実施例7] 実施例5に示したAMLCDは々な電子機器の表示装置として利用できる。本実施例に挙げる電子機器とは、アクティブマトリクス型の表示装置を搭載した製品と定義する。

【0160】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図16及び図17に示す。

【0161】

図16(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示装置2003、キーボード2004で構成される。本願発明を画像入力部2002、表示装置2003やその他の信号制御回路に適用することができる。

【0162】

図16(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明を表示装置2102、音声入力部2103やその他の信号制御回路に適用することができる。

【0163】

図16(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本願発明は表示装置2205やその他の信号制御回路に適用できる。

【0164】

図16(D)はゴーグル型ディスプレイであり、本体2301、表示装置2302、アーム部2303で構成される。本発明は表示装置2302やその他の信号制御回路に適用することができる。

【0165】

図16(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示装置2402、スピーカ部2403、記録媒体2404、操作スイッチ2405で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示装置2402やその他の信号制御回路に適用することができる。

【0166】

図16(F)はデジタルカメラであり、本体2501、表示装置2502、接眼部2503、操作スイッチ2504、受像部(図示しない)で構成される。本願発明を表示装置2502やその他の信号制御回路に適用することができる。

【0167】

図17(A)はフロント型プロジェクターであり、表示装置2601、スクリーン2602で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。

【0168】

図17(B)はリア型プロジェクターであり、本体2701、表示装置2702、ミラー2703、スクリーン2704で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。

【0169】

なお、図17(C)は、図17(A)及び図17(B)中における表示装置2601、2702の構造の一例を示した図である。表示装置2601、2702は、光源光学系2801、ミラー2802、2805〜2807、ダイクロイックミラー2803、2804、光学レンズ2808、2809、2811、液晶表示装置2810、投射光学系2812で構成される。投射光学系2812は、投射レンズを備えた光学系で構成される。本実施例は液晶表示装置2810を三つ使用する三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図17(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0170】

また、図17(D)は、図17(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、光源2813、2814、合成プリズム2815、コリメータレンズ2816、2820、レンズアレイ2817、2818、偏光変換素子2819で構成される。なお、図17(D)に示した光源光学系は光源を2つ用いたが、光源を3〜4つ、あるいはそれ以上用いてもよく、勿論、光源を1つ用いてもよい。また、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等を設けてもよい。

【0171】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1〜6のどのような組み合わせからなる構成を用いても実現することができる。

【0172】

【発明の効果】

本発明では、ゲート絶縁膜を絶縁性有機樹脂でなる平坦化膜と、絶縁性無機膜との積層膜を有し、平坦化膜によってゲート配線12よる段差を埋めているため、平坦な表面を有するゲート絶縁膜を得ることができる。

【0173】

このため、ゲート絶縁膜表面に形成される半導体膜も平坦にすることができるため、レーザ光の焦点のずれが場所ごとに異なることがなくなるため、半導体膜を均一に結晶化することができる。

【0174】

また、ゲート配線の端部で平坦化膜の厚さが薄くなることがないので、ゲート配線と半導体層がショートしたり、ゲート絶縁膜に電子やホールが注入されることでしきい値電圧がシフトしたり、さらにゲート絶縁膜が静電破壊したりすることを防止できる。

【図面の簡単な説明】

【図1】 実施形態1の画素TFTの製造工程を示す断面図。

【図2】 実施形態2の画素TFTの製造工程を示す断面図。

【図3】 図2の製造工程に続く製造工程を示す断面図。

【図4】 実施例1のCMOS回路の上面図。

【図5】 実施例1のCMOS回路の製造工程を示す断面図。

【図6】 図5の製造工程に続く製造工程を示す断面図。

【図7】 実施例1で用いるCVD装置の概略図。

【図8】 実施例2のCMOS回路の製造工程を示す断面図。

【図9】 製造工程を示す断面図。

【図10】 実施例3のCMOS回路の製造工程を示す断面図。

【図11】 図10の製造工程に続く製造工程を示す断面図。

【図12】 実施例4のアクティブマトリクス基板の斜視図。

【図13】 画素マトリクス回路、CMOS回路の上面図。

【図14】 アクティブマトリクス基板の断面図。

【図15】 実施例5のアクティブマトリクス型液晶パネルの断面図。

【図16】 実施例7の電子機器の構成図。

【図17】 実施例7の電子機器の構成図。

【図18】 従来例の逆スタガ型TFTの製造工程を示す断面図。

【符号の説明】

200 基板

201 下地膜

202 ゲート配線

203 BCB膜

204 SiOx Ny 膜

205 非晶質シリコン膜

206 SiOx Ny 膜

207 多結晶シリコン膜[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a method for manufacturing a semiconductor device using a crystalline semiconductor thin film. Note that the semiconductor device of the present invention includes not only a single element such as a thin film transistor but also an electronic device having a semiconductor circuit formed of a thin film transistor, typically a liquid crystal display device using an active matrix substrate, an image sensor, and the like. This category also includes electronic devices such as personal computers and digital cameras equipped with the above.

[0002]

[Prior art]

Thin film transistors (TFTs) are used in various integrated circuits. Since TFTs can be manufactured on insulating substrates such as glass and quartz, they are particularly suitable as switching elements for matrix circuits in active matrix liquid crystal display devices.

[0003]

As the semiconductor layer of the TFT, an amorphous silicon film or a polycrystalline silicon film is generally used. In order to form a driver circuit of a matrix circuit with TFTs, it is necessary to use a polycrystalline silicon film with high mobility as a semiconductor layer. In general, in order to form a polycrystalline silicon film used for a semiconductor layer, an amorphous silicon film is formed, thermal crystallization is performed by heat-treating the amorphous silicon film, or laser crystallization is performed by irradiating an excimer laser beam. Is used.

[0004]

Currently, the upper limit of the crystallization process temperature is required to be about 600 ° C. because of the heat resistance of the glass substrate used for the active matrix substrate. Due to the low temperature of crystallization, it takes 20 hours or more for thermal crystallization.

[0005]

On the other hand, a laser crystallization technique using an excimer laser is one of the techniques that makes it possible to lower the process temperature and shorten the process time. The energy of excimer laser light is absorbed and converted to heat at the extreme surface of amorphous silicon at a depth of about 10 nm, so that it is comparable to thermal annealing at around 1000 ° C. with almost no thermal effect on the substrate. Can be applied to the amorphous silicon film in a short time, and a highly crystalline semiconductor film can be formed.

[0006]

As a TFT structure, a bottom gate type (typically an inverted stagger type) and a top gate type (typically a coplanar type) are typically known. The bottom gate type has a gate wiring (electrode) on the substrate.),The gate insulating film and the semiconductor layer are stacked in this order, and the top gate type is stacked in the order of the semiconductor layer, the gate insulating film, and the gate wiring (electrode).

[0007]

Referring to FIG. 18, a conventional TFT manufacturing process using inverted staggered polycrystalline silicon will be briefly described. FIG. 18 is a cross-sectional view of the TFT along the channel length (gate length).

[0008]

A metal film having a thickness of 300 to 500 nm, such as Cr or Ta, is formed on the

[0009]

Crystallization is performed by irradiating excimer laser light to form a polycrystalline silicon film 5. (Fig. 18B)

[0010]

The polycrystalline silicon film 5 is patterned to form a semiconductor layer 6. Next, an impurity that becomes a donor or an acceptor is selectively added to the semiconductor layer 6 to form a source region 6S, a drain electrode 6D, and a channel formation region 6C. (Figure 18 (C))

[0011]

Next, as the

[0012]

[Problems to be solved by the invention]

As shown in FIG. 18, in the manufacturing process of an inverted stagger type TFT using polycrystalline silicon, the thickness of the gate wiring is about 300 to 500 nm, and the thickness of the gate insulating film is 100 to 200 nm. As shown in FIG. 18A, the surface of the amorphous silicon film 4 has irregularities reflecting the shape of the

[0013]

In general, in laser crystallization, excimer laser light is shaped into a linear beam or a rectangular beam, and this beam is scanned and irradiated. However, due to the height difference of the surface of the

[0014]

In addition, TFTs using polycrystalline silicon have a problem of large off-state current. The cause of off current, TThe reason is that when the FT is in the off state, the voltage applied to the drain electrode 9 is concentrated at the junction between the channel formation region 6C and the drain region 6D, and current flows through the trap at this junction. It has been.

[0015]

Further, in the TFT using polycrystalline silicon, the gate

[0016]

An object of the present invention is to solve the above-described problems, and in a semiconductor device including a bottom gate type semiconductor element in which a gate wiring, a gate insulating film, and a semiconductor layer are stacked in this order, a structure for uniformizing laser crystallization, and It is to provide a manufacturing method thereof. At the same time, it is an object of the present invention to provide a structure of a bottom gate type semiconductor element in which off current is reduced and reliability is improved, and a manufacturing method thereof.

[0017]

[Means for Solving the Problems]

In order to solve the above-described problems, a semiconductor device of the present invention includes a gate electrode formed on an insulating surface, a planarization film formed of an insulating organic resin, and an insulating inorganic film formed to cover the gate electrode. A semiconductor device in which a gate insulating film having a stacked film and a semiconductor layer covering the gate insulating film are stacked, wherein the semiconductor layer is formed of a crystalline semiconductor film.

[0018]

Furthermore, the present invention is a method of manufacturing a semiconductor device having the above laminated structure,

Forming a gate wiring on the insulating surface;

Forming a planarization film made of an insulating organic resin so as to cover the gate wiring;

Forming an insulating inorganic film in contact with the planarization film;

Forming a semiconductor film having an amorphous component so as to cover the insulating inorganic film;

And a step of crystallizing the semiconductor film having an amorphous component to form a crystalline semiconductor film.

[0019]

Note that in this specification, a gate electrode refers to a portion where a gate wiring intersects with a semiconductor layer. The same applies to the relationship between the gate wiring and the gate electrode in the source / drain wiring and the source / drain electrode.

[0020]

In the above structure, the step of the gate electrode and the gate wiring is filled with the planarization film, so that the surface of the gate insulating film becomes flat. Therefore, since the semiconductor film having an amorphous component can be formed over a flat surface, the semiconductor film itself can be formed into a flat film. Therefore, even if crystallization is performed by irradiating with laser light, the focal position does not differ from part to part, so that crystallization can be made more uniform than in the conventional example.

[0021]

Further, the insulating organic resin film can be generally formed by a coating method, and the coating film has a much higher step coverage than the insulating inorganic film formed by the vapor phase method of the CVD method. Therefore, since the insulating resin film does not thin the organic resin film at the end of the gate wiring, the above-described short circuit between the gate wiring and the semiconductor layer and the dielectric breakdown of the gate insulating film can be prevented. The reliability and stability of the device can be improved.

[0022]

In addition, since the organic resin film has a relative dielectric constant smaller than that of the insulating inorganic film, the parasitic capacitance can be reduced even if the gate insulating film is a laminated film.

[0023]

Since the insulating inorganic film is formed by chemical vapor deposition such as CVD or physical vapor deposition such as sputtering, it contains less impurities than the organic resin film, and the size of the impurities is small. By having a laminated film of a resin film and an insulating inorganic film, pinholes in the gate insulating film can be reduced, and the interface between the semiconductor layer and the gate insulating film can be reduced rather than forming a semiconductor layer on the organic resin film. The level can be lowered.

[0024]

NaOh,In the above structure, the semiconductor film having an amorphous component is a non-crystalline semiconductor film having no crystallinity or a semiconductor thin film having crystallinity but having almost no crystal grains on the order of 100 nm or more. Denotes an amorphous semiconductor film or a microcrystalline semiconductor film. A microcrystalline semiconductor film is a semiconductor film in a mixed phase of microcrystals including a crystal grain with a size of several nm to several tens of nm and an amorphous state.

[0025]

More specifically, the semiconductor film having an amorphous component is an amorphous silicon film, a microcrystalline silicon film, an amorphous germanium film, a microcrystalline germanium film, or an amorphous Si film.xGe1-x(0 <x <1), and these semiconductor films are formed by a chemical vapor deposition method such as a plasma CVD method or a low pressure CVD method, or a physical vapor deposition method such as a sputtering method. The thickness of the semiconductor film is about 10 nm to 150 nm.

[0026]

DETAILED DESCRIPTION OF THE INVENTION

The embodiment of the present invention will be described with reference to FIGS. In this embodiment, an inverted stagger type TFT is used as a switching element of a matrix circuit of an active matrix substrate, that is, a so-called pixel TFT.

[0027]

[0028]

As shown in FIG. 1A, a

[0029]

Moreover, when using the back surface exposure process used in the manufacturing process of bottom gate type TFT, the board |

[0030]

The

[0031]

The

[0032]

In the case where the back exposure process is not used, as the

[0033]

A conductive film is formed on the

[0034]

In addition, when the back exposure process used in the manufacturing process of the bottom gate type TFT is used, the gate wiring material is a material having a light shielding property to the light used for the exposure.

[0035]

Next, a

[0036]

The organic resin material used for the

[0037]

As the insulating

[0038]

Since the insulating organic resin film can be formed by a coating method, the step due to the

[0039]

Conventionally, in order to improve the coverage of the gate insulating film, the

[0040]

In addition, since the insulating

[0041]

In the

[0042]

Next, a

[0043]

Next, laser light with a wavelength of 400 nm or less or intense light with a wavelength of 400 nm or less is irradiated to crystallize the

[0044]

An excimer laser can be used as a light source used for crystallization. For example, KrF excimer laser (wavelength 248 nm), XeCl excimer laser (wavelength 308 nm), XeF excimer laser (

[0045]

In the present invention, the

[0046]

Next, the obtained

[0047]

After the patterning step of FIG. 1B, FIG. 1C, or the

[0048]

Note that in this specification, intrinsic refers to a region that does not contain any impurities that can change the Fermi level of silicon. A substantially intrinsic semiconductor is a region in which electrons and holes are completely balanced to cancel the conductivity type, that is, a concentration range in which threshold control is possible (1 × 10 in SIMS analysis).14~ 1x1017atoms / cmThree) Shows a region containing an impurity which imparts a conductivity type which becomes a donor or an acceptor, or a semiconductor whose conductivity type is offset by intentionally adding an impurity of a reverse conductivity type.

[0049]

And the semiconductor layer is made of SiO2

[0050]

In FIG. 1, only the pixel TFTs arranged in one pixel are shown, but in actuality, they are arranged in a matrix on the

[0051]

[0052]

In general, one or more pixel TFTs are formed in one matrix circuit, but it is required to make the characteristics of all the pixel TFTs uniform, in particular, the threshold voltage uniform. One of the major factors that shift the threshold voltage is the interface state between the channel and the gate insulating film.

[0053]

In view of this, in the present embodiment, a manufacturing method is shown in which the interface between the channel formation region of the semiconductor layer and the insulating film in contact with the channel formation region can be kept clean.

[0054]

As in the first embodiment, the substrate 20ThePrepare a

[0055]

Next, the

[0056]

Alternatively, the insulating

[0057]

The thickness of the

[0058]

When the state of FIG. 2B is obtained in this way, the

[0059]

Next, the

[0060]

Note that a step of adding impurities to the

[0061]

Next, a photoresist is applied and exposed from the back surface of the

[0062]

Next, using this

[0063]

After the

[0064]

An impurity which becomes a donor or an acceptor is added through the

[0065]

In this embodiment mode, the effect of reducing off-state current can be further increased by making the TFT have an LDD structure. Further, the

[0066]

In other words, since the

[0067]

With this structure, a larger electric field is applied to the lower gate parasitic capacitance in the off state, so that the electric field concentrated at the end of the

[0068]

Next, SiO2, SiNyOr SiOxNyAn interlayer insulating

[0069]

Further, an

[0070]

【Example】

Hereinafter, examples of the present invention will be described with reference to FIGS.

[0071]

[Embodiment 1] In this embodiment, a manufacturing process for manufacturing a CMOS circuit using an inverted staggered TFT will be described. In this embodiment, the description will be given focusing on one CMOS circuit, but it goes without saying that a plurality of circuits can be formed on the same substrate.

[0072]

The present embodiment will be described with reference to FIGS. FIG. 4 shows a schematic top view of a CMOS circuit. In FIG. 4,

[0073]

The manufacturing process of the TFT will be described with reference to FIGS. In FIGS. 5 and 6, a cross-sectional view of the N-channel TFT is shown on the left side, and a cross-sectional view of the P-channel TFT is shown on the right side. The sectional view of each TFT corresponds to the sectional view taken along the chain line A-A 'and the chain line B-B' in FIG.

[0074]

First, a 1737 glass substrate manufactured by Cornings is used as the

[0075]

Next, a stacked film of a

[0076]

A BCB film is formed as the

[0077]

In this embodiment, the

[0078]

FIG. 7 is a schematic configuration diagram of a CVD apparatus used in this embodiment. 7A is a top view, and FIG. 7B is a cross-sectional view taken along the chain line XX ′ in FIG. 7A.

[0079]

In FIG. 7, 300 is a processing substrate, 301 is a common chamber, 302 and 303 are load lock chambers, 304 to 306 are CVD chambers, and 307 is a heating chamber. The

[0080]

The

[0081]

Each of the

[0082]

The

[0083]

Hereinafter, a method of forming a stacked film of the

[0084]

Here, the

[0085]

As shown in FIG. 5A, the

[0086]

In this embodiment, since the

[0087]

Next, using the same photoresist mask,xNyThe

[0088]

After the previous photoresist mask is peeled off, a photoresist is applied and exposed from the back surface of the

[0089]

In the state where the

[0090]

After the

[0091]

Using the

[0092]

In the

[0093]

In this embodiment, since the low

[0094]

Next, a

[0095]

In the boron addition process, the conditions such as the acceleration voltage, the dose, the number of times of doping, etc. are appropriately set, so that P+Of the

[0096]

When the source / drain regions are formed as described above, excimer laser light is irradiated to activate the added phosphorus and boron. Next, an

[0097]

Contact holes are formed in the

[0098]

A cross-sectional view taken along the chain line C-C '(see FIG. 4) of the CMOS circuit is shown in FIG. In this embodiment, the TFTs are divided for each TFT (FIG. 5C) and then patterned in a self-aligning manner using the gate wiring as a mask (FIG. 5D), so that the

[0099]

In this embodiment, since the

[0100]

Second Embodiment This embodiment is a modification of the first embodiment. In Example 1, the crystalline semiconductor film is patterned into an island shape, and then the source / drain regions are formed. In the manufacturing process of this example, after the source / drain regions are formed, the crystalline semiconductor film is patterned. .

[0101]

This embodiment will be described with reference to FIGS. 8 and 9, the same reference numerals as those in FIGS. 5 and 6 denote the same components. The top view of the CMOS circuit corresponds to FIG. 4, and the cross-sectional views of FIGS. 8 and 9 are cross-sectional views of the TFT along the channel length direction (chain lines AA ′ and BB ′ in FIG. 4). .

[0102]

First, in accordance with the steps shown in Example 1, the steps up to FIG. Then, a photoresist is applied, exposed from the back surface of the

[0103]

In FIG. 8, the

[0104]

Using the

[0105]

After the

[0106]

Using the

[0107]

A

[0108]

In the boron addition process,By appropriately setting conditions such as fast voltage, dose, and number of dopings, P+In the

[0109]

After the photoresist masks 155 and 160 are peeled off, excimer laser light is irradiated to activate the added phosphorus and boron.

[0110]

Next, the

[0111]

The N-channel TFT semiconductor layer has N+Source /

[0112]

Next, an

[0113]

A cross-sectional view of the N-channel TFT cut in the channel width direction of FIG. 9B is shown in FIG. Similarly to the

[0114]

Example 3 This example is a modification of Example 2. In Example 2, the

[0115]

This embodiment will be described with reference to FIGS. First, according to the process shown in Example 1, a SiO2 film having a thickness of 200 nm is formed on a glass substrate 200.2A

[0116]

Next, the BCB solution is applied with a spin coater, and the solvent is dried. Then, the

[0117]

Similarly to Example 1, in this example, the apparatus shown in FIG. 7 was used to perform the steps from the baking step of the

[0118]

The

[0119]

Next, a photoresist is applied, and a

[0120]

Subsequently, a

[0121]

After removing the photoresist masks 208 and 209, a photoresist is applied and exposed again from the back surface of the

[0122]

Next, a

[0123]

After the photoresist masks 212 and 216 are peeled off, a photoresist mask is formed, and the

[0124]

The N-channel TFT semiconductor layer has N+Source /

[0125]

Next, an

[0126]

A cross-sectional view of the N-channel TFT cut in the channel width direction is shown in FIG. Unlike the first and second embodiments, the

[0127]

[Embodiment 4] In this embodiment, the TFT described in

[0128]

The present embodiment will be described with reference to FIGS. 12 to 14, the same reference numerals denote the same components. FIG. 12 is a schematic perspective view of the active matrix substrate of this embodiment. The active matrix substrate includes a

[0129]

The

[0130]

First, in accordance with the TFT manufacturing process of Example 1,Road 4The N-

[0131]

FIG. 13A is a top view of the

[0132]

The

[0133]

The semiconductor layer 502 includes N+Mold regions 511 to 513, two

[0134]

In the CMOS circuit, one

[0135]

After the source / drain regions are formed in the semiconductor layers 502, 602, and 603, an

[0136]

The

[0137]

As shown in FIG. 13B, the

[0138]

An interlayer insulating

[0139]

Next, a

[0140]

Prior to the formation of the third-

[0141]

In the recess 530, the

[0142]

An interlayer insulating

[0143]

Contact holes are formed in the

[0144]

When the active matrix substrate of this embodiment is used for a liquid crystal display device, an alignment film (not shown) is formed so as to cover the entire surface of the substrate. If necessary, the alignment film is rubbed

[0145]

Note that an active matrix substrate for a reflective AMLCD can be manufactured by using a conductive film having a high reflectance, typically aluminum or a material containing aluminum as a main component, as the

[0146]

In this embodiment, the

[0147]

[Embodiment 5] In this embodiment, as an example of an electro-optical device using the active substrate shown in Embodiment 4, an example in which an active matrix liquid crystal display device (referred to as AMLCD) is configured will be described.

[0148]

The appearance of the AMLCD of this example is shown in FIG. 15A, the same reference numerals as those in FIG. 12 denote the same components. The active matrix substrate includes a

[0149]

The active matrix substrate and the

[0150]

In the

[0151]

IC chips 711 and 712 are attached to the active matrix substrate of this embodiment using the surface to which the

[0152]

Or the structure of FIG. 15 (B) is also possible. In FIG. 15B, the same components as those in FIG. Here, an example is shown in which the signal processing performed by the IC chip in FIG. 15A is performed by a logic circuit 720 formed of TFTs on the same substrate. In this case, similarly to the

[0153]

In this embodiment, a configuration in which a black mask is provided on an active matrix substrate (BM on TFT) is adopted, but in addition to this, a configuration in which a black mask is provided on the opposite side may be employed.

[0154]

Further, color display may be performed using a color filter, or the liquid crystal may be driven in an ECB (electric field control birefringence) mode, a GH (guest host) mode, or the like, and the color filter may not be used. Further, as described in JP-A-8-15686, a configuration using a microlens array may be used.

[0155]

[Example 6] The TFTs shown in Examples 1 to 3 can be applied to various other electro-optical devices and semiconductor circuits besides AMLCD.

[0156]

Examples of electro-optical devices other than AMLCDs include EL (electroluminescence) display devices and image sensors.

[0157]

Further, examples of the semiconductor circuit include an arithmetic processing circuit such as a microprocessor constituted by an IC chip, and a high-frequency module (such as MMIC) that handles input / output signals of portable devices.

[0158]

As described above, the present invention can be applied to all semiconductor devices that function by a circuit formed of an insulated gate TFT.

[0159]

[Example 7] The AMLCD shown in Example 5 can be used as a display device of various electronic devices. The electronic device described in this embodiment is defined as a product on which an active matrix display device is mounted.

[0160]

Such electronic devices include video cameras, digital cameras, projectors (rear type or front type), head mounted displays (goggles type displays), car navigation systems, personal computers, personal digital assistants (mobile computers, mobile phones or electronic books). Etc.). Examples of these are shown in FIGS.

[0161]

FIG. 16A illustrates a personal computer, which includes a main body 2001, an image input portion 2002, a display device 2003, and a

[0162]

FIG. 16B shows a video camera, which includes a main body 2101, a display device 2102, an

[0163]

FIG. 16C illustrates a mobile computer, which includes a main body 2201, a camera unit 2202, an

[0164]

FIG. 16D illustrates a goggle type display which includes a

[0165]

FIG. 16E shows a player using a recording medium (hereinafter referred to as a recording medium) on which a program is recorded. The player includes a main body 2401, a

[0166]

FIG. 16F illustrates a digital camera which includes a main body 2501, a

[0167]

FIG. 17A illustrates a front type projector, which includes a

[0168]

FIG. 17B illustrates a rear projector, which includes a main body 2701, a

[0169]

Note that FIG. 17C illustrates an example of the structure of the

[0170]

FIG. 17D illustrates an example of the structure of the light source optical system 2801 in FIG. In this embodiment, the light source optical system 2801 includes light sources 2813 and 2814, a combining prism 2815, collimator lenses 2816 and 2820, lens arrays 2817 and 2818, and a polarization conversion element 2819. Note that although the light source optical system shown in FIG. 17D uses two light sources, three or four or more light sources may be used. Of course, one light source may be used. In addition, the practitioner may appropriately provide an optical lens, a film having a polarization function, a film for adjusting a phase difference, an IR film, and the like in the light source optical system.

[0171]

As described above, the application range of the present invention is extremely wide and can be applied to electronic devices in various fields. Moreover, the electronic apparatus of a present Example is realizable even if it uses the structure which consists of what combination of Examples 1-6.

[0172]

【The invention's effect】

In the present invention, the gate insulating film includes a planarized film made of an insulating organic resin and an insulating inorganic film, and the level difference caused by the

[0173]

For this reason, since the semiconductor film formed on the surface of the gate insulating film can also be flattened, the shift of the focal point of the laser light does not vary from place to place, and the semiconductor film can be crystallized uniformly.

[0174]

Further, since the thickness of the planarization film does not become thin at the edge of the gate wiring, the threshold voltage is increased by short-circuiting the gate wiring and the semiconductor layer or injecting electrons or holes into the gate insulating film. It is possible to prevent shift and further electrostatic breakdown of the gate insulating film.

[Brief description of the drawings]

FIG. 1 is a cross-sectional view showing a manufacturing process of a pixel TFT according to a first embodiment.

FIG. 2 is a cross-sectional view illustrating a manufacturing process of a pixel TFT according to a second embodiment.

3 is a cross-sectional view showing a manufacturing process that follows the manufacturing process of FIG. 2;

4 is a top view of the CMOS circuit of

5 is a cross-sectional view showing a manufacturing step of the CMOS circuit of

6 is a cross-sectional view showing a manufacturing process that follows the manufacturing process of FIG. 5;

7 is a schematic view of a CVD apparatus used in Example 1. FIG.

8 is a cross-sectional view showing a manufacturing step of the CMOS circuit of Example 2. FIG.

FIG. 9 is a cross-sectional view showing a manufacturing process.

10 is a cross-sectional view showing a manufacturing step of the CMOS circuit of

11 is a cross-sectional view showing a manufacturing step that follows the manufacturing step of FIG. 10. FIG.

12 is a perspective view of an active matrix substrate of Example 4. FIG.

FIG. 13 is a top view of a pixel matrix circuit and a CMOS circuit.

FIG. 14 is a cross-sectional view of an active matrix substrate.

15 is a cross-sectional view of an active matrix liquid crystal panel of Example 5. FIG.

FIG. 16 is a configuration diagram of an electronic apparatus according to a seventh embodiment.

FIG. 17 is a configuration diagram of an electronic apparatus according to a seventh embodiment.

FIG. 18 is a cross-sectional view showing a manufacturing process of a conventional inverted stagger type TFT.

[Explanation of symbols]

200 substrates

201 Underlayer

202 Gate wiring

203 BCB film

204 SiOxNyfilm

205 Amorphous silicon film

206 SiOxNyfilm

207 Polycrystalline silicon film

Claims (6)

絶縁表面にゲート配線を形成する工程と、

前記ゲート配線を覆って絶縁性有機樹脂でなる平坦化膜を塗布法で形成する工程と、

前記平坦化膜に接して絶縁性無機膜を形成する工程と、

前記絶縁性無機膜上に非晶質成分を有する半導体膜を形成する工程と、

前記非晶質成分を有する半導体膜に接して保護膜を形成する工程と、

前記非晶質成分を有する半導体膜を、レーザ光により、結晶化して結晶性半導体膜を形成する工程と、

前記保護膜の少なくとも一部を通過させて前記結晶性半導体膜に不純物を添加して、ソース領域、ドレイン領域を形成する工程と、

を有し、

前記絶縁性無機膜、前記非晶質成分を有する半導体膜、及び前記保護膜を、大気開放せずに順次積層して形成することを特徴とする半導体装置の製造方法。In a method for manufacturing a semiconductor device having a circuit using a thin film transistor formed on an insulating surface,

Forming a gate wiring on the insulating surface;

Forming a planarizing film made of an insulating organic resin by covering the gate wiring by a coating method;

Forming an insulating inorganic film in contact with the planarization film;

Forming a semiconductor film having an amorphous component on the insulating inorganic film;

Forming a protective film in contact with the semiconductor film having an amorphous component;

Crystallizing the semiconductor film having the amorphous component with laser light to form a crystalline semiconductor film;

Adding a impurity to the crystalline semiconductor film through at least a part of the protective film to form a source region and a drain region;

Have

A method of manufacturing a semiconductor device, wherein the insulating inorganic film, the semiconductor film having an amorphous component, and the protective film are sequentially stacked without being exposed to the atmosphere.

絶縁表面にテーパーを有するゲート配線を形成する工程と、Forming a gate wiring having a taper on an insulating surface;

前記ゲート配線を覆って絶縁性有機樹脂でなる平坦化膜を塗布法で形成する工程と、Forming a planarizing film made of an insulating organic resin by covering the gate wiring by a coating method;

前記平坦化膜に接して絶縁性無機膜を形成する工程と、Forming an insulating inorganic film in contact with the planarization film;

前記絶縁性無機膜上に非晶質成分を有する半導体膜を形成する工程と、Forming a semiconductor film having an amorphous component on the insulating inorganic film;

前記非晶質成分を有する半導体膜に接して保護膜を形成する工程と、Forming a protective film in contact with the semiconductor film having an amorphous component;

前記非晶質成分を有する半導体膜を、レーザ光により、結晶化して結晶性半導体膜を形成する工程と、Crystallizing the semiconductor film having an amorphous component with laser light to form a crystalline semiconductor film;

前記保護膜の少なくとも一部を通過させて前記結晶性半導体膜に不純物を添加して、ソース領域、ドレイン領域を形成する工程と、Adding a impurity to the crystalline semiconductor film through at least a part of the protective film to form a source region and a drain region;

を有し、Have

前記絶縁性無機膜、前記非晶質成分を有する半導体膜、及び前記保護膜を、大気開放せずに順次積層して形成することを特徴とする半導体装置の製造方法。A method for manufacturing a semiconductor device, wherein the insulating inorganic film, the semiconductor film having an amorphous component, and the protective film are sequentially stacked without being exposed to the atmosphere.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24075899A JP4472064B2 (en) | 1998-08-31 | 1999-08-27 | Manufacturing method of semiconductor device |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24543398 | 1998-08-31 | ||

| JP10-245433 | 1998-08-31 | ||

| JP24075899A JP4472064B2 (en) | 1998-08-31 | 1999-08-27 | Manufacturing method of semiconductor device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000150906A JP2000150906A (en) | 2000-05-30 |

| JP2000150906A5 JP2000150906A5 (en) | 2006-10-05 |

| JP4472064B2 true JP4472064B2 (en) | 2010-06-02 |

Family

ID=26534902

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP24075899A Expired - Fee Related JP4472064B2 (en) | 1998-08-31 | 1999-08-27 | Manufacturing method of semiconductor device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4472064B2 (en) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW504846B (en) * | 2000-06-28 | 2002-10-01 | Semiconductor Energy Lab | Semiconductor device and manufacturing method thereof |

| JP4741569B2 (en) * | 2000-12-21 | 2011-08-03 | 株式会社半導体エネルギー研究所 | Light emitting device |

| SG111923A1 (en) | 2000-12-21 | 2005-06-29 | Semiconductor Energy Lab | Light emitting device and method of manufacturing the same |

| JP4067819B2 (en) * | 2000-12-21 | 2008-03-26 | 株式会社半導体エネルギー研究所 | Light emitting device |

| JP4766758B2 (en) * | 2001-02-28 | 2011-09-07 | 株式会社半導体エネルギー研究所 | Method for manufacturing semiconductor device |

| JP2002289347A (en) * | 2001-03-27 | 2002-10-04 | Sanyo Electric Co Ltd | ELECTROLUMINESCENT DISPLAY, ITS MANUFACTURING METHOD, DEPOSITION MASK, AND ITS MANUFACTURING METHOD |

| JP4731718B2 (en) * | 2001-04-27 | 2011-07-27 | 株式会社半導体エネルギー研究所 | Display device |

| KR20020091705A (en) * | 2001-05-31 | 2002-12-06 | 주식회사 현대 디스플레이 테크놀로지 | Method for manufacturing tft-lcd |

| KR100720099B1 (en) | 2001-06-21 | 2007-05-18 | 삼성전자주식회사 | Thin film transistor substrate and manufacturing method thereof |

| JP2003068757A (en) * | 2001-08-30 | 2003-03-07 | Sony Corp | Active matrix substrate and manufacturing method thereof |

| US7223641B2 (en) | 2004-03-26 | 2007-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, method for manufacturing the same, liquid crystal television and EL television |

| US7491590B2 (en) | 2004-05-28 | 2009-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor in display device |

| JP2006215086A (en) * | 2005-02-01 | 2006-08-17 | Sharp Corp | Active matrix substrate and display device equipped with the same |

| KR100712295B1 (en) | 2005-06-22 | 2007-04-27 | 삼성에스디아이 주식회사 | Organic electroluminescent device and manufacturing method thereof |

| JP4964442B2 (en) * | 2005-08-10 | 2012-06-27 | 三菱電機株式会社 | Thin film transistor and manufacturing method thereof |

| TWI411095B (en) | 2005-09-29 | 2013-10-01 | Semiconductor Energy Lab | Memory device |

| TWI521712B (en) * | 2007-12-03 | 2016-02-11 | 半導體能源研究所股份有限公司 | Thin film transistor, display device including the same, and method of manufacturing the same |

| EP2312620A4 (en) * | 2008-08-04 | 2013-12-25 | Panasonic Corp | FLEXIBLE SEMICONDUCTOR COMPONENT AND MANUFACTURING METHOD THEREFOR |

| CN103151387A (en) | 2009-09-04 | 2013-06-12 | 株式会社半导体能源研究所 | Semiconductor device and method for manufacturing the same |

| JP2011176153A (en) * | 2010-02-25 | 2011-09-08 | Dainippon Printing Co Ltd | Thin film transistor substrate |

| TWI467774B (en) * | 2012-01-19 | 2015-01-01 | E Ink Holdings Inc | Thin-film transistor structure and method for manufacturing the same |

| US9123691B2 (en) | 2012-01-19 | 2015-09-01 | E Ink Holdings Inc. | Thin-film transistor and method for manufacturing the same |

| JP2013250319A (en) * | 2012-05-30 | 2013-12-12 | Sharp Corp | Active matrix substrate, manufacturing method, and display device |

| JP2017136724A (en) * | 2016-02-02 | 2017-08-10 | 東芝テック株式会社 | Inkjet head |

| KR102675575B1 (en) * | 2016-12-12 | 2024-06-18 | 삼성디스플레이 주식회사 | Display device |

| JP6853770B2 (en) * | 2017-11-30 | 2021-03-31 | 株式会社Joled | Semiconductor devices and display devices |

-

1999

- 1999-08-27 JP JP24075899A patent/JP4472064B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000150906A (en) | 2000-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4472064B2 (en) | Manufacturing method of semiconductor device | |

| US6555420B1 (en) | Semiconductor device and process for producing semiconductor device | |

| US6674136B1 (en) | Semiconductor device having driver circuit and pixel section provided over same substrate | |

| JP5298110B2 (en) | Manufacturing method of semiconductor device and semiconductor device | |

| US6359320B1 (en) | Thin-film transistor with lightly-doped drain | |

| US7476937B2 (en) | Semiconductor device and method of fabricating the same | |

| US6677221B2 (en) | Semiconductor device and the fabricating method therefor | |

| US6890840B2 (en) | Method of manufacturing a semiconductor device, utilizing a laser beam for crystallization | |

| US20020163016A1 (en) | Semiconductor device | |

| JP4646368B2 (en) | Method for manufacturing liquid crystal display device | |

| JP4683761B2 (en) | Method for manufacturing semiconductor device | |

| JP4583540B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4094179B2 (en) | Method for manufacturing semiconductor device | |

| US6261971B1 (en) | Method of manufacturing a semiconductor device by thermal oxidation of amorphous semiconductor film | |

| JP5046439B2 (en) | Method for manufacturing semiconductor device | |

| JP4397439B2 (en) | Semiconductor device | |

| JP4357672B2 (en) | Exposure apparatus, exposure method, and manufacturing method of semiconductor device | |

| JP4494451B2 (en) | Method for manufacturing semiconductor device | |

| JP4656685B2 (en) | Semiconductor device | |

| JP2002016015A (en) | Method of manufacturing semiconductor device | |

| JP4597295B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP4637333B2 (en) | Method for manufacturing semiconductor device | |

| JP4583654B2 (en) | Method for manufacturing semiconductor device | |

| JP2000150903A (en) | Semiconductor device provided with semiconductor circuit consisting of semiconductor element and manufacture thereof | |

| JP6466614B2 (en) | Liquid crystal display |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060822 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060822 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100302 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100303 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130312 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130312 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130312 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140312 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |