JP4440552B2 - 電力用半導体装置およびその製造方法 - Google Patents

電力用半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4440552B2 JP4440552B2 JP2003063897A JP2003063897A JP4440552B2 JP 4440552 B2 JP4440552 B2 JP 4440552B2 JP 2003063897 A JP2003063897 A JP 2003063897A JP 2003063897 A JP2003063897 A JP 2003063897A JP 4440552 B2 JP4440552 B2 JP 4440552B2

- Authority

- JP

- Japan

- Prior art keywords

- groove

- type semiconductor

- opening

- conductivity type

- oblique

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

- H10D64/513—Disposition of the gate electrodes, e.g. buried gates within recesses in the substrate, e.g. trench gates, groove gates or buried gates

Landscapes

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

【発明の属する技術分野】

本発明は、電力用半導体装置およびその製造方法、特に、トレンチゲート型MOSゲートデバイスに関するものである。

【0002】

【従来の技術】

大電流を制御する電力用半導体装置は家庭用電化製品から産業用装置の分野まで広く普及している。特に自動車用エレクトロニクスを支える半導体装置として、ABS等の油圧バルブ制御、パワーウインドウ等のモータ制御、さらに電気自動車のバッテリ直流電圧を交流に変換するインバータシステム等多くの部分に使用されている。

【0003】

インバータの高周波化と小型化の要求により、電力用半導体装置のなかでも、高速スイッチングが可能で、しかも電圧駆動であるため駆動回路を低損失にできるという特徴を有するMOS(Metal Oxide Semiconductor)ゲートデバイスが注目されている。MOSゲートデバイスは、電子または正孔どちらか一方がキャリアとして動作するユニポーラデバイスであるMOSFET(Field Effect Transistor)と、電子と正孔がともにキャリアとして動作するバイポーラデバイスであるIGBT(Insulated Gate Bipolor Transistor)とに大別できる。MOS FETは少数キャリアの蓄積がないため、特に高速性に優れている。

【0004】

電力用半導体装置に要求されている課題として、無効電力削減のためのオン抵抗の低減と、信頼性向上のための耐圧の向上がある。オン抵抗とはMOS FETの最も重要な特性の一つで、ドレインからソースまで、ドレイン電流が流れる素子内のすべての経路を通じた抵抗値を言い、主にチャネル領域の抵抗(チャネル抵抗)に支配されている。一方、耐圧とはドレイン−ソース間の耐圧を言い、オン抵抗とはトレードオフの関係にあることが知られている。

【0005】

チャネル抵抗を下げるために、半導体表面に狭く、深い溝(トレンチ)を掘って、その側面にゲートを形成するトレンチゲート構造が開発された。これにより電流経路がトレンチ側壁に3次元的に拡大したことで、飛躍的な低オン抵抗が実現できた。さらに、微細加工技術を用いて単位面積あたりのゲート(セル)の集積度を上げることにより、低オン抵抗化が進められてきた。(例えば特許文献1参照。)。

【0006】

そのような微細加工を行う方法としては、ドライエッチング法が一般的に用いられている。ドライエッチング法とは、液体の薬品を使わずにエッチングを行うものである。代表的な例としてはRIE(Reactive Ion Etching:反応性イオンエッチング)法がある。これは半導体表面にイオンを衝突させて、エッチングマスクに覆われていない部分を削り取る方法である。一般にドライエッチング法は異方性を有し、一方向のみにエッチングが進むため、微細な形状の形成に適している。

【0007】

また、ドライエッチング法により、トレンチを所望の方向に傾斜した形状で形成する方法として、エッチングマスクにテーパーを付けることにより、ドライエッチングの進行方向を傾けるという方法があった(例えば特許文献2参照。)。

【0008】

【特許文献1】

特開平9−266309号公報

【特許文献2】

特開平5−29283号公報

【0009】

【発明が解決しようとする課題】

半導体微細加工を実現させるための最も重要な工程であるパターン転写を行う露光装置においては、パターン転写に必要な解像度によって、装置の構成が大きく異なる。用いる光源の波長により、解像度限界が決まるためである。例えば、最小パターン寸法が0.5μm程度までであれば、波長365nmの水銀灯i線による露光で転写ができるが、それ以下の最小パターン寸法が必要な場合、更に波長の短い光の光源であるArFエキシマレーザやKrFエキシマレーザ等を用いる必要がある。水銀灯光源は比較的安価であるが、エキシマレーザ等波長の短い光の光源は非常に高価である。また、露光装置全体としても高い精度を実現させるための構成が高度となるため、露光装置は解像度が高いものほど、価格は飛躍的に高くなる。さらに、それらの装置の能力を発揮させるために、解像度に応じた設置環境や整備環境を整える必要があるため、装置本体以外に付加的なコストも必要な解像度に応じて増大する。

【0010】

したがって、従来の方法によるゲート集積度の向上に頼ったオン抵抗低減化は、生産コストの増大につながってしまうという問題があった。

【0011】

一方、トレンチの形成方法としても、高度な微細パターンによらず、実効的にチャネル抵抗の低減が可能となるゲート構造を実現させるエッチング方法が望まれていた。

【0012】

本発明は、オン抵抗が低くかつ耐圧の高いパワーMOS FETを低コストで実現できる素子構造とその作製方法の提供を目的とする。

【0013】

【課題を解決するための手段】

本発明の電力用半導体装置の特徴は、溝の中にゲート絶縁膜を介して埋め込まれたゲート電極を備えた電力用半導体装置において、溝は半導体表面において一つの開口を有し、その開口から鉛直方向に延びる鉛直溝と、その開口から前記鉛直溝と異なる方向に延びる一つ以上の斜方溝と、から構成され、前記斜方溝の両側のソース領域は、連接していることである。

【0014】

また、本発明の電力用半導体装置の特徴は、半導体基板に形成された第一導電型の半導体層と、この第一導電型の半導体層の表面に形成された第二導電型の半導体層と、この第二導電型の半導体層の表面部に形成された第一導電型の半導体領域と、第一導電型の半導体領域及び第二導電型の半導体層を貫き前記第一導電型の半導体層に達するように形成された溝と、この溝の中にゲート絶縁膜を介して埋め込まれたゲート電極と、を備えた電力用半導体装置において、溝は第一導電型の半導体領域表面において一つの開口を有し、その開口から鉛直方向に延びる鉛直溝と、その開口から前記鉛直溝と異なる方向に延びる一つ以上の斜方溝と、から構成され、斜方溝の両側の第一の導電型の半導体領域は連接していることである。

【0015】

これら構成によれば、従来の構成に比べ、エッチングマスクの開口パターンの集積度に対して、単位体積あたりに広い表面積のゲート溝が形成され、かつ、ゲートの全ての面の近傍をキャリアの経路として働かせることができる。すなわち、エッチングマスクの開口パターンの露光に高い解像度を必要とすること無しに低いオン抵抗を実現できる。

【0016】

また、この電力用半導体装置の、鉛直溝および前記斜方溝は平板状の溝であることが望ましい。

【0017】

この場合、溝の形成は、ドライエッチング装置のエッチング進行方向に対して、ウエハを置く角度を変えるだけで実現することができる。

【0018】

また、この電力用半導体装置の鉛直溝と前記斜方溝に挟まれた第一の導電型の半導体領域を、斜方溝の外側の第一導電型の半導体領域と連接させるために、溝の半導体表面の前記斜方溝の延設方向に沿った開口部長さに比べてその開口部から延びる前記斜方溝の延設方向に沿った長さが短いことも好ましい。

【0019】

この場合はゲートの全ての面の近傍をキャリアの経路として働かせることができる。

【0020】

さらに、この電力用半導体装置の溝の半導体表面の開口は略円形であり、斜方溝は開口部を頂点とする円錐形状の一部をなす形状であって、前記円錐形状の斜方溝と鉛直溝とに挟まれた第一の導電型の半導体領域が斜方溝の外側の第一導電型の半導体領域と連接するように、切り欠きを備えることを特徴とする。

【0021】

この構造によれば、単位体積あたりにより広い表面積のゲート電極を形成することができる。

【0022】

さらに、第二導電型の半導体層の表面部に形成された第一導電型の半導体領域は、半導体層表面において、高濃度にドーピングした第二の伝導型の半導体領域に囲まれていることも望ましい。

【0023】

この高濃度にドーピングした第二の伝導型の半導体領域から電気的配線をとることにより、ボディ層の電位を安定化することができ、安定した高周波スイッチングが可能となる。

【0024】

また、本発明はエッチングマスクパターンを配した半導体板にドライエッチング法を用いてエッチングをする方法において、エッチング進行方向に対して前記半導体表面を垂直に配置して第一のエッチングを行い、エッチング進行方向に対して前記半導体板表面を垂直以外の角度に配置して第二のエッチングを行い、前記半導体表面の一つの開口から、複数の異なる方向へ延びる溝を形成するエッチング方法である。

【0025】

この方法によれば、一つの開口から、複数の溝を容易に形成することができる。

【0026】

また、本発明のエッチング方法はエッチングマスクパターンの開口は略円形であって、前記第二のエッチングにおいて、エッチング進行中に、前記半導体板を半導体表面がエッチング進行方向と成す角度を保持しながらエッチング進行方向を軸として回転させることを特徴とする。

【0027】

この方法によれば、エッチングマスクパターンの開口部を頂とした円錐形状の一部をなす溝を形成することができる。

【0028】

さらに、このエッチング方法はエッチング進行方向を軸とした回転は360度未満であることが望ましい。

【0029】

それにより、エッチングされる溝は前記エッチングマスクパターンの開口部を頂とした円錐から一部を欠いた形状とすることができる。この場合、斜方溝の両側のソース領域は連接するので、ゲートの全ての面の近傍をキャリアの経路として働かせることができる。

【0030】

さらに、これらのエッチング方法によって溝を形成した後、溝の入口部を広げるためのエッチングを行うことを特徴とする。

【0031】

入口部を広げることにより、後続工程において、溝の奥にまでポリシリコンを埋め込むことが容易にできる。

【0032】

【発明の実施の形態】

実施形態1.

[デバイスの構造]

図1は本発明にかかるMOS FET100の断面図である。シリコンからなるn+半導体基板(ドレイン層)2にn-半導体層(ドリフト層)3、p-半導体層(ボディ層)4が順に積層されており、p-型半導体層4の表面にはn+半導体領域(ソース領域)5(5a,5b,5c,5d)が形成されている。そして、n+型半導体領域5表面から、n+型半導体領域5及びp-型半導体層4を貫きn-型半導体層3に達するように形成された3本の平板状の溝(トレンチ)10a,10b,10cが形成されており、溝内にはゲート絶縁膜20(20a,20b,20c)を介してゲート電極30が設けられている。3本の溝10a,10b,10cのn+型半導体領域5の表面における開口80は一つであり、溝10aは開口80から鉛直に、溝10b,10cはそれぞれ鉛直とは異なる方向に延びている。n+型半導体領域5に接続されるようにAlを用いたソース電極50が形成されている。ゲート電極30とソース電極50の間には絶縁のための層間膜45が挟まれている。n+型半導体基板2の裏面にはドレイン電極51が形成されている。

【0033】

ソース電極50はAlの代わりに電気伝導率のよい他の金属を用いても良い。例えば、CuやAuやPtを用いても良い。

【0034】

ソース領域5a,5b,5c,5dは互いに連接するようにソース領域と溝10a,10b,10cが配置されている。この関係をソース領域と溝の底部との配置を上視した図2で説明する。

【0035】

図2(a)のようにソース領域5全体を3本の溝が縦断する配置とした場合、図1におけるソース領域5a,5bは溝10bおよび10cによって、ソース電極と接続されたソース領域5c,5dと分断されてしまう。したがって、ソース領域5a,5bにはソース電極からの電子の供給が行われないため、ゲートとなる鉛直溝10aの両面および斜方溝10b,10cの内側のボディ層4は電子の経路とは成りえない。電子の経路は斜方溝10b,10cの外側の2面のみであるから、ゲートとなる溝が一本である従来構造と比べて、ボディ層4内の電子の経路の密度は同じであるから、チャネル抵抗の低減は果たせないことになる。

【0036】

一方、例えば、図2(b)のようにソース領域5の縁部で斜方溝10b,10cを形成しない構造の場合、および、(c)のようにソース領域5内で斜方溝10b,10cが分断されている場合は、溝を横断する断面は斜方溝10b,10cの形成されたA−A断面部と鉛直溝10aのみ形成されたB−B断面部とを有する。図3(a)にA−A断面部の溝配置を、図3(b)にB−B断面部の溝配置を示す。B−B断面部ではソース領域5が分断されていないため、ソース領域全域にソース電極50から電子を供給することができる。したがって、A−A断面部の斜方溝10b,10cの内側のソース領域5a,5bにはB−B断面部を通じてソース電極50から電子を供給することができるので、ボディ層4内の三本の溝に形成されるゲート電極の全ての面の近傍に電子の経路が形成され、チャネル抵抗の低減が可能となる。

【0037】

また、半導体各層、領域の導電型はそれぞれ逆の導電型でも良い。例えば、ドレイン領域、ドリフト領域およびソース領域がp型であり、ボディ領域がn型でもよい。その場合、キャリアはホールとなる。さらに本実施例では半導体としてシリコンを用いたが、化合物半導体を用いることも可能である。

【0038】

図4に示すように、n+型ソース領域5は、半導体層表面において、高濃度にドーピングしたp+型の半導体領域(コンタクトp領域)に囲まれていることも望ましい。このコンタクトp領域に電気的接続をし、その電位を制御することにより、ボディ層4の電位が安定化でき、安定した高周波スイッチングが可能となる。

【0039】

[デバイスの動作]

次に図1を用いて、MOS FET100のオン動作を説明する。まず、ドレイン電極51に正電圧(n+型ドレイン層2に正電圧)、例えば、2Vを印加し、ソース電極50を接地(n+型ソース領域5を接地)させる。この状態において、ゲート電極30に正電圧、例えば、5Vを印加すると、p-型ボディ層4中の電子は、鉛直溝10a、および斜方溝10b,10c,10dの中に埋め込まれたゲート電極30に引き寄せられ、鉛直溝10a、および斜方溝10b,10c,10dの近傍領域にn型のチャネルが形成される。これにより、ソース電極50から供給された電子は、n+型ソース領域5c,5dおよび5a,5bからn型チャネル,n-型ドリフト層3,n+型ドレイン層2を通り、ドレイン電極51に到達する。すなわち、MOS FET100は、n+型ドレイン層2からn+型ソース領域5へ電流を流す動作をする。このとき、ソース領域5a,5bはソース電極と接続されたソース領域5c,5dと連接しているため、ソース電極50からの電子の供給を受けることができる。したがって、図1に示すようにボディ層4において、3本のゲートの近傍全てが電子の経路200となる。電子の経路200は、従来構造では溝開口につき一本のゲートの両面に形成される2面のみであったが、本実施例では3本のゲートそれぞれの両面に形成されるため、チャネル抵抗は1/3に低減できることになる。

【0040】

次にオン抵抗を具体的に計算して説明する。一般に、MOS FETのオン抵抗に占めるチャネル抵抗の比率はその耐圧によって異なり、耐圧20Vクラスで、約70%、100Vクラスで約30%である。したがって、従来の構造においてオン抵抗が100mΩ・mm2の耐圧100VクラスのMOS FETではチャネル抵抗は30mΩ・mm2程度であった。これに今回の発明を適用すると、チャネル抵抗は10mΩ・mm2程度になるため、オン抵抗は80mΩ・mm2に低減できることになる。また、従来の構造においてオン抵抗が100mΩ・mm2であって、チャネル抵抗の占める割合が60%とした場合には、今回の発明を適用するとチャネル抵抗は60mΩ・mm2から20mΩ・mm2とできるので、オン抵抗は60mΩ・mm2に低減できることになる。これにより、消費電力を下げることが可能となる。

【0041】

また、本発明の構造によれば、半導体層の単位体積当たりのゲート底面積が上がるため、電界集中が緩和する。したがって、従来構造に比べて高い耐圧を得ることができる。

【0042】

A−A断面領域とB−B断面領域の配置について説明する。ソース領域を導電するためのソース抵抗がオン抵抗に占める割合は、チャネル抵抗と比べて小さい。しかしながら、低オン抵抗化を更に進めるためにはA−A断面領域とB−B断面領域の配置を検討することが重要である。一般にn+ソース領域のシート抵抗は約100Ω/cm2程度である。n+ソースの配線幅を0.5μmとすると、配線長10μmでは配線抵抗は約20-2mΩとなる。したがって、素子全体の抵抗値との比較により、A−A断面領域の領域長は10〜20μmとするのが好ましい。一方、B−B領域長はフォトリソグラフィーによるパターン転写時の合わせ精度、転写の解像度より、0.5μm程度が好ましい。

【0043】

[デバイスの製造方法]

次に図4に示すMOS FET101(MOS FET100にコンタクトp領域を備えた)の製造工程を説明する。図5から図10はこれを説明するための工程図である。

【0044】

図5(a)に示すように、n+型半導体基板2の素子周辺領域に、素子周辺領域での電界集中を防ぐためのフィールドプレート(図示せず)を形成する。次に、たとえばエピタキシャル成長で、n-型半導体層3とp-型半導体層4を積層する。n-型半導体層3はドリフト層となる。p-型半導体層4はボディ層となる。

【0045】

次に図5(b)に示すように、ソース領域5を形成する。p-型半導体層4の表面にフォトリソグラフィー法を用いてソース領域パターンマスクを形成し、イオン注入法により、マスク開口部に選択的にイオンを注入した後、拡散してn型のソース領域5を形成する。

【0046】

次の溝の形成から、ゲート電極30形成までの工程は図3のA−A断面を有する領域とB−B断面を有する領域と分けて行う。どちらの領域を先に行っても構わないが、ここでは先にB−B断面を有する領域を形成する例を図6を用いて説明する。

【0047】

まず、p-型半導体層4を貫通しn-型半導体層3まで到達する溝(トレンチ)10を形成する。エピタキシャル成長を行った半導体基板1の表面の全面にHTOCVD(高温酸化膜化学気相堆積)法によりHTO(高温酸化)膜60を形成した後、アニールを行う。この表面にB−B領域の開口パターンのフォトリソグラフィー、HTO膜エッチングを行い、HTO膜60にB−B断面領域のトレンチ溝開口70のパターンを形成する(図6(a))。

【0048】

CF系およびHBr系ガス等を用いたRIE(反応性イオンエッチング装置)などの異方性ドライエッチングによりB−B断面領域に鉛直溝を形成する。図6(b)に示すように、エッチングの進行方向に対し、半導体基板1の表面を垂直に設置してエッチングを行うと、エッチングマスク開口70から、鉛直方向のみにエッチングが進行し、鉛直溝10aが形成される。エッチングはn-型半導体層3に達する深さまで進行させた後停止する。そしてHTO膜60を除去する。

【0049】

次にトレンチ内壁にゲート絶縁膜を形成する。半導体基板全面を熱酸化してトレンチ内壁に厚さ数百Åのゲート絶縁膜20aを形成する(図6(C))。そして、図6(d)に示すようにCVD法により、全面にポリシリコン層25を溝を埋めるように堆積させ、リンを高濃度に注入・拡散して高導電率化を図る。

【0050】

その後、図6(e)に示すように、全面に付着したポリシリコン層25をマスクなしでエッチングして、平坦化する。このときのエッチングはHTO膜は残し、ポリシリコンのみエッチングさせるため、HTOとポリシリコンのエッチング選択比の大きいドライエッチング法が望ましい。このトレンチ溝に埋設されたポリシリコンをゲート電極30とする。

【0051】

次にA−A断面領域の溝の形成から、ゲート電極形成までの工程を行う。その工程を図7および図8を用いて説明する。エピタキシャル成長を行った半導体基板1表面の全面にHTOCVD法によりHTO(高温酸化)膜61を形成した後、アニールを行う。この表面にA−A断面領域の開口パターンのフォトリソグラフィー、HTO膜エッチングを行い、HTO膜61にA−A領域のトレンチ溝開口71のパターンを形成する(図7(a))。

【0052】

CF系およびHBr系ガス等を用いたRIEなどの異方性ドライエッチングによりA−A断面領域に鉛直溝10aを形成する。図7(b)に示すように、エッチングの進行方向に対し、基板表面を垂直に設置し、エッチングを行う。エッチングはエッチングマスク開口71の開口形状を保って進行し、鉛直溝10aが形成される。エッチングはn-型半導体層3に達する深さまで進行させた後停止する。

【0053】

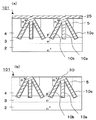

次に同じく、RIE等の異方性ドライエッチング装置により、斜方溝10bおよび10cを形成する。鉛直溝10aのエッチングに用いたHTO膜61はそのまま利用する。図7(c)に示すように、エッチング装置のチャンバ内において、エッチングの進行方向に対し、半導体基板1の垂直方向を傾けて設置する。エッチングは半導体基板1に対して傾いた方向に進行するため、鉛直溝10aとは設置角度だけ傾いた斜方溝10bが形成される。エッチングはn-型半導体層3に達する深さまで進行させた後停止する。

【0054】

更に引き続き、もう一本の斜方溝を形成する。ここでも鉛直溝10aのエッチングに用いたエッチングマスクであるHTO膜61はそのまま利用する。図7(d)に示すように、基板表面とエッチング進行方向が成す角度を、一回目の斜方溝のエッチングの時と異なるようにエッチング装置のチャンバ内において、傾けて設置する。エッチングは半導体基板1に対して傾いた方向に進行するため、鉛直溝とは設置角度だけ傾いた斜方溝10cが形成される。エッチングはn-型半導体層3に達する深さまで進行させた後停止する。最後にエッチングマスクとして用いたHTO膜61を除去する。

【0055】

次に図8(a)に示す、溝10a,10b,10c内壁にゲート絶縁膜を形成する。半導体基板全面を熱酸化して溝内壁に厚さ数百Åのゲート絶縁膜20を形成する(図8(b))。そして、図9(a)に示すようにCVD法により溝を埋めるように全面にポリシリコン層25を堆積させ、リンを高濃度に注入・拡散して高導電率化を図る。

【0056】

このとき、溝の入口部近傍に酸化膜が速い速度で堆積し、溝が詰まってしまうことのないように、斜方溝10b,10cのエッチング後に溝の入口部を広げるエッチングを行うことも好ましい。すなわち、エッチング完了後の溝の入口部の幅をW、溝の幅をW0とすると、W>W0とすることが好ましい。そのエッチング工程を図10を用いて説明する。

【0057】

基板表面の全面にHTOCVD法によりHTO(高温酸化)膜62を形成した後、アニールを行う。この溝開口を拡大させるパターンのフォトリソグラフィー、HTO膜エッチングを行い、HTO膜62に開口幅W1(W1>W0)の開口パターンを形成する(図10(a))。

【0058】

そのパターン化されたHTO膜62を用いて、RIE法等のドライエッチング法により、エッチングを行う。エッチングにより、図10(b)に示すように、溝の入口の幅はW1(W1>W0)と広くすることができる。このような溝形状であれば、ポリシリコン膜の堆積を容易に溝の奥にまですることが可能になる。

【0059】

その後、図9(a)に示すように全面に付着したポリシリコン層25をマスクなしでエッチングを行い、図9(b)のように平坦化する。このときのエッチングではHTO膜は残し、ポリシリコンのみエッチングさせるため、HTOとポリシリコンのエッチング選択比の大きいドライエッチング法が望ましい。このトレンチ溝に埋設されたポリシリコンをゲート電極30とする。以上により、A−A断面領域、B−B断面領域に分けた工程は終了する。なお、上記の工程ではエッチングマスクとしてHTO膜を用いたが、RIE法等のドライエッチングにおいて、GaAsとエッチング選択比のとれる膜であれば、HTO膜に限らず用いることが可能である。

【0060】

以降は一般的なMOS FETの作製プロセスと同様である。

【0061】

すなわち、まず、トレンチ間のチャネル領域を除いてレジスト膜の開口を形成し、選択的にイオン注入によって、p+型半導体領域(コンタクトp領域)6を形成する。次に、ゲート電極30上に層間絶縁膜45を形成する。さらに、コンタクトp領域6と外部配線とを接続するために、層間絶縁膜45にコンタクトホールを形成する。引き続き、ソース電極50の形成を行う。バリアメタルスパッタの後、アルミスパッタを行い、ソース電極50とする。次に外部との電気的配線をするためのボンディングパッドの形成を行う。前面にパッシベーション膜を形成した後、パッドパターンのフォトリソグラフィー法によるパターン転写を行った後、ドライエッチング法により、パッドパターンを形成する。さらにポリイミド膜もフォトリソグラフィー法によりパッドパターンに形成する。そして、Auなどのボンディングパッド用配線(図示せず)を形成する。最後に裏面加工を行う。すなわち、裏面研磨、ドレイン電極51の形成を行う。

【0062】

本発明の溝のエッチング方法によれば、溝開口部のエッチングマスクは例えば、水銀ランプのi線を光源とした露光機で解像できる程度の微細パターンであっても、従来の方法では、エキシマレーザを光源とした露光機でないと実現できなかった密度のトレンチゲートを形成することが可能となる。すなわち、低コストでオン抵抗が低くかつ耐圧が高いMOS FETを作製することができる。

【0063】

また、本実施例では斜方溝は二本としたが、一本以上であれば何本でも良い。従来構造と比べゲートの数が増えることになるので、オン抵抗低減することができる。

【0064】

以上はMOS FETの作製プロセスを例に説明したが、トレンチ構造のMOSゲートを有するデバイス、例えば、IGBT(Insulated Gate Bipolor Transistor)などにも用いることができる。

【0065】

実施形態2.

[デバイスの構造]

実施形態2にかかるMOS FET102の構造は実施形態1にかかるMOSFET101と比べて、溝の構造が異なっている。図11(a)および(b)は本発明の実施形態2にかかるMOS FET102の溝底部の配置を示す上面視図およびそのC−C断面図である。n+型ソース領域5表面には略円形の開口81があり、n+型ソース領域5及びp-半導体層層(ボディ層)4を貫きn-半導体層層(ドリフト層)3に達するように延びた円柱状の鉛直溝11と、同じ開口81から延びた、開口部を頂点とする円錐形状の一部をなす形状の斜方溝21が形成されている。これらの溝の中にゲート絶縁膜を介してゲート電極(図示せず)が形成されている。また、各ゲート電極間は上層配線26によって相互に接続されており、チップ上の各ゲートは同一の電位で動作される。

【0066】

[デバイスの動作]

斜方溝21の円錐形状には切り欠き22があるため、斜方溝21と鉛直溝11とに挟まれたソース領域5a,5bは斜方溝21の外側のソース領域5c,5dと連接している。この構造によれば、ソース領域5a,5bにもソース電極から電子を供給することができる。したがって、ボディ層4の中で円錐形状の鉛直溝11のゲートと、円錐形状の一部を成す斜方溝21のゲートの近傍の全てが電子を流す経路となるため、従来構造に比べ、電流が流れる経路の密度が高くなる。したがって、チャネル抵抗が下がり、オン抵抗を低減することができる。

【0067】

また、本発明の構造によれば、ゲートの密度が上がるため、電界集中が緩和する。したがって、従来構造に比べて高い耐圧を得ることができる。

【0068】

[デバイスの製造方法]

実施形態2にかかる溝の形成方法は実施形態1にかかる方法と比べて、マスクの開口形状とエッチング方法が異なっている。本発明の実施形態2にかかる溝の形成方法を図12を用いて具体的に説明する。

【0069】

エピタキシャル成長を行った半導体基板1の表面の全面にHTOCVD法によりHTO膜63を形成した後、アニールを行う。この表面に溝開口パターンのフォトリソグラフィー、HTO膜エッチングを行い、HTO膜63に略円形のトレンチ溝開口73のパターンを形成する(図12(a))。

【0070】

まず、鉛直溝を形成する。CF系およびHBr系ガス等を用いたRIEなどの異方性ドライエッチング装置において、図12(b)に示すように、エッチングの進行方向に対し、半導体基板1表面を垂直に設置し、エッチングを行う。エッチングはエッチングマスクであるHTO膜63の略円形の開口73の形状を保って進行し、円柱形状の鉛直溝11が形成される。エッチングはn-型半導体層3に達する深さまで進行させた後停止する。

【0071】

次に、円錐形状の斜方溝を形成する。エッチングマスクとして用いたHTO膜63は除去せず、そのまま用いて、CF系およびHBr系ガス等を用いたRIEなどの異方性ドライエッチング装置により、再度エッチングを行う。この時、図12(c)に示すように、エッチング進行方向に対して、半導体基板表面を垂直から傾けて配置する。そして、エッチング進行中に、半導体基板を表面がエッチング進行方向と成す角度を保持しながら半導体基板に垂直な方向を軸として回転させる。エッチングは常に一方向にのみ進行するので、半導体基板の回転によって、略円形のエッチングマスク開口73を頂とした円錐形状の一部をなす溝12を形成することができる。基板の回転速度を一定とすると、エッチング中に基板を一回転すれば、溝はつながり円錐形状となる。溝を円錐形状に切り欠きを入れた形状にする場合はエッチング中の基板の回転を360度(一回転)未満とすればよい。

【0072】

本発明の溝のエッチング方法によれば、溝開口部のエッチングマスクは例えば、水銀ランプのi線を光源とした露光機で解像できる程度の微細パターンであっても、従来の方法では、エキシマレーザを光源とした露光機でないと実現できなかった密度のトレンチゲートを形成することが可能となる。すなわち、低コストでオン抵抗が低くかつ耐圧が高いMOS FETを作製することができる。

【0073】

また、本実施例では斜方溝は一つの円錐形状としたが、一つの開口から頂角を変えた複数の円錐の重なった形状とすることもできる。それぞれの溝が円錐形状のゲートとなり、キャリアの経路が増加することになるので、さらに、オン抵抗を低減することができる。

【0074】

以上はMOS FETの作製プロセスを例に説明したが、トレンチ構造のMOSゲートを有するデバイス、例えば、IGBT(Insulated Gate Bipolor Transistor)などにも用いることができる。

【0075】

以上、本発明の実施の形態について実施例を用いて説明したが、本発明はこうした実施例に何等限定されるものではなく、本発明の要旨を逸脱しない範囲内において、種々な形態で実施することができる。

【図面の簡単な説明】

【図1】 本発明にかかるMOS FETの断面構造とオン動作時の電子の経路を示す。

【図2】 本発明にかかるMOS FETのソース領域と溝の底部との配置を上視した図である。

【図3】 本発明にかかるMOS FETのA−A断面とB−B断面を示す図である。

【図4】 本発明にかかる実施形態1のMOS FET101の断面構造を示す図である。

【図5】 本発明にかかる実施形態1のMOS FET101の作製方法を示す図である。

【図6】 本発明にかかる実施形態1のMOS FET101のB−B断面領域の作製方法を示す図である。

【図7】 本発明にかかる実施形態1のMOS FET101のA−A断面領域の作製方法を示す図である。

【図8】 本発明にかかる実施形態1のMOS FET101のA−A断面領域のゲート絶縁膜の作製方法を示す図である。

【図9】 本発明にかかる実施形態1のMOS FET101のゲート電極の作製方法を示す図である。

【図10】 本発明にかかる実施形態1のMOS FET101の溝入口部のエッチング方法を示す図である。

【図11】 本発明にかかる実施形態2のMOS FET102の溝の底部と配線電極の配置を上視した図および断面構造の概略図である。

【図12】 本発明にかかる実施形態2のMOS FET102の作製方法を示す図である。

【符号の説明】

1 エピタキシャル成長済み半導体基板、2 n+型半導体基板(ドレイン層)、3 n-型半導体層(ドリフト層)、4 p-型半導体層(ボディ層)、5,5a,5b,5c,5d n+型半導体領域(ソース領域)、6 p+型半導体領域(コンタクトp領域)、10a,11 鉛直溝、10b,10c,12 斜方溝、20a,20b,20c ゲート絶縁膜、25 ポリシリコン層、30 ゲート電極、45 層間膜、50 ソース電極、51 ドレイン電極、60,61,62,63 HTO膜、70,71,73 エッチングマスク開口、80,81 溝開口、100,101,102 MOS FET、200 電子の経路。

Claims (6)

- 溝の中にゲート絶縁膜を介して埋め込まれたゲート電極を備えた電力用半導体装置において、

前記溝は半導体表面において一つの開口を有し、

その開口から鉛直方向に延びる鉛直溝と、

その開口から前記鉛直溝と異なる方向に延びる一つ以上の斜方溝と、

から構成され、前記斜方溝の両側のソース領域は、連接していることを特徴とする電力用半導体装置。 - 半導体基板に形成された第一導電型の半導体層と、

この第一導電型の半導体層の表面に形成された第二導電型の半導体層と、

この第二導電型の半導体層の表面部に形成された第一導電型の半導体領域と、

前記第一導電型の半導体領域及び前記第二導電型の半導体層を貫き前記第一導電型の半導体層に達するように形成された溝と、

この溝の中にゲート絶縁膜を介して埋め込まれたゲート電極と、

を備えた電力用半導体装置において、

前記溝は第一導電型の半導体領域表面において一つの開口を有し、

その開口から鉛直方向に延びる鉛直溝と、

その開口から前記鉛直溝と異なる方向に延びる一つ以上の斜方溝と、

から構成され、前記斜方溝の両側の第一の導電型の半導体領域は、連接していることを特徴とする電力用半導体装置。 - 前記鉛直溝および前記斜方溝は平板状の溝であることを特徴とする請求項2の電力用半導体装置。

- 前記鉛直溝と前記斜方溝に挟まれた第一の導電型の半導体領域を、前記斜方溝の外側の第一導電型の半導体領域と連接させるために、溝の半導体表面の前記斜方溝の延設方向に沿った開口部長さに比べてその開口部から延びる前記斜方溝の延設方向に沿った長さが短いことを特徴とする請求項3に記載の電力用半導体装置。

- 前記溝の半導体表面の開口は略円形であり、前記斜方溝は開口部を頂点とする円錐形状の一部をなす形状であって、

前記円錐形状の斜方溝と鉛直溝とに挟まれた第一の導電型の半導体領域が斜方溝の外側の第一導電型の半導体領域と連接するように、切り欠きを備えることを特徴とする請求項2の電力用半導体装置。 - 前記第二導電型の半導体層の表面部に形成された第一導電型の半導体領域は、半導体層表面において、高濃度にドーピングした第二の伝導型の半導体領域に囲まれていることを特徴とする請求項2から5のいずれか1項に記載の電力用半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003063897A JP4440552B2 (ja) | 2003-03-10 | 2003-03-10 | 電力用半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003063897A JP4440552B2 (ja) | 2003-03-10 | 2003-03-10 | 電力用半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004273849A JP2004273849A (ja) | 2004-09-30 |

| JP4440552B2 true JP4440552B2 (ja) | 2010-03-24 |

Family

ID=33125360

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003063897A Expired - Fee Related JP4440552B2 (ja) | 2003-03-10 | 2003-03-10 | 電力用半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4440552B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4979309B2 (ja) * | 2006-08-29 | 2012-07-18 | 三菱電機株式会社 | 電力用半導体装置 |

| CN104718623A (zh) * | 2012-10-15 | 2015-06-17 | 丰田自动车株式会社 | 半导体装置及其制造装置 |

| JP6453634B2 (ja) | 2014-12-10 | 2019-01-16 | トヨタ自動車株式会社 | 半導体装置 |

| DE102016111998B4 (de) | 2016-06-30 | 2024-01-18 | Infineon Technologies Ag | Ausbilden von Elektrodengräben unter Verwendung eines gerichteten Ionenstrahls und Halbleitervorrichtung mit Graben-Elektrodenstrukturen |

| US11398441B2 (en) * | 2020-09-14 | 2022-07-26 | Nanya Technology Corporation | Semiconductor device with slanted conductive layers and method for fabricating the same |

-

2003

- 2003-03-10 JP JP2003063897A patent/JP4440552B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004273849A (ja) | 2004-09-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7445982B2 (en) | Method of manufacturing a semiconductor integrated circuit device | |

| US12080793B2 (en) | Semiconductor device | |

| TWI503894B (zh) | 形成具有遮蔽電極結構的絕緣閘場效應電晶體裝置的方法 | |

| JP5167973B2 (ja) | 半導体装置 | |

| US20100285647A1 (en) | Insulated gate silicon carbide semiconductor device and method for manufacturing the same | |

| JP4456006B2 (ja) | 半導体装置およびその製造方法 | |

| JP2008034794A (ja) | 縦型トレンチ型絶縁ゲートmos半導体装置 | |

| CN110718546A (zh) | 在源极接触沟槽中具有集成的伪肖特基二极管的功率mosfet | |

| CN108574000A (zh) | 半导体装置和半导体装置的制造方法 | |

| JP5420225B2 (ja) | 半導体装置およびその製造方法 | |

| CN115224127B (zh) | 场效晶体管结构及其制造方法、芯片装置 | |

| JP5036130B2 (ja) | 自己整合した垂直ゲート半導体装置 | |

| US10326013B2 (en) | Method of forming a field-effect transistor (FET) or other semiconductor device with front-side source and drain contacts | |

| TW202308159A (zh) | 集成的平面-溝道閘極功率mosfet | |

| CN108695390A (zh) | 半导体器件及其制造方法 | |

| JP4440552B2 (ja) | 電力用半導体装置およびその製造方法 | |

| TW200945587A (en) | Semiconductor device and method of manufacturing the same | |

| JP2004363498A (ja) | 電力用半導体装置およびその製造方法 | |

| US8652906B2 (en) | Method for manufacturing a semiconductor device and semiconductor device | |

| US20180145171A1 (en) | Field Effect Transistor (FET) or Other Semiconductor Device with Front-Side Source and Drain Contacts | |

| JP4383820B2 (ja) | トレンチゲート型半導体装置 | |

| CN104600067A (zh) | 集成电路和制造集成电路的方法 | |

| JP4228594B2 (ja) | 半導体装置の製造方法 | |

| CN1675776A (zh) | 制造垂直栅极半导体器件的方法 | |

| CN223452324U (zh) | 半导体结构 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050629 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080327 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090428 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090624 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091215 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100107 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140115 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |