JP4351990B2 - 強誘電体メモリ装置及びその製造方法 - Google Patents

強誘電体メモリ装置及びその製造方法 Download PDFInfo

- Publication number

- JP4351990B2 JP4351990B2 JP2004355243A JP2004355243A JP4351990B2 JP 4351990 B2 JP4351990 B2 JP 4351990B2 JP 2004355243 A JP2004355243 A JP 2004355243A JP 2004355243 A JP2004355243 A JP 2004355243A JP 4351990 B2 JP4351990 B2 JP 4351990B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- ferroelectric

- hydrogen barrier

- memory device

- upper electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Semiconductor Memories (AREA)

Description

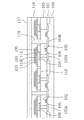

複数の前記上部電極を覆うように設けられ、Si 3 N 4 膜、SiON膜、Al 2 O 3 膜、TiO 2 膜、TiN膜若しくはTiとAlとの合金膜、又はTiとAlとの合金の酸化物膜、窒化物膜若しくは酸窒化物膜よりなる第2の水素バリア膜を備え、前記第1の水素バリア膜は、ワード線方向及びビット線方向のうちの一方向に並ぶ前記複数の強誘電体キャパシタよりなるキャパシタ列のうち、ワード線方向及びビット線方向のうちの他方向に隣り合う一対のキャパシタ列を覆うように形成されている。

半導体基板上の層間絶縁膜の上に順次形成された下部電極、強誘電体膜よりなる容量絶縁膜及び上部電極を有し、ワード線方向及びビット線方向に配置された複数の強誘電体キャパシタを備えた強誘電体メモリ装置の製造方法であって、

前記層間絶縁膜の上に、前記複数の強誘電体キャパシタの下部電極を形成する工程と、

前記下部電極上に容量絶縁膜を形成する工程と、

前記容量絶縁膜の上に上部電極を形成する工程と、

Si 3 N 4 膜、SiON膜、Al 2 O 3 膜、TiO 2 膜、TiN膜若しくはTiとAlとの合金膜、又はTiとAlとの合金の酸化物膜、窒化物膜若しくは酸窒化物膜よりなる第2の水素バリア膜を、複数の前記上部電極を覆い、かつ、ワード線方向及びビット線方向のうちの一方向に並ぶ前記複数の強誘電体キャパシタよりなるキャパシタ列のうち、ワード線方向及びビット線方向のうちの他方向に隣り合う一対のキャパシタ列を覆うように形成する工程とを備えている。

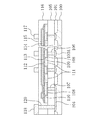

101 素子分離領域

102 ゲート電極

103A,103B 第1の高濃度不純物拡散層

104 第2の高濃度不純物拡散層

105 第1の層間絶縁膜

106 第1のコンタクトプラグ

107 第2のコンタクトプラグ

108 導電性の第3の水素バリア膜

109 下部電極

110 上部電極中継部

111 絶縁性の第2の水素バリア膜

112 容量絶縁膜

113 上部電極

114 段差緩和膜

115 第1の水素バリア膜

116 第2の層間絶縁膜

117 第1の金属配線

118 第2の金属配線

119 第3のコンタクトプラグ

120 第4のコンタクトプラグ

Claims (10)

- 半導体基板上の層間絶縁膜の上に順次形成された下部電極、強誘電体膜よりなる容量絶縁膜及び上部電極を有し、ワード線方向及びビット線方向に配置された複数の強誘電体キャパシタを備えた強誘電体メモリ装置であって、

前記上部電極を覆うように設けられ、Si3N4膜、SiON膜、Al2O3膜、TiO2膜、TiN膜若しくはTiとAlとの合金膜、又はTiとAlとの合金の酸化物膜、窒化物膜若しくは酸窒化物膜よりなる第2の水素バリア膜を備え、

前記第2の水素バリア膜は、ワード線方向及びビット線方向のうちの一方向に並ぶ前記複数の強誘電体キャパシタよりなるキャパシタ列のうち、ワード線方向及びビット線方向のうちの他方向に隣り合う一対のキャパシタ列を連続的に覆うように形成されており、

前記上部電極は、前記キャパシタ列毎に分割して形成されていることを特徴とする強誘電体メモリ装置。 - 前記上部電極と前記第2の水素バリア膜との間に形成され、前記上部電極の周縁部に形成される段差を緩和する段差緩和膜をさらに備え、

前記段差緩和膜は、前記一対のキャパシタ列を連続的に覆うように形成されていることを特徴とする請求項1に記載の強誘電体メモリ装置。 - 前記上部電極は、前記一方向に並ぶ前記複数の強誘電体キャパシタに共通に形成されていることを特徴とする請求項1に記載の強誘電体メモリ装置。

- 前記層間絶縁膜に形成されているコンタクトプラグと前記下部電極との間に形成された導電性水素バリア膜をさらに備えていることを特徴とする請求項1に記載の強誘電体メモリ装置。

- 前記共通の上部電極と前記第2の水素バリア膜との間に形成され、前記共通の上部電極の周縁部に形成される段差を緩和する段差緩和膜をさらに備えていることを特徴とする請求項3に記載の強誘電体メモリ装置。

- 前記導電性水素バリア膜は、TiとAlとの合金膜、TiとAlとの合金の窒化物膜若しくは酸窒化物膜、又はTiN膜よりなることを特徴とする請求項4に記載の強誘電体メモリ装置。

- 半導体基板上の層間絶縁膜の上に順次形成された下部電極、強誘電体膜よりなる容量絶縁膜及び上部電極を有し、ワード線方向及びビット線方向に配置された複数の強誘電体キャパシタを備えた強誘電体メモリ装置の製造方法であって、

前記層間絶縁膜の上に、前記複数の強誘電体キャパシタの下部電極を形成する工程と、

前記下部電極上に容量絶縁膜を形成する工程と、

前記容量絶縁膜の上に上部電極を形成する工程と、

Si3N4膜、SiON膜、Al2O3膜、TiO2膜、TiN膜若しくはTiとAlとの合金膜、又はTiとAlとの合金の酸化物膜、窒化物膜若しくは酸窒化物膜よりなる第2の水素バリア膜を、前記上部電極を覆い、かつ、ワード線方向及びビット線方向のうちの一方向に並ぶ前記複数の強誘電体キャパシタよりなるキャパシタ列のうち、ワード線方向及びビット線方向のうちの他方向に隣り合う一対のキャパシタ列を連続的に覆うように形成する工程とを備えていることを特徴とする強誘電体メモリ装置の製造方法。 - 前記下部電極を形成する工程よりも前に、前記層間絶縁膜に形成されているコンタクトプラグと前記下部電極との間に介在する導電性水素バリア膜を形成する工程をさらに備えていることを特徴とする請求項7に記載の強誘電体メモリ装置の製造方法。

- 前記上部電極を形成する工程と前記第2の水素バリア膜を形成する工程との間に、前記上部電極と前記第2の水素バリア膜との間に介在し、前記上部電極の周縁部に形成される段差を緩和する段差緩和膜を形成する工程をさらに備えていることを特徴とする請求項7に記載の強誘電体メモリ装置の製造方法。

- 前記導電性水素バリア膜は、TiとAlとの合金膜、TiとAlとの合金の窒化物膜若しくは酸窒化物膜、又はTiN膜よりなることを特徴とする請求項8に記載の強誘電体メモリ装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004355243A JP4351990B2 (ja) | 2001-09-27 | 2004-12-08 | 強誘電体メモリ装置及びその製造方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001296855 | 2001-09-27 | ||

| JP2004355243A JP4351990B2 (ja) | 2001-09-27 | 2004-12-08 | 強誘電体メモリ装置及びその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002224451A Division JP3962296B2 (ja) | 2001-09-27 | 2002-08-01 | 強誘電体メモリ装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005094038A JP2005094038A (ja) | 2005-04-07 |

| JP2005094038A5 JP2005094038A5 (ja) | 2007-03-15 |

| JP4351990B2 true JP4351990B2 (ja) | 2009-10-28 |

Family

ID=34466582

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004355243A Expired - Lifetime JP4351990B2 (ja) | 2001-09-27 | 2004-12-08 | 強誘電体メモリ装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4351990B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5230119B2 (ja) * | 2006-04-28 | 2013-07-10 | 株式会社半導体エネルギー研究所 | 半導体装置及びその作製方法 |

-

2004

- 2004-12-08 JP JP2004355243A patent/JP4351990B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005094038A (ja) | 2005-04-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4025829B2 (ja) | 半導体装置及びその製造方法 | |

| US20080076192A1 (en) | Semiconductor memory device and method of manufacturing the same | |

| US20050035384A1 (en) | Ferroelectric memory devices having expanded plate lines | |

| US6717198B2 (en) | Ferroelectric memory | |

| JP3962296B2 (ja) | 強誘電体メモリ装置及びその製造方法 | |

| US8324671B2 (en) | Semiconductor device and method of manufacturing the same | |

| US20080020492A1 (en) | Ferroelectric memory and its manufacturing method | |

| JP2010056133A (ja) | 半導体記憶装置 | |

| US7132709B2 (en) | Semiconductor device including a capacitor having a capacitive insulating film of an insulating metal oxide | |

| US20020042185A1 (en) | Semiconductor integrated circuit device and manufacturing method thereof | |

| JP4893304B2 (ja) | 半導体装置及びその製造方法 | |

| JP3793207B2 (ja) | 強誘電体記憶装置及びその製造方法 | |

| JP2010225928A (ja) | 半導体記憶装置及びその製造方法 | |

| JP4181135B2 (ja) | 半導体記憶装置 | |

| JP2009099767A (ja) | 半導体記憶装置およびその製造方法 | |

| US7507662B2 (en) | Ferroelectric memory and its manufacturing method | |

| JP4351990B2 (ja) | 強誘電体メモリ装置及びその製造方法 | |

| JP2005094038A5 (ja) | ||

| KR100574534B1 (ko) | 반도체장치 및 그 제조방법 | |

| US20080296646A1 (en) | Semiconductor memory device and method for fabricating the same | |

| JP2011124478A (ja) | 半導体記憶装置及びその製造方法 | |

| KR100867363B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2006253194A (ja) | 半導体装置およびその製造方法 | |

| JP2011018709A (ja) | 半導体記憶装置及びその製造方法 | |

| KR20070011273A (ko) | 반도체 장치 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050411 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050411 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090407 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090605 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090630 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090727 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120731 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4351990 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120731 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130731 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |