JP4238377B2 - 固体撮像素子およびその駆動方法 - Google Patents

固体撮像素子およびその駆動方法 Download PDFInfo

- Publication number

- JP4238377B2 JP4238377B2 JP02286798A JP2286798A JP4238377B2 JP 4238377 B2 JP4238377 B2 JP 4238377B2 JP 02286798 A JP02286798 A JP 02286798A JP 2286798 A JP2286798 A JP 2286798A JP 4238377 B2 JP4238377 B2 JP 4238377B2

- Authority

- JP

- Japan

- Prior art keywords

- reset

- signal

- mos transistor

- photoelectric conversion

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000003384 imaging method Methods 0.000 title claims description 28

- 238000000034 method Methods 0.000 title description 6

- 230000003321 amplification Effects 0.000 claims description 38

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 38

- 238000006243 chemical reaction Methods 0.000 claims description 31

- 238000005070 sampling Methods 0.000 claims description 9

- 230000002596 correlated effect Effects 0.000 claims description 8

- 230000004044 response Effects 0.000 claims description 3

- 239000011159 matrix material Substances 0.000 claims description 2

- 230000001276 controlling effect Effects 0.000 claims 2

- 230000005540 biological transmission Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 18

- 239000003990 capacitor Substances 0.000 description 5

- 238000009825 accumulation Methods 0.000 description 4

- 230000000875 corresponding effect Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 206010047571 Visual impairment Diseases 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 230000008034 disappearance Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000009795 derivation Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

【発明の属する技術分野】

本発明は、固体撮像素子およびその駆動方法に関し、特に単位画素ごとに増幅機能を持つMOS型イメージセンサなどの増幅型固体撮像素子およびその駆動方法に関する。

【0002】

【従来の技術】

従来、この種の増幅型固体撮像素子として、図13に示す構成の2次元固体撮像素子が知られている。すなわち、図13において、フォトダイオード101、増幅用MOSトランジスタ102、リセット用MOSトランジスタ103および垂直選択用MOSトランジスタ104によって単位画素105が構成され、リセット用MOSトランジスタ103のゲート電極が垂直リセット線108に、垂直選択用MOSトランジスタ104のゲート電極が垂直選択線109に、垂直選択用MOSトランジスタ104のソース電極が垂直信号線110にそれぞれ接続されている。

【0003】

また、垂直信号線110の一端と水平信号線111の間には、水平選択用MOSトランジスタ112が接続されている。そして、行選択をする垂直走査回路113から出力される2種類の垂直走査パルスφVSn,φVRnにより各行ごとに画素の動作が制御され、列選択をする水平走査回路114から出力される水平走査パルスφHmにより制御される水平選択用MOSトランジスタ112を介して画素信号が水平信号線111に出力される。その際、光電変換によってフォトダイオード101に蓄積された信号電荷が、増幅用MOSトランジスタ102によって信号電流に変換されて撮像素子の出力信号として導出される。

【0004】

【発明が解決しようとする課題】

しかしながら、上記構成の従来の増幅型2次元固体撮像素子では、各画素を構成する能動素子、主に増幅用MOSトランジスタ102の特性の画素ごとのバラツキ、特にMOSトランジスタのVth(閾値)バラツキがそのまま撮像素子の出力信号に乗ってきてしまう。この特性のバラツキは、画素ごとに固定の値を持つため、画面上に固定パターンノイズ(FPN;Fixed Patern Noise) として現れる。この固定パターンノイズを抑圧するためには、デバイスの外部にフレームメモリやラインメモリを用いたノイズ除去回路を設けて画素の特性のバラツキに起因するノイズ成分を除去する必要があり、したがって本固体撮像素子を撮像デバイスとして用いる例えばカメラシステムでは、ノイズ除去回路を外付けとする分だけ規模が大きくなってしまう。

【0005】

これに対し、固定パターンノイズをデバイスの内部で抑圧できるようにした増幅型固体撮像素子として、図14に示す構成のものが考えられる。この増幅型固体撮像素子においては、単位画素105の構成は図13と同じであるが、各画素105の特性のバラツキに起因する固定パターンノイズを抑圧するための水平出力回路115を設け、この水平出力回路115で画素105の読み出し前後(リセット前後)の信号の差分をとる処理を行うようにしている点が違う。

【0006】

図14において、垂直信号線110とグランドとの間には、増幅用MOSトランジスタ102のソースフォロワ動作の負荷として働く負荷用MOSトランジスタ116が接続されている。また、垂直信号線110には、一対の信号スイッチ用MOSトランジスタ117,117′の各一方の主電極が接続されている。この一対の信号スイッチ用MOSトランジスタ117,117′の各他方の主電極とグランドとの間には、一対の信号保持用キャパシタ118,118′がそれぞれ接続されている。

【0007】

また、一対の信号スイッチ用MOSトランジスタ117,117′の各他方の主電極と一対の水平信号線111,111′の間には、一対の水平選択用MOSトランジスタ112,112′がそれぞれ接続されている。一対の水平信号線111,111′には、差動アンプ119の非反転(+)入力端および反転(−)入力端がそれぞれ接続されている。

【0008】

上記構成の増幅型固体撮像素子においては、画素リセット前とリセット後のそれぞれの信号が、信号スイッチ用MOSトランジスタ117,117′を介して信号保持用キャパシタ118,118′に保持され、水平選択用MOSトランジスタ112,112′および水平信号線111,111′を介して差動アンプ119に供給される。そして、差動アンプ119において、画素リセット前とリセット後のそれぞれの信号の差分がとられることにより、単位画素ごとの特性のバラツキに起因する固定パターンノイズが除去される。

【0009】

しかしながら、上記構成の増幅型固体撮像素子では、単位画素ごとの特性のバラツキに起因する固定パターンノイズについては抑圧することはできるものの、画素リセット前とリセット後のそれぞれの信号が別々の信号経路を通って差動アンプ119に至ることから、一対の信号スイッチ用MOSトランジスタ117,117′や一対の水平選択用MOSトランジスタ112,112′の特性のバラツキが、垂直に相関を持つ縦筋状の固定パターンノイズとして画面上に現れることになる。したがって、この構成の場合にも、縦筋状の固定パターンノイズを抑圧するための補正回路がデバイスの外部に必要となる。

【0010】

本発明は、上記課題に鑑みてなされたものであり、その目的とするところは、単位画素ごとの特性のバラツキに起因する固定パターンノイズのみならず、縦筋状の固定パターンノイズをもデバイス内部で抑圧可能な増幅型固体撮像素子およびその駆動方法を提供することにある。

【0011】

【課題を解決するための手段】

本発明による固体撮像素子は、

入射光を光電変換しかつ光電変換によって得られた信号電荷を蓄積する光電変換素子と、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセットスイッチをオン/オフ制御するリセット選択スイッチと

を有し、前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通の垂直信号線を経由して出力する単位画素と、

前記単位画素から出力されたリセット前の信号とリセット後の信号のそれぞれの差分をとる差分回路とを備え、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

構成となっている。

【0012】

また、本発明による駆動方法は、上記構成の固体撮像素子において、単位画素の各々で画素信号を出力するごとに光電変換素子をリセットスイッチによってリセットし、単位画素の各々からリセットスイッチによるリセット前の信号とリセット後の信号とを導出しかつ共通の伝送経路を経由して伝送し、しかる後リセット前の信号とリセット後の信号のそれぞれの差分をとるようにする。

【0013】

上記構成の固体撮像素子の単位画素の各々において、画素信号を出力するごとに光電変換素子をリセットすることで、各単位画素からはリセット前とリセット後の信号が1画素ごとに順次出力される。このとき、画素の特性のバラツキに起因する固定パターンノイズが、各画素の増幅素子からオフセット成分として発生することから、リセット前とリセット後の信号の差分をとることで、ノイズ成分をキャンセルできる。また、2次元固体撮像素子においては、リセット前とリセット後の信号を垂直信号線から水平信号線へ同一の信号経路を経由して出力することで、垂直に相関を持つ縦筋状のノイズ成分も原理的に発生しない。

【0014】

【発明の実施の形態】

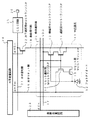

以下、本発明の実施の形態について図面を用いて詳細に説明する。図1は、2次元固体撮像素子に適用された本発明の第1実施形態を示す構成図である。

【0015】

図1において、破線で囲まれた領域が単位画素11を表している。この単位画素11は、光電変換素子であるフォトダイオード(PD)12と、増幅素子である増幅用MOSトランジスタ13と、選択スイッチである選択用MOSトランジスタ14と、リセットスイッチであるリセット用MOSトランジスタ15と、リセット選択用MOSトランジスタ16とから構成され、行列状に2次元配置されている。なお、図面上においては、簡略化のため、m列n行目の単位画素11のみを示している。

【0016】

この単位画素11において、フォトダイオード12は入射光を光電変換しかつ光電変換によって得られた信号電荷を蓄積する機能を持つ。このフォトダイオード12のカソード電極には、増幅用MOSトランジスタ13のゲート電極が接続されている。増幅用MOSトランジスタ13のドレイン電極は、電源(VDD)線17に接続されている。増幅用MOSトランジスタ13のソース電極と垂直信号線18の間には、選択用MOSトランジスタ14が接続されている。

【0017】

また、フォトダイオード12のカソード電極と電源線17の間には、リセット用MOSトランジスタ15が接続されている。リセット用MOSトランジスタ15のゲート電極と水平リセット線19の間には、リセット選択用MOSトランジスタ16が接続されている。リセット用MOSトランジスタ15およびリセット選択用MOSトランジスタ16としては、デプレッション型トランジスタが用いられている。このリセット選択用MOSトランジスタ16のゲート電極は、選択用MOSトランジスタ14のゲート電極と共に、垂直選択線20に接続されている。また、垂直信号線18と水平信号線21の間には、水平選択用MOSトランジスタ22が接続されている。

【0018】

また、行選択のための垂直走査回路23および列選択のための水平走査回路24が設けられている。そして、垂直走査回路23から出力される垂直走査パルスφVnが垂直選択線20に印加され、水平走査回路24から出力される水平リセットパルスφHRmが水平リセット線19に、水平走査パルスφHSm が水平選択用MOSトランジスタ22のゲート電極にそれぞれ印加される。すなわち、水平走査回路24が、水平リセットパルスφHRmを発生するリセット回路を兼ねることにより、回路構成の簡略化を図っている。

【0019】

水平信号線21の出力端側には、画素リセット前とリセット後のそれぞれの信号の差分をとる差分回路として、例えば回路構成が簡単な相関二重サンプリング回路(以下、CDS(Correlated Double Sampling)回路と称する)25が設けられている。このCDS回路25の具体的な回路構成およびその回路動作については、後で詳細に説明する。CDS回路25の出力端は、本撮像素子の出力端子26に接続されている。

【0020】

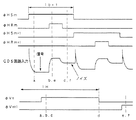

次に、上記構成の第1実施形態に係る増幅型固体撮像素子の動作について、図2のタイミングチャートを用いて説明する。

【0021】

先ず、光電変換によってフォトダイオード12に蓄積された信号電荷(電子)は、増幅用MOSトランジスタ13によって電気信号に変換される。そして、水平映像期間に入ると、垂直走査回路23から垂直走査パルスφVnが出力され、垂直選択線20を介して選択用MOSトランジスタ14およびリセット選択用MOSトランジスタ16の各ゲート電極に印加される。これにより、両MOSトランジスタ14,16が導通状態になり、選択用MOSトランジスタ14を通して信号電流が垂直信号線18に現れる。

【0022】

この水平映像期間中に、水平走査回路24から水平走査パルスφHSmが出力され、水平選択用MOSトランジスタ22のゲート電極に印加されることによって当該MOSトランジスタ22が導通状態になる。これにより、垂直信号線20に現れた信号電流は、水平選択用MOSトランジスタ22を通して水平信号線21に流れ、この水平信号線21を経てCDS回路25に供給される。

【0023】

その後すぐに、信号電流を出力したその同一画素に対し、水平走査回路24から水平リセットパルスφHRmが水平リセット線19に対して出力される。このとき、リセット選択用MOSトランジスタ16が導通状態にあることから、水平リセットパルスφHRmはこのリセット選択用MOSトランジスタ16を通してリセット用MOSトランジスタ15のゲート電極に印加される。これにより、リセット用MOSトランジスタ15が導通状態になるため、フォトダイオード12はVDDレベルにリセットされる。

【0024】

この水平リセットパルスφHRmは、図2のタイミングチャートから明らかなように、水平走査パルスφHSmの発生期間のほぼ中間で発生される。したがって、水平リセットパルスφHRmの消滅後、即ちリセット後のフォトダイオード12の電荷(ノイズ成分)が増幅用MOSトランジスタ13で電流に変換され、そのリセット電流が導通状態にある選択用MOSトランジスタ14、垂直信号線18および導通状態にある水平選択用MOSトランジスタ22を通して水平信号線21に流れ、この水平信号線21を経てCDS回路25に供給される。

【0025】

以上の一連の動作により、1つの画素11について信号出力→PDリセット→ノイズ出力という形で信号出力とリセット出力が順次得られる。これを垂直走査回路23で選択された画素行に対して、水平走査回路24によって順次画素選択を行うことにより、m列n行(信号出力→PDリセット→ノイズ出力)、m+1列n行(信号出力→PDリセット→ノイズ出力)、……という順番で水平信号線21に出力され、CDS回路25に供給される。そして、このCDS回路25において、リセット前の信号出力とリセット後のノイズ出力を使って相関二重サンプリングを行うことにより、主に増幅用MOSトランジスタ13の特性のバラツキ成分を除去することができる。

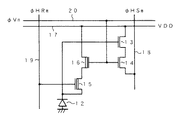

【0026】

図3に、CDS回路25の具体的な回路構成の一例を示す。このCDS回路25は、入力端子31に入力端が接続された電流電圧変換回路32と、この電流電圧変換回路32の出力端に一端が接続されたクランプキャパシタ33と、このクランプキャパシタ33の他端に一方の主電極が接続されたクランプMOSトランジスタ34と、クランプキャパシタ33の他端に一方の主電極が接続されたサンプルホールドMOSトランジスタ35と、このサンプルホールドMOSトランジスタ35の他方の主電極とグランドとの間に接続されたサンプルホールドキャパシタ36と、サンプルホールドMOSトランジスタ35の他方の主電極と出力端子38との間に接続されたバッファアンプ37とから構成されている。

【0027】

このCDS回路25において、電流電圧変換回路32は、入力端子31を介して供給される信号電流を反転(−)入力とし、所定のバイアス電圧Vbを非反転(+)入力とする差動アンプ39と、この差動アンプ39の反転入力端と出力端間に接続された帰還抵抗40とからなり、信号電流を信号電圧に変換する。クランプMOSトランジスタ34の他方の主電極にはクランプ電圧Vclが、そのゲート電極にはクランプパルスφCLがそれぞれ印加される。また、サンプルホールドMOSトランジスタ35のゲート電極には、サンプルホールドパルスφSHが印加される。

【0028】

上記構成のCDS回路25を差分回路として用い、リセット前の信号出力とリセット後のノイズ出力を使って相関二重サンプリングを行うことにより、増幅用MOSトランジスタ13の特性の画素ごとのバラツキ、特にMOSトランジスタのVthバラツキを除去することができる。

【0029】

上述したように、各単位画素11のフォトダイオード12のリセットを、1画素の信号が出力されるごとに行うようにするとともに、リセット前の信号出力とリセット後のノイズ出力を使って相関二重サンプリングを行うようにしたことにより、画素の特性のバラツキに起因する固定パターンノイズおよび垂直信号線18に接続されたスイッチ素子(水平選択用MOSトランジスタ22)の特性のバラツキに起因する縦筋状の固定パターンノイズを抑圧できる。

【0030】

すなわち、画素の特性のバラツキに起因する固定パターンノイズについては、単位画素11の増幅用MOSトランジスタ13からオフセット成分として発生するが、原理的に、画素リセット前とリセット後の信号を相関二重サンプリングすることによって除去できる。また、垂直信号線18に接続されたスイッチ素子の特性のバラツキに起因する縦筋状の固定パターンノイズについては、画素リセット前とリセット後の信号が同一の信号経路を通る構成となっており、別々のスイッチ素子(水平選択用MOSトランジスタなど)を通ることがないため、これも原理的に発生することがない。

【0031】

ここで、フォトダイオード12のリセット動作についてさらに詳しく述べる。なお、図1から明らかなように、リセット用MOSトランジスタ15およびリセット選択用MOSトランジスタ16として、デプレッション型トランジスタが用いられている。

【0032】

フォトダイオード12をVDDレベルにリセットする際に、リセット選択用MOSトランジスタ16にエンハンスメント型トランジスタを使った場合には、垂直走査パルスφVnによって選択された状態において、水平リセットパルスφHRmがリセット選択用MOSトランジスタ16のドレイン電極に印加されても、図4(A)に示すように、飽和領域の動作となるために、ソース側の電位はドレイン側の電位よりも落ちてしまうことになる。

【0033】

これに対し、リセット選択用MOSトランジスタ16としてデプレッション型トランジスタを使うことにより、図4(B)に示すように、線型領域での動作となり、ソース側の電位がほぼドレイン側の電位まで達する。同様に、リセット用MOSトランジスタ15にもエンハンスメント型トランジスタを用いると、飽和領域でのリセット動作となり、リセットの時間が短いと電荷の取り残しが生じ、残像の原因となる。これに対し、デプレッション型トランジスタを用いて線型領域でリセットすることにより、電荷の取り残しの無い、完全なリセット動作が可能となる。

【0034】

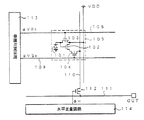

次に、上記構成の第1実施形態に係る増幅型固体撮像素子の動作について、図2のタイミングチャートに基づいて図5のポテンシャル図を用いて説明する。

【0035】

選択画素の信号読み出し時(図2のタイミングa)には、垂直走査パルスφVnによってリセット選択用MOSトランジスタ16が導通状態となり、ソース側の電位である水平リセットパルスφHRmの“L”レベルの電位がリセット用MOSトランジスタ15のゲート電極に印加される。このとき、リセット用MOSトランジスタ15は導通状態にならないので、フォトダイオード12に蓄積された信号電荷が増幅用MOSトランジスタ13で信号電流に変換される。

【0036】

選択画素のリセット時(図2のタイミングb)には、“H”レベルの水平リセットパルスφHRmが導通状態のリセット選択用MOSトランジスタ16を経てリセット用MOSトランジスタ15のゲート電極に印加され、これによりリセット用MOSトランジスタ15が導通状態となるため、フォトダイオード12がVDDレベルにリニア領域で完全リセットされる。

【0037】

選択画素のノイズレベル読み出し時(図2のタイミングc)には、水平リセットパルスφHRmが“L”レベルの状態にあり、この“L”レベルが導通状態のリセット選択用MOSトランジスタ16を経てリセット用MOSトランジスタ15のゲート電極に印加されることによってリセット用MOSトランジスタ15が非導通状態になる。これにより、リセットのレベルが増幅用MOSトランジスタ13でノイズ電流に変換される。また、この時点より次のフレーム蓄積が開始される。

【0038】

信号電荷の蓄積時(図2のタイミングd)、即ち他の行の他の列の読み出し時には、垂直走査パルスφVmが“L”レベルに遷移するが、リセット選択用MOSトランジスタ16がデプレッション型であるために、リセット用MOSトランジスタ15のゲート電極はフローティング状態にはならず、“L”レベルに保たれる。

【0039】

非選択画素のリセット時(図2のタイミングe)には、“H”レベルの水平リセットパルスφHRmによりリセット選択用MOSトランジスタ16のドレインがVDDレベルになると、リセット選択用MOSトランジスタ16のゲート電極の“L”レベルのポテンシャルに応じた電位が、リセット用MOSトランジスタ15のゲート電極に印加される。なお、フォトダイオード12は、デプレッションのリセットゲートがそのまま横型オーバーフローバリアになっていて、このレベルを超える電荷は電源へと捨てられるようになっているが、この時点でオーバーフローバリアが下がり、ここでオーバーフローレベルが決まる。

【0040】

ところで、単位画素の構成を考えた場合に、図6又は図7に示すように、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16を、フォトダイオード12のカソード電極と電源線17の間に直列に接続し、リセット用MOSトランジスタ15のゲート電極に水平リセットパルスφHRm又は垂直走査パルスφVnを、リセット選択用MOSトランジスタ16のゲート電極に垂直走査パルスφVn又は水平リセットパルスφHRmを印加する構成が一般的に考えられる。

【0041】

しかしながら、これらの構成の場合には、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16によるフィードスルーが、信号レベルを読み出す際とノイズレベルを読み出す際で異なってしまい、これが画素ごとのバラツキの原因となる。その理由について、図6の構成に対応した図8のポテンシャル図を用いて以下に説明する。

【0042】

先ず、垂直走査パルスφVnの発生によって画素が選択され、水平リセットパルスφHRmの発生によってリセットされているときを状態1.とする。この状態1.では、フォトダイオード12はVDDレベルにリセットされている。そして、状態2.では、水平リセットパルスφHRmが消滅し、リセット用MOSトランジスタ15がオフする際のフィードスルーの影響で、フォトダイオード12のポテンシャルはVDDレベルよりも僅かに浅くなる。この状態でノイズレベルの読み出しとなる。

【0043】

状態3.では、垂直走査パルスφVnが消滅することで非選択状態となる。リセット選択用MOSトランジスタ16がオフする際のフィードスルーの影響で、リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16の間の拡散領域のポテンシャルはVDDレベルよりも僅かに浅くなる。

【0044】

状態4.は電荷の蓄積状態であり、フォトダイオード12のポテンシャルが蓄積された電荷により浅くなっていく。状態5.は、非選択のリセット状態、即ち他の行の同じ列がリセットされている状態であり、水平リセットパルスφHRmの発生により、リセット用MOSトランジスタ15が導通状態となり、信号電荷とリセットゲートのフィードスルーおよびリセット選択ゲートのフィードスルーが合わされる。

【0045】

状態6.で水平リセットパルスφHRmが消滅するときに、さらにフォトダイオード12にリセットゲートのフィードスルーが加わる。他の行を読み出している期間中、状態5.状態6.を繰り返す。状態7.で、垂直走査パルスφVnの発生により、リセット選択用MOSトランジスタ16が導通状態となり、この状態で信号レベルが読み出される。この後、状態1.に戻る。

【0046】

図8のポテンシャル図において、状態2.と状態7.の比較から明らかなように、状態7.の信号レベルの読み出し時と、状態2.のノイズレベルの読み出し時では、フォトダイオード12に蓄えられているフィードスルーによる電荷の量が異なる。フィードスルーの量は、Vthバラツキと同様に個々のトランジスタによって異なるので、信号レベルの読み出しとノイズレベルの読み出しのフィードスルーの違いは、画素バラツキを抑圧するためのCDS回路25ではキャンセルすることができず、そのまま画素バラツキとして残ってしまう。

【0047】

リセット用MOSトランジスタ15とリセット選択用MOSトランジスタ16の接続関係を逆にした図7の構成の場合にも、図9のポテンシャル図から明らかなように、図6の構成の場合と同様のことが言える。

【0048】

これに対し、本実施形態においては、リセット用MOSトランジスタ15のゲート電極に、リセット選択用MOSトランジスタ16のソース電極を接続し、リセット選択用MOSトランジスタ16のドレイン電極、ソース電極を介してリセット用MOSトランジスタ15のゲート電極に水平リセットパルスφHRmを印加する構成としたことで、ノイズ読み出し時、信号読み出し時のいずれにおいても、リセット選択ゲートによるフィードスルーの影響がないので、各画素ごとのリセットゲートによるフィードスルーのバラツキは後段のCDS回路25で抑圧することができる。

【0049】

図10は、1次元固体撮像素子に適用された本発明の第2実施形態を示す構成図である。

【0050】

図10において、破線で囲まれた領域が単位画素51を表している。この単位画素51は、光電変換素子であるフォトダイオード(PD)52と、増幅素子である増幅用MOSトランジスタ53と、選択スイッチである選択用MOSトランジスタ54と、リセットスイッチであるリセット用MOSトランジスタ55とから構成され、直線状に1次元配置されている。

【0051】

この単位画素51において、フォトダイオード52は入射光を光電変換しかつ光電変換によって得られた信号電荷を蓄積する機能を持つ。このフォトダイオード52のカソード電極には、増幅用MOSトランジスタ53のゲート電極が接続されている。増幅用MOSトランジスタ53のドレイン電極は、電源(VDD)線56に接続されている。

【0052】

増幅用MOSトランジスタ53のソース電極と信号線57の間には、選択用MOSトランジスタ54が接続されている。また、フォトダイオード52のカソード電極と電源線56の間には、リセット用MOSトランジスタ55が接続されている。このリセット用MOSトランジスタ55としては、デプレッション型トランジスタが用いられている。

【0053】

また、1次元配列された単位画素51を順に選択するための走査回路58が設けられている。そして、この走査回路58から出力される走査パルスφHSmが選択用MOSトランジスタ54のゲート電極に、リセットパルスφHRmがリセット用MOSトランジスタ55のゲート電極にそれぞれそれぞれ印加される。すなわち、走査回路58が、リセットパルスφHRmを発生するリセット回路を兼ねることにより、回路構成の簡略化を図っている。

【0054】

信号線57の出力端側には、画素リセット前とリセット後のそれぞれの信号の差分をとる差分回路として、例えば回路構成が簡単なCDS回路59が設けられている。このCDS回路59としては、先の実施形態の場合と同様に、図3に示す回路構成のものが用いられる。

【0055】

次に、上記構成の第2実施形態に係る増幅型固体撮像素子の動作について、図11のタイミングチャートを用いて説明する。

【0056】

先ず、光電変換によってフォトダイオード52に蓄積された信号電荷(電子)は、増幅用MOSトランジスタ53によって電荷信号に変換される。そして、走査回路58から走査パルスφHSmが出力されると、選択用MOSトランジスタ54が導通状態になり、この選択用MOSトランジスタ54を通して信号電流が信号線57を経てCDS回路59に供給される。

【0057】

その後すぐに、信号電流を出力した同一画素に対し、走査回路58からリセットパルスφHRmが出力され、リセット用MOSトランジスタ55のゲート電極に印加される。これにより、リセット用MOSトランジスタ55が導通状態となるため、フォトダイオード52はVDDレベルにリセットされる。

【0058】

このリセットパルスφHRmは、図11のタイミングチャートから明らかなように、走査パルスφHSmの発生期間(“H”レベルの期間)内で発生される。したがって、リセットパルスφHRmの消滅後、即ちリセット後のフォトダイオード52の電荷(ノイズ成分)が増幅用MOSトランジスタ53で電流に変換され、そのリセット電流が導通状態にある選択用MOSトランジスタ54を通して信号線57に流れ、この信号線57を経てCDS回路59に供給される。

【0059】

以上の一連の動作により、1つの画素51について信号出力→PDリセット→ノイズ出力という形で信号出力とリセット出力が順次得られ、CDS回路59に供給される。そして、CDS回路59において、リセット前の信号出力とリセット後のノイズ出力を使って相関二重サンプリングを行うことにより、主に増幅用MOSトランジスタ53の特性のバラツキ成分を抑圧することができる。

【0060】

ここで、フォトダイオード52のリセット動作についてさらに詳しく述べる。なお、図10から明らかなように、リセット用MOSトランジスタ55として、デプレッション型トランジスタが用いられている。

【0061】

フォトダイオード52をVDDレベルにリセットする際に、リセット用MOSトランジスタ55にエンハンスメント型トランジスタを使った場合には、リセットパルスφHRmによって選択された状態でリセット用MOSトランジスタ55のドレイン電極に電源VDDが印加されても、図4(A)に示すように、飽和領域の動作となるため、ソース側の電位はドレイン側の電位よりも落ちてしまい、リセットの時間が短いと電荷の取り残しが生じ、残像の原因となる。

【0062】

これに対して、リセット用MOSトランジスタ55としてデプレッション型トランジスタを使うことにより、図4(B)に示すように、線型領域での動作となり、ソース側の電位がほぼドレイン側の電位まで達するため、電荷の取り残しの無い、完全なリセット動作が可能となる。

【0063】

続いて、上記構成の第2実施形態に係る増幅型固体撮像素子の動作について、図11のタイミングチャートに基づいて図12のポテンシャル図を用いて説明する。

【0064】

信号読み出し時(図11のタイミングa)には、リセット用MOSトランジスタ55は導通状態にはならないので、フォトダイオード52に蓄積された信号電荷が増幅用MOSトランジスタ53で信号電流に変換される。

【0065】

リセット時(図11のタイミングb)には、“H”レベルのリセットパルスφHRmがリセット用MOSトランジスタ55のゲート電極に印加され、これによりリセット用MOSトランジスタ55が導通状態となるため、フォトダイオード52がVDDレベルにリニア領域で完全リセットされる。

【0066】

ノイズレベル読み出し時(図11のタイミングc)には、リセットパルスφHRmが“L”レベルの状態にあり、リセット用MOSトランジスタ55が非導通状態になる。これにより、リセットのレベルが増幅用MOSトランジスタ53でノイズ電流に変換される。また、この時点(図11のタイミングd)より次のフレーム蓄積が開始される。

【0067】

なお、フォトダイオード52は、デプレッションのリセットゲートがそのまま横型オーバーフローバリアになっていて、このレベルを超える電荷は電源へと捨てられるようになっている。オーバーフローレベルは、リセット用MOSトランジスタ55のゲート電位の“L”レベルのポテンシャルである。

【0068】

【発明の効果】

以上説明したように、本発明によれば、単位画素ごとに増幅機能を持つ固体撮像素子において、単位画素の各々で画素信号を出力するごとに光電変換素子を完全リセットする構成としたことにより、各画素より信号成分とノイズ成分を順次出力することができるので、リセット前後の差分をとることによって固定パターンノイズを抑圧することができる。また、各画素を完全リセットしているので残像の発生もなく、さらに2次元固体撮像素子においては、信号成分とノイズ成分が垂直信号線から水平信号線へ同一の経路を経由して出力されるので、縦筋状の固定パターンノイズの発生も抑えることができる。

【図面の簡単な説明】

【図1】本発明の第1実施形態を示す構成図である。

【図2】第1実施形態の動作説明のためのタイミングチャートである。

【図3】CDS回路の回路構成の一例を示す回路図である。

【図4】エンハンスメント型MOSトランジスタ(A)とデプレッション型MOSトランジスタ(B)のId−Vd特性図である。

【図5】第1実施形態に係るリセット部の動作説明のためのポテンシャル図である。

【図6】単位画素の他の構成例を示す回路図である。

【図7】単位画素のさらに他の構成例を示す回路図である。

【図8】図5の構成に対応したポテンシャル図である。

【図9】図6の構成に対応したポテンシャル図である。

【図10】本発明の第2実施形態を示す構成図である。

【図11】第2実施形態の動作説明のためのタイミングチャートである。

【図12】第2実施形態に係るリセット部の動作説明のためのポテンシャル図である。

【図13】従来例を示す構成図である。

【図14】課題を説明するための構成図である。

【符号の説明】

11,51…単位画素、12,52…フォトダイオード(光電変換素子)、13,53…増幅用MOSトランジスタ、14,54…選択用MOSトランジスタ、15,55…リセット用MOSトランジスタ、16…リセット選択用MOSトランジスタ、17,56…電源(VDD)線、18…垂直信号線、19…水平リセット線、20…垂直選択線、21…水平信号線、22…水平選択用MOSトランジスタ、23…垂直走査回路、24…水平走査回路、25,59…CDS(相関二重サンプリング)回路、57…信号線、58…走査回路

Claims (7)

- 入射光を光電変換しかつ光電変換によって得られた信号電荷を蓄積する光電変換素子と、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセットスイッチをオン/オフ制御するリセット選択スイッチと

を有し、前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通の垂直信号線を経由して出力する単位画素と、

前記単位画素から出力されたリセット前の信号とリセット後の信号のそれぞれの差分をとる差分回路とを備え、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

ことを特徴とする固体撮像素子。 - 前記単位画素が行列状に2次元配置されてなる

ことを特徴とする請求項1記載の固体撮像素子。 - 前記垂直信号線と水平信号線との間に、前記垂直信号線に導出された前記リセットスイッチによるリセット前の信号とリセット後の信号とを共通に出力する水平選択スイッチを備えた

ことを特徴とする請求項2記載の固体撮像素子。 - 前記差分回路は、相関二重サンプリング回路である

ことを特徴とする請求項1記載の固体撮像素子。 - 前記単位画素が直線状に1次元配置されてなる

ことを特徴とする請求項1記載の固体撮像素子。 - 前記リセットスイッチは前記光電変換素子と電源線の間に接続されている

ことを特徴とする請求項5記載の固体撮像素子。 - 入射光を光電変換しかつ光電変換によって得られた信号電荷を蓄積する光電変換素子と、

デプレッション型トランジスタで構成され、前記光電変換素子をリセットするリセットスイッチと、

前記光電変換素子に蓄積された信号電荷を電気信号に変換する増幅素子と、

前記増幅素子からの信号を選択的に出力する選択スイッチと、

デプレッション型MOSトランジスタからなり、リセットパルスに応答して前記リセットスイッチをオン/オフ制御するリセット選択スイッチとを有し、

前記リセットスイッチは前記光電変換素子と電源線の間に接続され、

前記リセット選択スイッチは前記リセットスイッチのゲート電極と前記リセットパルスが与えられるリセット線の間に接続されている

単位画素を備えた固体撮像素子において、

単位画素の各々において画素信号を出力するごとに前記リセットスイッチによって前記光電変換素子をリセットし、

単位画素の各々から前記リセットスイッチによるリセット前の信号とリセット後の信号とを導出しかつ共通の伝送経路を経由して伝送し、

しかる後リセット前の信号とリセット後の信号のそれぞれの差分をとる

ことを特徴とする固体撮像素子の駆動方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP02286798A JP4238377B2 (ja) | 1997-08-15 | 1998-02-04 | 固体撮像素子およびその駆動方法 |

| US10/627,138 US7755690B2 (en) | 1997-08-15 | 2003-07-25 | Solid state image sensor with fixed pattern noise reduction |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9-220264 | 1997-08-15 | ||

| JP22026497 | 1997-08-15 | ||

| JP02286798A JP4238377B2 (ja) | 1997-08-15 | 1998-02-04 | 固体撮像素子およびその駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11122534A JPH11122534A (ja) | 1999-04-30 |

| JP4238377B2 true JP4238377B2 (ja) | 2009-03-18 |

Family

ID=26360156

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP02286798A Expired - Lifetime JP4238377B2 (ja) | 1997-08-15 | 1998-02-04 | 固体撮像素子およびその駆動方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4238377B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106341627A (zh) * | 2015-07-07 | 2017-01-18 | 松下知识产权经营株式会社 | 摄像装置 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1227893C (zh) * | 2000-02-04 | 2005-11-16 | 皇家菲利浦电子有限公司 | 有源像素传感器 |

| JP4262020B2 (ja) * | 2003-07-11 | 2009-05-13 | 浜松ホトニクス株式会社 | 光検出装置 |

| EP2639578B1 (en) * | 2006-12-14 | 2016-09-14 | Life Technologies Corporation | Apparatus for measuring analytes using large scale fet arrays |

| FR2930841B1 (fr) * | 2008-04-30 | 2010-08-13 | E2V Semiconductors | Capteur d'image a coins coupes avec un multiplexeur entre deux lignes adjacentes de pixels. |

-

1998

- 1998-02-04 JP JP02286798A patent/JP4238377B2/ja not_active Expired - Lifetime

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106341627A (zh) * | 2015-07-07 | 2017-01-18 | 松下知识产权经营株式会社 | 摄像装置 |

| CN106341627B (zh) * | 2015-07-07 | 2020-08-11 | 松下知识产权经营株式会社 | 摄像装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11122534A (ja) | 1999-04-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100681986B1 (ko) | 고체 이미지 센서 | |

| JP3911788B2 (ja) | 固体撮像素子およびその駆動方法 | |

| KR100552946B1 (ko) | 확장된 동적 범위의 이미지 센서 시스템 | |

| JP3918248B2 (ja) | 固体撮像素子およびその駆動方法 | |

| KR100636485B1 (ko) | 상관형 이중 샘플링을 갖는 3 트랜지스터 능동 픽셀 감지기 및 그의 제조 방법 | |

| KR20080012129A (ko) | 고체촬상장치 및 촬상장치 | |

| JP2708455B2 (ja) | 固体撮像装置 | |

| US6798451B1 (en) | Solid-state image pickup device and method for driving the same | |

| JPH0946597A (ja) | 固体撮像装置およびその駆動方法 | |

| JP5053892B2 (ja) | 固体撮像素子 | |

| JP2007067484A (ja) | 固体撮像装置 | |

| JP4238377B2 (ja) | 固体撮像素子およびその駆動方法 | |

| US7417212B2 (en) | Solid-state image-sensing device | |

| JP4253908B2 (ja) | 固体撮像素子およびその駆動方法、並びに固体撮像素子の信号処理方法 | |

| US7012238B2 (en) | Amplification-type solid-state image pickup device incorporating plurality of arrayed pixels with amplification function | |

| JP4058789B2 (ja) | 固体撮像装置及びその駆動方法、並びにカメラ | |

| JP2006148455A (ja) | 固体撮像装置 | |

| JPH09284658A (ja) | 固体撮像素子 | |

| JP4229770B2 (ja) | 増幅型固体撮像装置 | |

| JPH11313255A (ja) | 固体撮像素子およびその駆動方法 | |

| JP4424049B2 (ja) | 固体撮像装置および固体撮像装置の駆動方法 | |

| JP2007135227A (ja) | 固体撮像素子および固体撮像素子の駆動方法 | |

| KR20060123077A (ko) | 광전 변환 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070925 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071126 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080307 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080319 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081125 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081208 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130109 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |