JP4170033B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP4170033B2 JP4170033B2 JP2002205768A JP2002205768A JP4170033B2 JP 4170033 B2 JP4170033 B2 JP 4170033B2 JP 2002205768 A JP2002205768 A JP 2002205768A JP 2002205768 A JP2002205768 A JP 2002205768A JP 4170033 B2 JP4170033 B2 JP 4170033B2

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- region

- layer

- substrate

- electrode layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1339—Gaskets; Spacers; Sealing of cells

- G02F1/13394—Gaskets; Spacers; Sealing of cells spacers regularly patterned on the cell subtrate, e.g. walls, pillars

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136222—Colour filters incorporated in the active matrix substrate

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Liquid Crystal (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Optical Filters (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【発明の属する技術分野】

本発明は、液晶表示装置に係り、特に、アクティブ素子を形成した基板側にカラーフィルタ層を有する液晶表示装置に関する。

【0002】

【従来の技術】

ノート型コンピュータやコンピュータモニター、あるいはテレビ受像機用の高精細かつカラー表示が可能な液晶表示装置としてアクティブ・マトリクス型の液晶表示装置が多様されている。この種の液晶表示装置は、基本的には少なくとも一方がガラス板等の透明基板からなる二枚の基板の間に液晶層を挟持した所謂液晶パネルを有する。液晶パネルには、その周辺に駆動回路(駆動IC)やその配線等が搭載、または形成され、制御回路基板や必要に応じてバックライト等の補助照明装置が組み合わされて液晶表示装置とされる。なお、以下では、液晶パネル自体の構成の説明であっても便宜上、液晶表示装置として説明する。

【0003】

上記液晶表示装置の一方の基板(以下、第1基板)には薄膜トランジスタや薄膜ダイオード等のアクティブ素子とこのアクティブ素子で駆動される画素電極を有し、他方の基板(以下、第2基板)には前記画素電極との間に液晶駆動用の電界を形成する共通電極が形成される、所謂縦電界方式(TN方式)の液晶表示装置が知られている。この種のアクティブ・マトリクス型の液晶表示装置を開示したものとしては、例えば、特開昭63−309921号公報を挙げることができる。

【0004】

一方、第1基板側に上記の共通電極を形成して液晶層に印加する電界の方向を基板面とほぼ平行な方向とする、所謂横電界方式(IPS方式)の液晶表示装置も実用化されている。このIPS方式の液晶表示装置を開示したものとしては、2枚の基板の一方に櫛歯電極を用いて非常に広い視野角を得るようにした特公昭63−21907号公報等を挙げることができる。

【0005】

上記の各方式の液晶表示装置において、フルカラー表示を行うために第1基板または第2基板に3色のカラーフィルタ層を設けている。このカラーフィルタ層は、第2基板側に設けたものが広く知られているが、第1基板側にカラーフィルタ層を形成する方式もある。何れの方式も、アクティブ素子で選択される画素電極と共通電極の間にある液晶層を通る光をカラーフィルタ層で色変調することでカラー表示を得るものである。

【0006】

一般に、第1基板は画素を駆動する薄膜トランジスタ等のアクティブ素子をマトリクス状に有することからアクティブ・マトリクス基板とも称する。以下では第1基板をアクティブ・マトリクス基板、アクティブ素子を薄膜トランジスタとして説明する。このアクティブ・マトリクス基板にカラーフィルタ層を形成する方式は、対向して重ね合わせる第2基板との重ね合わせ工程が容易であるという利点を有する。以下、第2基板を対向基板とも称する。

【0007】

【発明が解決しようとする課題】

アクティブ・マトリクス基板は、基板上に多数の薄膜トランジスタをマトリクス状に形成し、この薄膜トランジスタの駆動端子(出力端子)に第1の電極層を形成する。対向基板側にカラーフィルタを有する方式では、この第1の電極層は画素電極となるものであるが、本発明の液晶表示装置では、第1の電極層を覆ってカラーフィルタ層を形成し、このカラーフィルタ層の上層に上記第1の電極層とは別部材として形成される第2の電極層を設け、第1の電極層と電気的に接続して画素電極とする。

【0008】

後述する実施例では、第1の電極層と第2の電極層および対向基板に設ける共通電極は、全てITO(インジウム・チン・オキサイド)であるものとして説明するが、この他にIZO(インジウム・ジンク・オキサイド)その他の透明導電膜を用いることができる。それぞれの薄膜トランジスタが配置される領域を画素領域とし、この画素領域にカラーフィルタ層が塗布される。そして、このカラーフィルタ層を覆って画素電極となる第2の電極層を形成する。このとき、第2の電極層を第1の電極層に対して電気的に接続する必要がある。

【0009】

従来のこの種のカラーフィルタ一体型アクティブ・マトリクス基板を採用する液晶表示装置では、カラーフィルタ層を形成後に薄膜トランジスタの駆動出力部にコンタクトホールを穿孔し、このコンタクトホールを通してカラーフィルタ層の上層に設ける電極層(画素電極)と薄膜トランジスタの駆動出力部とを電気的に接続している。また、画素領域を避けた部分で第1の基板と第2の基板との間の電気的接続を行う場合もあるが、画素領域を避けた部分には薄膜トランジスタの構成層やこの薄膜トランジスタに駆動のための各種信号を印加する配線等が存在するため、膜面が不整な場合が多い。そのため、電極層(画素電極)と薄膜トランジスタの駆動出力部と接続信頼性を大きくすることには限界があった。また、従来はカラーフィルタを形成後にコンタクトホールを形成する工程等を要する等、ホトグラフィー工程が多くなる等、特有の製造プロセスを採用する必要があり、対向基板側にカラーフィルタを形成する、所謂カラーフィルタ分離型の場合に比べて製造工程数が多くなるという問題があり、これが解決すべき課題の一つとなっていた。

【0010】

本発明の目的は、上記従来技術における課題を解決して低コストかつ高信頼性の液晶表示装置を得ることにあり、従来のカラーフィルタ分離型のアクティブ・マトリクス基板の製造工程を変更することなくカラーフィルタ一体型アクティブ・マトリクス基板を得ることができる。

【0011】

【課題を解決するための手段】

上記目的を達成するために、本発明は、アクティブ・マトリクス基板である第1基板の画素領域の夫々に、アクティブ素子の駆動出力端子に電気的に接続した導電性薄膜からなる第1の電極層を設け、画素領域の夫々にカラーフィルタ層の一部に形成した開孔部、あるいは端縁が第1の電極層の一部を露呈した露呈部を有するカラーフィルタ層を形成する。このカラーフィルタ層を覆って画素電極となる第2の電極層を形成することにより、第2の電極層は第1の電極層と上記開孔部、あるいは露呈部を通して電気的に接続される。第1の電極層は前記した従来のカラーフィルタ分離型のアクティブ・マトリクス基板と同等の構造であり、カラーフィルタ分離型では画素電極となるものである。

【0012】

したがって、カラーフィルタ層の形成の前工程までは従来のカラーフィルタ分離型のアクティブ・マトリクス基板の製造プロセスをそのまま使用でき、対向基板との位置合わせも容易であり、スループットが向上し、低コスト化が可能である。また、第1の電極層と第2の電極層の電気的接続部は画素領域にあるため、両電極層は高精度で接続され、信頼性が向上する。

【0013】

さらに、上記電気的接続部にアクティブ・マトリクス基板と対向基板の間の間隙を規制するスペーサを設けることで、光漏れが抑制される。さらに、カラーフィルタ層の開孔部、あるいは露呈部に対応する対向基板の部分に遮光層を設けることにより、開口率は低下するものの、コントラストを向上することがでいる。

【0014】

なお、本発明は、上記の構成および後述する実施例の構成に限定されるものではなく、本発明の技術思想を逸脱することなく種々の変更が可能であることは言うまでもない。

【0015】

【発明の実施の形態】

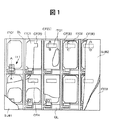

以下、本発明の実施の形態について、実施例の図面を参照して詳細に説明する。図1は本発明の液晶表示装置を構成する画素部の平面図であり、理解を容易にするため、各構成層の一部を破断し、あるいは除去して示す。また、図2〜図5はそれぞれ図1のA−A’線、B−B’線、C−C’線、D−D’線で切断した断面図である。なお、以下の実施例では、アクティブ素子として薄膜トランジスタを用いた例で説明する。各図中、参照符号SUB1は第1基板であるアクティブ・マトリクス基板、SUB2は第2基板(対向基板)、TFTは単位画素を駆動する薄膜トランジスタである。

【0016】

アクティブ・マトリクス基板SUB1の内面には、モノクロ表示の場合の1画素を構成する一つの単位画素、あるいはカラー表示の場合のカラー1画素を構成する赤(R)、緑(G)、青(B)の各単位画素は2本のデータ線(以下、ドレイン線)DLと2本の走査線(以下、ゲート線)GLで囲まれた領域(画素領域)に形成される。この単位画素をオン/オフ駆動する薄膜トランジスタTFTは画素領域の一郭に形成される。図2〜図4はアクティブ・マトリクス基板SUB1に薄膜トランジスタTFTおよび画素電極等を形成する工程を説明しており、図5はアクティブ・マトリクス基板SUB1に対向基板SUB2を貼り合わせ、内部に液晶層を封入した状態を示す。

【0017】

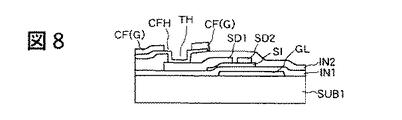

図2において、ゲート線GLの一部は薄膜トランジスタTFTのゲート電極となり、その上に第1の絶縁層IN1を介して半導体層SIが所要のパターンに形成され、この半導体層SI上にアルミニウム、クロム、モリブデン、その他の金属膜の成膜とパターニングでソース電極SD1およびドレイン電極SD2が形成される。そして、その上層には第2の絶縁層IN2が形成される。第2の絶縁層IN2にコンタクトホールTHを穿ち、このコンタクトホールTHを通してインジウム・チン・オキイドを好適とする導電層を蒸着等で成膜し、ソース電極SD1と電気的に接続された第1の電極層ITO1を画素領域毎にその大略全域にわたる範囲に形成する(図1参照)。

【0018】

そして、画素領域内の第1の電極層ITO1を覆って各色のカラーフィルタ層が塗布される。図3は図1のB−B’線の沿った断面を示す。この画素には緑(G)のカラーフィルタ層CF(G)が形成される。このとき、カラーフィルタ層の一部に開孔部CFHを設ける。開孔部CFH内には下層にある第1の電極層ITO1が見えている。

【0019】

次に、図4に示したように、カラーフィルタ層CFを覆って第2のデータ層ITO2を蒸着等で形成する。図4は青の蛍光体層CF(B)の単位画素の部分の断面図である。図示されたように、第2の電極層ITO2はカラーフィルタ層CFの開孔部CFHを通して第1の電極層ITO1と電気的に接続される。この第2の電極層ITO2は画素電極となる。その後、第2の電極層ITO2の上層に配向膜を形成してアクティブ・マトリクス基板が完成する。なお、配向膜は図示は省略した。

【0020】

図5は上記のようにして製造されたアクティブ・マトリクス基板に共通電極ITO3を有する対向基板である第2基板SUB2を液晶層CLを介して貼り合わせた状態を示す図1のD−D’線の沿った断面図である。

【0021】

本実施例の液晶表示装置では、アクティブ・マトリクス基板側に形成したカラーフィルタ層CFの上に画素電極である第2の電極層ITO2と対向基板SUB2に共通電極ITO3の間に形成される電界で液晶層CLの配向が制御され、所定の色の単位画素が駆動されて画像表示が行われる。カラーフィルタ層CFに設ける開孔部CFHの面積比をあまり大きくすると色相の劣化が目立つので、この大きさは1%〜20%とするのが望ましい。この面積比は液晶パネルのサイズや実装する電子機器の種類等、表示品質の要求性能を勘案して決めればよい。

【0022】

本実施例によれば、従来のように、金属層で形成されたソース電極SD1(あるいはドレイン電極SD2)と画素電極であるインジウム・チン・オキサイドで形成される透明電極ITOとを電気的に接続のためのコンタクト層の形成を要せず、従ってこのようなコンタクト層の形成のためのプロセスを必要としない。また、アクティブ・マトリクス基板SUB1は従来のカラーフィルタ分離型のアクティブ・マトリクス基板の製造プロセスをそのまま採用できるため、新規な製造設備を要しない。

【0023】

さらに、第1の電極層ITO1と第2の電極層ITO2の電気的接続部を画素領域の内部で行うため、画素領域の外側にはゲート線やドレイン線が存在するために、膜面が不整でかつコンタクトホールの大きさ、位置に制限がある。本実施例によれば、このような部分にコンタクトホールTHを形成しないため、第1の電極層ITO1と第2の電極層ITO2の電気的接続を容易に、かつ確実に行うことはでき、信頼性が向上する。

【0024】

そして、本実施例は、共に透明な第1の電極層ITO1と第2の電極層ITO2を直接接続するため、当該接続の信頼性が向上し、また、開口率の低下はなく、明るい画像表示を得ることができる。

【0025】

図6は本発明の第2実施例を説明する図1と同様の画素部の平面図である。また、図7〜図10は図6のA−A’線、B−B’線、C−C’線、D−D’線で切断した断面図である。本実施例は、図7に示したように、アクティブ・マトリクス基板SUB1上に薄膜トランジスタTFTを形成し、薄膜トランジスタTFTのソース電極SD1と接続する第1の電極層ITO1の形成までは第1実施例と同様であるので、繰り返しの説明は省略する。本実施例では、第1の電極層ITO1の上層に形成するカラーフィルタ層CFNI設ける開孔部CFHの位置を薄膜トランジスタTFTのソース電極SD1の直上で第1の電極層ITO1と当該ソース電極SD1との接続部分を含む部分としたものである。

【0026】

薄膜トランジスタTFTのソース電極SD1の部分は、画素領域でカラーフィルタ層の光透過に寄与しない部分である。したがって、ソース電極SD1を含んだ部分にカラーフィルタ層CFの開孔部CFHを設けることで当該開孔部CFHにより色相の劣化を低減できる。図7〜図10は、カラーフィルタ層CFの開孔部CFHの位置を除いては同様である。また、本実施例の他の効果は第1実施例と同様であるので繰り返しの説明は省略する。

【0027】

図11は本発明の第3実施例を説明する図1および図2と同様の画素部の平面図である。本実施例は、薄膜トランジスタTFTのソース電極SD1に接続する第1の電極層ITO1を当該ソース電極SD1の近傍のみに限定したものである。第1の電極層ITO1はカラーフィルタ層CFの上層に成膜する第2の電極層ITO2との電気的接続の機能を有するのみでよい。したがって、本実施例では、前記の各実施例のように画素領域の大略全域を覆って第1の電極層ITO1を形成せずに、必要な部分にのみ第1の電極層ITO1を形成した。

【0028】

カラーフィルタ層CFに設ける開孔部CFHは、この第1の電極層ITO1の位置に合わせて形成する。そして、カラーフィルタ層CFの上層に形成する画素電極となる第2の電極層ITO2は、図中に参照符号COTで示した部分で第1の電極層ITO1と電気的に接続される。

【0029】

本実施例によれば、第1の電極層ITO1を必要最小限の面積とすることで画素の透過率を向上できる。他の効果は前記の各実施例と同様であるので、繰り返しの説明は省略する。

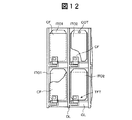

【0030】

図12は本発明の第4実施例を説明する画素部の平面図である。本実施例では、例えば第1実施例における第1の電極層ITO1の上層に形成するカラーフィルタ層CFの一部を当該第1の電極層ITO1の端縁から後退させて塗布する。このカラーフィルタ層CFの上に第2の電極層ITO2を画素領域の大略全域に形成することで、上記カラーフィルタ層CFの後退で露呈した第1の電極層ITO1と電気的に接続される。この接続部分を参照符号COTで示す。本実施例の効果は第1の実施例と同様である。

【0031】

図13は本発明の第5実施例を説明する図12と同様の画素部の平面図である。本実施例では、例えば第1実施例における第1の電極層ITO1の上層に形成するカラーフィルタ層CFを第1の電極層ITO1の領域で分割し、カラーフィルタ層CFが露呈した露呈部を設けた。このカラーフィルタ層CFの上に第2の電極層ITO2を画素領域の大略全域に形成することで、上記カラーフィルタ層CFの分割で露呈した第1の電極層ITO1と画素領域内で電気的に接続される。この接続部分を参照符号COTで示す。なお、カラーフィルタ層CFの分割は図13に示したようにゲート線GLの延在方向と平行な方向に限るものではなく、ドレイン線DLと平行な方向、非平行な方向、あるいはそれらを組合せて分割数を3以上とすることも可能である。本実施例の効果は第1の実施例等と同様である。

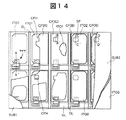

【0032】

図14は本発明の第6実施例を説明する画素部の平面図であり、理解を容易にするため、各構成層の一部を破断し、あるいは除去して示す。また、図15〜図18はそれぞれ図14のA−A’線、B−B’線、C−C’線、D−D’線で切断した断面図である。本実施例は、例えば図1で説明した本発明の第1実施例にスペーサを設けたものである。通常、アクティブ・マトリクス基板SUB1と対向基板SUB2の間隙を所定値に保持するために、両者の間にスペーサを介挿している。本実施例では、このスペーサを、アクティブ・マトリクス基板SUB1に固定した、所謂柱状スペーサSPとしたものである。この柱状スペーサSPは第2の電極層ITO2の上、かつカラーフィルタ層CFに設けた開孔部CFHの直上に形成した。

【0033】

図15と図16までは前記実施例と同様のプロセスで各層が形成される。その後、図17に示したように、柱状スペーサSPをホトリソグラフィー技法などを用いてカラーフィルタ層CFの開孔部CFHに設ける。このとき、柱状スペーサSPを遮光性材料で形成すれば、開口率は低下するが、当該開孔部CFHからの光抜けを抑制してコントラストを向上することができる。なお、柱状スペーサに代えて粒状のスペーサ(スペーサビーズ)を設けてもよい。スペーサビーズはスプレーで散布されるが、このときに凹部を形成するカラーフィルタ層CFの開孔部CFHに当該スペーサビーズが配置される確率が大きくなる。スペーサビーズを用いる場合は、画素領域の内部にランダムに散布されるので、ガラスあるいはプラスチックの透明ビーズを用いるのが望ましい。

【0034】

図19は本発明の第7実施例を説明する画素部の平面図であり、理解を容易にするため、各構成層の一部を破断し、あるいは除去して示す。また、図20〜図23はそれぞれ図19のA−A’線、B−B’線、C−C’線、D−D’線で切断した断面図である。本実施例は、図6で説明した本発明の第2実施例に相当するアクティブ・マトリクス基板SUB1を用い、対向基板SUB2におけるカラーフィルタ層CFの開孔部CFHに対応した部分に遮光膜BSを設けたものである。

【0035】

すなわち、図20〜図22は図7〜図9と同様であり、図23に示した対向基板SUB2に遮光膜BSを設けた。この遮光膜BSは図19のカラーフィルタ層CFの開孔部CFHである第1の電極層ITO1と第2の電極層ITO2との接続部分の直上に位置する。遮光膜BSの大きさはカラーフィルタ層CFの開孔部CFHと同等とするのが望ましいが、それより多少の大きくても、あるいは小さくてもよい。

【0036】

本実施例によれば、画素の開口率は若干低下するが、開孔部CFHを透過する光Lを遮断することで色相低下を抑制し、コントラストの向上を図ることができ、高精細の画像表示装置に好適である。本実施例の他の効果は本発明の第2実施例と同様である。

【0037】

図24は本発明による液晶表示装置の全体構成の一例を説明する展開斜視図である。また、図25は図24のE−E’線に相当する位置で切断した断面図である。図24中、参照符号PNLは液晶パネルを示し、前記実施例において説明したアクティブ・マトリクスSUB1と対向基板SUB2の貼り合わせたものの表裏にそれぞれ偏光板(図示せず)を貼付して構成されている。また、この液晶パネルPNLの周縁には画素を構成する薄膜トランジスタに表示データや走査信号を供給するための駆動回路チップDICが搭載されている。

【0038】

また、参照符号OPSはプリズムシートや拡散シートからなる光学シート、GLBは導光板、RFSは反射シート、MDLはモールドフレーム、SHDはシルドフレーム、CFLは導光板GLBと共にバックライトを構成する冷陰極蛍光ランプ、RFSは反射板である。また、参照符号FPC1、FPC2は駆動回路チップDIC等に表示のためのデータやタイミング信号を供給するためのフレキシブルプリント基板、LPCはランプケーブルを示す。

【0039】

導光板GLBはモールドフレームMDLの内側に設置され、その下側には反射板RFSが設けられている。導光板GLBの液晶パネルPNL側にはプリズムシートや拡散シートからなる光学シートOPSが重ね合わされてモールドフレームMDLに収容されている。そして、導光板GLBのの両側の側縁に沿って冷陰極蛍光ランプCFLが配置されている。

【0040】

なお、図25には駆動回路チップDICやフレキシブルプリント基板FPC1、FPC2等は図示を省略してある。このような構成とした液晶表示装置において、液晶パネルPNLは導光板GLB、冷陰極蛍光ランプCFL、ランプ反射シートLFS等で構成されたバックライトからの光で照明され、当該液晶パネルPNLに形成された電子潜像を可視化する。

【0041】

図26は本発明の液晶表示装置を構成する液晶表示装置の回路構成を簡略に説明するブロック図である。図中、参照符号ARは液晶パネルの有効表示領域を示し、この有効表示領域ARにおいて前記した第1の基板SUB1の内面にゲート線(走査線)GL、ドレイン線(データ線)GL、共通電極線CL、薄膜トランジスタTFT、カラーフィルタ層CF、画素電極(ITO2)等が形成されている。走査線GLとデータ線GLの交差部分に画素選択用の薄膜トランジスタTFTが形成されている(図示せず)。共通電極線CLは前記した第1の基板(対向基板SUB2)の内面に形成された共通電極に共通電位を供給するものであり、、アクティブ・マトリクス基板SUB1側から端子Vcomを介して体好基板SUB2側に接続される。

【0042】

走査線GLは走査回路GDRで駆動され、データ線GLにはデータ線駆動回路DDRから表示データが供給される。コントローラCTLは外部信号源SSCから入力する表示信号に基づいて表示データやタイミング信号などの制御信号を生成する。表示データはデータ線駆動回路DDRに与えられ、制御信号は走査回路GDRに印加される。電源回路PWUは液晶表示装置に必要とれる各種の電圧を生成する。

【0043】

図27は本発明の液晶表示装置を適用した電子機器の一例であるテレビ受像機の外観図である。このテレビ受像機は表示部DSPとスタンド部STDで構成され、比較的大サイズの画面を有する液晶パネルPNLを有する液晶表示装置が表示部DSPに実装される。液晶表示装置の画面となる液晶パネルPNLの有効表示領域は表示部に露呈されている。このテレビ受像機の表示部に本発明の液晶表示装置を実装することで、高品質、高信頼性の画像表示装置を実現できる。

【0044】

なお、本発明は、上記実施例のサイドエッジ型バックライトを用いた液晶表示装置に限らず、液晶表示装置の背面に直接複数の冷陰極蛍光ランプを配置した、所謂直下型のバックライト、あるいはバックライトやフロントライト等の補助照明装置を備えた、あるいはこのような補助照明装置を備えない携帯電話機等の電子端末にも同様に適用できることは言うまでもない。

【0045】

【発明の効果】

以上説明したように、本発明によれば、従来のカラーフィルタ分離型のアクティブ・マトリクス基板の製造工程を変更することなくカラーフィルタ一体型アクティブ・マトリクス基板を用いた高品質の液晶表示装置を提供することができる。

【図面の簡単な説明】

【図1】本発明の液晶表示装置を構成する画素部の平面図である。

【図2】図1のA−A’線で切断した断面図である。

【図3】図1のB−B’線で切断した断面図である。

【図4】図1のC−C’線で切断した断面図である。

【図5】図1のD−D’線で切断した断面図である。

【図6】本発明の第2実施例を説明する図1と同様の画素部の平面図である。

【図7】図6のA−A’線で切断した断面図である。

【図8】図6のB−B’線で切断した断面図である。

【図9】図6のC−C’線で切断した断面図である。

【図10】図6のD−D’線で切断した断面図である。

【図11】本発明の第3実施例を説明する図1および図2と同様の画素部の平面図である。

【図12】本発明の第4実施例を説明する画素部の平面図である。

【図13】本発明の第5実施例を説明する画素部の平面図である。

【図14】本発明の第6実施例を説明する画素部の平面図である。

【図15】図14のA−A’線で切断した断面図である。

【図16】図14のB−B’線で切断した断面図である。

【図17】図14のC−C’線で切断した断面図である。

【図18】図14のD−D’線で切断した断面図である。

【図19】本発明の第7実施例を説明する画素部の平面図である。

【図20】図19のA−A’線で切断した断面図である。

【図21】図19のB−B’線で切断した断面図である。

【図22】図19のC−C’線で切断した断面図である。

【図23】図19のD−D’線で切断した断面図である。

【図24】本発明による液晶表示装置の全体構成の一例を説明する展開斜視図である。

【図25】図24のE−E’線に相当する位置で切断した断面図である。

【図26】本発明の液晶表示装置を構成する液晶表示装置の回路構成を簡略に説明するブロック図である。

【図27】本発明の液晶表示装置を適用した電子機器の一例であるテレビ受像機の外観図である。

【符号の説明】

SUB1・・・・第1基板(アクティブ・マトリクス基板)、DL・・・・データ線(ドレイン線)、GL・・・・走査線(ゲート線)、TFT・・・・薄膜トランジスタ、SUB2・・・・対向基板、IN1・・・・第1の絶縁層、IN2・・・・第2の絶縁層、SI・・・・半導体層、SD1・・・・ソース電極、SD2・・・・ドレイン電極、TH・・・・コンタクトホール、ITO1・・・・第1の電極層、ITO2・・・・第2の電極層、CF(CF(R),CF(G),CF(B))・・・・カラーフィルタ層、CFH・・・・開孔部、ITO3・・・・共通電極。

Claims (9)

- 画素電極と、これに対応するアクティブ素子及びカラーフィルタ層を夫々含む複数の画素領域がマトリクス状に配列された第1基板と、前記画素電極との間に電界を形成するための共通電極を形成した第2基板と、前記第1基板及び前記第2基板の間に挟持された液晶層とを有する液晶パネルを具備する液晶表示装置であって、

前記第1基板の前記画素領域の夫々には、前記アクティブ素子の駆動出力端子に電気的に接続した導電性薄膜からなる第1の電極層が設けられ、

前記画素領域内の夫々にて前記カラーフィルタ層の一部に形成した当該カラーフィルタ層の開孔部と、

前記カラーフィルタ層の上層にて前記画素電極を形成し、且つ前記第1の電極層と前記開孔部を通して電気的に接続される第2の電極層とが設けられ、

前記第1の電極層と、前記第2の電極層は、透明電極であり、

前記アクティブ素子の前記駆動出力端子は、遮光性の金属膜であり、

前記第1基板は、複数の走査線と、前記複数の走査線に交差する複数のデータ線とを有し、

前記開孔部は、前記アクティブ素子の前記駆動出力端子が形成された第1の領域と、前記第1の領域以外の領域であって、かつ、前記走査線と前記データ線の何れとも重畳しない第2の領域との両方を含むように設けられていることを特徴とする液晶表示装置。 - 前記第1の電極層は、前記走査線の延在方向に長手方向を有することを特徴とする請求項1に記載の液晶表示装置。

- 前記開孔部は、前記走査線の延在方向に長手方向を有することを特徴とする請求項1または2に記載の液晶表示装置。

- 前記第1の電極層の面積は、前記第2の電極層の面積よりも小さいことを特徴とする請求項1から3の何れかに記載の液晶表示装置。

- 前記画素領域は、隣り合う一対の前記走査線と、隣り合う一対の前記データ線とで囲まれた領域であり、

前記画素領域を前記走査線に平行な仮想的な線で第3の領域と第4の領域とに二等分したとき、前記アクティブ素子の前記駆動出力端子と前記開孔部は、ともに前記第3の領域内に配置されていることを特徴とする請求項1から4の何れかに記載の液晶表示装置。 - 前記第2基板は、前記開孔部に対応する位置に遮光層を有することを特徴とする請求項1から5の何れかに記載の液晶表示装置。

- 画素電極と、これに対応するアクティブ素子及びカラーフィルタ層を夫々含む複数の画素領域がマトリクス状に配列された第1基板と、前記画素電極との間に電界を形成するための共通電極を形成した第2基板と、前記第1基板及び前記第2基板の間に挟持された液晶層とを有する液晶パネルを具備する液晶表示装置であって、

前記第1基板の前記画素領域の夫々には、前記アクティブ素子の駆動出力端子に電気的に接続した導電性薄膜からなる第1の電極層が設けられ、

前記画素領域内の夫々にて前記カラーフィルタ層の一部に形成した当該カラーフィルタ層の開孔部と、

前記カラーフィルタ層の上層にて前記画素電極を形成し、且つ前記第1の電極層と前記開孔部を通して電気的に接続される第2の電極層とが設けられ、

前記第1基板は、複数の走査線と、前記複数の走査線に交差する複数のデータ線とを有し、

前記開孔部は、前記アクティブ素子の前記駆動出力端子が形成された第1の領域と、前記第1の領域以外の領域であって、かつ、前記走査線と前記データ線の何れとも重畳しない第2の領域との両方を含むように設けられ、

前記第1の電極層は、前記走査線の延在方向に長手方向を有し、

前記開孔部は、前記走査線の延在方向に長手方向を有し、

前記第1の電極層と、前記第2の電極層は、透明電極であり、

前記第1の電極層の面積は、前記第2の電極層の面積よりも小さく、

前記アクティブ素子の前記駆動出力端子は、遮光性の金属膜であることを特徴とする液晶表示装置。 - 前記画素領域は、隣り合う一対の前記走査線と、隣り合う一対の前記データ線とで囲まれた領域であり、

前記画素領域を前記走査線に平行な仮想的な線で第3の領域と第4の領域とに二等分したとき、前記アクティブ素子の前記駆動出力端子と前記開孔部は、ともに前記第3の領域内に配置されていることを特徴とする請求項7に記載の液晶表示装置。 - 前記第2基板は、前記開孔部に対応する位置に遮光層を有することを特徴とする請求項7または8に記載の液晶表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002205768A JP4170033B2 (ja) | 2002-07-15 | 2002-07-15 | 液晶表示装置 |

| US10/617,755 US6992738B2 (en) | 2002-07-15 | 2003-07-14 | Liquid crystal display device including an electrode constituting pixel electrode connected to another electrode through opening formed in color filter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002205768A JP4170033B2 (ja) | 2002-07-15 | 2002-07-15 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004045970A JP2004045970A (ja) | 2004-02-12 |

| JP2004045970A5 JP2004045970A5 (ja) | 2005-08-18 |

| JP4170033B2 true JP4170033B2 (ja) | 2008-10-22 |

Family

ID=31710983

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002205768A Expired - Fee Related JP4170033B2 (ja) | 2002-07-15 | 2002-07-15 | 液晶表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6992738B2 (ja) |

| JP (1) | JP4170033B2 (ja) |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005316404A (ja) * | 2004-03-31 | 2005-11-10 | Seiko Epson Corp | 電気光学装置及び電子機器 |

| US20070077218A1 (en) * | 2005-08-26 | 2007-04-05 | L'oreal | Composition containing a coloring agent |

| JP2007163620A (ja) * | 2005-12-12 | 2007-06-28 | Hitachi Displays Ltd | 液晶表示装置及びバックライト装置 |

| US7615706B2 (en) * | 2006-08-21 | 2009-11-10 | Tpo Displays Corp. | Layout of a printed circuit board |

| KR101304410B1 (ko) * | 2006-09-19 | 2013-09-05 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| TWI401495B (zh) * | 2009-06-24 | 2013-07-11 | Au Optronics Corp | 顯示面板 |

| US9223138B2 (en) | 2011-12-23 | 2015-12-29 | Microsoft Technology Licensing, Llc | Pixel opacity for augmented reality |

| US9606586B2 (en) | 2012-01-23 | 2017-03-28 | Microsoft Technology Licensing, Llc | Heat transfer device |

| US9779643B2 (en) | 2012-02-15 | 2017-10-03 | Microsoft Technology Licensing, Llc | Imaging structure emitter configurations |

| US9297996B2 (en) | 2012-02-15 | 2016-03-29 | Microsoft Technology Licensing, Llc | Laser illumination scanning |

| US9368546B2 (en) | 2012-02-15 | 2016-06-14 | Microsoft Technology Licensing, Llc | Imaging structure with embedded light sources |

| US9726887B2 (en) | 2012-02-15 | 2017-08-08 | Microsoft Technology Licensing, Llc | Imaging structure color conversion |

| US9578318B2 (en) | 2012-03-14 | 2017-02-21 | Microsoft Technology Licensing, Llc | Imaging structure emitter calibration |

| US11068049B2 (en) | 2012-03-23 | 2021-07-20 | Microsoft Technology Licensing, Llc | Light guide display and field of view |

| US9558590B2 (en) | 2012-03-28 | 2017-01-31 | Microsoft Technology Licensing, Llc | Augmented reality light guide display |

| US10191515B2 (en) | 2012-03-28 | 2019-01-29 | Microsoft Technology Licensing, Llc | Mobile device light guide display |

| US9717981B2 (en) | 2012-04-05 | 2017-08-01 | Microsoft Technology Licensing, Llc | Augmented reality and physical games |

| US10502876B2 (en) | 2012-05-22 | 2019-12-10 | Microsoft Technology Licensing, Llc | Waveguide optics focus elements |

| US8989535B2 (en) | 2012-06-04 | 2015-03-24 | Microsoft Technology Licensing, Llc | Multiple waveguide imaging structure |

| US9151984B2 (en) * | 2012-06-18 | 2015-10-06 | Microsoft Technology Licensing, Llc | Active reflective surfaces |

| US10192358B2 (en) | 2012-12-20 | 2019-01-29 | Microsoft Technology Licensing, Llc | Auto-stereoscopic augmented reality display |

| US9304235B2 (en) | 2014-07-30 | 2016-04-05 | Microsoft Technology Licensing, Llc | Microfabrication |

| US10678412B2 (en) | 2014-07-31 | 2020-06-09 | Microsoft Technology Licensing, Llc | Dynamic joint dividers for application windows |

| US10592080B2 (en) | 2014-07-31 | 2020-03-17 | Microsoft Technology Licensing, Llc | Assisted presentation of application windows |

| US10254942B2 (en) | 2014-07-31 | 2019-04-09 | Microsoft Technology Licensing, Llc | Adaptive sizing and positioning of application windows |

| US10018844B2 (en) | 2015-02-09 | 2018-07-10 | Microsoft Technology Licensing, Llc | Wearable image display system |

| US9827209B2 (en) | 2015-02-09 | 2017-11-28 | Microsoft Technology Licensing, Llc | Display system |

| US9429692B1 (en) | 2015-02-09 | 2016-08-30 | Microsoft Technology Licensing, Llc | Optical components |

| US9423360B1 (en) | 2015-02-09 | 2016-08-23 | Microsoft Technology Licensing, Llc | Optical components |

| US9535253B2 (en) | 2015-02-09 | 2017-01-03 | Microsoft Technology Licensing, Llc | Display system |

| US11086216B2 (en) | 2015-02-09 | 2021-08-10 | Microsoft Technology Licensing, Llc | Generating electronic components |

| US10317677B2 (en) | 2015-02-09 | 2019-06-11 | Microsoft Technology Licensing, Llc | Display system |

| US9513480B2 (en) | 2015-02-09 | 2016-12-06 | Microsoft Technology Licensing, Llc | Waveguide |

| US9372347B1 (en) | 2015-02-09 | 2016-06-21 | Microsoft Technology Licensing, Llc | Display system |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3078554B2 (ja) * | 1989-11-08 | 2000-08-21 | セイコーエプソン株式会社 | 反射型液晶表示装置 |

| JP2655941B2 (ja) * | 1991-01-30 | 1997-09-24 | シャープ株式会社 | アクティブマトリクス型液晶表示装置およびその製造方法 |

| JP3738530B2 (ja) | 1997-06-30 | 2006-01-25 | ソニー株式会社 | カラー表示装置 |

| JPH1164885A (ja) * | 1997-08-21 | 1999-03-05 | Sharp Corp | アクティブマトリクス基板 |

| JP2001305523A (ja) * | 2000-04-18 | 2001-10-31 | Toshiba Corp | アレイ基板の製造方法 |

| JP3793402B2 (ja) * | 2000-07-28 | 2006-07-05 | 株式会社日立製作所 | カラー液晶表示装置 |

| JP2002169166A (ja) * | 2000-12-05 | 2002-06-14 | Matsushita Electric Ind Co Ltd | 液晶表示装置およびその製造方法ならびに画像表示応用機器 |

| KR100397399B1 (ko) * | 2001-02-22 | 2003-09-13 | 엘지.필립스 엘시디 주식회사 | 반투과형 액정 표시 장치 및 그의 제조 방법 |

| KR100816333B1 (ko) * | 2001-08-30 | 2008-03-24 | 삼성전자주식회사 | 액정 표시 장치용 색 필터 기판 및 박막 트랜지스터 기판및 이들의 제조 방법 |

-

2002

- 2002-07-15 JP JP2002205768A patent/JP4170033B2/ja not_active Expired - Fee Related

-

2003

- 2003-07-14 US US10/617,755 patent/US6992738B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6992738B2 (en) | 2006-01-31 |

| US20040051829A1 (en) | 2004-03-18 |

| JP2004045970A (ja) | 2004-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4170033B2 (ja) | 液晶表示装置 | |

| US7116390B2 (en) | Electro-optical device and electronic apparatus comprising the same | |

| US10663821B2 (en) | Display board having insulating films and terminals, and display device including the same | |

| US7760277B2 (en) | Active matrix LCD panel with first and second alignment layers having respectively plural first and second grooves that extend respectively along ten and one o'clock directions thereon when viewed from above | |

| EP1008896A1 (en) | Liquid crystal display device | |

| US10001676B2 (en) | Display device | |

| US7298430B2 (en) | Liquid crystal display device | |

| US7667798B2 (en) | Liquid crystal display device | |

| JP5489267B2 (ja) | 液晶装置、電子機器 | |

| US10520761B2 (en) | Method of producing substrate having alignment mark | |

| JPH11183904A (ja) | 液晶表示装置 | |

| US10353253B2 (en) | Mounting substrate and display device | |

| JP5164672B2 (ja) | 液晶表示装置、電子機器 | |

| JP2004354553A (ja) | 液晶表示装置 | |

| JPH10325951A (ja) | 液晶表示装置 | |

| KR101995778B1 (ko) | 액정표시장치 | |

| JP4196609B2 (ja) | 電気光学装置及び電子機器 | |

| US7508480B2 (en) | Liquid crystal display device with dummy portions | |

| JP2000035573A (ja) | 液晶表示装置 | |

| KR20070071753A (ko) | 액정표시모듈 | |

| JP4967516B2 (ja) | 電気光学装置及び電子機器 | |

| JP2006350168A (ja) | 液晶装置及びその製造方法、並びに電子機器 | |

| JP2000089223A (ja) | 液晶表示装置 | |

| JPH11194336A (ja) | 液晶表示装置 | |

| JPH04260021A (ja) | 液晶表示装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050203 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050203 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070123 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070323 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071002 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080408 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080805 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080806 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313121 Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120815 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120815 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130815 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |