JP4155209B2 - マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ - Google Patents

マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ Download PDFInfo

- Publication number

- JP4155209B2 JP4155209B2 JP2004049133A JP2004049133A JP4155209B2 JP 4155209 B2 JP4155209 B2 JP 4155209B2 JP 2004049133 A JP2004049133 A JP 2004049133A JP 2004049133 A JP2004049133 A JP 2004049133A JP 4155209 B2 JP4155209 B2 JP 4155209B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- input

- output

- vibrator

- input electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

Description

Claims (6)

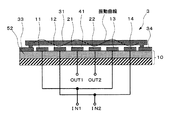

- 信号を入力する入力電極と、

信号を出力する出力電極と、

前記入力電極および前記出力電極に対して空間を介して対向する振動子と

を備えたマイクロ電気機械システムの共振器において、

前記入力電極に平衡で信号が入力され、

前記出力電極は平衡で信号が出力され、

前記入力電極は第1入力電極と第2入力電極とからなり、

前記出力電極は第1出力電極と第2出力電極とからなり、

前記第1入力電極と前記第1出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるように配置され、

第2入力電極と第2出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相の位置でかつ前記第1入力電極の位置における前記振動子の振幅の位相とは180度異なる位相となるように配置されている

ことを特徴とするマイクロ電気機械システムの共振器。 - 前記第1入力電極、前記第2出力電極、前記第1出力電極、前記第2入力電極の順に配置されている

ことを特徴とする請求項1記載のマイクロ電気機械システムの共振器。 - 前記第1入力電極、前記第2入力電極、前記第1出力電極、前記第2出力電極の順に配置されている

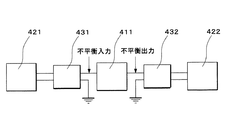

ことを特徴とする請求項1記載のマイクロ電気機械システムの共振器。 - 前記入力電極は複数個の入力電極からなり、

前記出力電極は複数個の出力電極からなり、

前記各入力電極のうちの第1入力電極と前記各出力電極のうちの第1出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるように配置され、

前記各入力電極のうちの第2入力電極と前記各出力電極のうちの第2出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるようにかつ前記第1入力電極の位置における前記振動子の振幅の位相とは180度異なる位相となるように配置され、

前記入力電極のうち残りの入力電極は前記第1入力電極もしくは前記第2入力電極の位置における前記振動子の振幅の位相と同位相となるように配置され、

前記出力電極のうち残りの出力電極は前記第1出力電極もしくは前記第2出力電極の位置における前記振動子の振幅の位相と同位相となるように配置される

ことを特徴とする請求項1記載のマイクロ電気機械システムの共振器。 - 信号を入力する入力電極と、

信号を出力する出力電極と、

前記入力電極および前記出力電極に対して空間を介して対向する振動子と

を備えたマイクロ電気機械システムの共振器の製造方法において、

前記入力電極と前記出力電極とは同時に形成され、

前記入力電極には第1入力電極と第2入力電極とを形成し、

前記出力電極には第1出力電極と第2出力電極とを形成し、

前記第1入力電極と前記第1出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるように配置され、

第2入力電極と第2出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるようにかつ前記第1入力電極の位置における前記振動子の振幅の位相とは180度異なる位相となるように配置される

ことを特徴とするマイクロ電気機械システムの共振器の製造方法。 - 信号を入力する入力電極と、

信号を出力する出力電極と、

前記入力電極および前記出力電極に対して空間を介して対向する振動子と

を備えたマイクロ電気機械システムの共振器を備えた周波数フィルタにおいて、

前記入力電極に平衡で信号が入力され、前記出力電極は平衡で信号が出力され、

前記入力電極は第1入力電極と第2入力電極とからなり、

前記出力電極は第1出力電極と第2出力電極とからなり、

前記第1入力電極と前記第1出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相となるように配置され、

第2入力電極と第2出力電極とはそれぞれの位置における前記振動子の振幅の位相が同位相の位置でかつ前記第1入力電極の位置における前記振動子の振幅の位相とは180度異なる位相となるように配置されている

ことを特徴とする周波数フィルタ。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004049133A JP4155209B2 (ja) | 2004-02-25 | 2004-02-25 | マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ |

| US10/571,723 US20070010227A1 (en) | 2003-09-19 | 2004-09-17 | Micro electric machine system resonator, drive method thereof, manufacturing method thereof, and frequency filter |

| TW093128108A TWI291450B (en) | 2003-09-19 | 2004-09-17 | Resonator for micro-electro-mechanical system, (MEMS), its driving method and frequency filter |

| PCT/JP2004/014010 WO2005029700A1 (ja) | 2003-09-19 | 2004-09-17 | マイクロ電気機械システムの共振器およびその駆動方法およびその製造方法および周波数フィルタ |

| KR1020067005369A KR20060065720A (ko) | 2003-09-19 | 2004-09-17 | 마이크로 전기 기계 시스템의 공진기 및 그 구동 방법 및그 제조 방법 및 주파수 필터 |

| EP04773394A EP1667323A1 (en) | 2003-09-19 | 2004-09-17 | Micro electric machine system resonator, drive method thereof, manufacturing method thereof, and frequency filter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004049133A JP4155209B2 (ja) | 2004-02-25 | 2004-02-25 | マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005244406A JP2005244406A (ja) | 2005-09-08 |

| JP4155209B2 true JP4155209B2 (ja) | 2008-09-24 |

Family

ID=35025701

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004049133A Expired - Fee Related JP4155209B2 (ja) | 2003-09-19 | 2004-02-25 | マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4155209B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4736735B2 (ja) * | 2005-11-15 | 2011-07-27 | ソニー株式会社 | 静電容量型共振素子、静電容量型共振素子の製造方法および通信装置 |

| JP2007150736A (ja) | 2005-11-28 | 2007-06-14 | Sony Corp | 微小電気機械デバイス |

-

2004

- 2004-02-25 JP JP2004049133A patent/JP4155209B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005244406A (ja) | 2005-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7312674B2 (en) | Resonator system with a plurality of individual mechanically coupled resonators and method of making same | |

| TWI291450B (en) | Resonator for micro-electro-mechanical system, (MEMS), its driving method and frequency filter | |

| WO2007000929A1 (ja) | 圧電共振器、圧電フィルタ、それを用いた共用器及び通信機器 | |

| JP4908156B2 (ja) | 薄膜圧電振動子及び薄膜圧電バルク波共振器及びそれを用いた高周波フィルタ | |

| US7755454B2 (en) | Micro-electromechanical device | |

| CN111490740A (zh) | 阵列化的分布式兰姆模态射频微机电谐振器 | |

| US7498901B2 (en) | Filter device and transmitter-receiver utilizing beam-structured micro-resonators | |

| JP4581658B2 (ja) | 微小共振器、周波数フィルタ及び通信装置 | |

| JP3982182B2 (ja) | 弾性表面波装置及びその製造方法 | |

| CN100517964C (zh) | 微振子、半导体装置以及通信装置 | |

| JP4341288B2 (ja) | Mems型共振器及びその製造方法、並びにフィルタ | |

| JP4254445B2 (ja) | マイクロ電気機械システムの共振器およびその駆動方法 | |

| JP4155209B2 (ja) | マイクロ電気機械システムの共振器およびその製造方法および周波数フィルタ | |

| JP2005142852A (ja) | Mems共振器 | |

| JP2008177933A (ja) | 電気機械素子、並びに信号処理デバイス、通信装置 | |

| JP4710435B2 (ja) | 微小共振器、バンドパスフィルタ、半導体装置、並びに通信装置 | |

| JP4040475B2 (ja) | マイクロメカニカルフィルタ及び携帯型情報端末 | |

| JP2007013447A5 (ja) | ||

| JP4389518B2 (ja) | マイクロ電気機械システムの共振器およびその調整方法 | |

| JP2005072757A (ja) | マイクロ電気機械システムの共振器およびその駆動方法 | |

| KR100393774B1 (ko) | 박막 벌크 어쿠스틱 공진기를 이용한 대역통과필터 제조방법 | |

| Zuo et al. | Novel electrode configurations in dual-layer stacked and switchable ALN contour-mode resonators for low impedance filter termination and reduced insertion loss | |

| JP2005192146A (ja) | Mems共振器及びその作製方法 | |

| JP2005311568A (ja) | フィルタ装置及び送受信機 | |

| JP2007142532A (ja) | 静電容量型共振素子、静電容量型共振素子の製造方法および通信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071120 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080617 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080630 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110718 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110718 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |