JP4068594B2 - フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 - Google Patents

フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 Download PDFInfo

- Publication number

- JP4068594B2 JP4068594B2 JP2004172262A JP2004172262A JP4068594B2 JP 4068594 B2 JP4068594 B2 JP 4068594B2 JP 2004172262 A JP2004172262 A JP 2004172262A JP 2004172262 A JP2004172262 A JP 2004172262A JP 4068594 B2 JP4068594 B2 JP 4068594B2

- Authority

- JP

- Japan

- Prior art keywords

- address

- data

- flash memory

- buffer

- physical

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

複数個の物理ページを含む物理ブロック単位で記憶データの消去が行われるフラッシュメモリに対するアクセスを制御するメモリコントローラであって、

前記フラッシュメモリに書き込むデータ又は前記フラッシュメモリから読み出されたデータを保持する手段であって、ホストシステムのメモリアドレス空間に割り当てられているバッファと、

ホストシステム側から、該ホストシステムのメモリアドレス空間におけるアクセス単位で、前記バッファにランダムアクセスできるように制御し、さらに、前記ホストシステム側から与えられる複数ビットのアドレスを所定の上位側ビットと下位側ビットに分離し、該上位側ビットに基づいて前記バッファに保持されているデータがアクセス対象のデータに該当するか否かを判別し、該下位側ビットに基づいて前記バッファ内のアクセス領域を識別するホストインタフェース制御手段と、

前記ホストシステム側から与えられるアクセス対象の論理ページを特定するための論理ページアドレスが保持されるアドレス保持手段と、

複数の前記論理ページを含む論理ブロックに付けられたアドレスである論理ブロックアドレスと、前記物理ブロックに付けられたアドレスである物理ブロックアドレスとの対応関係を管理するアドレス管理手段と、

前記アドレス保持手段に保持されている前記論理ページアドレスの前記論理ブロックアドレスに対応する所定の上位側ビット部分を、該論理ブロックアドレスと対応する前記物理ブロックアドレスに置き換えた物理ページアドレスを生成するアドレス生成手段と、

前記アドレス生成手段によって生成された前記物理ページアドレスに対応する前記物理ページにデータを書き込むための前記バッファから前記フラッシュメモリへの512バイト単位のデータ転送と、前記アドレス生成手段によって生成された前記物理ページアドレスに対応する前記物理ページからデータを読み出すための前記フラッシュメモリから前記バッファへの512バイト単位のデータ転送とを制御するフラッシュメモリインタフェース制御手段と、

を備えることを特徴とする。

複数個の物理ページを含む物理ブロック単位で記憶データの消去が行われるフラッシュメモリに対するアクセスを制御するフラッシュメモリの制御方法であって、

アクセス対象の論理ページを特定するための論理ページアドレスが保持されるアドレス保持手段に、ホストシステム側から与えられる複数ビットの前記論理ページアドレスを保持する論理ページアドレス保持ステップと、

複数の前記論理ページを含む論理ブロックに付けられたアドレスである論理ブロックアドレスと、前記物理ブロックに付けられたアドレスである物理ブロックアドレスとの対応関係を管理するアドレス管理ステップと、

前記アドレス保持手段に保持されている前記論理ページアドレスの前記論理ブロックアドレスに対応する所定の上位側ビット部分を、該論理ブロックアドレスと対応する前記物理ブロックアドレスに置き換えた物理ページアドレスを生成するアドレス生成ステップと、

512バイトの転送単位で、前記アドレス生成ステップで生成された前記物理ページアドレスに対応する前記物理ページに書き込まれるデータ又は前記アドレス生成ステップで生成された前記物理ページアドレスに対応する前記物理ページから読み出されたデータを保持するバッファと前記フラッシュメモリとの間でのデータ転送を制御するデータ転送ステップと、

ホストシステム側から与えられる複数ビットのアドレスを所定の上位側ビットと下位側ビットに分離し、前記上位側ビットに基づいて、前記バッファに保持されているデータがアクセス対象のデータに該当するか否かを判別し、前記下位側ビットに基づいて前記バッファ内のアクセス領域を識別する識別ステップと、

前記ホストシステム側から、該ホストシステムのメモリアドレス空間におけるアクセス単位で、前記バッファにランダムアクセスできるように制御するアクセス制御ステップとを有し、

前記バッファは、前記ホストシステムのメモリアドレス空間に割り当てられていることを特徴とする。

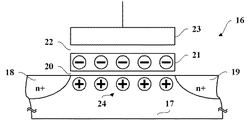

図2及び図3に示されているように、メモリセル16は、P型半導体基板17と、N型ソース拡散領域18と、N型ドレイン拡散領域19と、トンネル酸化膜20と、フローティングゲート電極21と、絶縁膜22と、コントロールゲート電極23とを含んでいる。

バッファ9は、フラッシュメモリ2から読み出されたデータ及びフラッシュメモリ2に書き込まれるべきデータを、保持するための機能ブロックである。フラッシュメモリ2から読み出されたデータは、ホストコンピュータ4に出力されるまで、バッファ9に保持される。フラッシュメモリ2に書き込まれるべきデータは、フラッシュメモリ2のデータ書込動作の準備ができるまで、バッファ9に保持される。

ECCブロック11は、フラッシュメモリ2への書込データに付加されるエラーコレクションコードを生成するための機能ブロックである。加えて、ECCブロック11は、フラッシュメモリ2から読み出されたデータに含まれるエラーコレクションコードに基づいて、読出データに含まれる誤りの検出及び訂正を行う。

図5は、フラッシュメモリ2のメモリ空間31におけるブロック及びページの割当例を概略的に示している。図5に示されているように、メモリ空間31は、各々がデータ消去動作における一括処理単位である複数のブロック31a(B0000〜B1023)に分割されている。各ブロック31aは、各々がデータ読出動作及びデータ書込動作における一括処理単位である複数のページ31b(P00〜P31)に分割されている。各ページ31bは、各々が1バイトである512個のデータ領域(A000〜A511)に分割されている。

バッファ9のバッファ空間32は、ホストコンピュータ4のメモリアドレス空間38において、512バイトを有するメモリ領域(M10000〜M10511)に割り付けられている。ホストコンピュータ4のメモリアドレス空間38には、ポインタレジスタ33及びジョブレジスタ34にアクセスするためのアドレスが含まれている。メモリアドレス空間38にてポインタレジスタ33及びジョブレジスタ34に割り当てられるアドレスは、ポインタレジスタ33及びジョブレジスタ34のデータ容量に応じて、適宜設定されていればよい。ホストコンピュータ4にてポインタレジスタ33及びジョブレジスタ34に割り当てられるアドレスは、ホストコンピュータ4のI/Oアドレス空間に含まれていてもよい。

2、31 フラッシュメモリ

3 コントローラ

4、35 ホストコンピュータ

5 ホストインタフェース制御ブロック

6 マイクロプロセッサ

7 ホストインタフェースブロック

8 ワークエリア

9,32 バッファ

10 フラッシュメモリインタフェースブロック

11 ECCブロック

12 フラッシュシーケンサブロック

13 外部バス

14 内部バス

16 メモリセル

17 P型半導体基板

18 N型ソース拡散領域

19 N型ドレイン拡散領域

20 トンネル酸化膜

21 フローティングゲート電極

22 絶縁膜

23 コントロールゲート電極

24 チャネル

25 データ領域

26 冗長領域

33 ポインタレジスタ

34 ジョブレジスタ

36 アドレスカウンタ

37 アドレスバッファ

38 メモリアドレス空間

Claims (3)

- 複数個の物理ページを含む物理ブロック単位で記憶データの消去が行われるフラッシュメモリに対するアクセスを制御するメモリコントローラであって、

前記フラッシュメモリに書き込むデータ又は前記フラッシュメモリから読み出されたデータを保持する手段であって、ホストシステムのメモリアドレス空間に割り当てられているバッファと、

ホストシステム側から、該ホストシステムのメモリアドレス空間におけるアクセス単位で、前記バッファにランダムアクセスできるように制御し、さらに、前記ホストシステム側から与えられる複数ビットのアドレスを所定の上位側ビットと下位側ビットに分離し、該上位側ビットに基づいて前記バッファに保持されているデータがアクセス対象のデータに該当するか否かを判別し、該下位側ビットに基づいて前記バッファ内のアクセス領域を識別するホストインタフェース制御手段と、

前記ホストシステム側から与えられるアクセス対象の論理ページを特定するための論理ページアドレスが保持されるアドレス保持手段と、

複数の前記論理ページを含む論理ブロックに付けられたアドレスである論理ブロックアドレスと、前記物理ブロックに付けられたアドレスである物理ブロックアドレスとの対応関係を管理するアドレス管理手段と、

前記アドレス保持手段に保持されている前記論理ページアドレスの前記論理ブロックアドレスに対応する所定の上位側ビット部分を、該論理ブロックアドレスと対応する前記物理ブロックアドレスに置き換えた物理ページアドレスを生成するアドレス生成手段と、

前記アドレス生成手段によって生成された前記物理ページアドレスに対応する前記物理ページにデータを書き込むための前記バッファから前記フラッシュメモリへの512バイト単位のデータ転送と、前記アドレス生成手段によって生成された前記物理ページアドレスに対応する前記物理ページからデータを読み出すための前記フラッシュメモリから前記バッファへの512バイト単位のデータ転送とを制御するフラッシュメモリインタフェース制御手段と、

を備えることを特徴とするフラッシュメモリコントローラ。 - 請求項1に記載のメモリコントローラと、複数個の物理ページを含む物理ブロック単位で記憶データの消去が行われるフラッシュメモリとを備えることを特徴とするフラッシュメモリシステム。

- 複数個の物理ページを含む物理ブロック単位で記憶データの消去が行われるフラッシュメモリに対するアクセスを制御するフラッシュメモリの制御方法であって、

アクセス対象の論理ページを特定するための論理ページアドレスが保持されるアドレス保持手段に、ホストシステム側から与えられる複数ビットの前記論理ページアドレスを保持する論理ページアドレス保持ステップと、

複数の前記論理ページを含む論理ブロックに付けられたアドレスである論理ブロックアドレスと、前記物理ブロックに付けられたアドレスである物理ブロックアドレスとの対応関係を管理するアドレス管理ステップと、

前記アドレス保持手段に保持されている前記論理ページアドレスの前記論理ブロックアドレスに対応する所定の上位側ビット部分を、該論理ブロックアドレスと対応する前記物理ブロックアドレスに置き換えた物理ページアドレスを生成するアドレス生成ステップと、

512バイトの転送単位で、前記アドレス生成ステップで生成された前記物理ページアドレスに対応する前記物理ページに書き込まれるデータ又は前記アドレス生成ステップで生成された前記物理ページアドレスに対応する前記物理ページから読み出されたデータを保持するバッファと前記フラッシュメモリとの間でのデータ転送を制御するデータ転送ステップと、

ホストシステム側から与えられる複数ビットのアドレスを所定の上位側ビットと下位側ビットに分離し、前記上位側ビットに基づいて、前記バッファに保持されているデータがアクセス対象のデータに該当するか否かを判別し、該下位側ビットに基づいて前記バッファ内のアクセス領域を識別する識別ステップと、

前記ホストシステム側から、該ホストシステムのメモリアドレス空間におけるアクセス単位で、前記バッファにランダムアクセスできるように制御するアクセス制御ステップとを有し、

前記バッファは、前記ホストシステムのメモリアドレス空間に割り当てられていることを特徴とするフラッシュメモリの制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004172262A JP4068594B2 (ja) | 2003-06-10 | 2004-06-10 | フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003165656 | 2003-06-10 | ||

| JP2004172262A JP4068594B2 (ja) | 2003-06-10 | 2004-06-10 | フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005025733A JP2005025733A (ja) | 2005-01-27 |

| JP2005025733A5 JP2005025733A5 (ja) | 2007-03-15 |

| JP4068594B2 true JP4068594B2 (ja) | 2008-03-26 |

Family

ID=34196947

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004172262A Expired - Fee Related JP4068594B2 (ja) | 2003-06-10 | 2004-06-10 | フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4068594B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4670370B2 (ja) * | 2005-01-28 | 2011-04-13 | Tdk株式会社 | メモリコントローラ及びフラッシュメモリシステム |

| KR100706246B1 (ko) * | 2005-05-24 | 2007-04-11 | 삼성전자주식회사 | 읽기 성능을 향상시킬 수 있는 메모리 카드 |

| JP2010277352A (ja) * | 2009-05-28 | 2010-12-09 | Toshiba Corp | メモリシステム |

-

2004

- 2004-06-10 JP JP2004172262A patent/JP4068594B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005025733A (ja) | 2005-01-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9075740B2 (en) | Memory system | |

| US7006383B2 (en) | Nonvolatile semiconductor memory for management of a number of data writer/erase times | |

| US20030033567A1 (en) | Memory card and memory controller | |

| JPH06111589A (ja) | 一括消去型不揮発性半導体記憶装置 | |

| JP2008524705A (ja) | スクラッチパッドブロック | |

| JP2006018373A (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2012058770A (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| US7606993B2 (en) | Flash memory controller, memory control circuit, flash memory system, and method for controlling data exchange between host computer and flash memory | |

| JP4661191B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4068594B2 (ja) | フラッシュメモリコントローラ、フラッシュメモリシステム、及びフラッシュメモリの制御方法 | |

| JP2012068765A (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| JP4433792B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP2008123241A (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| JP4582078B2 (ja) | メモリコントローラ及びフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| JP4177292B2 (ja) | メモリンコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP3934659B1 (ja) | メモリコントローラ及びフラッシュメモリシステム | |

| JP2005292925A (ja) | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4177301B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4419525B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4332108B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2012037971A (ja) | メモリコントローラ及びメモリコントローラを備える不揮発性メモリシステム、並びに不揮発性メモリの制御方法 | |

| JP4222879B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP2006048746A (ja) | メモリカード | |

| JP4251950B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4561110B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070130 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070322 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070327 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071009 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071030 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080108 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080110 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110118 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4068594 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110118 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120118 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120118 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130118 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130118 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140118 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |