JP4055831B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4055831B2 JP4055831B2 JP35895596A JP35895596A JP4055831B2 JP 4055831 B2 JP4055831 B2 JP 4055831B2 JP 35895596 A JP35895596 A JP 35895596A JP 35895596 A JP35895596 A JP 35895596A JP 4055831 B2 JP4055831 B2 JP 4055831B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- film

- crystalline silicon

- crystal growth

- nickel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本明細書で開示する発明は、結晶性を有する薄膜半導体を利用した半導体装置およびその作製方法に関する。

【0002】

【従来の技術】

薄膜トランジスタ(TFT)は、基板上に珪素膜を成膜し作製された半導体装置で、アクティブマトリクス型液晶表示装置などの電気光学装置に利用されている。

【0003】

特に、結晶性を有する半導体よりなるポリシリコンTFTは、非晶質半導体よりなるアモルファスTFTに比べ電界効果移動度が大きいので、ポリシリコンを用いて液晶表示装置のアクティブマトリクス回路と周辺駆動回路とを同一基板上に形成することが行われている。

【0004】

ポリシリコンTFTには、高温ポリシリコンTFTと低温ポリシリコンTFTがある。

【0005】

高温ポリシリコンTFTは、結晶性珪素膜の作製手段として、800℃や900℃以上というような比較的高温の加熱処理を利用する技術を利用して得られる。しかし、高温ポリシリコンが作製される基板としては、上記加熱処理の温度に耐える、高価な石英基板しか利用できない。

【0006】

一方、低温ポリシリコンTFTは、安価なガラス基板上に、ガラス基板が耐えうる600℃以下の加熱や、ガラス基板に対して熱ダメージのほとんど無いレーザーアニール技術を利用して、結晶性珪素膜を形成することにより得られる。

【0007】

現状において、高温ポリシリコンTFTも低温ポリシリコンTFTもその特性に大きな違いはなく、移動度が50〜100(cm2/Vs)程度、S値が200〜400(mV/dec)(VD =1V)程度のものが得られている。

【0008】

しかし、周辺駆動回路のソースドライバー回路は、十数MHz以上の動作が必要とされ、現状における高温ポリシリコンTFTおよび低温ポリシリコンTFTで構成した回路は、その動作速度のマージンが数MHz程度しかとれない。

【0009】

従って、現状では、動作を分割する(分割駆動という)などをして、液晶表示装置を構成している。しかし、この方法は、分割のタイミングの微妙なズレ等により、画面に縞模様が現れる等の問題がある。

【0010】

そこで、特願平8−327978に開示されたTFTがある。それは、所定の方向に連続性を有する結晶構造を有し、かつ前記所定の方向に延在した結晶粒界を有する結晶性珪素膜を用いたTFTで、S値が100(mV/dec)以下、移動度が200(cm2/Vs)以上という優れた特性を持つものである。

【0011】

従って、このTFTを用いることにより、数十MHz以上といった高速動作が可能な周辺回路を得ることができる。

【0012】

【発明が解決しようとする課題】

上記出願に記載された技術を要約すると、

(1)非晶質珪素膜の表面の一部の領域にニッケルなどの金属元素を接して保持させた状態で加熱処理を施すことにより、前記一部の領域から他の領域へと基板に平行な方向への結晶成長を行わせる。

【0013】

(2)ハロゲン元素を含んだ雰囲気中で加熱処理することにより熱酸化膜を形成する。

【0014】

(3)前記熱酸化膜を除去する。

【0015】

(4)ゲイト絶縁膜として熱酸化膜を再度形成する。

【0016】

このようにして得られた結晶性珪素膜を用いてTFTを作製する場合、結晶構造の連続性が延在している方向と、ソース領域とドレイン領域とを結ぶ方向とを概略一致させることが好ましい。

【0017】

それは、TFTの動作において、キャリアが最も移動しやすい構造になっているからである。すなわち、この結晶構造の連続性が延在している方向は、格子構造の連続性がほぼ保たれ、キャリアの移動に際しての散乱やトラップが他の方向に比較して非常に少ないのである。

【0018】

このように、結晶構造の連続性が延在している方向とキャリアの移動の方向とをどのようにとるかにより、作製されるTFTの特性が決定され、両方向が概略一致するとき移動度の大きいTFTを得ることができる。

【0019】

したがって、高速動作の要求される回路を前記TFTを用いて作製する場合、前記ニッケルなどの金属元素を添加する領域に対する、TFTのソース領域とドレイン領域とを結ぶ方向(動作時にキャリアが移動する方向)を考慮して配置するように回路を設計することが重要となる。

【0020】

すなわち、結晶成長は、ニッケル元素が添加された領域から周囲に向かって、基板に平行な方向に進行する。この方向が結晶構造の連続性が延在している方向であり、この方向とTFTのソース領域とドレイン領域とを結ぶ方向とを概略一致するように、TFTを配置することが必要とされる。

【0021】

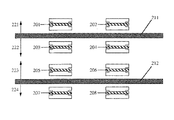

上記のようにニッケル添加領域とTFTを基板上に配置するパターンとしては、図2に示すような配置が考えられる。

【0022】

図2において、TFT201〜208はニッケル添加領域211または212の脇に配置され、各TFTの活性層はその最も近い位置に配置されたニッケル添加領域から成長した結晶性珪素膜(結晶成長領域)を用いて構成される。なお、221〜224で示す矢印は結晶成長の方向である。

【0023】

しかし、結晶成長の距離はニッケル添加領域間の距離に依存し、ニッケル添加領域間の距離が長いほど結晶成長の距離は短いという傾向がある。この成長距離の違いがTFTの特性に影響する。

【0024】

液晶表示装置には、同種の回路が多数内蔵されている。数百×数百もの画素を同じように駆動させるには、これら多数の同種回路が同じように動作しなくてはならない。したがって、各回路を構成するTFTの特性をそろえる必要がある。

【0025】

特にニッケル添加領域に挟まれていない領域に形成されたTFT201、202、207、208については、活性層に用いる珪素膜の結晶成長の距離が十分でない場合、あるいは結晶性が十分でない場合がある。この場合、TFT201、202、207、208の移動度が十分でなくなる。

【0026】

即ち、TFT201と203を比較すると、同じチャネル導電型で同じ寸法であっても、203の方が結晶性が良好なことを反映してそれだけ高速動作に適した特性となり、他方201の方は結晶性が良好でないことを反映して高速動作に適さない特性となる傾向が生じてしまう。

【0027】

このようなTFTを用いて、高速動作が必要な回路を作製した場合、素子特性のバランスの悪さに起因して、十分な動作速度を得ることができないという場合がある。

【0028】

本明細書で開示する発明は、上記結晶成長の違いを是正し、ニッケル添加を利用して作製した結晶性珪素膜を用いて、特性のそろったTFTを提供することを課題とする。特に、ニッケル添加領域に挟まれていない領域の結晶成長状態を改善する技術を提供することを課題とする。

【0029】

【課題を解決するための手段】

本明細書で開示する発明の一つは、

絶縁表面を有する基板上に非晶質珪素膜を成膜する工程と、

前記非晶質珪素膜の複数の領域に珪素の結晶化を助長する金属元素を選択的に導入する工程と、

加熱処理を施し、前記金属元素が選択的に導入された複数の領域から基板に平行な方向に結晶成長を行わせる工程と、

を有する半導体装置の作製方法において、

前記金属元素が選択的に導入された領域の少なくとも1つは、素子形成には利用されず、他の金属元素が選択的に導入された領域からの結晶成長状態を制御するために設けられることを特徴とする。

【0030】

上記構成において、珪素の結晶化を助長する金属元素として、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複数種類のものを利用することができる。

【0031】

特に高い効果が得られ、かつ高い再現性が得られる元素としては、ニッケル(Ni)を挙げることができる。

【0032】

上記構成において、金属元素の導入はイオン注入法、または金属元素が溶解または分散された溶液を塗布して行うことが好ましい。

【0033】

本明細書で開示する他の発明の一つは、

絶縁表面を有する基板上に設けられた半導体装置であって、

前記半導体装置の活性層は、珪素の結晶化を助長する金属元素が添加された複数の領域の1つから基板に平行または概略平行な方向に結晶成長された結晶性珪素膜を利用して構成されており、

前記複数の領域の他の1つから結晶成長された結晶成長領域は半導体装置の活性層として利用されていないことを特徴とする。

【0034】

【発明の実施の形態】

例えば、図1のように、等間隔にニッケル添加領域101〜104を配置し、しかも102と103の領域からの結晶成長領域を利用して薄膜トランジスタを構成する。なお、矢印121〜128は結晶成長を示す。

【0035】

このように、ニッケル添加領域101および104を配置したことにより、TFT111、112、117、118の活性層を形成する結晶性珪素膜の結晶成長距離と、TFT113〜114の活性層を形成する結晶性珪素膜の結晶成長距離とをほぼ同一にすることができる。

【0036】

このとき、ニッケル添加領域101および104は、非晶質珪素膜を結晶化する目的で設けられているのではない。このニッケル添加領域101及び104は、結晶成長123および126の距離、及び結晶成長状態を124や125と同じ状態とするために設けられている。即ち、最終的には利用されないが、他の結晶成長領域の結晶状態を制御するためのダミーの領域として設けられている。

【0037】

従って、ニッケル添加領域101および104から結晶成長が進行した領域は素子形成には利用されない。

【0038】

ここで重要なのは、ニッケル添加領域101および104からの結晶成長を行わせることで、他の素子形成に利用される結晶成長領域に意図した好ましい影響を与えることにある。

【0039】

換言すれば、ニッケル添加領域101および104からの結晶成長を行わせることで、他の素子形成に利用される結晶成長領域の結晶成長状態を制御することにある。

【0040】

このように、ダミーのニッケル添加領域101、104を設けることにより、111〜118で示されるTFTを形成するための結晶性珪素膜の領域の結晶成長の距離、及び結晶状態をコントロールし、TFTの特性をそろえることができる。

【0041】

なお、このとき、各ニッケル添加領域間の間隔はそろえるほうが好ましい。これは、ニッケル添加領域の幅によっても結晶成長距離は変化し、設計パラメータが増えてしまうからである。

【0042】

【実施例】

[実施例1]

本実施例では、所定の方向に連続性を有する結晶構造を有し、かつ前記所定の方向に延在した結晶粒界を有する結晶性珪素膜を用いたTFTの作製工程について、ニッケル添加領域との配置関係と絡めて述べる。

【0043】

図3〜図5に本実施例の作製工程を示す。まず、石英基板301上に下地膜302として酸化珪素膜を3000Åの厚さに形成する。なお、石英基板の表面の平滑性が良く、また洗浄を十分に行うのであれば、この下地膜302は必要ない。

【0044】

なお、基板としては石英基板を利用することが現状としては好ましいが、加熱処理温度に耐える基板であれば、石英に限定されるものではない。

【0045】

次に結晶性珪素膜の出発膜となる非晶質珪素膜303を減圧熱CVD法で500Åの厚さに成膜する。

【0046】

次に図示しない酸化珪素膜を1500Åの厚さに成膜し、それをパターニングすることにより304で示されるマスクを形成する。このマスクは305〜307で示される領域に開口が形成されている。この開口305〜307が形成されている領域においては非晶質珪素膜303が露出する。

【0047】

なお、開口307は、ダミーのニッケル添加領域用の開口である。

【0048】

開口305〜307は、紙面の表から裏方向に長手方向を有する細長い長方形を有している。これら開口の幅は20μm以上とするのが適当である。またその長手方向の長さは必要とする長さで形成すれよい。

【0049】

次に重量換算で10ppmのニッケル元素を含んだ酢酸ニッケル溶液を塗布する。そして図示しないスピナーを用いてスピンドライを行い、余分な溶液を除去する。ニッケル元素の導入量は、上記溶液中におけるニッケル元素の含有濃度で制御することができる。

【0050】

こうして、ニッケル元素が図3(A)の点線308で示されるような状態で存在した状態が得られる。この状態では、ニッケル元素が開口305〜307の底部において、非晶質珪素膜の一部に選択的に保持された状態が得られる。

【0051】

なお、ニッケル元素の導入をイオン注入法を用いて行ってもよい。この場合、ニッケル元素の溶液を塗布する場合に比較して、ニッケル元素の導入位置をより精度よく制御することができる。したがって、ニッケル元素の導入領域の幅が数μmあるいはそれ以下の極めて狭い場合や、導入領域の形状が複雑な場合に特に有効である。

【0052】

次に水素を3%含有した極力酸素を含まない窒素雰囲気中(または窒素雰囲気中)において、500℃〜630℃、例えば600℃、8時間の加熱処理を行う。すると、図3(A)の309で示されるような、基板301に平行な方向への結晶成長が進行する。

【0053】

この結晶成長は、ニッケル元素が導入された開口305〜307の領域から周囲に向かって進行する。この基板に平行な方向への結晶成長を横成長またはラテラル成長と称する。

【0054】

次にニッケル元素を選択的に導入するための酸化珪素膜でなるマスク304を除去する。

【0055】

この状態においては、ニッケル元素が珪素膜中に偏在している。特に開口305〜307が形成されていた領域と、結晶成長の先端部および結晶成長のぶつかる領域においては、ニッケル元素が比較的高濃度に存在している。

【0056】

したがって、活性層の形成においては、それらの領域を避けることが重要となる。即ち、活性層中に上記ニッケル元素が偏在した領域が存在しないようにする。

【0057】

結晶化の後、さらにレーザー光の照射を行ってもよい。即ち、レーザー光の照射により、さらに結晶化を助長させてもよい。このレーザー光の照射は、膜中に存在するニッケル元素の固まりを分散させ、後にニッケル元素を除去しやすくする効果を有している。なお、この段階でレーザー光の照射を行っても、さらに横成長が進行することはない。

【0058】

レーザー光としては、紫外領域の波長を有するエキシマーレーザーを利用することができる。例えば、KrFエキシマーレーザー(波長248nm)やXeClエキシマーレーザー(波長308nm)を利用することができる。

【0059】

次にハロゲン元素を含んだ酸素雰囲気、例えばHClを3体積%含んだ酸素雰囲気中において、950℃の加熱処理を行い、図示しない熱酸化膜を200Åの厚さに成膜する。この熱酸化膜の形成に伴い、珪素膜の膜厚は100Å程度減少する。即ち、珪素膜の膜厚は400Å程度となる。

【0060】

一般に、珪素膜の表面に形成される熱酸化膜は、表面に盛り上がる厚さと内部に進行する酸化の距離とがほぼ同じものとなる。したがって、例えば100Åの珪素膜の表面に100Åの熱酸化膜を形成すると、珪素膜の厚さは50Å目減りし、50Å厚の珪素膜とその表面に形成された100Å厚の熱酸化膜という構成となる。

【0061】

上記工程においては、熱酸化膜の形成に伴い、膜中の不安定な結合状態を有する珪素元素が熱酸化膜の形成に利用される。そして、膜中の欠陥が減少し、より高い結晶性を得ることができる。

【0062】

また同時に熱酸化膜の形成およびハロゲン元素、ここでは塩素の作用により膜中よりニッケル元素のゲッタリングが行われる。

【0063】

当然、熱酸化膜中には比較的高濃度にニッケル元素が取り込まれることになる。そして相対的に珪素膜中のニッケル元素は減少する。

【0064】

そして、この熱酸化膜を除去する。こうして、ニッケル元素の含有量を減少させた結晶性珪素膜を得る。

【0065】

こうして得られた結晶性珪素膜は一方向に結晶構造が延在した(この方向は結晶成長方向に一致する)構造を有している。即ち、複数の細長い円柱状の結晶体が複数の一方向に延在した結晶粒界を介して、平行に並んでいる構造を有している。

【0066】

次にパターンニングを行うことにより、横成長領域でなるパターン310を形成する。この島状の領域310が後にTFTの活性層になる。

【0067】

ここでは、ソース領域とドレイン領域とを結ぶ方向と結晶成長方向とが一致または概略一致するようにパターンの位置取りを行う。こうすることで、キャリアの移動する方向と結晶格子が連続して延在する方向とを合わせることができ、結果的に特性の高いTFTを得ることができる。

【0068】

そして、310でなるパターンを形成後に熱酸化膜311を300Åの厚さに成膜する。この熱酸化膜は、HClを0.1〜10体積%、例えば3体積%含有した酸素雰囲気中において、950℃の加熱処理を行うことによって得る。

【0069】

熱酸化膜311を成膜することにより、パターン(活性層となるパターン)310の膜厚は、250Åとなる。

【0070】

この工程においても、除去した熱酸化膜を成膜する場合と同様の効果を得ることができる。なお、熱酸化膜311は、TFTのゲイト絶縁膜の一部となる。

【0071】

本実施例においては、最終的に得られる結晶性珪素膜でなる活性層310の膜厚(250Å)は、第2の熱酸化膜311の膜厚(300Å)よりも薄くなる。こうすることで、所定の方向に連続性を有する結晶構造を有し、かつ前記所定の方向に延在した結晶粒界を有する結晶構造を得るための効果を得ることができる。

【0072】

この後、熱酸化膜と共にゲイト絶縁膜を構成する酸化珪素膜312を1000Åの厚さにプラズマCVD法により成膜する。(図3(B))

【0073】

最終的に珪素膜中に残留するニッケルの濃度は、現状では1×1014原子個/cm3 〜5×1018原子個/cm3 程度となるが、低いほど好ましい。熱酸化膜のゲッタリング条件を詰めれば、この濃度の上限は5×1017原子個/cm3 程度まで低減できる。この濃度の計測は、SIMS(2次イオン分析方法)を利用して計測できる。

【0074】

次にゲイト電極を形成するためのアルミニウム膜をスパッタ法で4000Åの厚さに成膜する。このアルミニウム膜中には、スカンジウムを0.2重量%含有させる。

【0075】

アルミニウム膜中にスカンジウムを含有させるのは、後の工程において、ヒロックやウィスカーが発生することを抑制するためである。ヒロックやウィスカーというのは、加熱の際のアルミニウムの異常成長に起因する針状あるいは刺状の突起部のことである。

【0076】

ゲイト電極を形成するための材料として、アルミウニム以外にタンタル(Ta)、多量にリン(P)がドープされた多結晶シリコン、タングステンのシリサイド(WSi)、またはリンドープされた多結晶シリコンとタングステンのシリサイドの積層また混成した構造としてもよい。

【0077】

アルミニウム膜を成膜したら、図示しない緻密な陽極酸化膜を形成する。この陽極酸化膜は、3%の酒石酸を含んだエチレングルコール溶液を電解溶液とし、アルミニウム膜を陽極、白金を陰極として行う。この工程においては、アルミニウム膜上に緻密な膜質を有する陽極酸化膜を100Åの厚さに成膜する。

【0078】

この図示しない陽極酸化膜は、後に形成されるレジストマスクとの密着性を向上させる役割を有している。

【0079】

この陽極酸化膜の膜厚は、陽極酸化時の印加電圧によって制御することができる。

【0080】

次にレジストマスク313を形成する。そしてこのレジストマスク313を利用して、アルミニウム膜を314で示されるパターンにパターニングする。こうして図4(C)に示す状態を得る。

【0081】

ここで再度の陽極酸化を行う。ここでは、3%のシュウ酸水溶液を電解溶液として用いる。この電解溶液中において、アルミニウムのパターン314を陽極とした陽極酸化を行うことにより、315で示される多孔質状の陽極酸化膜が形成される。

【0082】

この工程においては、上部に密着性の高いレジストマスク306が存在する関係で、アルミニウムパターンの側面に選択的に陽極酸化膜315が形成される。

【0083】

この陽極酸化膜は、その膜厚を数μmまで成長させることができる。ここでは、その膜厚を6000Åとする。なお、その成長距離は、陽極酸化時間によって制御することができる。

【0084】

そしてレジストマスク314を除去する。次に再度の緻密な陽極酸化膜の形成を行う。即ち、前述した3%の酒石酸を含んだエチレングルコール溶液を電解溶液とした陽極酸化を再び行う。

【0085】

この工程においては、多孔質状の陽極酸化膜315中に電解溶液が進入する関係から、図4(D)の316に示されるように緻密な膜質を有する陽極酸化膜が形成される。

【0086】

この緻密な陽極酸化膜316の膜厚は1000Åとする。この膜厚の制御は印加電圧によって行う。

【0087】

ここで、露呈した酸化珪素膜312をエッチングする。また同時に熱酸化膜311をエッチングする。このエッチングはドライエッチングを利用する。そして酢酸と硝酸とリン酸とを混合した混酸を用いて多孔質状の陽極酸化膜315を除去する。こうして図5(E)に示す状態を得る。

【0088】

図5(E)に示す状態を得たら、不純物イオンの注入を行う。ここでは、Nチャネル型の薄膜トランジスタを作製するためにP(リン)イオンの注入をプラズマドーピング法でもって行う。

【0089】

この工程においては、ヘビードープがされる319の領域とライトドープがされる320の領域が形成される。これは、残存した酸化珪素膜318が半透過なマスクとして機能し、注入されたイオンの一部がそこで遮蔽されるからである。

【0090】

そしてレーザー光(またはランプを用いた強光)の照射を行うことにより、不純物イオンが注入された領域の活性化を行う。こうして、ソース領域・ドレイン領域319、チャネル形成領域321、低濃度不純物領域320が自己整合的に形成される。(図5(E))

【0091】

なお、緻密な陽極酸化膜316の膜厚を2000Å以上というように厚くした場合、その膜厚でもってチャネル形成領域321の外側にオフセットゲイト領域を形成することができる。

【0092】

本実施例においてもオフットゲイト領域は形成されているが、その寸法が小さいのでその存在による寄与が小さく、また図面が煩雑になるので図中には記載していない。

【0093】

なお、緻密な膜質を有する陽極酸化膜を2000Å以上というように厚く形成するのには、200V以上の印加電圧が必要とされるので、再現性や安全性に関して、注意が必要である。

【0094】

次に層間絶縁膜322として酸化珪素膜、または窒化珪素膜、またはその積層膜を形成する。層間絶縁膜としては、酸化珪素膜または窒化珪素膜上に樹脂材料でなる層を用いてもよい。

【0095】

そしてコンタクトホールの形成を行い、ソース電極・ドレイン電極323の形成を行う。こうして図5(F)に示す薄膜トランジスタが完成する。

【0096】

本実施例に示すTFTは、その特性として従来には得られなかった極めて高いものを得ることができる。

【0097】

例えば、NTFT(Nチャネル型のTFT)で、移動度が200〜300(cm2/Vs)、S値が75〜90(mV/dec)(VD =1V)という高性能なものが得られる。PTFT(Pチャネル型のTFT)で120〜180(cm2/Vs)、S値が75〜100(mV/dec)(VD =1V)という高性能なものを得ることができる。

【0098】

特にS値は、従来の高温ポリシリコンTFT及び低温ポリシリコンTFTの値に比較して、1/2以下という驚異的に良い値である。

【0099】

そしてこのようにして作製されたTFTは、駆動信号の電圧が3.3〜5Vにおいて、リングオシレータレベルで1GHz、シフトレジスタレベルで100MHzの動作を行わすことができる。

【0100】

また、ダミーのニッケル添加領域307の存在により、TFT503の半導体層を構成する珪素膜の結晶成長の距離を十分にすることができ、上記のような特性を持つTFTにすることができる。

【0101】

さらに、各ニッケル添加領域間の間隔をそろえると、TFT501〜503の特性をそろえることができる。

【0102】

また、上述したような特異な結晶構造を有する結晶性珪素膜を利用した薄膜トランジスタは、その結晶構造に起因して短チャネル効果が現れにくいという特徴がある。また基板として絶縁体を利用するので基板の容量の問題がなく、高速動作に適するという特徴もある。

【0103】

従来の単結晶シリコンウエハーを利用したMOS型トランジスタにおいては、スケーリング則というものがあった。これは、所定に法則に従ってトランジスタに寸法を小さくすれば、これまた所定の法則に従ってトランジスタの性能が高くなるというものである。

【0104】

しかし、近年の微細化大きく進行した状態においては、このスケーリング則に従って、トランジスタの性能を高めることが困難になってきている。

【0105】

その一つに短チャネル効果を抑制するためにチャネル長を短くすればするほど、チャネルの横に不純物のドーピングをしたりする細かな工夫が必要になり、作製工程上の困難性が増大するという点を挙げることができる。

【0106】

しかし、上述した特異な結晶構造を有した結晶性珪素膜を用いた場合には、必要とする特性を上記のスケーリング則に従わない寸法で得ることができる。

【0107】

これは、以下のような事項が要因であると考えられる。

(1)チャネルにおいてキャリアの移動する方向に柱状の結晶体の延在方向を合わせることにより、短チャネル効果が抑制される。

(2)基板に絶縁体を利用することで、容量の問題が大きく抑制される。

(3)ゲイト電極にアルミニウムを利用できるので、高速動作に有利である。

【0108】

(1)については、以下にように考えることができる。即ち、一つ一つに柱状の結晶構造体は、不活性な結晶粒界により仕切られているが、この結晶粒界部分では、エネルギーにレベルが高いので、キャリアは結晶体の延在方向にその移動が寄生される。また同様な考え方により、ソース及びドレイン領域からのチャネル内部への空乏層の広がりも抑制される。このことが、短チャネル効果の抑制になっていると考えられる。

【0109】

上述したスケーリング則に従わない具体的な例としては、以下のような例を挙げることができる。

【0110】

例えば、従来にスケーリング則に従えば、ゲイト絶縁膜の厚さが100Åでなければならないところ、本明細書で開示するような結晶性珪素膜を用いた場合、ゲイト絶縁膜の厚さを300Åとして、同じ特性を得ることができる。その結果、耐静電気特性を高くできる。

【0111】

これは、上述した(1)〜(3)に示すような要因であると理解される。

【0112】

また、ゲイト絶縁膜の膜厚のみではなく、チャネル長に関しても従来のスケーリング則よりも緩い条件(1ランク下の条件)でもって、所定の特性を得ることができる。

【0113】

これは、高速動作が可能な半導体回路を大面積にわたって低コストで作製する場合に有用なことである。

【0114】

[実施例2]

図6に示すのは、液晶表示装置におけるソースドライバー回路のうちバッファー回路部の一部を示した図である。特にこの図はバッファー回路部全体のうち端の部分を示した図で、2つのインバータ回路601、602が一番端に配置されており、図の下側には同様な回路およびニッケル添加領域が周期的に配置されている。図6の等価回路図は図7に示す。

【0115】

図6において、611、612、613はニッケル添加領域である。また、621は結晶性珪素膜のパターン、622はゲート線、623、624、625はソースまたはドレイン線である。

【0116】

ニッケル添加領域612より下に作製されたインバータ回路(例えば603、604など)を構成するTFTの特性は十分である。それは、ニッケル添加領域の間に配置されているので、その間の領域での珪素膜の結晶成長距離は十分だからである。

【0117】

また、ニッケル添加領域間の間隔は等しくされているので、TFTの特性もほぼ同じである。

【0118】

一方、インバータ回路601、602は一番端に配置された回路で、この回路を構成するTFTの特性を十分得るために、ダミーとしてニッケル添加領域611を図6のように配置する。

【0119】

特に最も端に配置されたインバータ回路601を構成するTFTの特性を十分に得ることが目的である。なぜなら、結晶成長が不十分な場合、前記TFTの特性が最も悪くなるからである。

【0120】

このとき、ニッケル添加領域611、612、613の間の各間隔は同じになるようにする。

【0121】

このように、ダミーのニッケル添加領域611を配置することにより、インバータ回路601、602を構成するTFTを配置する領域の珪素膜の結晶成長の距離を十分にし、TFTの特性を十分にすることができる。

【0122】

そして、一番端に配置されたインバータ回路601、602について、その動作速度を十分にすることができる。

【0123】

さらに、インバータ回路601、602を構成するTFTの特性を、ニッケル添加領域602より下に作製されたインバータ回路を構成するTFTの特性にそろえ、ほぼ同じ動作速度を持つ複数のバッファー回路を得ることができる。

【0124】

[実施例3]

本実施例は、実施例1〜2で示した構成を逆スタガ型の薄膜トランジスタで構成する。各実施例で示したプレナー型の薄膜トランジスタに変えて、逆スタガ型の薄膜トランジスタとしても、同様の効果を得ることができる。

【0125】

なお、逆スタガ型の薄膜トランジスタのゲイト電極として、ゲイト電極に耐熱性の高い材料、例えばリンが多量にドープされた多結晶シリコンを利用することは、高性能な薄膜トランジスタを得るために有効である。

【0126】

【発明の効果】

本明細書で開示する発明により、ニッケル添加領域間の距離による結晶成長の違いを是正し、ニッケル添加を利用して作製した結晶性珪素膜を用いて、特性のそろったTFTを提供することができる。特に、ニッケル添加領域に挟まれていない領域の結晶成長の距離を十分にすることができる。

【0127】

そして、液晶表示装置において、同種の回路の動作特性を同一にすることができ、多数の画素を同じように動作させることができる。

【0128】

本明細書で開示した発明は、透過型、反射型のアクティブマトリクス型の液晶表示装置の、アクティブマトリクス回路と同一基板に形成される周辺回路を構成するのみでなく、他にEL(エレクトロルミネセンス)素子を用いた表示装置、その他薄膜トランジスタを用いた種々の回路にて利用することが可能である。

【図面の簡単な説明】

【図1】 本願発明におけるニッケル添加領域およびTFTの配置を示す図。

【図2】 従来例におけるニッケル添加領域およびTFTの配置を示す図。

【図3】 薄膜トランジスタの作製工程を示す図。

【図4】 薄膜トランジスタの作製工程を示す図。

【図5】 薄膜トランジスタの作製工程を示す図。

【図6】 バッファー回路部におけるニッケル添加領域およびTFTの配置を示す図。

【図7】 図6の等価回路図。

【符号の説明】

101〜104 ニッケル添加領域

111〜118 TFT

121〜128 結晶成長方向

301 石英基板

302 下地膜(酸化珪素膜)

303 非晶質珪素膜

304 酸化珪素膜でなるマスク

305、306 ニッケル添加領域

307 ダミーのニッケル添加領域

308 ニッケル元素

309 結晶成長方向

310 活性層を構成する結晶性珪素膜のパターン

311 熱酸化膜

312 酸化珪素膜

313 レジストマスク

314 アルミニウム膜でなるパターン

315 多孔質状の陽極酸化膜

316 緻密な陽極酸化膜

317 ゲイト電極

318 残存した酸化珪素膜

319 ソース領域、ドレイン領域

320 低濃度不純物領域

321 チャネル領域

322 層間絶縁膜

323 ソース電極、ドレイン電極

Claims (6)

- 絶縁基板上に非晶質珪素膜を成膜し、

前記非晶質珪素膜の第1乃至第3の領域に、珪素の結晶化を助長する金属元素を導入し、

加熱処理により、前記第1乃至第3の領域から、前記基板に平行な方向に結晶成長を行わせて結晶性珪素膜を形成し、

前記結晶性珪素膜をパターニングすることによって、前記第1の領域から前記第2の領域に向かって結晶成長が行われた領域を用いて第1の島状結晶性珪素領域を形成し、前記第2の領域から前記第1の領域に向かって結晶成長が行われた領域を用いて第2の島状結晶性珪素領域を形成し、前記第2の領域から前記第3の領域に向かって結晶成長が行われた領域を用いて第3の島状結晶性珪素領域を形成し、かつ、前記第3の領域から前記第2の領域に向かって結晶成長が行われた領域を除去し、

前記第1の領域と前記第2の領域との間隔は、前記第2の領域と前記第3の領域との間隔と等しいことを特徴とする半導体装置の作製方法。 - 絶縁基板上に非晶質珪素膜を成膜し、

前記非晶質珪素膜の第1乃至第3の領域に、珪素の結晶化を助長する金属元素を導入し、

加熱処理により、前記第1乃至第3の領域から、前記基板に平行な方向に結晶成長を行わせて結晶性珪素膜を形成し、

前記結晶性珪素膜をパターニングすることによって、前記第1の領域から前記第2の領域に向かって結晶成長が行われた領域を用いて第1の島状結晶性珪素領域を形成し、前記第2の領域から前記第1の領域に向かって結晶成長が行われた領域を用いて第2の島状結晶性珪素領域を形成し、前記第2の領域から前記第3の領域に向かって結晶成長が行われた領域を用いて第3の島状結晶性珪素領域を形成し、かつ、前記第3の領域から前記第2の領域に向かって結晶成長が行われた領域を除去し、

前記第1乃至第3の島状結晶性珪素領域をそれぞれ用いて、第1乃至第3の薄膜トランジスタを形成し、

前記第1乃至第3の薄膜トランジスタをそれぞれ用いて、第1乃至第3のインバータ回路を形成し、

前記第1乃至第3のインバータ回路はバッファ回路部の一部を構成し、前記第3のインバータ回路は前記バッファ回路部の端に配置されており、

前記第1の領域と前記第2の領域との間隔は、前記第2の領域と前記第3の領域との間隔と等しいことを特徴とする半導体装置の作製方法。 - 請求項1又は請求項2において、

前記金属元素は、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複数種類のものであることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか1項において、

前記金属元素の導入は、イオン注入法により行われることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項3のいずれか1項において、

前記金属元素の導入は、前記金属元素が溶解または分散された溶液を塗布して行われることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項5のいずれか1項において、

前記結晶性珪素膜に加熱処理を行って、前記結晶性珪素膜上に酸化珪素膜を形成し、

前記酸化珪素膜を除去することにより、前記結晶性珪素膜中の金属元素を減少させることを特徴とする半導体装置の作製方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35895596A JP4055831B2 (ja) | 1996-12-30 | 1996-12-30 | 半導体装置の作製方法 |

| US08/998,964 US6011275A (en) | 1996-12-30 | 1997-12-29 | Semiconductor device and method of manufacturing the same |

| US09/455,991 US7026193B1 (en) | 1996-12-30 | 1999-12-06 | Method of manufacturing a semiconductor device having TFTs with uniform characteristics |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35895596A JP4055831B2 (ja) | 1996-12-30 | 1996-12-30 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10199805A JPH10199805A (ja) | 1998-07-31 |

| JP4055831B2 true JP4055831B2 (ja) | 2008-03-05 |

Family

ID=18461980

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP35895596A Expired - Fee Related JP4055831B2 (ja) | 1996-12-30 | 1996-12-30 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4055831B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4539041B2 (ja) * | 2003-08-04 | 2010-09-08 | セイコーエプソン株式会社 | 薄膜半導体装置の製造方法 |

-

1996

- 1996-12-30 JP JP35895596A patent/JP4055831B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10199805A (ja) | 1998-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3645378B2 (ja) | 半導体装置の作製方法 | |

| JP3645379B2 (ja) | 半導体装置の作製方法 | |

| KR100285020B1 (ko) | 반도체장치 제작방법 | |

| JP3124480B2 (ja) | 半導体装置の作製方法 | |

| JP3645380B2 (ja) | 半導体装置の作製方法、情報端末、ヘッドマウントディスプレイ、ナビゲーションシステム、携帯電話、ビデオカメラ、投射型表示装置 | |

| US8497508B2 (en) | Semiconductor device and manufacturing method thereof | |

| US6455875B2 (en) | Thin film transistor having enhanced field mobility | |

| US6011275A (en) | Semiconductor device and method of manufacturing the same | |

| JP3983334B2 (ja) | 半導体装置の作製方法 | |

| JP4055831B2 (ja) | 半導体装置の作製方法 | |

| JP3645387B2 (ja) | 半導体回路 | |

| JP3734582B2 (ja) | アナログスイッチ回路の作製方法 | |

| US6764928B1 (en) | Method of manufacturing an El display device | |

| JP3645381B2 (ja) | 半導体装置の作製方法、情報端末、ヘッドマウントディスプレイ、カーナビゲーション、携帯電話、ビデオカメラ、投写型表示装置 | |

| JP3265297B2 (ja) | 半導体装置の作製方法 | |

| JP2004064056A (ja) | 半導体集積回路の作製方法 | |

| JP3874825B2 (ja) | 半導体装置及び電気光学装置の作製方法 | |

| JP2007108785A (ja) | 半導体装置 | |

| JP2009116335A (ja) | 表示装置 | |

| JP2005092230A (ja) | 半導体装置 | |

| JPH09171964A (ja) | 半導体装置およびその作製方法 | |

| JP2017010039A (ja) | 液晶表示装置 | |

| JP2006099134A (ja) | 半導体装置 | |

| JPH1168111A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040419 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070619 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070808 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070808 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070911 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071025 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071204 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101221 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101221 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101221 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111221 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111221 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121221 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121221 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131221 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |