JP3963423B2 - マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 - Google Patents

マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 Download PDFInfo

- Publication number

- JP3963423B2 JP3963423B2 JP2001142749A JP2001142749A JP3963423B2 JP 3963423 B2 JP3963423 B2 JP 3963423B2 JP 2001142749 A JP2001142749 A JP 2001142749A JP 2001142749 A JP2001142749 A JP 2001142749A JP 3963423 B2 JP3963423 B2 JP 3963423B2

- Authority

- JP

- Japan

- Prior art keywords

- connection path

- power distribution

- distribution circuit

- modulation signal

- mixer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

Description

【発明の属する技術分野】

本発明は、マイクロ波帯FM復調回路およびマイクロ波帯FSK復調回路に関するものである。

【0002】

【従来の技術】

近年、30GHzを越えるミリ波等の高周波帯を用い、100Mbps〜1Gbpsの高速大容量の無線通信システムの研究開発が盛んに行われている。

【0003】

このような無線通信システムでは、1チャネル当たりの帯域幅が100MHz〜1GHzと広帯域であるので、その中間周波数は、GHzのマイクロ波帯になる。したがって、復調する際には、マイクロ波の変調信号から、伝送データに対応するベースバンド信号を抽出する必要がある。

【0004】

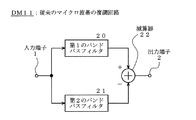

図9は、変調方式としてFSK(Frequency Shift Keying)を用いた従来のマイクロ波帯の復調回路DM11を示す図である。

【0005】

従来のマイクロ波帯の復調回路DM11は、入力端子1と、出力端子2と、第1のバンドパスフィルタ20と、第2のバンドパスフィルタ21と、減算器22とを有する。

【0006】

FSK(Frequency Shift Keying)復調回路では、送信するデータの0、1に応じて搬送波の角周波数を、ω0−|Δω|と、ω0+|Δω|とに切り替える。ただし、ω0は、搬送波の中心周波数であり、Δωは、周波数偏移である。

【0007】

従来のマイクロ波帯の復調回路DM11では、第1のバンドパスフィルタ20の中心周波数、第2のバンドパスフィルタ21の中心周波数が、それぞれ、ω0−|Δω|、ω0+|Δω|であるとし、減算器22が、バンドパスフィルタの出力の差を取り出す。したがって、出力端子2が出力する信号の電圧は、入力端子1に入力されるFSK変調信号の角周波数が、ω0であるときに、0になり、その角周波数がω0−|Δω|であるときに、正になり、その角周波数がω0+|Δω|であるときに、負になる。したがって、出力端子2が出力する信号の電圧の正負を、コンパレータで判定することによって、入力端子1に印加された入力信号を復調することができる。

【0008】

図10は、従来のクオドラチャ検波回路DM12を示す図である。

【0009】

入力周波数が100MHz程度の低周波である場合には、従来のFSK復調回路として、図10に示すクオドラチャ検波回路DM12が用いられている。

【0010】

このクオドラチャ検波回路DM12は、National Semiconductor社の製品LMX3162や、Motorola社の製品MC3356等に使われている。図10に示すクオドラチャ検波回路DM12は、入力端子1と、出力端子2と、ミキサ5と、ローパスフィルタ6と、第1のコンデンサ23と、第2のコンデンサ24と、コイル25とを有する。第2のコンデンサ24と、コイル25とは、入力端子1から入力されたFSK変調信号の角周波数ωの中心周波数ω0で共振するように値が設定されている。

【0011】

図11は、従来のクオドラチャ検波回路DM12の動作を説明する図であり、クオドラチャ検波回路DM12の等価回路を示す図である。

【0012】

図10に示すミキサ5の入力インピーダンスを、図11では抵抗10とし、そのインピーダンス値をRとする。また、第1のコンデンサ23の容量をC1とし、第2のコンデンサ24の容量をCとし、コイル25のインダクタンスをLとし、入力端子1に入力される電圧をV3とし、抵抗10にかかる電圧をV4とし、電圧V3と電圧V4との位相差をθとする。このときに、入出力電圧の応答V4/V3は、以下のようになる。

【0013】

V4/V3=[−ω2LRC1{R(1−ω2LC−ω2LC1)−jωL}]

/{R2(1−ω2LC−ω2LC1)2−ω2L2} …式(1)

V4/V3=|V4/V3|ejθ から、

θ=tan-1[(−ωL)/{R(1−ω2LC−ω2LC1)}] …式(2)

であり、FSK変調信号の角周波数ωは、中心周波数ω0と周波数偏移Δωとを用いると、

ω=ω0+Δω

である。ただし、Δωは、正および負の値を取る。第2のコンデンサ24とコイル25とは、周波数がω0であるときに、共振するので、1−ω0 2LC=0である。したがって、

θ≒tan-1[1/{ω0RC1+2R(C+C1)Δω}] …式(3)

ただし、Δω2/ω0≒0、1+Δω/ω0≒1を用いている。

【0014】

関数f(x)は、xが小さいときに、テイラー展開によって、

f(x)=f(0)+f’(0)x

である。ただし、f’(x)は、f(x)に関する微分である。Δωに関するテイラー展開によって、θは、以下のようになる。

【0015】

θ=[tan −1 (1/ω 0 RC 1 )]

−2R(C+C1)・Δω/{(ω0RC1)2+1}] …式(4)

ω0RC1≪1となるように、第1のコンデンサ23の容量C1を選ぶと、

θ=90°−AΔω

である。ただし、A=−2R(C+C1)/{(ω0RC1)2+1}である。

【0016】

したがって、V3=Vcos(ωt+φ)(Vは定数)とすると、

V4=−Bsin(ωt+φ−AΔω)となる。Bは、定数である。

【0017】

図10に示すクオドラチャ検波回路DM12の入力端子1に、入力電圧V3が印加されると、ミキサ5の一方の入力端子に直接入力される入力信号S3は、電圧V3であり、第1のコンデンサ23を介して、ミキサ5の他方の入力端子に入力される入力信号S4は、電圧V4である。ミキサ5の出力信号は、信号S3と信号S4との積であり、ローパスフィルタ6を介して、出力端子2に得られる信号VOUTは、以下のようになる。

【0018】

ただし、ω0RC1≪1、C=1/(ω0 2L)であるので、AΔωは、十分小さく、sin(AΔω)≒AΔωである。

【0019】

したがって、出力端子2に得られる電圧は、周波数偏移Δωに比例し、Δωが正であるときに、正であり、Δωが負であるときに、負になるので、出力端子2に得られる電圧の正負を、コンパレータで判定することによって、クオドラチャ検波回路DM12の入力信号を復調することができる。

【0020】

【発明が解決しようとする課題】

上記バンドパスフィルタを用いる従来のFSK復調回路では、Q値の高いバンドパスフィルタを必要とするので、半導体に集積することが困難であるという問題があり、回路の小型軽量化や低コスト化が困難であるという問題がある。

【0021】

また、コンデンサ、コイル、ミキサによって構成されているクオドラチャ検波回路DM12を用いる従来のFSK復調回路では、ω0RC1≪1となるように、コンデンサの容量を選ぶ必要があるので、周波数が高くなるに従って、コンデンサの容量値が小さくなり、必要なコンデンサの容量を精度良く実現することができず、復調回路を精度良く実現することができないという問題がある。

【0022】

たとえば、周波数が5GHzであり、Rが50Ωであるときに、ω0RC1を1/10とする容量C1は、0.06pFであり、FSK復調回路を精度良く実現することができない。

【0023】

また、周波数が高くなるに従って、コイルのQ値が小さくなり、性能が劣化するという問題がある。

【0024】

上記問題は、FSK用の復調回路に限らず、アナログ的な周波数変調信号を復調をする回路でも生じる問題である。

【0025】

本発明は、マイクロ波帯において半導体に集積可能な素子のみでマイクロ波周波数変調復調回路を構成することができ、回路の小型軽量化や低コスト化が可能になり、また、周波数が高くなっても性能が劣化しないマイクロ波周波数変調復調回路を提供することを目的とする。

【0026】

【課題を解決するための手段】

本発明は、周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度の位相差を持つ2信号を出力する90度電力分配回路と、上記90度電力分配回路が出力する上記2信号を混合するミキサと、上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と、上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と上記ミキサの2つの入力端子のうちの他方の入力端子とを接続する第2の接続経路と、上記第1の接続経路または上記第2の接続経路に、一端が接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路とを有するマイクロ波周波数変調復調回路である。

【0027】

【発明の実施の形態および実施例】

[第1の実施例]

図1は、本発明の第1の実施例であるFSK復調回路DM1を示す回路図である。

【0028】

FSK復調回路DM1は、入力端子1と、出力端子2と、90度電力分配回路3と、伝送線路4と、ミキサ5と、ローパスフィルタ6とを有する。

【0029】

90度電力分配回路3は、周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度位相差を持つ2信号を出力する90度電力分配回路である。

【0030】

ミキサ5は、90度の電力分配回路が出力する2信号を混合するものである。

【0031】

90度電力分配回路3の2つの出力端子のうちの一方の出力端子と、ミキサ5の2つの入力端子のうちの一方の入力端子とが、第1の接続経路によって接続され、90度電力分配回路3の2つの出力端子のうちの他方の出力端子と、ミキサ5の2つの入力端子のうちの他方の入力端子とが、第2の接続経路によって接続されている。また、上記第1の接続経路と上記第2の接続経路は、電気長が互いに同じである。

【0032】

伝送線路4の電気長は、入力端子1から入力されるFSK変調信号の角周波数ωの中心周波数ω0における1/4波長であり、先端42が短絡されている(接地されている)。つまり、伝送線路4は、第1の接続経路または第2の接続経路に、一端41が接続され、他端42が、短絡されている。

【0033】

次に、FSK復調回路DM1の動作について説明する。

【0034】

図2は、FSK復調回路DM1の動作を説明する図であり、FSK復調回路DM1の等価回路である。

【0035】

ミキサ5の入力インピーダンスを、図2では、抵抗10とし、そのインピーダンス値をRとする。90度電力分配回路3の出力インピーダンスが、抵抗11であるとすると、整合状態では、抵抗11のインピーダンス値もRになる。伝送線路4の特性インピーダンスをZ0とし、短絡端42を他端から見たインピーダンスをZ1とすると、Z1は、

Z1=jZ0tan(πω/2ω0)…式(6)

である。

【0036】

抵抗11に入力される電圧を、V1とし、抵抗10にかかる電圧を、V2とし、電圧V1と電圧V2との位相差を、θとする。このときに、入出力電圧の応答V2/V1は、以下のようになる。

【0037】

V2/V1={2Z0 2・tan2(πω/2ω0)+jRZ0・tan(πω/2ω0)}/{R2+4Z0 2・tan2(πω/2ω0)} …式(7)

V2/V1=|V2/V1|ejθ であるので、

θ=tan-1[R/{2Z0・tan(πω/2ω0)}] …式(8)

である。

【0038】

FSK変調信号の角周波数ωは、中心周波数ω0と周波数偏移Δωとを用いると、

ω0=ω+Δω

である。ただし、Δωは、正および負の値を取る。したがって、

θ=tan-1{(−R/2Z0)・tan(πΔω/2ω0)} …式(9)

関数f(x)は、xが小さいときにはテイラー展開によって、f(x)=f(0)+f’(0)xとなる。

【0039】

ただし、f’(x)は、f(x)のxに関する微分である。Δωに関するテイラー展開によって、θは、以下のようになる。

【0040】

θ=−(RπΔω)/(4Z0ω0)=−DΔω …式(10)

ただしD=Rπ/(4Z0ω0)である。

【0041】

したがって、V1=Vcos(ωt+φ)(Vは定数)であるとすると、V2=Ecos(ωt+φ−DΔω)となる。なお、Eは、定数である。

【0042】

この電圧V2が、図1に示す90度電力分配回路3の一方の出力端子からミキサ5へ入力される信号がS2であるときに、90度電力分配回路3の他方の出力端子からミキサ5に入力される信号S1は、V1と90度位相差を持った信号であり、S1=Fsin(ωt+φ)となる。ただし、Fは、定数である。

【0043】

ミキサ5の出力信号は、信号S1と信号S2との積であり、ローパスフィルタ6を介して、出力端子2に得られる信号VOUTは、以下のようになる。

【0044】

VOUT

=(EF/2)sin(DΔω)≒(DEF/2)Δω …式(11)

ただし、Δω/ω0≪1であるので、DΔωは、十分小さく、sin(DΔω)≒DΔωである。したがって、出力端子2に得られる電圧は、周波数偏移Δωに比例し、Δωが正であるときに、正になり、Δωが負のときに、負になるので、FSK復調回路DM1の出力電圧の正負を、コンパレータで判定することによって、FSK復調回路DM1の入力信号を復調できる。

【0045】

FSK復調回路DM1では、90度電力分配回路3、伝送線路4、ミキサ5というマイクロ波帯において半導体に集積可能な素子のみを使用して、FSK復調回路MD1を構成することができる。マイクロ波帯における90度電力分配回路3として、ブランチラインハイブリッドや、方向性結合器がよく知られている。

【0046】

また、FSK復調回路DM1では、コイルやコンデンサを使用しないので、周波数が高くなっても、性能が劣化しない。

【0047】

[第2の実施例]

図3は、本発明の第2の実施例であるFSK復調回路DM2を示す図である。

【0048】

FSK復調回路DM2において、FSK復調回路DM1と同一部分には同一符号を付与してある。

【0049】

FSK復調回路DM2が、FSK復調回路DM1と異なる点は、90度電力分配回路3とミキサ5との間に、増幅器7、8が設けられている点である。

【0050】

増幅器7、8の代わりに、アッティネータ(減衰器)やアイソレータ、サーキュレータといったマイクロ波素子を使用するようにしてもよい。

【0051】

すなわち、90度電力分配回路3とミキサ5との間には、ミキサを駆動するために必要な入力レベルやアイソレーション特性によって様々な素子を置くことができる。これらの素子は、2つの信号パスS1、S2で、必ずしも同じである必要はなく、90度位相差を保つ限り、異なる種類の素子を設けるようにしてもよい。

【0052】

すなわち、90度電力分配回路3、増幅器7、8等の素子を含めて、広い意味で、90°電力分配回路であると言える。これらマイクロ波素子は、マイクロ波帯において、半導体に集積可能であるので、回路を、小型軽量化や低コスト化することができる。

【0053】

[第3の実施例]

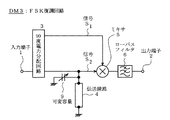

図4は、本発明の第3の実施例であるFSK復調回路DM3を示す回路図である。

【0054】

FSK復調回路DM3において、FSK復調回路DM1と同一部分には、同一符号を付してある。FSK復調回路DM3が、FSK復調回路DM1と異なる点は、伝送線路4の一端41と接地電位との間に、可変容量9が設けられている点である。

【0055】

伝送線路4の一端41と接地電位との間に容量を設けることによって、伝送線路の等価的な電気長が長くなり、1/4波長の周波数が低くなる。したがって、この容量9を可変にすることによって、伝送線路4の等価的な電気長を調整することができ、広い周波数範囲にわたって、FSKの復調が可能になる。

【0056】

可変容量9は、バラクタと呼ばれる素子を用いれば、マイクロ波帯において半導体に集積可能である。また、連続的に可変の容量ではなく、複数の固定容量をスイッチで切り替えることによって、段階的に容量を変化できるようにしてもよい。

【0057】

[第4の実施例]

図5は、本発明の第4の実施例であるFSK復調回路DM4を示す図である。

【0058】

FSK復調回路DM4において、FSK復調回路DM1と同一部分には、同一符号を付してある。

【0059】

FSK復調回路DM4は、FSK復調回路DM1において、90度電力分配回路3と伝送線路4との代わりに、電力分配回路10が設けられている。

【0060】

電力分配回路10は、同相電力分配回路11と、伝送線路12とを有する。伝送線路4は、入力端子1から入力されるFSK変調信号の角周波数ωの中心周波数ω0における1/4波長の電気長とする。このときに、電力分配回路10の2つの出力信号の位相差は、中心周波数ω0において互いに90度であり、中心周波数ω0からの周波数偏移Δωに比例した位相差を持つ。

【0061】

図6は、FSK復調回路DM4において、伝送線路12の電気長を、5GHzにおける1/4波長としたときに、電力分配回路10の2つの出力信号の位相差の周波数特性を示す図である。

【0062】

図7は、代表的な90度電力分配回路であるブランチラインハイブリッドの2つの出力信号における位相差の周波数特性を示す図である。

【0063】

ただし、ブランチラインハイブリッドは、5GHzにおいて1/4波長の電気長を持つ伝送線路で構成されている。

【0064】

図7に示すブランチラインハイブリッドの2つの出力信号の位相差は、5GHzで90度になるとともに、その近辺の周波数でも、90度になっている。

【0065】

一方、図6に示す電力分配回路10における2出力信号の位相差は、5GHzで90度になり、その位相差は、この周波数(5GHz)からの周波数偏移に比例する。

【0066】

したがって、FSK復調回路DM4において、電力分配回路10の一方の出力端子からミキサ5に入力される信号S1が、S1=Fcos(ωt+φ)(Fは定数)であるときに、電力分配回路10の他方の出力端子からミキサ5に入力される信号S2は、S2=Fsin(ωt+φ−kΔω)になる。ただし、kは、信号S1の中心周波数ω0と、信号S2の中心周波数ω0とにおける位相差の周波数偏移Δωに対する変化率である。

【0067】

FSK復調回路DM4では、図6に示すように、周波数が0からω0まで変化する間に、位相差が、π/2rad変化するので、変化率k=π/(2ω0)である。一方、図7に示すブランチラインハイブリッドの場合の変化率kは、ほぼ0である。

【0068】

ミキサ5の出力信号は、信号S1と信号S2との積であり、ローパスフィルタ6を介して、出力端子2に得られる信号VOUTは、以下のようになる。

【0069】

ただし、Δω/ω0≪1であるので、kΔωは、十分小さく、sin(kΔω)≒kΔωである。したがって、出力端子2で出力される電圧は、周波数偏移Δωに比例し、Δωが正であるときに、負であり、Δωが負であるときに、正となるので、出力端子2で出力される電圧の正負を、コンパレータで判定することによって、復調することができる。

【0070】

以上の実施例では、同相電力分配回路、伝送線路、ミキサというマイクロ波帯において、半導体に集積可能な素子のみによって、FSK復調回路を構成することができる。マイクロ波帯における同相電力分配回路として、ウィルキンソンハイブリッドがよく知られている。

【0071】

また、伝送線路12の電気長は、1/4波長だけでなく、(2n―1)/4波長(nは1以上の整数)としてもよい。この場合、kは、k=π/(2ω0)×(2n−1)となる。

【0072】

また、伝送線路12の代わりに、FSK変調信号の角周波数ωの中心周波数ω0において通過時間が(2n―1)/4周期(nは1以上の整数)である遅延素子を使用するようにしてもよい。遅延素子は、トランジスタ等で実現することができる。このときも、電力分配回路10の2出力信号の位相差は、中心周波数ω0において90度であり、中心周波数ω0からの周波数偏移Δωに比例した位相差を持つ。

【0073】

[第5の実施例]

図8は、本発明の第5の実施例であるFSK復調回路DM5を示す図である。

【0074】

図8において、FSK復調回路DM1、DM4と同一部分には、同一符号を付してある。

【0075】

FSK復調回路DM5は、FSK復調回路DM1とDM4とを組み合わせた回路である。

【0076】

すなわち、FSK復調回路DM5は、入力端子1と、出力端子2と、電力分配回路10と、伝送線路4と、ミキサ5と、ローパスフィルタ6とを有する。電力分配回路10は、同相電力分配回路11と、伝送線路12とを有する。

【0077】

FSK復調回路DM5において、伝送線路4の電気長は、入力端子1から入力されるFSK変調信号の角周波数ωの中心周波数ω0における1/4波長とし、伝送線路4の先端42を短絡している。また、伝送線路12の電気長は、入力端子1から入力されるFSK変調信号の角周波数ωの中心周波数ω0における1/4波長とする。このときに、電力分配回路10の2つの出力信号の位相差は、中心周波数ω0において90度であり、中心周波数ω0からの周波数偏移Δωに比例した位相差を持つ。

【0078】

したがって、電力分配回路10の一方の出力端子からミキサ5に入力される信号S1が、S1=Fcos(ωt+φ)(Fは定数)であるときに、電力分配回路10の他方の出力端子に抵抗負荷を付けたときの出力信号S3は、S3=Fsin(ωt+φ―kΔω)となる。ただし、k=π/2/ω0である。

【0079】

この信号S3が、伝送線路4を通過してミキサ5に入力される信号S2は、式(10)を参照し、以下のようになる。

【0080】

S2=Esin(ωt+φ―kΔω−DΔω) …式(13)

ただし、D=Rπ/(4Z0ω0)である。

【0081】

ミキサ5の出力信号は、信号S1と信号S2との積であり、ローパスフィルタ6を介して、出力端子2に得られる信号VOUTは、以下のようになる。

【0082】

ただし、Δω/ω0≪1であるので、sin((k+D)Δω)≒(k+D)Δωである。したがって、出力端子2に得られる電圧は、周波数偏移Δωに比例し、Δωが正であるときに、負になり、Δωが負であるときに、正になるので、出力端子2に得られ電圧の正負を、コンパレータで判定することによって、復調することができる。

【0083】

上記実施例では、電圧分配回路10と伝送線路4との両方が、周波数偏移Δωに比例した周波数特性を持つので、高い復調感度を持つ。

【0084】

また、FSK復調回路DM4と同様に、伝送線路12の代わりに、FSK変調信号の角周波数ωの中心周波数ω0における通過時間が1/4周期の通過時間を有する遅延素子を設けるようにしてもよい。この遅延素子を、トランジスタで実現することができる。このときも、電力分配回路10の2出力信号の位相差は、中心周波数ω0において90度であり、中心周波数ω0からの周波数偏移Δωに比例した位相差を持つ。

【0085】

上記各実施例は、FSK用の復調回路であるが、FSKのようなデジタル信号に限らず、アナログ的なFM(周波数変調)信号をも復調することができる。

【0086】

また、上記実施例は、基本的には90度分配器の2つの出力端子のうちの一方の出力端子と、ミキサの2つの入力端子のうちの一方の入力端子とを1つの接続経路で接続し、90度分配器の2つの出力端子のうちの他方の出力端子と、ミキサの2つの入力端子のうちの他方の入力端子とを別の接続経路で接続しているが、これら2つ接続経路は等しい電気長を有する。

【0087】

つまり、FSK復調回路DM4は、周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに90度の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と、上記電力分配回路の2つの出力信号を混合するミキサとを有するマイクロ波帯FM復調回路およびマイクロ波帯FSK復調回路の例である。

【0088】

また、FSK復調回路DM5は、周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに90度の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と、上記電力分配回路の2つの出力信号を混合するミキサと、上記電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と、上記電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続する第2の接続経路と、上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路とを有するマイクロ波帯FM復調回路およびマイクロ波帯FSK復調回路の例である。

【0089】

上記実施例において、電力分配回路は、入力信号の中心周波数において互いに90度の位相差を有する2つの信号を出力する。これは、性能が最も良くなる位相差が90度であるためであるが、90度以外の位相差であっても動作する。つまり、上記電力分配回路は、入力信号の中心周波数において、所定の位相差を具備する2つの信号を出力すればよい。

【0090】

【発明の効果】

本発明によれば、マイクロ波帯において半導体に集積可能な素子のみでマイクロ波周波数変調復調回路を構成することができるので、回路の小型軽量化や低コスト化が可能になり、また、コイルやコンデンサを用いないので、周波数が高くなっても性能は劣化しないという効果を奏する。

【図面の簡単な説明】

【図1】本発明の第1の実施例であるFSK復調回路DM1を示す回路図である。

【図2】FSK復調回路DM1の動作を説明する図であり、FSK復調回路DM1の等価回路である。

【図3】本発明の第2の実施例であるFSK復調回路DM2を示す図である。

【図4】本発明の第3の実施例であるFSK復調回路DM3を示す回路図である。

【図5】本発明の第4の実施例であるFSK復調回路DM4を示す図である。

【図6】FSK復調回路DM4において、伝送線路12の電気長を、5GHzにおける1/4波長としたときに、電力分配回路10の2つの出力信号の位相差の周波数特性を示す図である。

【図7】代表的な90度電力分配回路であるブランチラインハイブリッドの2つの出力信号における位相差の周波数特性を示す図である。

【図8】本発明の第5の実施例であるFSK復調回路DM5を示す図である。

【図9】 従来のマイクロ波帯のFSK復調回路DM11を示す図である。

【図10】従来のクオドラチャ検波回路DM12を示す図である。

【図11】従来のクオドラチャ検波回路DM12の動作を説明する図であり、クオドラチャ検波回路DM12の等価回路を示す図である。

【符号の説明】

DM1〜DM5…FSK復調回路、

1…入力端子、

2…出力端子、

3…90度電力分配回路、

4…伝送線路、

5…ミキサ、

6…ローパスフィルタ、

7、8…増幅器、

9…可変容量、

10…電力分配回路、

11…同相電力分配回路、

12…伝送線路。

Claims (16)

- 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

上記伝送線路において短絡されていない端子と接地電位との間に設けられている可変容量と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに90度の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と;

上記電力分配回路が出力する上記2信号を混合するミキサと;

上記電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 請求項3において、

周波数変調信号が入力されて位相差の無い2信号を出力する同相電力分配回路の一方の出力信号を、上記周波数変調信号の中心周波数における(2n―1)/4波長(nは1以上の整数)の電気長を持つ伝送線路に通過させることを特徴とするマイクロ波帯FM復調回路。 - 請求項3において、

周波数変調信号が入力されて位相差の無い2信号を出力する同相電力分配回路の一方の出力信号を、上記周波数変調信号の中心周波数における(2n―1)/4周期(nは1以上の整数)の遅延時間を持つ遅延素子に通過させることを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに所定の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに所定の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

上記伝送線路において短絡されていない端子と接地電位との間に設けられている可変容量と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに所定の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と;

上記電力分配回路が出力する上記2信号を混合するミキサと;

上記電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FM復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FSK復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに90度の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

上記伝送線路において短絡されていない端子と接地電位との間に設けられている可変容量と;

を有することを特徴とするマイクロ波帯FSK復調回路。 - 周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに90度の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と;

上記電力分配回路が出力する上記2信号を混合するミキサと;

上記電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FSK復調回路。 - 請求項11において、

周波数変調信号が入力されて位相差の無い2信号を出力する同相電力分配回路の一方の出力信号を、上記周波数変調信号の中心周波数における(2n―1)/4波長(nは1以上の整数)の電気長を持つ伝送線路に通過させることを特徴とするマイクロ波帯FSK復調回路。 - 請求項11において、

周波数変調信号が入力されて位相差の無い2信号を出力する同相電力分配回路の一方の出力信号を、上記周波数変調信号の中心周波数における(2n―1)/4周期(nは1以上の整数)の遅延時間を持つ遅延素子に通過させることを特徴とするマイクロ波帯FSK復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに所定の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FSK復調回路。 - 周波数変調信号を入力し、上記入力した周波数変調信号の中心周波数において互いに所定の位相差を持つ2信号を出力する90度電力分配回路と;

上記90度電力分配回路が出力する上記2信号を混合するミキサと;

上記90度電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記90度電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

上記伝送線路において短絡されていない端子と接地電位との間に設けられている可変容量と;

を有することを特徴とするマイクロ波帯FSK復調回路。 - 周波数変調信号を入力し、この周波数変調信号の中心周波数において互いに所定の位相差を持ち、しかも、上記周波数変調信号の中心周波数からの周波数偏移に比例した位相差を持つ2信号を出力する電力分配回路と;

上記電力分配回路が出力する上記2信号を混合するミキサと;

上記電力分配回路の2つの出力端子のうちの一方の出力端子と、上記ミキサの2つの入力端子のうちの一方の入力端子とを接続する第1の接続経路と;

上記電力分配回路の2つの出力端子のうちの他方の出力端子と、上記ミキサの2つの入力端子のうちの他方の入力端子とを接続し、しかも、上記第1の接続経路と電気長が同じである第2の接続経路と;

上記第1の接続経路または上記第2の接続経路に、一端が、接続され、他端が、短絡されている伝送線路であって、上記周波数変調信号の中心周波数における1/4波長の電気長を持つ伝送線路と;

を有することを特徴とするマイクロ波帯FSK復調回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001142749A JP3963423B2 (ja) | 2001-05-14 | 2001-05-14 | マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001142749A JP3963423B2 (ja) | 2001-05-14 | 2001-05-14 | マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002344245A JP2002344245A (ja) | 2002-11-29 |

| JP2002344245A5 JP2002344245A5 (ja) | 2004-12-24 |

| JP3963423B2 true JP3963423B2 (ja) | 2007-08-22 |

Family

ID=18988992

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001142749A Expired - Fee Related JP3963423B2 (ja) | 2001-05-14 | 2001-05-14 | マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3963423B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2007032317A1 (ja) | 2005-09-16 | 2009-03-19 | 日本電気株式会社 | 無線通信機および無線通信機の電力制御方法ならびに無線ネットワーク |

| WO2007096940A1 (ja) * | 2006-02-20 | 2007-08-30 | Fujitsu Limited | 半導体回路 |

-

2001

- 2001-05-14 JP JP2001142749A patent/JP3963423B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002344245A (ja) | 2002-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103503314A (zh) | Mems可调陷波滤波器频率自动控制回路系统和方法 | |

| EP0866513A2 (en) | Phasing and balancing member | |

| US8299869B2 (en) | Setting of a balun | |

| Atwater | Mlcrostrip Reactive Circuit Elements | |

| US5361050A (en) | Balanced split ring resonator | |

| JPH08242261A (ja) | 検波器及び受信装置並びに送信装置 | |

| CN102571134B (zh) | 一种高频率选择性的射频前端集成电路结构 | |

| CN210225363U (zh) | 一种带通滤波器、接收机及通信装置 | |

| JP4233451B2 (ja) | フィルタ一体型偶高調波ミキサおよびそれを用いた高周波無線通信装置 | |

| US7383034B2 (en) | Frequency conversion circuit, modulation circuit, polar modulation transmitting circuit, quadrature modulation transmitting circuit, communication instrument, and frequency conversion method | |

| JP2004166204A (ja) | 周波数変換器および無線送受信機 | |

| KR100260965B1 (ko) | 증폭기와그증폭기를사용한휴대전화기 | |

| US7509112B2 (en) | Wideband image rejection mixer | |

| JP3963423B2 (ja) | マイクロ波帯fm復調回路およびマイクロ波帯fsk復調回路 | |

| JP2000036721A (ja) | インピ―ダンス・マッチング方法とインピ―ダンス・マッチング回路 | |

| JPH10256809A (ja) | 電子同調型有極フィルタ | |

| CN110764061B (zh) | 一种正交变频接收机 | |

| US8190117B2 (en) | Mixer circuit and radio communication device using the same | |

| JP2007515905A (ja) | フィードバックを有するミキサ | |

| JPH04352528A (ja) | 高周波電力増幅装置 | |

| US7512394B2 (en) | Wideband up-conversion mixer | |

| JPH09181570A (ja) | 能動直交電力分配器 | |

| WO2004040755A1 (ja) | フィルタ回路及び無線装置 | |

| US6545554B1 (en) | Differential oscillator | |

| JP3560774B2 (ja) | 偶高調波ミクサ、直交ミクサ、イメージリジェクションミクサ、受信装置及び位相同期発振器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070223 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070417 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070518 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070521 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100601 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110601 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120601 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130601 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140601 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |