JP3961392B2 - ダイオードベースのマルチプレクサ - Google Patents

ダイオードベースのマルチプレクサ Download PDFInfo

- Publication number

- JP3961392B2 JP3961392B2 JP2002298312A JP2002298312A JP3961392B2 JP 3961392 B2 JP3961392 B2 JP 3961392B2 JP 2002298312 A JP2002298312 A JP 2002298312A JP 2002298312 A JP2002298312 A JP 2002298312A JP 3961392 B2 JP3961392 B2 JP 3961392B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- input

- diode

- latch

- multiplexer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 claims description 29

- 239000007787 solid Substances 0.000 claims description 10

- 239000000758 substrate Substances 0.000 claims description 8

- 230000004044 response Effects 0.000 claims 1

- 239000003990 capacitor Substances 0.000 description 10

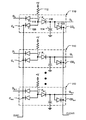

- 238000010586 diagram Methods 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/002—Switching arrangements with several input- or output terminals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/74—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of diodes

- H03K17/76—Switching arrangements with several input- or output-terminals, e.g. multiplexers, distributors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/04—Distributors combined with modulators or demodulators

- H04J3/047—Distributors with transistors or integrated circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Read Only Memory (AREA)

- Electronic Switches (AREA)

- Static Random-Access Memory (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/976744 | 2001-10-13 | ||

| US09/976,744 US6614697B2 (en) | 2001-10-13 | 2001-10-13 | Diode-based multiplexer |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003142994A JP2003142994A (ja) | 2003-05-16 |

| JP2003142994A5 JP2003142994A5 (enExample) | 2005-05-12 |

| JP3961392B2 true JP3961392B2 (ja) | 2007-08-22 |

Family

ID=25524408

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002298312A Expired - Fee Related JP3961392B2 (ja) | 2001-10-13 | 2002-10-11 | ダイオードベースのマルチプレクサ |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6614697B2 (enExample) |

| EP (1) | EP1303044B1 (enExample) |

| JP (1) | JP3961392B2 (enExample) |

| KR (1) | KR20030031423A (enExample) |

| CN (1) | CN1412779A (enExample) |

| DE (1) | DE60211093T2 (enExample) |

| TW (1) | TWI240281B (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1157466A1 (en) * | 1999-12-21 | 2001-11-28 | Koninklijke Philips Electronics N.V. | Diode multiplexer circuit and electronic device incorporating the same |

| US7747415B1 (en) * | 2005-12-22 | 2010-06-29 | Microstrain, Inc. | Sensor powered event logger |

| TWI340911B (en) * | 2007-04-13 | 2011-04-21 | Generalplus Technology Inc | Capacitance touch sensor |

| US20240070059A1 (en) * | 2022-08-30 | 2024-02-29 | Micron Technology, Inc. | Memory devices including logic non-volatile memory |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5900767A (en) | 1995-06-24 | 1999-05-04 | U.S. Philips Corporation | Electronic devices comprising an array |

| GB9614480D0 (en) * | 1995-12-01 | 1996-09-04 | Philips Electronics Nv | Multiplexer circuit |

| GB9524560D0 (en) * | 1995-12-01 | 1996-01-31 | Philips Electronics Nv | Multiplexer circuit |

| GB9600543D0 (en) * | 1996-01-11 | 1996-03-13 | Philips Electronics Nv | Electronic devices comprising an array |

| US6199140B1 (en) * | 1997-10-30 | 2001-03-06 | Netlogic Microsystems, Inc. | Multiport content addressable memory device and timing signals |

| EP1157466A1 (en) * | 1999-12-21 | 2001-11-28 | Koninklijke Philips Electronics N.V. | Diode multiplexer circuit and electronic device incorporating the same |

-

2001

- 2001-10-13 US US09/976,744 patent/US6614697B2/en not_active Expired - Lifetime

-

2002

- 2002-08-29 TW TW091119704A patent/TWI240281B/zh not_active IP Right Cessation

- 2002-10-08 EP EP02256961A patent/EP1303044B1/en not_active Expired - Lifetime

- 2002-10-08 DE DE60211093T patent/DE60211093T2/de not_active Expired - Lifetime

- 2002-10-11 JP JP2002298312A patent/JP3961392B2/ja not_active Expired - Fee Related

- 2002-10-11 CN CN02143600A patent/CN1412779A/zh active Pending

- 2002-10-12 KR KR1020020062230A patent/KR20030031423A/ko not_active Ceased

Also Published As

| Publication number | Publication date |

|---|---|

| DE60211093D1 (de) | 2006-06-08 |

| JP2003142994A (ja) | 2003-05-16 |

| DE60211093T2 (de) | 2007-02-01 |

| TWI240281B (en) | 2005-09-21 |

| US20030072184A1 (en) | 2003-04-17 |

| CN1412779A (zh) | 2003-04-23 |

| EP1303044A1 (en) | 2003-04-16 |

| EP1303044B1 (en) | 2006-05-03 |

| US6614697B2 (en) | 2003-09-02 |

| KR20030031423A (ko) | 2003-04-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6618295B2 (en) | Method and apparatus for biasing selected and unselected array lines when writing a memory array | |

| US6545898B1 (en) | Method and apparatus for writing memory arrays using external source of high programming voltage | |

| US6504753B1 (en) | Method and apparatus for discharging memory array lines | |

| KR101031133B1 (ko) | 반도체 장치 | |

| US6859410B2 (en) | Tree decoder structure particularly well-suited to interfacing array lines having extremely small layout pitch | |

| CN102467971B (zh) | 包括熔丝阵列的半导体器件和操作其的方法 | |

| US6633509B2 (en) | Partial selection of passive element memory cell sub-arrays for write operations | |

| JP5544442B2 (ja) | ページ消去機能におけるアドレス変化検出によるデコーディング制御 | |

| US20030002338A1 (en) | Biasing scheme of floating unselected wordlines and bitlines of a diode-based memory array | |

| KR102515463B1 (ko) | 비휘발성 메모리 장치와, 이의 리드 및 라이트 방법 | |

| TW200837753A (en) | Semiconductor memory device | |

| US7263017B2 (en) | AC sensing for a resistive memory | |

| US6768696B2 (en) | Semiconductor memory device in which data are read and written asynchronously with application of address signal | |

| JP3961392B2 (ja) | ダイオードベースのマルチプレクサ | |

| US8526217B2 (en) | Low-complexity electronic circuit and methods of forming the same | |

| US20250054529A1 (en) | Sram with fast, controlled peak current, power efficient array reset, and data corruption modes for secure applications | |

| US6072713A (en) | Data storage circuit using shared bit line and method therefor | |

| US9142294B2 (en) | Nonvolatile resistive memory device and writing method | |

| US7978547B2 (en) | Data I/O control signal generating circuit in a semiconductor memory apparatus | |

| JP2003178595A (ja) | 固体メモリのフォールトトレラントなアドレスロジック | |

| US20250054528A1 (en) | Sram with fast, controlled peak current, power efficient array reset, and data corruption modes for secure applications | |

| JPH06500421A (ja) | Bi―CMOSメモリ | |

| JPH0460996A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040628 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040628 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060314 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060328 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20060628 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20060703 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20061121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070319 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20070327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070417 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070516 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3961392 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110525 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110525 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110525 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110525 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120525 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120525 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130525 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |