JP3800520B2 - 半導体集積回路装置と半導体装置 - Google Patents

半導体集積回路装置と半導体装置 Download PDFInfo

- Publication number

- JP3800520B2 JP3800520B2 JP2002046740A JP2002046740A JP3800520B2 JP 3800520 B2 JP3800520 B2 JP 3800520B2 JP 2002046740 A JP2002046740 A JP 2002046740A JP 2002046740 A JP2002046740 A JP 2002046740A JP 3800520 B2 JP3800520 B2 JP 3800520B2

- Authority

- JP

- Japan

- Prior art keywords

- mosfet

- pair

- transistor

- drain

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 46

- 230000000295 complement effect Effects 0.000 claims description 13

- 230000003321 amplification Effects 0.000 claims description 9

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 9

- 238000010586 diagram Methods 0.000 description 25

- 239000000758 substrate Substances 0.000 description 9

- 238000000034 method Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 230000008054 signal transmission Effects 0.000 description 4

- 102100028945 Developmentally-regulated GTP-binding protein 1 Human genes 0.000 description 3

- 102100037711 Developmentally-regulated GTP-binding protein 2 Human genes 0.000 description 3

- 101000838507 Homo sapiens Developmentally-regulated GTP-binding protein 1 Proteins 0.000 description 3

- 101000880940 Homo sapiens Developmentally-regulated GTP-binding protein 2 Proteins 0.000 description 3

- 101000979748 Homo sapiens Protein NDRG1 Proteins 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 230000001360 synchronised effect Effects 0.000 description 3

- 101100464782 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CMP2 gene Proteins 0.000 description 2

- 101100464779 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CNA1 gene Proteins 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 241000080590 Niso Species 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000004570 scanning spreading resistance microscopy Methods 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

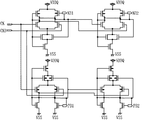

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

- H03F3/4521—Complementary long tailed pairs having parallel inputs and being supplied in parallel

- H03F3/45219—Folded cascode stages

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/72—Gated amplifiers, i.e. amplifiers which are rendered operative or inoperative by means of a control signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45396—Indexing scheme relating to differential amplifiers the AAC comprising one or more switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45506—Indexing scheme relating to differential amplifiers the CSC comprising only one switch

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

- Logic Circuits (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002046740A JP3800520B2 (ja) | 2002-02-22 | 2002-02-22 | 半導体集積回路装置と半導体装置 |

| US10/360,868 US6806743B2 (en) | 2002-02-22 | 2003-02-10 | Semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002046740A JP3800520B2 (ja) | 2002-02-22 | 2002-02-22 | 半導体集積回路装置と半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003249829A JP2003249829A (ja) | 2003-09-05 |

| JP2003249829A5 JP2003249829A5 (enExample) | 2005-08-04 |

| JP3800520B2 true JP3800520B2 (ja) | 2006-07-26 |

Family

ID=27750653

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002046740A Expired - Fee Related JP3800520B2 (ja) | 2002-02-22 | 2002-02-22 | 半導体集積回路装置と半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6806743B2 (enExample) |

| JP (1) | JP3800520B2 (enExample) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4532847B2 (ja) * | 2003-05-16 | 2010-08-25 | 株式会社リコー | 差動増幅器 |

| KR100577566B1 (ko) * | 2004-12-28 | 2006-05-08 | 삼성전자주식회사 | 입력버퍼회로 |

| US7310018B2 (en) | 2005-08-23 | 2007-12-18 | Micron Technology, Inc. | Method and apparatus providing input buffer design using common-mode feedback |

| JP4626456B2 (ja) * | 2005-09-13 | 2011-02-09 | ソニー株式会社 | 差動増幅回路、レシーバ回路、発振回路及びドライバ回路 |

| US8010813B2 (en) * | 2005-11-30 | 2011-08-30 | International Business Machines Corporation | Structure for system for extending the useful life of another system |

| US7437620B2 (en) * | 2005-11-30 | 2008-10-14 | International Business Machines Corporation | Method and system for extending the useful life of another system |

| US7425847B2 (en) * | 2006-02-03 | 2008-09-16 | Micron Technology, Inc. | Input buffer with optimal biasing and method thereof |

| KR101159045B1 (ko) | 2006-05-04 | 2012-06-25 | 삼성전자주식회사 | 레귤레이티드 캐스코드 회로 및 이를 구비하는 증폭기 |

| WO2015046025A1 (en) * | 2013-09-26 | 2015-04-02 | Semiconductor Energy Laboratory Co., Ltd. | Switch circuit, semiconductor device, and system |

| KR102609662B1 (ko) * | 2018-04-20 | 2023-12-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP7655742B2 (ja) * | 2021-03-03 | 2025-04-02 | キヤノン株式会社 | 比較器、光電変換装置、および機器 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4958133A (en) * | 1989-11-13 | 1990-09-18 | Intel Corporation | CMOS complementary self-biased differential amplifier with rail-to-rail common-mode input-voltage range |

| JP3519499B2 (ja) * | 1995-05-11 | 2004-04-12 | 株式会社ルネサステクノロジ | 相補差動増幅器およびそれを備える半導体メモリ装置 |

| US5815020A (en) * | 1996-09-24 | 1998-09-29 | Motorola, Inc. | Balance differential receiver |

| DE19725286A1 (de) * | 1997-06-14 | 1998-12-17 | Philips Patentverwaltung | Schaltungsanordnung mit einer Differenzverstärkerstufe |

| US6549971B1 (en) * | 1999-08-26 | 2003-04-15 | International Business Machines Corporation | Cascaded differential receiver circuit |

-

2002

- 2002-02-22 JP JP2002046740A patent/JP3800520B2/ja not_active Expired - Fee Related

-

2003

- 2003-02-10 US US10/360,868 patent/US6806743B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003249829A (ja) | 2003-09-05 |

| US20030160639A1 (en) | 2003-08-28 |

| US6806743B2 (en) | 2004-10-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4584492A (en) | Temperature and process stable MOS input buffer | |

| US6271687B1 (en) | Sense amplifier circuit | |

| US4074151A (en) | MOS interchip receiver differential amplifiers employing CMOS amplifiers having parallel connected CMOS transistors as feedback shunt impedance paths | |

| US6051999A (en) | Low voltage programmable complementary input stage sense amplifier | |

| KR100303735B1 (ko) | 메모리회로 | |

| US5537066A (en) | Flip-flop type amplifier circuit | |

| JP3800520B2 (ja) | 半導体集積回路装置と半導体装置 | |

| US5355028A (en) | Lower power CMOS buffer amplifier for use in integrated circuit substrate bias generators | |

| US5699305A (en) | Amplifier and semiconductor memory device having the same | |

| US5294847A (en) | Latching sense amplifier | |

| US5880990A (en) | Dual port memory apparatus operating a low voltage to maintain low operating current during charging and discharging | |

| JPH06349274A (ja) | 半導体集積回路のデータ入出力線センシング回路 | |

| JP2756797B2 (ja) | Fetセンス・アンプ | |

| US5172340A (en) | Double stage bipolar sense amplifier for BICMOS SRAMS with a common base amplifier in the final stage | |

| EP0316877B1 (en) | Semiconductor memory device with improved output circuit | |

| US6879524B2 (en) | Memory I/O buffer using shared read/write circuitry | |

| US5134319A (en) | Bicmos differential amplifier having improved switching speed | |

| EP1057185B1 (en) | Current sense amplifier | |

| US7737781B2 (en) | Differential amplifier and input circuit using the same | |

| KR0185386B1 (ko) | 센스 증폭기를 구비한 집적 메모리 | |

| US6570811B1 (en) | Writing operation control circuit and semiconductor memory using the same | |

| JP2000090683A (ja) | センスアンプ回路 | |

| JPS6299981A (ja) | スタテイツクram | |

| JP2802920B2 (ja) | 半導体集積回路装置 | |

| US5943274A (en) | Method and apparatus for amplifying a signal to produce a latched digital signal |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040329 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040331 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050107 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060117 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060201 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060330 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060420 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060420 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100512 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110512 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110512 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110512 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120512 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120512 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130512 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |