JP3788037B2 - GaN single crystal substrate - Google Patents

GaN single crystal substrate Download PDFInfo

- Publication number

- JP3788037B2 JP3788037B2 JP17127698A JP17127698A JP3788037B2 JP 3788037 B2 JP3788037 B2 JP 3788037B2 JP 17127698 A JP17127698 A JP 17127698A JP 17127698 A JP17127698 A JP 17127698A JP 3788037 B2 JP3788037 B2 JP 3788037B2

- Authority

- JP

- Japan

- Prior art keywords

- gan

- substrate

- mask

- gaas

- single crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Recrystallisation Techniques (AREA)

- Semiconductor Lasers (AREA)

- Led Devices (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

Description

【0001】

本発明は、III−V族窒化物化合物半導体(GaN系)を用いた発光ダイオード(LED)やレーザダイオード(LD)など青色発光素子用のGaN単結晶基板に関する。

【0002】

【従来の技術】

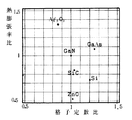

図1はGaN成長のための基板となりうる材料のGaNに対する格子定数と熱膨張率の比を示す。サファイヤ(Al2O3)、SiC、Si、GaAs、ZnOなどが比較衡量される。窒化物系半導体発光デバイス或いはGaN系発光デバイスは従来サファイヤ基板の上にGaN薄膜などをエピタキシャル成長して作られていた。サファイヤ(Al2O3)基板は化学的に安定であるし耐熱性もある。GaNと格子定数は16%程度異なるもののバッファ層を形成することによりGaNがその上にエピタキシャル成長する。このような利点があるからサファイヤ基板を使う。GaNなどの薄膜を付けたあともサファイヤ基板は付いたままLED、LDとして用いられる。つまりサファイヤとGaNの複合的な素子である。これは実用的な素子であって、サファイヤ基板上のGaN系LEDは市販されている。またGaN系LDも近く市販されるだろうと言われている。

【0003】

サファイヤとGaNの格子定数は食い違う。それにも拘らずサファイヤ基板上には実用的なGaN素子が成長する。それは格子定数の緩和が滑らかに起こるからである。図2はサファイヤ上のGaNの膜厚と、格子定数変化の関係を示すグラフである。膜厚の変化に従って格子定数がゆっくりと変化してゆく。いまなお基板としてサファイヤがもっとも優れている。現在量産されているものは全てGaN/Al2O3構造を持つ。このような構造は例えば次の文献に説明されている。

▲1▼特開平5−183189号

▲2▼特開平6−260680号

【0004】

ところがサファイヤ基板にもなお問題がある。サファイヤ基板上のGaNエピタキシャル層の欠陥密度は極めて高い。これは格子のミスマッチからくるのであろうか。なんと109cm−2もの欠陥密度がある。いわば欠陥だらけと言って良い。しかしそれにもの拘らずGaNLEDは長寿命である。不思議な材料である。だから高密度欠陥というのは結晶学的には問題であろうが実際にはあまり問題でないとも言える。

【0005】

しかしサファイヤにはもうひとつ機械的な難点がある。サファイヤ(Al2O3)は化学的に安定で硬度が高い。化学的に安定ということは良いようであるがそうでもない。GaNを残し、基板だけをエッチング除去できない。最も困るのは劈開性がないということである。それに硬い。GaN/サファイヤ基板をLEDチップに分割するときのダイシング加工が難しい。自然劈開がないから刃物状のものを押し当てて破壊切断する。破損することもあり歩留まりは低い。なお、GaN/サファイヤ基板から、サファイヤをポリッシュで除去して、実験した例が報告されている。

▲3▼J.J.Appl.Phys. vol. 37,Part2, No.3B(1988),ppL309-L312

がいまだ実験室レベルのものである。

【0006】

ダイシングを容易に行うためにSiCのような劈開性のある材料を基板にすることが考えられた。SiC基板GaN素子は例えば

▲4▼Appl.Phys.Lett. vol.71, No.17 (1997)

に提案されている。しかしSiCにも問題がある。化学的に安定であり、作製のための処理温度が1500℃以上にもなる。SiC基板自体の製造が難しい。ために高価な基板となり、GaN発光素子がコスト高になる。実際にはSiCはGaN発光素子の基板として利用されていない。SiC/GaN素子は量産規模では製造されていない。

【0007】

いずれにしても従来のGaN素子は、異種基板の上にGaNを成長させたもので基板を除去しないから、サファイヤが付いたままである。複合デバイスである。

【0008】

基板上にGaNをエピタキシャル成長させるには基板を1000℃以上の高温に加熱しなければならない。このような高温でないと気相反応が起こらない。GaNなどのエピタキシャル層を成長させた後温度を下げると薄膜と基板との熱膨張係数の違いによる影響が現れる。熱膨張係数は温度の関数であって一定でない。だから簡単に比較はできないがあらましの比較をすると次のようである。GaNの熱膨張係数を1とすると、GaAsは約1.08倍、SiCは0.87倍、サファイヤは1.36倍の熱膨張係数を持つ。

【0009】

薄膜、基板間の熱膨張係数の違いによる第1の問題は、GaN薄膜に熱応力が発生しGaN薄膜に欠陥やマイクロクラックなどが入ってしまう事である。熱膨張係数相違による第2の問題は、冷却時に反りが発生するということである。ウエハ−の全体が反りによる変形を受ける。第3の問題は大きい複合GaN基板ができないということである。サファイヤ基板にGaNの薄膜を載せた複合物はGaN基板と言えない事はない。しかし薄膜・基板間に熱膨張係数の差による熱応力や反りが大きいために大型複合基板とすることができない。高々数mm角のGaN/サファイヤによるGaN複合体が報告されていただけである。とても工業的に利用可能な大きさでない。

【0010】

振り返ってみれば、GaAsを基板として、GaNを成長させる試みが1970年代に精力的に推進された。GaAsとGaNの熱膨張率の差異はこれらの候補の中でもっとも小さい。熱膨張係数差が小さいので反りや欠陥も少ないはずである。しかしこれらの勇敢な試みはことごとく失敗に終わった。GaAsにうまくGaNが付かなかった。GaNが単結晶でないとか欠陥密度が高すぎる、GaNが剥離するとかで、良質の複合GaN基板は作製できなかった。その理由ははっきりしない。いくつもの原因があったのであろう。ひとつには成長時の高温中でのGaAsのAsの蒸発や、NH3との反応のために、良いGaN結晶が成長できず、GaAs基板上のGaN成長はほとんど有望視されていなかった。また格子定数がGaAsとGaNとでかなり違うからであろうか。GaNの格子定数を1とすると、GaAsは1.25である。約5/4も違う。SiCの格子定数は、1.03倍でGaNに近い値である。サファイヤの格子定数はGaNの0.86倍である。格子定数で言えばGaAsは、GaNに最も遠い。GaN/GaAsという複合デバイスはすでに20年も前に試みられ諦められた組み合わせであった。

【0011】

現在も生き残っているのはGaN/サファイヤの素子だけである。であるからサファイヤ基板法をより純化する、というのがひとつの開発のあり方になろう。いくら転位密度が高くても良い、LEDは長寿命だといっても、転位密度が低ければもっと長寿命かもしれない。それに青色LDはいまだ満足できる寿命でない。それはやはり高密度に存在する欠陥のせいかもしれない。サファイヤ基板でより低欠陥のGaNを成長させるという試みがさらになされる。

▲5▼電子情報通信学会論文誌C−II,vol.J81−C−II,p58〜64これはサファイヤ基板にストライプ状(縞状)のマスクをつけその上にGaNを厚膜成長させたものである。縦縞(ストライプ)によって横方向には分離された面からGaNが成長しやがてストライプを越えて合体する。そのようなストライプ成長によって欠陥密度が大幅に減退したと報告している。欠陥密度が減ったのであれば一つの成果である。しかしサファイヤ基板上ストライプ成長法は他の問題に対して沈黙している。あくまでサファイヤ上の成長で、サファイヤ基板が付いたままである。頑固な無劈開の問題を解決していない。無劈開だからダイシング工程が難しく歩留まりが悪い。サファイヤがついたままであるから熱膨張係数の差のため、GaN単結晶に転位、マイクロクラックが多数導入される。また反りが無視できない。反りのためウエハ−プロセスに不適である、という問題もある。

【0012】

熱膨張係数の差、格子定数の差は異種材料を使う限り常につきまとう。最も理想的な基板はGaN基板である。なんといってもGaN基板である。しかし広いGaN基板が存在しない。ウエハ−として半導体製造工程に適するのは1インチ径以上、好ましくは2インチ径以上のものが必要である。けれどもそんな大きいGaN基板はない。

【0013】

大型結晶を成長させるにはチョコラルスキー法、ブリッジマン法などがあるがいずれも原料融液から固体を凝固させる。融液から出発できるから大きい単結晶を製造することができる。しかしGaNは加熱しただけでは融液にならない。昇華して気体になってしまう。Gaに少量のGaNを添加して、数万気圧の超高圧を掛け加熱してGa−GaN融液とすることはできる。しかし超高圧にできる空間は極極狭い。狭い空間で大きい結晶を作ることはできない。大型の超高圧装置を製造するというのでは余りにコスト高になって現実的でない。大型結晶を製造する方法が適用できないから、これまで大型のGaN結晶ができず、GaN基板も存在しなかった。

【0014】

GaN薄膜は薄膜成長法により作られる。これらはいずれも気相から固相への反応である。サファイヤ基板の上に、GaN薄膜を成長させるため以下の4つの方法が知られている。

1.HVPE法(ハイドライド気相成長法:Hydride Vapor Phase Epitaxy)

2.MOC法(有機金属塩化物気相成長法:metallorganic chloride method)

3.MOCVD法(有機金属CVD法:metallorganic chemical vapor deposition)

4.昇華法

【0015】

MOC法は、トリメチルガリウムTMGなどGaの有機金属と、HClガスをホットウオール型の炉内で反応させ一旦GaClを合成し、これと基板付近に流したアンモニアNH3と反応させ、加熱した基板の上にGaN薄膜を成長させるものである。実際には水素をキャリヤガスとして、有機金属ガス、HClガスの輸送を行う。Ga原料として有機金属を用いるから炭素がGaNの中に不純物として混入する。炭素のために黄色を呈する。無色透明のGaN結晶を得ることは困難である。炭素のためにキャリヤ濃度(自由電子)が増加し、電子移動度が低下する。炭素のために電気特性も悪くなる。有機金属塩化物気相製法は優れた方法であるが、なおこのような欠点がある。

【0016】

MOCVD法はGaN薄膜成長法として最も頻用される。コールドウオール型の反応炉において、TMGなどGaの有機金属とアンモニアNH3を水素ガスとともに、加熱された基板上に吹き付ける。基板上でTMGとNH3が反応しGaN薄膜ができる。この方法は大量のガスを用いるので、原料ガス収率が低い。発光層のように薄い層を形成する場合には、大きな問題にならないかも知れない。しかし本願のように、厚いGaN基板を作ろうとするとこの問題は深刻な難点になる。またMOC法と同じように炭素混入の問題がある。黄色に着色する。電気特性が HVPE法はGa原料として金属Gaを使う。ホットウオール型反応炉にGa溜を設けGa金属を入れておく。Gaは融点が低いので30℃以上でGa融液になる。そこへ水素ガス、HClガスを吹き付けると、塩化ガリウムGaClができる。GaClがキャリヤガスH2によって基板の付近へ運ばれ、アンモニアと反応してGaNが基板表面に堆積する。この方法は金属Gaを使い炭素を原料中に含まない。炭素が薄膜に混入しないから着色しない。電子移動度も低下しない、などの利点がある。

【0017】

【発明が解決しようとする課題】

GaN発光素子を作製する基板はGaN単結晶が最も適する。大型GaN基板がこれまで存在しなかった。基板にできるような広い面積をもち自立できるGaN結晶を提供することが本発明の第1の目的である。反りがないGaN基板を提供する事が本発明の第2の目的である。炭素を含まず無色透明のGaN基板を提供する事が本発明の第3の目的である。但し成長条件によっては、蒸気圧の高いAsがGaN単結晶中に取り込まれて薄い茶色を呈する場合もある。GaN単結晶インゴットを製造しこれを薄く切断することによって複数のウエハ−を製造する方法を提供する事が本発明の第4の目的である。

【0018】

【課題を解決するための手段】

GaAs(111)単結晶基板の上に[11−2]方向に等間隔で並び[−110]方向にも等間隔で分布する窓を有するマスクをつけ、マスクの窓の部分に低温でGaNバッファ層を成長させ、ついで高温にしてGaN層をバッファ層の上とマスクの上にHVPE法によってエピタキシャル成長させ、GaAs基板を除去してGaN単結晶基板を製造する。これは1枚の基板を作る方法である。あるいはこの単結晶基板を種結晶として、さらにその上にGaNエピタキシャル層を厚く形成して、少なくとも10mmの厚みを有するGaNインゴットとし、これを切断或いは劈開して複数のGaN基板とする。これが本発明のGaN基板の製造方法である。GaAs基板は王水でエッチングすることによって除去できる。さらにGaNの表面は研磨して平滑にする。このように薄膜の製造方法であるエピタキシャル成長法を利用して大型結晶を作ってしまう。

【0019】

本発明のGaN結晶の最大の特徴はその大きさにある。本発明ではGaN基板の直径は1インチ以上、好ましくは2インチ径以上とする。LEDなどの発光素子を工業的に低コストで製造するためにはGaN基板が広い方が良い。それで20mm角以上好ましくは1インチ(25mm)以上、さらに好ましくは2インチ以上とするのである。出発材料であるGaAs基板が広ければ大面積のGaN結晶を製造できる。

【0020】

GaN基板の厚みは自立できハンドリングに不便がないようなものでなければならない。そのためには50μm〜1mm程度がよい。1mmを越えても半導体素子を製造できるがウエハ−自体の価格が高くなってしまう。50μm以下の厚みだと自らの形状を保持できない。より好ましくは70μm〜1mmという厚みである。

【0021】

HVPE法を採用するのは、炭素が原料に含まれないようにするためである。炭素がGaNに含まれないから黄色に殆ど着色しない。炭素によって電子がキャリヤとして加わり電子移動度を下げるということもない。炭素が入らないからGaNは無色透明のウエハ−になる。実際本発明のGaNウエハ−を文字の上におくと、下地の文字が透けて見える。まるでガラスのようである。原料からの混入はない。しかし、GaAs基板側から蒸発したAsなどの混入によりうすい黄色、薄茶色、暗灰色を帯びる場合もある。しかしマスク層とバッファ層がGaAs基板からのAsの蒸発を防ぐのでGaN中へのAsの混入量は極めて少ない。その量は1017個cm−3以下である。Asの量が多いとGaNの結晶性が乱れる。LEDとした場合はAsが特性を劣化させる。しかしHVPE法によればその恐れはない。

【0022】

【発明の実施の形態】

本発明のGaN製造はGaAs基板から出発する。サファイヤではない。サファイヤ基板は後から除去できない。ところがGaAsは王水で時間を掛けて除去することができる。先に説明したようにGaAs基板は1970年代に盛んに試みられ一旦は見込み無しとして見捨てられた手法であった。それをなぜにいまになって取り上げるのか?ラテラル成長法という有力な薄膜成長法を本発明者が新たに見いだしたからである。これは島状の窓を有するマスクによってGaAs基板を覆い、孤立した窓からGaNを独立に成長させる手法である。本発明者等が開発したこの手法がGaAs基板上のGaNを現実的な意味あるものにしたのである(特願平10−078333号)。

【0023】

GaNは六方晶系である。(0001)面は六回対称性がある。GaAsは立方晶系であるから(100)や(110)面は3回対称性を持たない。そこでGaAs(111)A面或いはB面を基板として用いる。これは三回対称性のある軸に直交する面である。A面というのはGa原子が露出している面である。B面はAs原子の露呈している面である。

【0024】

図3はラテラル成長に使うマスクの一部を示す。マスクは直接にはGaNが付かないようなSi3N4やSiO2などが良い。マスク厚みは100nm〜数100nmである。等間隔に窓を有するマスクである。窓は小さい正方形である。数μm直径の小さな窓である。これは別段丸でも三角でも楕円、六角形などでも良い。微細な加工であるから丸や楕円の方が加工しやすい。配列が重要である。[11−2]方向に列をなして並ぶ。間隔をLとする。それと直交する[−110]方向に隣接する列は半ピッチずれている。隣接列との距離をdとする。好ましくはd=31/2L/2とする。つまり正三角形の頂点に窓が配置されるのが最も良い。例えば窓を1辺2μmの正方形とし、窓ピッチLを6μm、列間隔dを5μmと言うようにすることもできる。そのような正三角形分布の窓が良いのは、図5のように隣接窓から成長したGaNが同時に境界を接するようになるからである。しかしながら、dやLが多少上記の式から外れても良い。

またストライプ状の窓を有するマスクでもGaNを成長させることはできる。ストライプ状の窓を用いると、マスク面全面がGaNで覆われるまでの時間が短いという長所がある。ただしやはり欠陥が多く反りの大きくなる傾向がある。

【0025】

窓付きのマスク越しにGaNを成長させるラテラル成長法はつぎのような意味を持つ。マスクとGaNが直接には結合しないから下地のGaAsと薄膜GaNが結合するのは窓の部分だけである。通常のGaN成長の場合には、バッファ層上で、数多くの核生成がなされ、互いに犇めき合って成長して行く。その際多くの欠陥が導入される。本発明のようにマスクがある場合は、マスクからはみ出して横方向に成長する分を妨害するものはない。妨害がないから殆ど欠陥なく成長すると考えられる。接合面積が狭いから高温で成長後、温度を下げても熱応力が緩和される。全面積で密合している場合に比較して窓だけでつながっているラテラル成長層は熱応力がよほど小さくなる。それだけだとどのような配列分布の窓でも良い事になる。そうではなくて、図5のように正六角形が同時に接触し、以後均等な厚みに成長する可能性があるような窓分布が望ましいのである。なお図4、5の正六角形は、六角錐の底部の形状を示したものである。

【0026】

マスクをつけるにはGaAs基板の全体にマスク材料を被覆し、フォトリソグラフィによって等間隔に窓を開けるようにする。同じ状態を図6(1)に断面によって示している。

【0027】

この後比較的低温450℃〜500℃程度で、HVPE法によって数10nm〜100nm程度の薄いGaNバッファ層を形成する。マスクより薄いから、バッファ層は窓内に孤立して存在する。図6(2)はその状態を示している。

【0028】

800℃〜1050℃程度の高温にして、HVPE法でGaNエピタキシャル層を形成する。この時バッファ層は結晶化する。図4のように孤立した窓で核発生したGaN結晶は通常六角錐を形成する。核発生後、六角錐が高さ方向と底部側方に次第に成長する。底面は六角形状に広がり窓を埋める。やがてGaNはマスクをこえて広がる。それも六角錐の形状を保持したままである。図5のように隣接窓からの結晶と接触し上に向けて成長する。このエピタキシャル成長層の厚みによって基板結晶の大きさが決まる。1枚のウエハ−は70μm〜1mmの厚みをもつのでその程度の厚みであれば良い。これが図6(3)の状態である。上記のような成長過程をとるので、成長表面は荒れていて擦りガラス状である。透明とするためには研磨しなければならない。

【0029】

さらに王水によってGaAs部分をエッチング除去する。マスクの部分は研磨によって除く。図6(4)の状態になる。これは1枚のGaN結晶である。透明であり自立している。1枚のウエハ−だけを作るのであればこれで終わりである。

【0030】

さらに複数のウエハ−を製造したいのであれば、この基板を種結晶として、さらにエピタキシャル成長させる。図7はこれを示す。図7(1)はGaN基板の上にHVPE法によってさらに厚くGaNをエピタキシャル成長したものを示す。円柱径のGaNインゴットになる。厚みは10mm以上とする。側面に支持部材を固定し、内周刃スライサーなどによって1枚1枚ウエハ−に切り出して行く。図7(2)はこれを示す。アズカットウエハ−を研磨して図7(3)のように透明平滑なGaNウエハ−ができる。この場合、AsはGaN結晶に混入しない。

【0031】

本発明においてエピタキシャル成長に用いるHVPE法を図8によって説明する。縦長の反応炉1を円筒形のヒ−タ2が取り囲んでいる。反応炉1の上頂部には原料ガス導入口3、4がある。原料ガス導入口3からはHCl+H2の原料ガスが導入される。H2はキャリヤガスである。その直下にはGa溜5がある。ここには金属Gaを収容しておく。融点が低いからヒ−タ2によって加熱されGa融液6になる。HClがGa融液に吹き付けられるから、Ga+HCl→GaClという反応が起こり塩化ガリウムGaClができる。このGaClとキャリヤガスH2の混合ガスが反応炉中の空間を下方に運ばれる。原料ガス導入口4はより下方に開口する。アンモニアNH3+水素H2の混合ガスがここから反応炉内に導入される。GaClとNH3により、GaCl+NH3→GaNの反応が起こる。

【0032】

サセプタ7はシャフト8によって回転昇降自在に設けられる。サセプタ7の上にはGaAs基板9またはGaN基板が取り付けられる。基板は加熱されているから気相反応した生成物GaNが基板の上に付着する。排ガスは排ガス出口10から排出される。HVPE法はGa金属を原料として使う。そしてGaClを中間生成物として作る。これが特徴である。

【0033】

エピタキシャル成長は原料を気体にしなければならないがGaを含む気体というものはない。Ga自体は30℃以上で液体である。気体にするため有機金属を使うのがMOC法、MOCVD法である。気体にはなるが炭素を含むからGaN結晶に炭素が不純物として混入してしまう。HVPE法はGaを加熱して液体にし、HClと反応させGaClにする。優勢な水素ガスによって気体として運ばれるのである。有機金属を使わないから炭素が不純物として結晶中に入らない、という長所がある。

【0034】

本発明によって作られたGaN単結晶基板は、ノンドープであるがn型である。キャリヤ濃度は1×1016cm−3程度である。n型の伝導性を与えるものは原料ガスに微量含まれる酸素であることを本発明者は見いだした。HVPE法炉中の酸素分圧を制御することによってキャリヤ濃度を1×1016cm−3〜1×1020cm−3の範囲で制御できる。酸素分圧を制御することによって、電子移動度は80cm2/Vs〜800cm2/Vsの範囲に調整できる。比抵抗は1×10−4Ωcm〜1×10Ωcmの範囲で制御可能である。キャリヤ濃度は5×1017cm−3〜1019cm−3の範囲が望ましく、比抵抗は5×10−2Ωcm以下の範囲がさらに望ましい。

【0035】

こうして作られたGaN基板は優れた特徴がある。広い。自立膜である。透明である。無色である、などの性質である。ただし成長条件により黄色、薄茶色、暗灰色である。光デバイス用基板としては光の吸収が少ないことが要件である。だから無色透明であることが要求される。GaN基板として重要なことである。基板の透明度はLambert-Beer則により記述され次の式で与えられる。

I = I0exp(−αx)

ここでI0は入射光の強度、Iは観測光の強度、αは吸収係数、xは基板の厚さである。αが小さいほど光の透過度が高く透明であることを示している。本発明によって得られたGaN基板の吸収係数は、400nm〜600nmにわたって低く、GaN基板はこれらの波長の光に対し高い透明度を有している。両面を研磨したGaN基板について吸収係数を測定した。本発明によれば、この波長帯で吸収係数が120cm−1以下のものを容易に得ることができた。さらに吸収係数が80cm−1以下のものをも作製できた。光デバイス用基板としては吸収係数が小さければ小さい程よい。

しかしながらそれだけでは不十分である。まだまだ問題がある。それはなにか?歪と内部応力の問題である。内部応力が大きいと反りが甚だしくなりフォトリソグラフィなどウエハ−プロセスに支障を来す。

【0036】

加熱したGaAs基板の上にGaNを成長させて常温に下ろして装置から複合体を取り出す。熱膨張係数が違うから、降温することによって歪が異なる。図9のようにGaN/GaAs複合体が撓む。GaNには応力が発生している。GaAsにも反対向きの応力が発生している。応力には2種類のものがある。熱応力と真性応力である。熱応力は熱膨張係数の異なる二つの異質材料が張り合わされているときに温度変化があることによって発生するものである。

【0037】

もしも熱応力だけだとすると、GaAs基板を除去すると熱応力も消失する。それゆえ図10のようにGaNは平坦になる筈である。真性応力があるとそうはいかない。GaAs基板を取り外しても尚GaNに残留する応力がある。そのために図11のようにGaN自体が歪む。この反りはGaAsとは無関係に表面と裏面の応力の相違、厚み方向の応力の傾斜のために現れる。

【0038】

1970年代にGaAs基板上にGaNを巧みに成長させることができなかったのは真性応力が大きかった事も原因している。熱応力も含めた内部応力が大きすぎてGaNが多大の欠陥をもち剥落したりした。真性の内部応力を減らすための工夫が実は先述のマスクを用いるラテラル成長法である。孤立した窓を多数マスクに作っておき、ここからGaNバッファ層を成長させさらにエピタキシャル層を重ねて成長させる。内部応力の原因は転位などの欠陥にあると考えている。転位から切り離されているのでマスク上に成長した部分が低欠陥化しており、これによって内部応力を減らすことができる。

【0039】

それはいいのであるが、やはりなにがしかの内部応力が残留する。ためにGaN基板が反る。反りが大きいとウエハ−プロセスにかからない。反りを評価し許容される反りの上限を決めなければならない。

【0040】

図12に反りの測定法あるいは表現法の定義をしめす。一定直径のウエハ−にして平坦なテーブルの上において、中心の隆起Hを測定する。例えば2インチ直径のウエハ−に換算して、中心の浮き上がりHを求める。Hが一つの測定法であり表現法である。

【0041】

反りはウエハ−の曲がりの曲率ξ或いは曲率半径Rによっても定義でき表現できる。R=D2/8Hあるいは、ξ=8H/D2によって換算できる。Dはウエハ−の直径である。2インチウエハ−の場合はD=50mmである。

【0042】

反りまたは撓みというものは外部に現れる現象であるから直接に測定することができる。内部応力は内在的なポテンシャルであるから簡単に測定できない。

【0043】

円板が曲率δで撓むときの内部応力は

【0044】

【数1】

【0045】

によって与えられる。σは内部応力、Eは剛性率、νはポアソン比、bは基板の厚さ、dは薄膜厚さ、Iは基板直径、δは撓み(Hに当たる)である。I=50mmとした場合は、上の定義でδ=Hに当たる。これは薄膜の内部応力を撓みから計算するStoneyの式という。薄膜だけにしてしまうので(GaN単層であるから)d=bとして、

【0046】

【数2】

【0047】

この式によって、撓みδからσを計算した。反りと、曲率半径と内部応力の関係はつぎのようである。基板厚さが一定の時、内部応力が大きくなればなるほど、反りは大きく、曲率半径は小さくなる。内部応力が一定の場合、基板厚さが厚くなればなるほど、反りは低減し、曲率半径は大きくなる。本発明者らによるGaN基板については、基板上へのデバイスプロセスの容易さ、基板強度を勘案し、反り、曲率半径、内部応力の許容範囲を検討した。

【0048】

ウエハの厚さによって適当な値が変わるのであるが、一般的にいうと、

1.曲率半径R 600mm以上(曲率が1.67×10-3mm-1以下)

2.反りH(50mm直径で) 0.55mm以下

3.内部応力σ 7MPa以下

【0049】

つまり、本発明者がウエハに課した条件は、R≧600mm、H≦0.55mm、σ≦7MPaである。さらに内部応力は3MPaであるとより好ましい。曲率半径は750mm以上であるとさらに良い。

【0050】

本発明において、1枚のGaN基板を製造する方法の他に、GaN基板を種結晶としてその上にGaNを厚くエピタキシャル成長させ単結晶インゴットを製造する方法も採用している。その場合は厚みを10ミリ以上にして、数十枚のウエハを切り出すようにする。インゴットが厚いから反りは小さい。反りが少ないから精度良くスライスできる。厚さが大きいので低転位化が進んでいる。スライスして切り出したウエハも低転位である。そのため反りも少ない。

【0051】

【実施例】

[実施例1(HVPE法ラテラル成長によるGaN単結晶1枚の作製)]

GaAs(111)A基板を反応容器内に設置した。基板サイズは30mm径の円形基板とした。常圧(大気圧)CVD装置でGaAs基板上に、Si3N4層を厚さ0.1μmになるように形成した。これに規則的な分布をする窓をフォトリソグラフィによって開けた。窓は3種類のものを採用した。図3に示す千鳥ドット窓と、<11−2>ストライプ窓、<1−10>ストライプ窓の3種である。

1.千鳥ドット窓…図3〜5に示すように、GaAs<11−2>に平行な直線上に並び隣接する窓群が半ピッチずれている。d=3.5μm、L=4μm。

2.<11−2>ストライプ窓…<11−2>方向に平行な長窓(ストライプ)のマスク。ストライプの幅が2μm、間隔2μm、ピッチ4μm。

3.<1−10>ストライプ窓…<11−2>方向に平行な長窓(ストライプ)のマスク。ストライプの幅が2μmで間隔が6μm。ピッチは8μmである。

【0052】

このような窓を開けたSi3N4をマスクとして使って、GaNバッファ層とエピタキシャル層を成長させる。

(1)GaNバッファ層の形成

周期的な窓を有するマスクによって覆われたGaAs基板をHVPE装置の中に設置した。HVPE装置を真空に引いてGaAs基板を約500℃に加熱した。石英のGa溜を850℃以上に加熱しGa融液とする。原料ガス導入口から水素ガスH2と塩化水素ガスHClの混合ガスをGa溜に導き、塩化ガリウムGaClを合成した。別の原料ガス導入口から水素H2とアンモニアNH3の混合ガスを導入し、500℃に加熱された基板近傍でGaCl+NH3→GaNの反応を起こさせGaAs基板に、GaNを堆積させる。これによってGaAs基板上に約70nmのGaNバッファ層を形成する。Si3N4はGaN成長抑制作用がありSi3N4マスクの上にはGaNは堆積しない。バッファ層(70nm)はマスク(100nm)より薄い。だから窓のGaAsの部分だけにGaNバッファ層ができる。

【0053】

(2)GaNエピタキシャル層の形成

HClの導入を停止した。基板温度を500℃から約1000℃まで上げた。再びHClをGa溜に向けて導入する。以前の工程と同じように、GaとHClの反応によって塩化ガリウムGaClを合成する。水素ガスがキャリヤとして流れているからGaClは下方へともに流れる。アンモニアNH3とGaClが加熱された基板の近傍で反応しGaNができる。これが窓の中のバッファ層の上にエピタキシャル成長する。マスク厚み(100nm)を越えるとマスクの上にGaN結晶が正六角形状に広がって行く。ただしマスク全面がGaNで覆われるまでは、GaN結晶は六角錐である。図4、図5は六角錐の底面部の状況を模式的に示したものである。窓は正三角形の頂点位置にあるからそこから正六角形状に広がったGaNは隣接窓から広がってきた結晶と丁度きびすを接することになる。成長速度は等しいので正六角錐の結晶は隈無く接触する。GaN結晶層がマスクの上面を隈無く覆い尽くすと、今度は上方へGaNが堆積してゆく。成長速度は50μm/Hである。約100μmの厚みのエピタキシャル層を成長させた。このように無数の小さい窓から独立に核発生させ結晶成長させる(ラテラル成長)のでGaNの中の内部応力を大幅に低減することができる。表面は擦りガラス状であった。

【0054】

(3)GaAs基板の除去

次に試料をエッチング装置の中に設置した。王水によって約10時間エッチングした。GaAs基板が完全に除去された。GaNだけの結晶になった。両面を研磨してGaN単結晶基板とした。これは自立膜であった。マスクの窓寸法と窓ピッチL、隣接列との距離dを変えその他はほぼ同じ条件で3つの試料についてGaN成長させた。試料1は千鳥ドット窓(窓2μm角、L=4μm、d=3.5μm)。試料2は<11−2>ストライプマスクである。試料3は<1−10>ストライプマスクである。

【0055】

【表1】

【0056】

ノンドープなのであるがn型の電子伝導型である。結晶性の維持を考えるとキャリヤ濃度は低い方が良く、電子移動度は高い方が良い。しかし比抵抗は高い方が良いのである。これら電気的特性は成長条件により変化する。ストライプマスクは内部応力低減という点で不完全である。これらサンプルは透明な薄茶色である。波長400nm〜600nmでの吸収係数は、40cm−1〜80cm−1であった。Asの含有量を調べたところ、9×1016cm−3であった。

【0057】

[実施例2(HVPEラテラル成長GaN種結晶、HVPE法GaN厚付け)]

2インチ径のGaAs(111)A面を基板とした。その上にSiO2の絶縁膜を形成した。フォトリソグラフィによって図3のような窓を設けた。

(1)GaNバッファ層の形成

【0058】

マスクを有するGaAs基板をHVPE装置に設置した。図8の装置を使うが、Ga溜5は800℃に加熱した。原料ガスとしては、H2+HClをGa溜に導き、H2+NH3は基板に直接に導いた。約500℃(基板温度)の低温において、GaNバッファ層を形成した。バッファ層厚みは80nmである。

(2)エピタキシャル層の形成

ついで基板温度を1000℃に上げた。同じ原料ガスを使って、GaNエピタキシャル層80μmを形成した。

(3)GaAsの除去

GaN/GaAs基板をHVPE装置から取りだした。鏡面状にGaN連続膜が生成されていることを確認した。これを王水中でGaAs基板をエッチング除去した。

【0059】

(4)GaNの厚付け

これを十分に洗浄した。図6(4)のような状態になる。GaNだけになったものをふたたびHVPE装置にセットした。基板温度を1020℃として、HVPE法によってGaNを厚付けしGaNのインゴットを得た。図7(1)に示す状態である。このインゴットは中央部が少し窪んだ形状であった。最低高さは約20mm、外径55mmのインゴットであった。

【0060】

(5)スライサーによるウエハ−の切り出し

円周刃スライサーによってインゴットを軸方向に直角な方向に切りだした。図7(2)に示すようである。外径約50mm、厚み350μmのGaN単結晶基板20枚を得た。GaNを分析したところ、As、炭素ともにバックグランドのレベルであった。ひ素(As)、炭素が、GaNのなかに殆ど含有されていない事が分かる。

【0061】

(6)研磨

さらにラッピング研磨、仕上げ研磨をした。図7(3)のような透明ウエハ−である。機械加工をしているため基板には反りは無かった。

【0062】

(7)電気的特性の測定

インゴットの上端(成長終期の分)から取ったウエハ−の電気的特性を測定した。n型でキャリヤ濃度は5×1018cm−3であった。電子移動度は200cm2/Vsであった。比抵抗は0.017Ωcmであった。

【0063】

インゴットの下端(成長初期の分)から取ったウエハ−の電気的特性はつぎのようであった。n型でキャリヤ濃度は1018cm−3、電子移動度は150cm2/Vsであった。比抵抗は0.01Ωcmであった。これは両極端の部位の電気的特性である。中間部は中間的な値になるであろう。

【0064】

(8)光吸収の測定

これらのウエハは透明であり暗灰色か無色であった。波長400nm〜600nmにおける吸収係数は20cm−1〜40cm−1であった。

(9)LEDの作製

GaN基板ができたので、その上にInGaNを発光層とするLEDを作製した。従来のサファイヤ基板のものと比較して、発光輝度が約5倍に向上した。発光輝度が向上した理由は、転位の減少による。従来のサファイヤ基板LEDでは活性層内に多くの貫通転位が存在していたが、GaN基板の本発明のLEDは貫通転位が大きく減少しているからである。

【0065】

[実施例3(MOCラテラル成長GaN種結晶、HVPEGaN厚付け)]

GaAs(111)B面を基板として用いた。SiO2を基板に付けフォトリソグラフィによって[1−10]方向に延びるストライプ窓を形成した。

【0066】

(1)GaNバッファ層の形成

有機金属塩化物気相成長法(MOC法)によって約490℃の低温で基板上に90nmの厚みのGaNバッファ層を形成した。

【0067】

(2)GaNエピタキシャル層の形成

同じ装置において、基板温度を約970℃に上げて、GaNエピタキシャル層を25μmの厚さに形成した。

(3)GaAs基板の除去

MOC装置からGaN/GaAs試料を取りだした。鏡面のGaN単結晶が成長していた。ストライプマスクの方向は、GaNの[11−20]方向であった。つまりGaAsの[1−10]方向にGaNの[11−20]方向が成長するということである。王水によってGaAs基板を溶解除去した。

【0068】

(4)GaNの厚付け成長

25μm厚みのGaNを種結晶として、HVPE装置にセットした。1000℃に加熱しHVPE法によってGaNを厚くエピタキシャル成長させた。円柱状で最低高さが約3センチのGaNインゴットを育成した。

【0069】

(5)内周刃スライサーによるウエハ−切り出し

内周刃スライサーによってインゴットを軸直角方向に400μmの厚みに切り出した。25枚のアズカットウエハ−を切り出すことができた。

【0070】

(6)研磨

切り出したウエハ−をラッピング研磨、仕上げ研磨した。製品としてのGaN単結晶ウエハ−を得た。

(7)電気特性の測定

ウエハ−の電気的特性を測定した。n型であって、電子移動度は250cm2/Vsであった。比抵抗は0.05Ωcmであった。

【0071】

この実施例ではGaN自体を種結晶として、GaN単結晶を厚く成長させている。厚い単結晶GaNを成長させこれをスライサーで切断しているから一挙に25枚もの基板が作製できる。製造コストは、1枚1枚GaAsから成長させる場合に比較して64%に低下した。基板の製造を低コスト化できる。品質管理も含めた1枚当たりの製造時間も大きく短縮できた。GaNを分析したところ砒素(As)、炭素(C)ともにバックグランドのレベルであった。

【0072】

マスクの窓は正三角形の頂点にある位置に窓を穿つマスクが最も良い。しかしストライプ(縞状)の窓をもつものであっても良い。それなりの内部応力低減の効果がある。マスク上のラテラル成長によって、結晶内の低欠陥化が進み内部応力が低減される共にGaAsとGaNの接触面積が減り内部応力を緩和できる。ために温度変化が大きいにもかかわらず反りの発生を抑制することができる。

【0073】

[実施例4(総流量と表面モフォロジー・内部応力の関係)]

[1−100]ストライプマスク、[11−2]ストライプマスク、ドットマスクを使いHVPE法によってGaNウエハを作製した。原料ガスはH2+NH3とH2+HClである。原料ガスの総流量を増やすと表面モフォロジーが改善される。しかし内部応力は増える傾向が認められた。

【0074】

【表2】

【0075】

これらのうち、イ、ロ、ニ、ホ、ト、チ、の6つはAグループであり、ハ、ヘ、リ、ヌ、ルの5つはBグループである。

(A)Ga分圧は1kPa(10-2atm)である。970℃でバッファ層・マスクの上にGaNを1時間成長させ、1030℃でさらに3時間GaNを成長させた。合計4時間のエピタキシャル成長である。図13に白丸○によってその結果をしめす。6個の試料がある。これらは表面は平坦でありモフォロジーは良好である。ところが内部応力は大きい。クラックが発生した試料もある。図13において横軸は膜厚(μm)である。膜厚は5μm〜120μmに分布している。縦軸は内部応力(GPa)である。○の試料は内部応力が2MPa〜40MPaである。ほとんどが10MPaより大きい内部応力を呈する。しかし内部応力は7MPa以下(7×10−3GPa)が好ましい。

(B)Ga分圧は2kPaである。970℃でバッファ層・マスクの上にGaNを6時間エピタキシャル成長させた。試料の数は10個である。図13に同じように示す。膜厚は70μm〜300μmの間に分布する。GaN試料の表面は粗い。Rmaxは約20μmである。GaN基板寸法は20mm×20mmである。表面状態は悪いが内部応力は小さい。内部応力は図13に黒丸によって示すように1MPa〜10MPaである。目標は7MPa以下であるからこれを充たすことができる。しかし同じ条件であるのに膜厚に広いばらつき(70μm〜300μm)がある。反りの曲率半径RはR=780mm〜1500mmである。

【0076】

[実施例5(曲率半径の関係)]

前例と同じ(A)の試料6枚と、(B)5枚の試料について膜厚と曲率半径の関係について調べた。触針法によって反りを評価した。図14にその結果を示す。横軸は膜厚(μm)である。縦軸は曲率半径である。曲率半径は600mm以上が好ましい。

(A)970℃1時間+1030℃3時間成長の試料Aは膜厚が薄く表面は平坦であるが反りが大きい。曲率半径は200mm以下である。曲率半径の望ましい範囲は600mm以上である。6個の試料の全てが目標に達しない。

(B)970℃6時間成長の試料Bは膜厚が厚く、表面は粗面化しているが、内部応力が小さく、反りも小さい。5個のB試料のすべては600mmという望ましい範囲をこえている。マスクなし成長では、曲率半径が極めて小さくて反りが大きい。1970年代のGaAs基板の試みが失敗したのはそのような理由にもよる。

【0077】

[実施例6(研磨)]

試料Aは研磨に失敗した。試料Bのうち、膜厚150μm、内部応力4MPa、曲率半径1030mm、Rmax20μmの試料について研磨した。研磨により膜厚は80μmに減った。曲率半径は研磨後650mmに減っている。研磨によって表面粗さはRmax7.2nm、Ra2nmに減少した。研磨は表面を平滑にしているが、反りを増大させる場合もある。

[実施例7(ウエハ内の内部応力の異方性)]

ストライプマスクを使用してGaN成長した場合と、ドットマスクを使用してGaN成長した場合の内部応力を比較した。図15に示したのは、マスクと内部応力の関係を示すグラフである。

GaAsウエハ上に、<1−10>方向に伸びるストライプマスクを作製し平均膜厚(膜の厚さはバラツキがあるのでこれを平均化したもの)120μmのGaNを成長させたもの、

実施例1と同様のドットマスクを使用し、平均膜厚160μmのGaNを成長させたもの、

を使用した。

成長の条件はいずれも、Ga分圧1×10−2atm(1kPa)、NH3分圧0.24atm(24kPa)、成長時間970℃、成長時間240分である。成長の後、冷却してGaAs基板を除去した。GaN自立膜としGaNの内部応力をX線によって調べた。その結果を図15に示す。ドットマスクを使用して製造したGaN基板は、異方性が極めて少なく内部応力も小さい。それに反してストライプマスクを使用して製造したGaN基板は、ストライプ方向とそれに直交する方向に異方性がある。とくにストライプに平行な方向に大きい反りが現れる。垂直方向に比較して10倍もある。図15の方位はGaN結晶に関する方位である。GaAsの<1−10>はGaNの<11−20>に、GaAsの<11−2>は、GaNの<1−100>に対応する。GaNの<11−20>と<1−100>は直交する。

【0078】

【発明の効果】

本発明は大型のGaN単結晶ウエハを提供する。ラテラル成長法によるからGaN結晶中の転位等の欠陥が少ない。炭素を使わない手法によってGaNを厚付けするから透明度の高いウエハとなる。ラテラル成長であるから内部応力が小さく抑えられ反りも少ない。反りが僅かでフォトリソグラフィなどの既存のウエハプロセスを使うことができる。このGaN単結晶ウエハをGaN発光素子の基板として利用することができる。薄膜部分と基板が同一であるから反りが出ない。内部応力も小さい。したがって転位密度も少なくなる。発光効率が上がる。GaNLED、GaNLDの寿命が伸びる。

【図面の簡単な説明】

【図1】GaN結晶を成長させるための基板材料とGaNとの熱膨張係数、格子定数の差を、x、y座標に示すグラフ。

【図2】サファイヤ基板上にGaNエピタキシャル成長させた場合に、GaN膜厚が変化することによって格子定数が滑らかに変化することを示すグラフ。

【図3】千鳥型点状窓マスクをGaAs(111)A面に固定したものの平面図。

【図4】マスク窓から露呈した部分にGaNバッファ層をエピタキシャル成長させた状態の平面図。

【図5】GaNをマスク、バッファ層の上にさらにエピタキシャル成長させ隣接窓からの結晶が相会した時に状態を示す平面図。

【図6】GaAs基板の上にマスクを載せてGaNバッファ層、GaNエピタキシャル層を成長させ、GaAs基板をエッチング除去する工程を示す工程図。(1)はGaAs(111)基板上にマスクを形成した工程の図。(2)はマスクによって覆われていない部分にバッファ層を成長させた工程の図。(3)はバッファ層、マスクの上にGaNエピタキシャル層を成長させた工程の図。(4)はGaAs基板を除去しGaNの自立膜となった状態を示す図。

【図7】GaN基板の上にさらにGaNを厚く成長させてGaNインゴットを作りこれを切断してウエハにする工程を示す図。(1)はGaN基板に厚付けしたGaNインゴットの図。(2)はインゴットを内周刃スライサーでアズカットウエハに切断している状況を示す図。(3)は切り出されたウエハの図。

【図8】HVPE装置の概略断面図。

【図9】GaAs基板の上にGaNを成長させた複合基板が熱応力のために反っている状態を示す断面図。

【図10】もしも内部応力が0であれば、GaAsを除去した後のGaNは平坦になることを示す断面図。

【図11】もしもGaN自体のなかに内部応力が存在するならばGaAsを除去しても尚歪みが残ることを示す断面図。

【図12】 GaNウエハの反りの定義を示す図。50mm直径のウエハの中央部の盛り上がりHによって反りを表現する。

【図13】ガス流量を(A)1800sccm〜900sccmの一群と(B)900sccmの一群について、膜厚と内部応力の測定値の分布を示す図。黒丸が表面粗くてB群である。白丸が表面平滑でA群である。

【図14】同じA群試料(30枚)とB群試料(9枚)について、膜厚と曲率半径の分布を示す図。黒丸がB群、白丸がA群である。

【図15】ストライプマスクとドットマスク使用時の内部応力の異方性を測定した結果をしめすグラフ。

【符号の説明】

1 反応炉

2 ヒ−タ

3 原料ガス導入口

4 原料ガス導入口

5 Ga溜

6 Ga融液

7 サセプタ

8 シャフト

9 GaAs基板またはGaN基板

10 ガス排出口[0001]

The present invention relates to a GaN single crystal substrate for a blue light emitting element such as a light emitting diode (LED) or a laser diode (LD) using a III-V nitride compound semiconductor (GaN-based).

[0002]

[Prior art]

FIG. 1 shows the ratio of the lattice constant to the thermal expansion coefficient of GaN, which can be a substrate for GaN growth. Sapphire (Al 2 O 3 ), SiC, Si, GaAs, ZnO, and the like are weighed. A nitride-based semiconductor light-emitting device or a GaN-based light-emitting device has been conventionally produced by epitaxially growing a GaN thin film on a sapphire substrate. A sapphire (Al 2 O 3 ) substrate is chemically stable and heat resistant. By forming a buffer layer having a lattice constant different from that of GaN by about 16%, GaN is epitaxially grown thereon. Because of these advantages, a sapphire substrate is used. Even after a thin film such as GaN is attached, the sapphire substrate is still attached, and it is used as an LED or LD. In other words, it is a composite element of sapphire and GaN. This is a practical element, and GaN-based LEDs on a sapphire substrate are commercially available. It is also said that GaN-based LDs will be commercially available soon.

[0003]

Sapphire and GaN have different lattice constants. Nevertheless, practical GaN elements grow on sapphire substrates. This is because the relaxation of the lattice constant occurs smoothly. FIG. 2 is a graph showing the relationship between the film thickness of GaN on sapphire and the change in lattice constant. The lattice constant changes slowly as the film thickness changes. Sapphire is still the most excellent substrate. All currently mass-produced products have a GaN / Al 2 O 3 structure. Such a structure is described in the following document, for example.

(1) JP-A-5-183189 (2) JP-A-6-260680

However, there are still problems with sapphire substrates. The defect density of the GaN epitaxial layer on the sapphire substrate is extremely high. Does this come from a lattice mismatch? There is a defect density as high as 10 9 cm −2 . It may be said that it is full of defects. Nevertheless, GaN LEDs have a long life. It is a mysterious material. Therefore, it can be said that high-density defects may be a problem in crystallography, but not really a problem.

[0005]

But sapphire has another mechanical difficulty. Sapphire (Al 2 O 3 ) is chemically stable and has high hardness. It seems good to be chemically stable, but it is not. GaN remains, and only the substrate cannot be removed by etching. The most troublesome is the lack of cleavage. Hard to it. Dicing when dividing the GaN / sapphire substrate into LED chips is difficult. Because there is no natural cleavage, the blade is pressed and cut. Yield is low due to damage. An example in which sapphire was removed from a GaN / sapphire substrate by polishing was reported.

(3) JJAppl. Phys. Vol. 37,

Still at the laboratory level.

[0006]

In order to easily perform dicing, it was considered to use a material having a cleavage property such as SiC as a substrate. For example, (4) Appl. Phys. Lett. Vol. 71, No. 17 (1997).

Has been proposed. However, there is a problem with SiC. It is chemically stable and the processing temperature for production is 1500 ° C. or higher. It is difficult to manufacture the SiC substrate itself. Therefore, it becomes an expensive substrate, and the cost of the GaN light emitting device becomes high. Actually, SiC is not used as a substrate for a GaN light emitting device. SiC / GaN devices are not manufactured on a mass production scale.

[0007]

In any case, the conventional GaN element is formed by growing GaN on a heterogeneous substrate and does not remove the substrate, so that the sapphire remains attached. It is a composite device.

[0008]

In order to epitaxially grow GaN on the substrate, the substrate must be heated to a high temperature of 1000 ° C. or higher. A gas phase reaction does not occur unless the temperature is high. When the temperature is lowered after growing an epitaxial layer such as GaN, an influence due to the difference in thermal expansion coefficient between the thin film and the substrate appears. The coefficient of thermal expansion is a function of temperature and is not constant. So it's not easy to compare, but a quick comparison is as follows. Assuming that the thermal expansion coefficient of GaN is 1, GaAs has a thermal expansion coefficient of approximately 1.08 times, SiC has a thermal expansion coefficient of 0.87 times, and sapphire has a thermal expansion coefficient of 1.36 times.

[0009]

The first problem due to the difference in the thermal expansion coefficient between the thin film and the substrate is that thermal stress is generated in the GaN thin film and defects or microcracks enter the GaN thin film. The second problem due to the difference in thermal expansion coefficient is that warpage occurs during cooling. The entire wafer is deformed by warping. The third problem is that a large composite GaN substrate is not possible. A composite in which a GaN thin film is placed on a sapphire substrate is not necessarily a GaN substrate. However, since the thermal stress and warpage due to the difference in thermal expansion coefficient between the thin film and the substrate are large, a large composite substrate cannot be obtained. Only a few mm square GaN / sapphire GaN composites have been reported. It is not a size that can be used industrially.

[0010]

In retrospect, attempts to grow GaN using GaAs as a substrate were vigorously promoted in the 1970s. The difference in coefficient of thermal expansion between GaAs and GaN is the smallest of these candidates. Since the difference in thermal expansion coefficient is small, there should be little warpage and defects. But all these brave attempts were unsuccessful. GaN did not attach well to GaAs. A high-quality composite GaN substrate could not be produced because GaN was not a single crystal, the defect density was too high, or GaN was peeled off. The reason is not clear. There may have been several causes. For one thing, a good GaN crystal could not be grown due to the evaporation of As of GaAs at a high temperature during growth and reaction with NH 3, and GaN growth on a GaAs substrate was hardly promising. Is it because the lattice constant is quite different between GaAs and GaN? If the lattice constant of GaN is 1, GaAs is 1.25. About 5/4 is different. The lattice constant of SiC is 1.03 and is close to GaN. The lattice constant of sapphire is 0.86 times that of GaN. In terms of lattice constant, GaAs is farthest from GaN. The GaN / GaAs composite device has already been tried and praised 20 years ago.

[0011]

Only the GaN / sapphire elements still survive today. Therefore, one way of development would be to further refine the sapphire substrate method. Even if the dislocation density is high, the LED has a long life, but if the dislocation density is low, it may have a longer life. And blue LD is still not a satisfactory life. It may be due to the high density of defects. Further attempts are made to grow GaN with lower defects on sapphire substrates.

(5) IEICE Transactions C-II, vol. J81-C-II, p58-64 This is a sapphire substrate with a striped (stripe) mask and a GaN film grown on it. GaN grows from the surfaces separated in the horizontal direction by the vertical stripes (stripes) and eventually coalesces beyond the stripes. It is reported that the defect density is greatly reduced by such stripe growth. If the defect density is reduced, it is one result. However, the stripe growth method on the sapphire substrate is silent against other problems. It is only a growth on sapphire, and the sapphire substrate remains attached. It does not solve the stubborn uncanny problem. Since it is not cleaved, the dicing process is difficult and the yield is poor. Since sapphire remains attached, many dislocations and microcracks are introduced into the GaN single crystal due to the difference in thermal expansion coefficient. Also, warping cannot be ignored. Another problem is that it is unsuitable for wafer processing due to warpage.

[0012]

The difference in coefficient of thermal expansion and the difference in lattice constant will always follow as long as different materials are used. The most ideal substrate is a GaN substrate. After all, it is a GaN substrate. However, there is no wide GaN substrate. A wafer suitable for the semiconductor manufacturing process must have a diameter of 1 inch or more, preferably 2 inches or more. But there is no such a large GaN substrate.

[0013]

For growing large crystals, there are a chocolate ski method and a Bridgman method, both of which solidify the solid from the raw material melt. Large single crystals can be produced because they can start from the melt. However, GaN cannot be melted only by heating. Sublimates and turns into gas. A small amount of GaN can be added to Ga and heated by applying an ultrahigh pressure of tens of thousands of atmospheres to obtain a Ga-GaN melt. However, the space where ultra-high pressure can be achieved is extremely narrow. Large crystals cannot be made in a small space. Manufacturing a large ultra-high pressure device is not practical because it is too costly. Since a method for producing a large crystal cannot be applied, a large GaN crystal has not been formed so far, and a GaN substrate has not existed.

[0014]

The GaN thin film is made by a thin film growth method. These are all reactions from the gas phase to the solid phase. The following four methods are known for growing a GaN thin film on a sapphire substrate.

1. HVPE (Hydride Vapor Phase Epitaxy)

2. MOC method (metallorganic chloride method)

3. MOCVD (metallorganic chemical vapor deposition)

4). Sublimation method [0015]

In the MOC method, an organometallic metal such as trimethylgallium TMG and HCl gas are reacted in a hot wall type furnace to synthesize GaCl once and react with ammonia NH 3 flowing in the vicinity of the substrate. A GaN thin film is grown thereon. In actuality, organometallic gas and HCl gas are transported using hydrogen as a carrier gas. Since an organic metal is used as a Ga raw material, carbon is mixed into GaN as an impurity. Yellow due to carbon. It is difficult to obtain a colorless and transparent GaN crystal. The carrier concentration (free electrons) increases due to carbon, and the electron mobility decreases. Due to the carbon, the electrical properties also deteriorate. The organometallic chloride vapor phase production method is an excellent method, but still has such drawbacks.

[0016]

The MOCVD method is most frequently used as a GaN thin film growth method. In a cold-wall type reactor, an organometallic metal such as TMG and ammonia NH 3 are sprayed onto a heated substrate together with hydrogen gas. TMG and NH 3 react on the substrate to form a GaN thin film. Since this method uses a large amount of gas, the raw material gas yield is low. When a thin layer such as a light emitting layer is formed, it may not be a big problem. However, this problem becomes a serious difficulty when trying to make a thick GaN substrate as in the present application. In addition, there is a problem of carbon contamination as in the MOC method. Color yellow. The electrical characteristics of the HVPE method use metallic Ga as a Ga raw material. A Ga reservoir is provided in a hot wall type reactor and Ga metal is placed therein. Since Ga has a low melting point, it becomes a Ga melt at 30 ° C. or higher. When hydrogen gas or HCl gas is sprayed there, gallium chloride GaCl is produced. GaCl is carried to the vicinity of the substrate by the carrier gas H 2 and reacts with ammonia to deposit GaN on the substrate surface. This method uses metal Ga and does not contain carbon in the raw material. It does not color because carbon does not enter the thin film. There is an advantage that the electron mobility is not lowered.

[0017]

[Problems to be solved by the invention]

A GaN single crystal is most suitable as a substrate for producing a GaN light emitting device. Large GaN substrates have not existed so far. It is a first object of the present invention to provide a GaN crystal that has a large area that can be used as a substrate and can be self-supporting. It is a second object of the present invention to provide a GaN substrate that does not warp. It is a third object of the present invention to provide a colorless and transparent GaN substrate that does not contain carbon. However, depending on the growth conditions, As having a high vapor pressure may be taken into the GaN single crystal and light brown. It is a fourth object of the present invention to provide a method of manufacturing a plurality of wafers by manufacturing a GaN single crystal ingot and cutting it into thin pieces.

[0018]

[Means for Solving the Problems]

A mask having windows arranged at equal intervals in the [11-2] direction and distributed at equal intervals in the [−110] direction is attached on a GaAs (111) single crystal substrate, and a GaN buffer is formed at a low temperature in the window portion of the mask. The layer is grown, and then the temperature is raised, and the GaN layer is epitaxially grown on the buffer layer and the mask by the HVPE method, and the GaAs substrate is removed to produce a GaN single crystal substrate. This is a method of making one substrate. Alternatively, this single crystal substrate is used as a seed crystal, and a GaN epitaxial layer is formed thickly thereon to form a GaN ingot having a thickness of at least 10 mm, which is cut or cleaved to form a plurality of GaN substrates. This is the GaN substrate manufacturing method of the present invention. The GaAs substrate can be removed by etching with aqua regia. Further, the surface of GaN is polished and smoothed. In this way, a large crystal is produced by using an epitaxial growth method which is a method for producing a thin film.

[0019]

The greatest characteristic of the GaN crystal of the present invention is its size. In the present invention, the diameter of the GaN substrate is 1 inch or more, preferably 2 inches or more. In order to manufacture light emitting elements such as LEDs at low cost industrially, a wider GaN substrate is better. Therefore, it is 20 mm square or more, preferably 1 inch (25 mm) or more, more preferably 2 inches or more. If the starting material GaAs substrate is wide, a large-area GaN crystal can be manufactured.

[0020]

The thickness of the GaN substrate must be such that it can be self-supporting and has no inconvenience in handling. For that purpose, about 50 μm to 1 mm is preferable. Even if it exceeds 1 mm, a semiconductor element can be manufactured, but the price of the wafer itself is increased. If the thickness is 50 μm or less, the shape cannot be maintained. More preferably, the thickness is 70 μm to 1 mm.

[0021]

The HVPE method is adopted so that carbon is not included in the raw material. Since carbon is not contained in GaN, it hardly colors yellow. Carbon does not add electrons as carriers and lower the electron mobility. Since carbon does not enter, GaN becomes a colorless and transparent wafer. Actually, when the GaN wafer of the present invention is placed on the letters, the letters on the base can be seen through. It looks like glass. There is no contamination from raw materials. However, there may be a light yellow, light brown, or dark gray color due to contamination of As or the like evaporated from the GaAs substrate side. However, since the mask layer and the buffer layer prevent evaporation of As from the GaAs substrate, the amount of As mixed into GaN is extremely small. The amount is 10 < 17 > cm <-3> or less. If the amount of As is large, the crystallinity of GaN is disturbed. In the case of an LED, As degrades the characteristics. However, according to the HVPE method, there is no fear.

[0022]

DETAILED DESCRIPTION OF THE INVENTION

The GaN production of the present invention starts from a GaAs substrate. Not sapphire. The sapphire substrate cannot be removed later. However, GaAs can be removed over time with aqua regia. As described above, the GaAs substrate was a method that was actively tried in the 1970s and was once abandoned as a prospect. Why do you pick it up now? This is because the present inventor newly found a powerful thin film growth method called a lateral growth method. This is a technique in which a GaAs substrate is covered with a mask having island-shaped windows, and GaN is grown independently from the isolated windows. This technique developed by the present inventors made GaN on a GaAs substrate practically meaningful (Japanese Patent Application No. 10-078333).

[0023]

GaN is hexagonal. The (0001) plane has sixfold symmetry. Since GaAs is cubic, the (100) and (110) planes do not have a three-fold symmetry. Therefore, the GaAs (111) A surface or B surface is used as a substrate. This is a plane orthogonal to an axis having threefold symmetry. The A plane is a plane where Ga atoms are exposed. The B surface is a surface where As atoms are exposed.

[0024]

FIG. 3 shows a part of a mask used for lateral growth. The mask is preferably Si 3 N 4 or SiO 2 that does not directly attach GaN. The mask thickness is 100 nm to several 100 nm. It is a mask having windows at equal intervals. The window is a small square. It is a small window with a diameter of several μm. This may be round, triangular, elliptical, hexagonal, etc. Since it is a fine process, it is easier to process a circle or ellipse. Sequence is important. [11-2] Lined up in a direction. Let L be the interval. The columns adjacent to the [−110] direction perpendicular to the same are shifted by a half pitch. Let d be the distance to the adjacent row. Preferably, d = 3 1/2 L / 2. In other words, it is best to arrange windows at the vertices of equilateral triangles. For example, the window may be a square with a side of 2 μm, the window pitch L may be 6 μm, and the column spacing d may be 5 μm. The reason why such an equilateral triangular distribution window is preferable is that GaN grown from adjacent windows simultaneously touches the boundary as shown in FIG. However, d and L may slightly deviate from the above formula.

Further, GaN can be grown even with a mask having a striped window. The use of a striped window has the advantage that the time until the entire mask surface is covered with GaN is short. However, there are still many defects and tend to be warped.

[0025]

The lateral growth method of growing GaN through a mask with a window has the following meaning. Since the mask and GaN are not directly bonded, the underlying GaAs and thin film GaN are bonded only to the window portion. In the case of normal GaN growth, a large number of nuclei are formed on the buffer layer, and they grow by striking each other. In doing so, many defects are introduced. When there is a mask as in the present invention, there is nothing that hinders the portion that protrudes from the mask and grows laterally. It is thought that it grows almost without defects because there is no interference. Since the bonding area is small, thermal stress is relaxed even if the temperature is lowered after growth at a high temperature. The lateral growth layer connected only by the window is much smaller in thermal stress than in the case where the entire area is dense. With that alone, any array distribution window can be used. Instead, it is desirable to have a window distribution in which regular hexagons contact at the same time as shown in FIG. 5 and may grow to a uniform thickness thereafter. 4 and 5 show the shape of the bottom of the hexagonal pyramid.

[0026]

To attach the mask, the entire GaAs substrate is coated with a mask material, and windows are opened at equal intervals by photolithography. The same state is shown in cross section in FIG.

[0027]

Thereafter, a thin GaN buffer layer of about several tens of nm to 100 nm is formed by HVPE at a relatively low temperature of about 450 ° C. to 500 ° C. Since it is thinner than the mask, the buffer layer is isolated in the window. FIG. 6 (2) shows this state.

[0028]

A GaN epitaxial layer is formed by HVPE at a high temperature of about 800 ° C. to 1050 ° C. At this time, the buffer layer crystallizes. As shown in FIG. 4, a GaN crystal nucleated in an isolated window usually forms a hexagonal pyramid. After nucleation, hexagonal pyramids gradually grow in the height direction and the bottom side. The bottom spreads in a hexagonal shape and fills the window. Eventually GaN spreads beyond the mask. It still retains the hexagonal pyramid shape. As shown in FIG. 5, the crystal grows in contact with the crystal from the adjacent window. The size of the substrate crystal is determined by the thickness of the epitaxial growth layer. Since one wafer has a thickness of 70 μm to 1 mm, it is sufficient if the thickness is about that level. This is the state of FIG. Since the growth process as described above is taken, the growth surface is rough and rubbed. To be transparent, it must be polished.

[0029]

Further, the GaAs portion is removed by etching with aqua regia. The mask portion is removed by polishing. The state shown in FIG. This is a single GaN crystal. Transparent and independent. If only one wafer is to be produced, this is the end.

[0030]

Further, if it is desired to manufacture a plurality of wafers, this substrate is used as a seed crystal for further epitaxial growth. FIG. 7 illustrates this. FIG. 7 (1) shows a GaN substrate epitaxially grown thicker by HVPE on a GaN substrate. It becomes a cylinder-shaped GaN ingot. The thickness is 10 mm or more. A support member is fixed to the side surface, and the wafer is cut into wafers one by one with an inner peripheral slicer or the like. FIG. 7 (2) shows this. The as-cut wafer is polished to obtain a transparent and smooth GaN wafer as shown in FIG. In this case, As is not mixed into the GaN crystal.

[0031]

The HVPE method used for epitaxial growth in the present invention will be described with reference to FIG. A

[0032]

The

[0033]

In epitaxial growth, the raw material must be gas, but there is no gas containing Ga. Ga itself is a liquid at 30 ° C. or higher. The MOC method and the MOCVD method use an organic metal to form a gas. Although it is a gas, it contains carbon, so carbon is mixed as an impurity in the GaN crystal. In the HVPE method, Ga is heated to a liquid and reacted with HCl to form GaCl. It is carried as a gas by the dominant hydrogen gas. Since no organic metal is used, there is an advantage that carbon does not enter the crystal as an impurity.

[0034]

A GaN single crystal substrate made according to the present invention is non-doped but n-type. The carrier concentration is about 1 × 10 16 cm −3 . The present inventor has found that what gives n-type conductivity is oxygen contained in a trace amount in the source gas. By controlling the oxygen partial pressure in the HVPE furnace, the carrier concentration can be controlled in the range of 1 × 10 16 cm −3 to 1 × 10 20 cm −3 . By controlling the oxygen partial pressure, the electron mobility can be adjusted in the range of 80cm 2 / Vs~800cm 2 / Vs. The specific resistance can be controlled in the range of 1 × 10 −4 Ωcm to 1 × 10 Ωcm. The carrier concentration is preferably in the range of 5 × 10 17 cm −3 to 10 19 cm −3 , and the specific resistance is more preferably in the range of 5 × 10 −2 Ωcm or less.

[0035]

The GaN substrate thus produced has excellent characteristics. wide. It is a self-supporting membrane. It is transparent. It is a property such as being colorless. However, it is yellow, light brown, or dark gray depending on the growth conditions. The substrate for an optical device is required to have little light absorption. Therefore, it is required to be colorless and transparent. This is important as a GaN substrate. The transparency of the substrate is described by the Lambert-Beer rule and is given by

I = I 0 exp (−αx)

Here, I 0 is the intensity of the incident light, I is the intensity of the observation light, α is the absorption coefficient, and x is the thickness of the substrate. The smaller α is, the higher the light transmittance and the more transparent. The absorption coefficient of the GaN substrate obtained by the present invention is low over 400 to 600 nm, and the GaN substrate has high transparency to light of these wavelengths. The absorption coefficient was measured for the GaN substrate whose both surfaces were polished. According to the present invention, an absorption coefficient of 120 cm −1 or less can be easily obtained in this wavelength band. Furthermore, the thing with an absorption coefficient of 80 cm < -1 > or less was also producible. As an optical device substrate, the smaller the absorption coefficient, the better.

However, that is not enough. There are still more problems. What is it? It is a problem of strain and internal stress. If the internal stress is large, the warpage becomes severe and the wafer process such as photolithography is hindered.

[0036]

GaN is grown on the heated GaAs substrate and cooled to room temperature, and the composite is taken out from the apparatus. Since the coefficient of thermal expansion is different, the strain varies with decreasing temperature. The GaN / GaAs composite is bent as shown in FIG. Stress is generated in GaN. Stress in the opposite direction is also generated in GaAs. There are two types of stress. Thermal stress and intrinsic stress. Thermal stress is generated when there is a temperature change when two different materials having different thermal expansion coefficients are bonded together.

[0037]

If only the thermal stress is present, the thermal stress disappears when the GaAs substrate is removed. Therefore, GaN should be flat as shown in FIG. This is not the case with intrinsic stress. Even when the GaAs substrate is removed, there is still residual stress in the GaN. Therefore, GaN itself is distorted as shown in FIG. This warp appears due to the difference in stress between the front and back surfaces and the gradient of stress in the thickness direction regardless of GaAs.

[0038]

The reason why GaN could not be skillfully grown on a GaAs substrate in the 1970s is also due to the large intrinsic stress. The internal stress including thermal stress was too large, and GaN had a lot of defects and was peeled off. The device for reducing the intrinsic internal stress is actually the lateral growth method using the mask described above. A large number of isolated windows are formed as masks, from which a GaN buffer layer is grown and an epitaxial layer is further grown. We believe that the internal stress is caused by defects such as dislocations. Since they are separated from the dislocations, the portion grown on the mask has a reduced defect, thereby reducing the internal stress.

[0039]

That's fine, but some internal stress still remains. Therefore, the GaN substrate is warped. When warping is large, the wafer process is not affected. The warpage must be evaluated to determine the upper limit of allowable warpage.

[0040]

FIG. 12 shows the definition of the measurement method or expression method of warpage. A central ridge H is measured on a flat table on a wafer of constant diameter. For example, the center lift H is calculated in terms of a 2 inch diameter wafer. H is one measurement method and expression method.

[0041]

The warpage can be defined and expressed by the curvature ξ or the curvature radius R of the curvature of the wafer. It can be converted by R = D 2 / 8H or ξ = 8H / D 2 . D is the diameter of the wafer. In the case of a 2-inch wafer, D = 50 mm.

[0042]

Since warping or bending is a phenomenon that appears outside, it can be measured directly. Internal stress cannot be easily measured because it is an intrinsic potential.

[0043]

The internal stress when the disk bends with a curvature δ is [0044]

[Expression 1]

[0045]

Given by. σ is the internal stress, E is the rigidity, ν is the Poisson's ratio, b is the thickness of the substrate, d is the thickness of the thin film, I is the substrate diameter, and δ is the deflection (corresponds to H). When I = 50 mm, δ = H in the above definition. This is called Stoney's formula for calculating the internal stress of the thin film from the deflection. Since it is only a thin film (since it is a GaN single layer), d = b,

[0046]

[Expression 2]

[0047]

From this equation, σ was calculated from the deflection δ. The relationship between warpage, radius of curvature and internal stress is as follows. When the substrate thickness is constant, the greater the internal stress, the greater the warp and the smaller the radius of curvature. When the internal stress is constant, the warpage decreases and the radius of curvature increases as the substrate thickness increases. Regarding the GaN substrate by the present inventors, considering the ease of device process on the substrate and the strength of the substrate, the allowable range of warpage, radius of curvature, and internal stress was studied.

[0048]

The appropriate value varies depending on the thickness of the wafer, but generally speaking,

1. Curvature radius R 600 mm or more (curvature is 1.67 × 10 −3 mm −1 or less)

2. Warpage H (with 50 mm diameter) 0.55 mm or less

That is, the conditions imposed on the wafer by the present inventors are R ≧ 600 mm, H ≦ 0.55 mm, and σ ≦ 7 MPa. Furthermore, the internal stress is more preferably 3 MPa. More preferably, the radius of curvature is 750 mm or more.

[0050]

In the present invention, in addition to a method of manufacturing a single GaN substrate, a method of manufacturing a single crystal ingot by using a GaN substrate as a seed crystal and epitaxially growing GaN thickly thereon is also employed. In that case, the thickness is 10 mm or more, and several tens of wafers are cut out. Warpage is small because the ingot is thick. Slicing with high accuracy because there is little warping. Lower dislocations are progressing because of the large thickness. Wafers sliced and cut out also have low dislocations. Therefore, there is little warp.

[0051]

【Example】

[Example 1 (Preparation of one GaN single crystal by HVPE lateral growth)]

A GaAs (111) A substrate was placed in the reaction vessel. The substrate size was a 30 mm diameter circular substrate. An Si 3 N 4 layer was formed to a thickness of 0.1 μm on a GaAs substrate with an atmospheric pressure (atmospheric pressure) CVD apparatus. A window having a regular distribution was opened by photolithography. Three types of windows were used. There are three types: a staggered dot window shown in FIG. 3, a <11-2> stripe window, and a <1-10> stripe window.

1. Staggered dot window: As shown in FIGS. 3 to 5, adjacent windows arranged on a straight line parallel to GaAs <11-2> are shifted by a half pitch. d = 3.5 μm, L = 4 μm.

2. <11-2> Striped window A mask of a long window (striped) parallel to the <11-2> direction. The stripe width is 2 μm, the interval is 2 μm, and the pitch is 4 μm.

3. <1-10> Striped window A mask of a long window (striped) parallel to the <11-2> direction. The stripe width is 2 μm and the interval is 6 μm. The pitch is 8 μm.

[0052]

A GaN buffer layer and an epitaxial layer are grown using Si 3 N 4 having such a window as a mask.

(1) Formation of GaN buffer layer A GaAs substrate covered with a mask having a periodic window was placed in an HVPE apparatus. The HVPE apparatus was evacuated to heat the GaAs substrate to about 500 ° C. The quartz Ga reservoir is heated to 850 ° C. or higher to form a Ga melt. A mixed gas of hydrogen gas H 2 and hydrogen chloride gas HCl was introduced into the Ga reservoir from the source gas inlet, and gallium chloride GaCl was synthesized. A mixed gas of hydrogen H 2 and ammonia NH 3 is introduced from another source gas inlet, and a reaction of GaCl + NH 3 → GaN is caused in the vicinity of the substrate heated to 500 ° C. to deposit GaN on the GaAs substrate. As a result, a GaN buffer layer of about 70 nm is formed on the GaAs substrate. Si 3 N 4 has a GaN growth suppressing action, and GaN is not deposited on the Si 3 N 4 mask. The buffer layer (70 nm) is thinner than the mask (100 nm). Therefore, a GaN buffer layer is formed only on the GaAs portion of the window.

[0053]

(2) Formation of GaN epitaxial layer The introduction of HCl was stopped. The substrate temperature was increased from 500 ° C. to about 1000 ° C. HCl is again introduced into the Ga reservoir. As in the previous step, gallium chloride GaCl is synthesized by the reaction of Ga and HCl. Since hydrogen gas flows as a carrier, GaCl flows downward. Ammonia NH 3 and GaCl react in the vicinity of the heated substrate to form GaN. This grows epitaxially on the buffer layer in the window. When the mask thickness (100 nm) is exceeded, the GaN crystal spreads in a regular hexagonal shape on the mask. However, the GaN crystal is a hexagonal pyramid until the entire mask is covered with GaN. 4 and 5 schematically show the state of the bottom surface of the hexagonal pyramid. Since the window is located at the apex position of the equilateral triangle, the GaN spreading in a regular hexagonal shape touches the crystal spreading from the adjacent window exactly. Since the growth rate is equal, the regular hexagonal pyramid crystals are in good contact. When the GaN crystal layer completely covers the upper surface of the mask, GaN is deposited upwards. The growth rate is 50 μm / H. An epitaxial layer having a thickness of about 100 μm was grown. As described above, nucleation is independently generated from a myriad of small windows and crystal growth is performed (lateral growth), so that the internal stress in GaN can be greatly reduced. The surface was frosted glass.

[0054]

(3) Removal of GaAs substrate Next, the sample was placed in an etching apparatus. Etched with aqua regia for about 10 hours. The GaAs substrate was completely removed. It became a crystal only of GaN. Both surfaces were polished to obtain a GaN single crystal substrate. This was a self-supporting membrane. Three samples were grown on GaN under almost the same conditions except that the window size and window pitch L of the mask and the distance d between adjacent rows were changed.

[0055]

[Table 1]

[0056]

Although it is non-doped, it is an n-type electron conduction type. Considering the maintenance of crystallinity, the lower carrier concentration is better and the higher electron mobility is better. However, a higher specific resistance is better. These electrical characteristics vary depending on the growth conditions. The stripe mask is incomplete in terms of reducing internal stress. These samples are transparent light brown. Absorption coefficient at a wavelength 400nm~600nm was 40cm -1 ~80cm -1. When the content of As was examined, it was 9 × 10 16 cm −3 .

[0057]

[Example 2 (HVPE laterally grown GaN seed crystal, HVPE method GaN thickening)]

A 2-inch diameter GaAs (111) A surface was used as the substrate. An SiO 2 insulating film was formed thereon. A window as shown in FIG. 3 was provided by photolithography.

(1) Formation of GaN buffer layer

A GaAs substrate having a mask was placed in an HVPE apparatus. The

(2) Formation of epitaxial layer Subsequently, the substrate temperature was raised to 1000 ° C. A GaN epitaxial layer of 80 μm was formed using the same source gas.

(3) Removal of GaAs The GaN / GaAs substrate was taken out of the HVPE apparatus. It was confirmed that a GaN continuous film was formed in a mirror shape. The GaAs substrate was removed by etching in aqua regia.

[0059]

(4) Thickening of GaN This was thoroughly cleaned. The state shown in FIG. What was only GaN was set again in the HVPE apparatus. The substrate temperature was 1020 ° C., and GaN was thickened by the HVPE method to obtain a GaN ingot. This is the state shown in FIG. This ingot had a shape in which the central portion was slightly depressed. The ingot had a minimum height of about 20 mm and an outer diameter of 55 mm.

[0060]

(5) Wafer cutting with a slicer An ingot was cut in a direction perpendicular to the axial direction with a circumferential blade slicer. As shown in FIG. Twenty GaN single crystal substrates having an outer diameter of about 50 mm and a thickness of 350 μm were obtained. When GaN was analyzed, both As and carbon were at the background level. It can be seen that arsenic (As) and carbon are hardly contained in GaN.

[0061]

(6) Polishing Further lapping polishing and final polishing were performed. This is a transparent wafer as shown in FIG. The substrate was not warped because it was machined.

[0062]

(7) Measurement of electrical characteristics The electrical characteristics of the wafer taken from the upper end of the ingot (at the end of growth) were measured. The n-type carrier concentration was 5 × 10 18 cm −3 . The electron mobility was 200 cm 2 / Vs. The specific resistance was 0.017 Ωcm.

[0063]

The electrical characteristics of the wafer taken from the lower end of the ingot (early growth portion) were as follows. The n-type carrier concentration was 10 18 cm −3 and the electron mobility was 150 cm 2 / Vs. The specific resistance was 0.01 Ωcm. This is the electrical property of the extremes. The middle part will be an intermediate value.

[0064]

(8) Measurement of light absorption These wafers were transparent and dark gray or colorless. Absorption coefficient at a wavelength 400nm~600nm was 20cm -1 ~40cm -1.

(9) Production of LED Since a GaN substrate was formed, an LED having InGaN as a light emitting layer was produced thereon. Compared with the conventional sapphire substrate, the light emission luminance is improved about 5 times. The reason why the luminance is improved is due to a decrease in dislocations. This is because many threading dislocations exist in the active layer in the conventional sapphire substrate LED, but the threading dislocations of the present invention on the GaN substrate greatly decrease.

[0065]

[Example 3 (MOC laterally grown GaN seed crystal, HVPEGaN thickened)]

The GaAs (111) B surface was used as the substrate. SiO 2 was attached to the substrate, and stripe windows extending in the [1-10] direction were formed by photolithography.

[0066]

(1) Formation of GaN buffer layer A GaN buffer layer having a thickness of 90 nm was formed on a substrate at a low temperature of about 490 ° C. by metal organic chloride vapor phase epitaxy (MOC method).

[0067]

(2) Formation of GaN epitaxial layer In the same apparatus, the substrate temperature was raised to about 970 ° C., and the GaN epitaxial layer was formed to a thickness of 25 μm.

(3) Removal of GaAs substrate A GaN / GaAs sample was taken out from the MOC apparatus. A mirror-finished GaN single crystal was growing. The direction of the stripe mask was the [11-20] direction of GaN. That is, the [11-20] direction of GaN grows in the [1-10] direction of GaAs. The GaAs substrate was dissolved and removed with aqua regia.

[0068]

(4) GaN thickening growth GaN having a thickness of 25 μm was set as a seed crystal in an HVPE apparatus. GaN was thickly epitaxially grown by heating at 1000 ° C. by the HVPE method. A GaN ingot having a cylindrical shape and a minimum height of about 3 cm was grown.

[0069]

(5) Wafer cut by inner peripheral edge slicer An ingot was cut to a thickness of 400 μm in the direction perpendicular to the axis by an inner peripheral edge slicer. 25 as-cut wafers could be cut out.

[0070]

(6) The lapped wafer was lapped and finished. A GaN single crystal wafer as a product was obtained.

(7) Measurement of electrical characteristics The electrical characteristics of the wafer were measured. It was n-type and had an electron mobility of 250 cm 2 / Vs. The specific resistance was 0.05 Ωcm.

[0071]

In this embodiment, a GaN single crystal is grown thick using GaN itself as a seed crystal. Since thick single crystal GaN is grown and cut with a slicer, as many as 25 substrates can be fabricated at once. The manufacturing cost was reduced to 64% as compared with the case of growing from one piece of GaAs. The manufacturing cost of the substrate can be reduced. The production time per sheet including quality control could be greatly reduced. When GaN was analyzed, both arsenic (As) and carbon (C) were at the background level.

[0072]

As the mask window, a mask having a window at the apex of the equilateral triangle is best. However, it may have a striped window. There is a certain effect of reducing internal stress. Lateral growth on the mask reduces the internal stress by reducing defects in the crystal and reduces the contact area between GaAs and GaN, thereby relaxing the internal stress. Therefore, it is possible to suppress the occurrence of warpage despite the large temperature change.

[0073]

[Example 4 (Relationship between total flow rate and surface morphology / internal stress)]

Using a [1-100] stripe mask, a [11-2] stripe mask, and a dot mask, a GaN wafer was fabricated by the HVPE method. The source gases are H 2 + NH 3 and H 2 + HCl. Increasing the total flow of source gas improves the surface morphology. However, the internal stress tended to increase.

[0074]

[Table 2]

[0075]

Of these, six (i), (b), (d), (d), (e), (d), (c), and (c) are group A, and (c) are five groups (c).

(A) The Ga partial pressure is 1 kPa (10 −2 atm). GaN was grown on the buffer layer / mask at 970 ° C. for 1 hour, and GaN was further grown at 1030 ° C. for 3 hours. Epitaxial growth for a total of 4 hours. The result is shown by white circles in FIG. There are 6 samples. These have a flat surface and good morphology. However, the internal stress is large. Some samples have cracks. In FIG. 13, the horizontal axis represents the film thickness (μm). The film thickness is distributed between 5 μm and 120 μm. The vertical axis represents internal stress (GPa). The sample of ○ has an internal stress of 2 MPa to 40 MPa. Most exhibit internal stresses greater than 10 MPa. However, the internal stress is preferably 7 MPa or less (7 × 10 −3 GPa).

(B) The Ga partial pressure is 2 kPa. GaN was epitaxially grown on the buffer layer / mask at 970 ° C. for 6 hours. The number of samples is ten. The same is shown in FIG. The film thickness is distributed between 70 μm and 300 μm. The surface of the GaN sample is rough. Rmax is about 20 μm. The GaN substrate size is 20 mm × 20 mm. Although the surface condition is poor, the internal stress is small. The internal stress is 1 MPa to 10 MPa as indicated by black circles in FIG. Since the target is 7 MPa or less, this can be satisfied. However, the film thickness varies widely (70 μm to 300 μm) even under the same conditions. The curvature radius R of the warp is R = 780 mm to 1500 mm.

[0076]

[Example 5 (Relationship of radius of curvature)]

The relationship between the film thickness and the radius of curvature was examined for the six samples (A) and the five samples (B) as in the previous example. Warpage was evaluated by the stylus method. FIG. 14 shows the result. The horizontal axis is the film thickness (μm). The vertical axis is the radius of curvature. The radius of curvature is preferably 600 mm or more.

(A) Sample A grown at 970 ° C. for 1 hour + 1030 ° C. for 3 hours has a thin film thickness and a flat surface but a large warp. The curvature radius is 200 mm or less. A desirable range of the radius of curvature is 600 mm or more. All six samples do not reach the target.

(B) Sample B grown at 970 ° C. for 6 hours has a large film thickness and a roughened surface, but the internal stress is small and the warpage is small. All five B samples exceed the desirable range of 600 mm. In growth without a mask, the radius of curvature is extremely small and the warp is large. This is why the 1970s GaAs substrate attempts failed.

[0077]

[Example 6 (polishing)]

Sample A failed to polish. Among samples B, a sample having a film thickness of 150 μm, an internal stress of 4 MPa, a curvature radius of 1030 mm, and a Rmax of 20 μm was polished. The film thickness was reduced to 80 μm by polishing. The radius of curvature is reduced to 650 mm after polishing. The surface roughness was reduced to Rmax 7.2 nm and

[Example 7 (Anisotropy of internal stress in wafer)]

The internal stress when GaN was grown using a stripe mask and when GaN was grown using a dot mask were compared. FIG. 15 is a graph showing the relationship between the mask and the internal stress.

A stripe mask extending in the <1-10> direction was produced on a GaAs wafer and GaN having a thickness of 120 μm was grown (averaged because the thickness of the film varies)

Using the same dot mask as in Example 1 and growing GaN with an average film thickness of 160 μm,

It was used.

All of the growth conditions are Ga

[0078]

【The invention's effect】

The present invention provides a large GaN single crystal wafer. Due to the lateral growth method, there are few defects such as dislocations in the GaN crystal. Since GaN is thickened by a method that does not use carbon, the wafer becomes highly transparent. Lateral growth reduces internal stress and reduces warping. An existing wafer process such as photolithography can be used with little warping. This GaN single crystal wafer can be used as a substrate for a GaN light emitting device. Since the thin film portion and the substrate are the same, there is no warping. Small internal stress. Therefore, the dislocation density is also reduced. Luminous efficiency increases. The lifetime of GaN LED and GaN LD is extended.

[Brief description of the drawings]

FIG. 1 is a graph showing the difference in thermal expansion coefficient and lattice constant between a substrate material for growing a GaN crystal and GaN, in x and y coordinates.

FIG. 2 is a graph showing that the lattice constant changes smoothly as the GaN film thickness changes when GaN is epitaxially grown on a sapphire substrate.

FIG. 3 is a plan view of a staggered dotted window mask fixed on a GaAs (111) A surface.

FIG. 4 is a plan view showing a state in which a GaN buffer layer is epitaxially grown on a portion exposed from a mask window.

FIG. 5 is a plan view showing a state when GaN is further epitaxially grown on a mask and a buffer layer and crystals from adjacent windows meet each other.

FIG. 6 is a process diagram showing a process of growing a GaN buffer layer and a GaN epitaxial layer by placing a mask on the GaAs substrate and etching away the GaAs substrate. (1) is a diagram of a process in which a mask is formed on a GaAs (111) substrate. (2) is a diagram of a process in which a buffer layer is grown on a portion not covered with a mask. (3) is a diagram of a process in which a GaN epitaxial layer is grown on a buffer layer and a mask. (4) is a diagram showing a state in which the GaAs substrate is removed to form a free-standing film of GaN.

FIG. 7 is a diagram showing a process of further growing GaN thick on a GaN substrate to form a GaN ingot and cutting it into a wafer. (1) is a diagram of a GaN ingot thickened on a GaN substrate. (2) is a figure which shows the condition which is cutting | disconnecting an ingot into an as-cut wafer with an internal peripheral slicer. (3) is a view of a cut wafer.

FIG. 8 is a schematic sectional view of an HVPE apparatus.

FIG. 9 is a cross-sectional view showing a state in which a composite substrate obtained by growing GaN on a GaAs substrate is warped due to thermal stress.

FIG. 10 is a cross-sectional view showing that GaN after removing GaAs becomes flat if the internal stress is zero.

FIG. 11 is a cross-sectional view showing that if an internal stress is present in GaN itself, strain remains even after GaAs is removed.

FIG. 12 is a view showing the definition of warpage of a GaN wafer. Warpage is expressed by a bulge H at the center of a 50 mm diameter wafer.

FIGS. 13A and 13B are graphs showing distributions of measured values of film thickness and internal stress for a group of (A) 1800 sccm to 900 sccm and a group of (B) 900 sccm. Black circles are rough and are group B. White circles are surface smooth and group A.

FIG. 14 is a diagram showing the distribution of film thickness and radius of curvature for the same group A sample (30 sheets) and group B sample (9 sheets). Black circles are group B and white circles are group A.

FIG. 15 is a graph showing the result of measuring the anisotropy of internal stress when using a stripe mask and a dot mask.

[Explanation of symbols]

DESCRIPTION OF

Claims (8)

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17127698A JP3788037B2 (en) | 1998-06-18 | 1998-06-18 | GaN single crystal substrate |

| TW088109629A TW417315B (en) | 1998-06-18 | 1999-06-09 | GaN single crystal substrate and its manufacture method of the same |

| US09/333,879 US6413627B1 (en) | 1998-06-18 | 1999-06-15 | GaN single crystal substrate and method of producing same |

| EP99111739A EP0966047B1 (en) | 1998-06-18 | 1999-06-17 | GaN single crystal substrate and method of producing same |

| DE69943012T DE69943012D1 (en) | 1998-06-18 | 1999-06-17 | GaN single crystal substrate and manufacturing method |

| KR1019990023075A KR100348175B1 (en) | 1998-06-18 | 1999-06-18 | GaN single-crystal substrate and the method of manufacturing the same |

| CNB991086449A CN1196176C (en) | 1998-06-18 | 1999-06-18 | GaN monocrystal substrate and making method thereof |

| HK00103240A HK1024099A1 (en) | 1998-06-18 | 2000-05-31 | Gan single crystal substrate. |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17127698A JP3788037B2 (en) | 1998-06-18 | 1998-06-18 | GaN single crystal substrate |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006034698A Division JP4089730B2 (en) | 2006-02-13 | 2006-02-13 | Manufacturing method of GaN single crystal substrate |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000012900A JP2000012900A (en) | 2000-01-14 |

| JP2000012900A5 JP2000012900A5 (en) | 2006-03-23 |

| JP3788037B2 true JP3788037B2 (en) | 2006-06-21 |

Family

ID=15920334

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP17127698A Expired - Lifetime JP3788037B2 (en) | 1998-06-18 | 1998-06-18 | GaN single crystal substrate |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3788037B2 (en) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1916321A1 (en) | 2006-10-02 | 2008-04-30 | Ricoh Company, Ltd. | Crystal producing apparatus, crystal producing method, substrate producing method, gallium nitride crystal, and gallium nitride substrate |

| EP2055811A2 (en) | 2007-10-24 | 2009-05-06 | Sumitomo Electric Industries, Ltd. | Nitride semiconductor substrate and method of manufacturing the same and field-effect transistor |

| US7718002B2 (en) | 2007-03-07 | 2010-05-18 | Ricoh Company, Ltd. | Crystal manufacturing apparatus |

| US8110484B1 (en) | 2010-11-19 | 2012-02-07 | Sumitomo Electric Industries, Ltd. | Conductive nitride semiconductor substrate and method for producing the same |

| US8129082B2 (en) | 2007-03-06 | 2012-03-06 | Ricoh Company, Ltd. | Electrophotographic photoreceptor, image forming method using electrophotographic photoreceptor, image forming apparatus, and process cartridge for image forming apparatus |

Families Citing this family (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3283802B2 (en) * | 1997-09-29 | 2002-05-20 | 日本電気株式会社 | Semiconductor layer using selective growth method and method for growing the same, nitride semiconductor layer using selective growth method and method for growing the same, nitride semiconductor light emitting device and method for manufacturing the same |

| US6596079B1 (en) * | 2000-03-13 | 2003-07-22 | Advanced Technology Materials, Inc. | III-V nitride substrate boule and method of making and using the same |

| JP4623799B2 (en) * | 2000-06-23 | 2011-02-02 | ローム株式会社 | Semiconductor light emitting device manufacturing method and semiconductor laser |

| US6562644B2 (en) | 2000-08-08 | 2003-05-13 | Matsushita Electric Industrial Co., Ltd. | Semiconductor substrate, method of manufacturing the semiconductor substrate, semiconductor device and pattern forming method |

| US6780239B2 (en) | 2000-10-19 | 2004-08-24 | Ricoh Company, Ltd. | Crystal growth method, crystal growth apparatus, group-III nitride crystal and group-III nitride semiconductor device |

| JP3679720B2 (en) * | 2001-02-27 | 2005-08-03 | 三洋電機株式会社 | Nitride semiconductor device and method for forming nitride semiconductor |

| JP3790677B2 (en) * | 2001-03-19 | 2006-06-28 | 株式会社東芝 | Semiconductor light emitting device and manufacturing method thereof |

| EP1244139A2 (en) | 2001-03-23 | 2002-09-25 | Matsushita Electric Industrial Co., Ltd. | Manufacturing method of semiconductor film |

| JP2002284600A (en) | 2001-03-26 | 2002-10-03 | Hitachi Cable Ltd | Method for manufacturing gallium nitride crystal substrate and the same |

| JP3631724B2 (en) | 2001-03-27 | 2005-03-23 | 日本電気株式会社 | Group III nitride semiconductor substrate and manufacturing method thereof |

| US8633093B2 (en) | 2001-04-12 | 2014-01-21 | Sumitomo Electric Industries Ltd. | Oxygen doping method to gallium nitride single crystal substrate |

| US6773504B2 (en) | 2001-04-12 | 2004-08-10 | Sumitomo Electric Industries, Ltd. | Oxygen doping method to gallium nitride single crystal substrate and oxygen-doped N-type gallium nitride freestanding single crystal substrate |

| US7001457B2 (en) | 2001-05-01 | 2006-02-21 | Ricoh Company, Ltd. | Crystal growth method, crystal growth apparatus, group-III nitride crystal and group-III nitride semiconductor device |

| JP3801125B2 (en) * | 2001-10-09 | 2006-07-26 | 住友電気工業株式会社 | Single crystal gallium nitride substrate, method for crystal growth of single crystal gallium nitride, and method for manufacturing single crystal gallium nitride substrate |

| US7473315B2 (en) | 2001-10-09 | 2009-01-06 | Sumitomo Electric Industries, Ltd. | AlxInyGa1-x-yN mixture crystal substrate, method of growing AlxInyGa1-x-yN mixture crystal substrate and method of producing AlxInyGa1-x-yN mixture crystal substrate |

| US6949140B2 (en) | 2001-12-05 | 2005-09-27 | Ricoh Company, Ltd. | Crystal growth method, crystal growth apparatus, group-III nitride crystal and group-III nitride semiconductor device |

| JP4932121B2 (en) | 2002-03-26 | 2012-05-16 | 日本電気株式会社 | Method for manufacturing group III-V nitride semiconductor substrate |

| JP3997827B2 (en) | 2002-04-30 | 2007-10-24 | 住友電気工業株式会社 | Gallium nitride growth substrate, gallium nitride growth substrate manufacturing method, and gallium nitride substrate manufacturing method |

| JP4117156B2 (en) | 2002-07-02 | 2008-07-16 | 日本電気株式会社 | Method for manufacturing group III nitride semiconductor substrate |

| AU2003259125A1 (en) * | 2002-12-16 | 2004-07-29 | The Regents Of The University Of California | Growth of reduced dislocation density non-polar gallium nitride by hydride vapor phase epitaxy |

| US7427555B2 (en) | 2002-12-16 | 2008-09-23 | The Regents Of The University Of California | Growth of planar, non-polar gallium nitride by hydride vapor phase epitaxy |