JP3764573B2 - 光モジュール - Google Patents

光モジュール Download PDFInfo

- Publication number

- JP3764573B2 JP3764573B2 JP33069197A JP33069197A JP3764573B2 JP 3764573 B2 JP3764573 B2 JP 3764573B2 JP 33069197 A JP33069197 A JP 33069197A JP 33069197 A JP33069197 A JP 33069197A JP 3764573 B2 JP3764573 B2 JP 3764573B2

- Authority

- JP

- Japan

- Prior art keywords

- light receiving

- subcarrier

- receiving element

- optical

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Led Device Packages (AREA)

- Light Receiving Elements (AREA)

- Optical Couplings Of Light Guides (AREA)

Description

【発明の属する技術分野】

本発明は受光する光素子を基板へ実装した光モジュールに関する。

【0002】

【従来の技術】

近年、光通信を各家庭やオフィスにまで適用することが急速に進められている。このような光通信の広範囲な適用発展は情報化社会実現の鍵を握ることになる。そして、光通信技術の中心である光素子搭載モジュールを高精度に且つ歩留まりよく安価に生産する技術が光通信の発展のためには不可欠となる。

【0003】

従来、光ファイバに対し平面で光結合を行なうPD(フォトダイオード)などの光素子を高精度に位置合わせした光モジュールが知られおり、その構成を図1に示す。すなわち、V溝12が形成された基板11上へ光ファイバ13が載置固定されており、基板11上に固定された板状のサブキャリア14に受光素子である光素子15が実装され、光素子15の受光面は光ファイバ13の端面13a側へ配向していた。

【0004】

【発明が解決しようとする課題】

しかしながら、上記の光モジュールJ1では、サブキャリア14の固定位置もしくは光ファイバ13の固定位置は、目視によって距離を認識し決定されていたため、光素子15と光ファイバ13の距離を精密に且つ再現性良く制御することが困難であった。

【0005】

また、サブキャリア14上へ光素子15、特に、PDチップの受光面側に存在するワイヤボンディング用のパッドが数十μm径程度でごく小さいため、ワイヤボンディングが非常に困難であった。

【0006】

そこで、本発明では、光素子と光ファイバとの距離を精密に且つ再現性よく設定することができ、しかも光素子の実装を極めて簡便に行なうことが可能な光モジュールを提供することを目的とする。

【0007】

【課題を解決するための手段】

上記目的を達成するために、本発明の光モジュールは、V溝と、電極パッドとが設けられた基板と、

両主面に端部を有する導光路と、一主面にキャリア電極パッドと、底面に底面電極と、該キャリア電極パッドと該底面電極とを結ぶ配線パターンとを有するとともに、該底面電極を前記基板の前記電極パッドにバンプ接合した板状体と、

受光面側に表面電極を有するとともに、該表面電極を前記板状体の前記キャリア電極パッドにフェイスダウンでバンプ接合した受光素子と、

前記基板の前記V溝に載置され、一端が前記板状体の他主面側に当接して、前記受光素子の前記受光面と光結合する光ファイバとを備えたことを特徴とする。

【0008】

また、前記板状体の前記導光路は、前記受光素子の前記受光面とほぼ同じ、もしくは前記受光面よりも小さい貫通孔によって構成されたことを特徴とする。

【0009】

また、前記板状体の前記配線パターンは、上面にも配線され、該上面に前記受光素子を駆動するプリアンプのICチップが搭載されていることを特徴とする。

【0010】

また、板状体の両主面が非平行であることを特徴とする。

【0011】

なお従来、面受光型の受光素子は結合面の反対側をサブキャリアへ固定していたが、本発明では、受光部分に例えば貫通孔を設けたサブキャリア(板状体)上へ受光面側を固定することを特徴としている。

【0012】

また、板状体には受光素子を固定した際に電気配線をするための配線パターンが施してあり、受光素子の受光面側に有る電極パッドと電気的に接続がとられる。この電気的接続は板状体へ受光素子を搭載する場合に、例えばはんだバンプ等を用いたフリップチップボンディングの手法にて行なわれ、キャリア実装と電気接続を同時に行なうことが可能になる。

【0013】

このように板状体に配線パターンが施されているため、基板上へはんだ固定することによって基板上の配線パターンと電気的接触が得られ、受光素子の実装後のワイヤリングなどの必要が無くなるメリットがあり、光モジュールの組み立てを大いに簡素化する効果がある。

【0014】

さらに、板状体に光ファイバを突き当てることによって光ファイバと受光素子の受発光面との距離を正確に決めることができるため、正確かつ再現性の良い実装が可能となる。

【0015】

【発明の実施の形態】

以下に、本発明の実施の形態について図面に基づき詳細に述べる。なお、ここでは主に面受光型の光素子として窒化ガリウムやアモルファスシリコン等を用いたフォトダイオード(以下、PDという)を例にとり説明する。

【0016】

図2に本発明の受光素子搭載サブキャリアS1の分解斜視図を示す。この図に示すように、板状体であるサブキャリア21には、その両主面に端部を有する導光路である貫通孔22が形成されている。この貫通孔22の開口部は実装すべきPDチップ27の受光部27cとほぼ同程度としている。また、サブキャリア21の一主面側には、PDチップ27の電極パッド27aと相応する位置へ配線23が設けられている。

【0017】

なお、サブキャリア21を構成する材料としては、セラミックモールド、積層セラミック配線基板、プラスチック、ガラス等が使用可能であるが、特に限定されるものではない。また、サブキャリア21に設けられた導光路は貫通孔である必要はなく、受光面を遮らないようなものであれば問題なく本発明のサブキャリアとして使用可能である。また、配線方法も印刷や積層焼成(積層セラミック基板)など方法は問わない。

【0018】

サブキャリア21の一主面にはPDチップ27の裏面電極27bとワイヤ23とを接続するための配線パターン24も設けられている。その際、サブキャリア21上の配線23,24はサブキャリア21の底面にまで引き回されている。PDチップ27の電極パッド27aとサブキャリア21上の配線23とをはんだバンプを用いてフェイスダウンでフリップチップ実装する。そして、このフリップチップ実装の後、PDチップ27の裏面電極27bとサブキャリア21上の配線24をワイヤボンディングによって接続する。

【0019】

このようにして、図3に示すようにPDチップ27を実装したサブキャリア21の他主面側は、V溝32上に載置された光導波路体である光ファイバ13の一端面と当接され、底面部をシリコン等から成る基板31に形成された凹部34上に固定されて、受光素子実装基板に光ファイバ13が配設されて光モジュールM1が完成する。ここで、サブキャリア21の底面部は基板31の凹部34上に半田等の適当な接着部材により固定されている。ここで、光ファイバ13を除く構成を受光素子実装基板とする。

【0020】

以上のように、本発明の受光素子搭載サブキャリアでは、受光素子の受光面(光機能面)側に貫通孔が開けられたサブキャリアを有しているため、受光素子の受光面と光ファイバの距離とを光ファイバの突き当てによって精密に制御することが可能となる。また、サブキャリアに受光面を遮らないように受光素子がフェイスダウンで実装されていることによって、サブキャリアへの突き当てが可能となる。また、サブキャリアに配線パターンを施し、サブキャリアの基板上への実装をフリップチップボンディングの技術が使用できるためワイヤボンディングの手間が省ける。また、サブキャリアの貫通孔の大きさを受光素子の受光面とほぼ同じ、もしくは、受光面より小さくすることによって、受光素子の受光面外への光結合を押さえることも可能となり、受光素子の性能を良好なまま使用することが可能となる。また、貫通孔の内壁を暗色にしたり粗面状にするなどして、PDチップからの反射光が光ファイバへ戻らないようにすることができる。また、この貫通孔に透明体で埋めるようにしてもよく、これによればサブキャリア上で局所的な封止が可能となる。

【0021】

次に本発明の他の実施形態について詳細に説明する。

〔変形例1〕図4(a)は、本発明のサブキャリアの一変形例を示す斜視図である。(b)は受光素子の斜視図である。サブキャリア41には搭載するPDチップ47の受光面と同一もしくは受光面より小さい面積の貫通孔42が設けられている。また、PDチップ47の表面電極48と相応するサブキャリア41の一主面49にはキャリア電極パッド43が設けられており、キャリア電極パッド43はサブキャリア41の底面までパターニングされている。また、サブキャリア41のチップ搭載面はPDチップ47の全体の面より若干大きく設計され、PDチップ47の面しないサブキャリア41の一部にはPDチップ47の裏面電極からワイヤボンドするための電極パッド44がキャリア電極パッド43と同様にキャリア底面までパターニングされている。

【0022】

上記サブキャリア41にPDチップ47をフェイスダウンでパンプ接合で一体化し、PDチップ47の裏面電極とサブキャリア41の電極パッド44をワイヤボンドにて接続する。このように作製したサブキャリア41とPDチップ47のサブアセンブリは電極パッド43、44の底面電極を用いて、別に作製したプラットフォーム上の電極パッドとバンプ接合により電気的接続と固定を行なう。また、サブキャリア41の厚み45はPDチップ47に結合する光ファイバとの光軸方向のトレランスから決定される値に設計されており、ファイバ端面をキャリア面46に突き当てることによって正確に位置決めされる。

【0023】

このような構成にすることにより、PDチップ47と光ファイバ端面との距離を正確に位置決めすることが可能となる。また、プラットフォーム(図3では基板31)上へのサブアセンブリの電気的接続と固定が一括で行なうことが可能となり、工程が簡素化され量産性が向上する。また、プラットフォーム上への固定がはんだバンプであるため、プラットフォーム上の電極パターンとサブアセンブリのはんだセルフアライメントが可能であり、位置決め等の工程の省略が可能となる。

【0024】

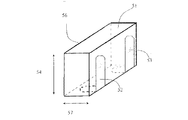

〔変形例2〕図5は本発明のサブキャリアの他の変形例を示す斜視図である。図5に示すように、搭載するPDチップの受光面の電極パッドに相応する部分に電極パッド52がサブキャリア51の底面まで伸びる配置で形成されている。また、電極パッド52のPD実装面と同一面にPD裏面電極からのワイヤボンディングのための電極53が電極パッド52と同様にサブキャリア底面まで形成されている。サブキャリア51はPDチップを実装した際に受光面を遮らない高さ54となっており、PDチップをサブキャリア面55へ搭載した後、搭載面とは反対の面56へ光ファイバを突き当てることによりサブキャリア厚57で制御された光軸方向へ光ファイバが位置合わせされる。このような構造にすることによって、変形例1で示したような貫通孔を形成する必要が無くなり、量産性に優れたサブキャリアを形成することが可能となる。

【0025】

〔変形例3〕図6は本発明のサブキャリアのさらに他の変形例を示す斜視図である。図6では変形例2で示したサブキャリア51のキャリア高さ54を若干高くし、しかも、受光面を遮らないように窪み62を形成することで、ワイヤボンド用の電極パッド63の面積を大きくすることができ、PDチップをサブキャリア61上へ実装する際に、ワイヤボンドが容易になり実装時の不良を低減することが可能となる。なお、図中64はPDチップの受光面側と接続される電極パッドである。

【0026】

〔変形例4〕図7(a)は本発明のサブキャリアのさらに他の変形例を示す斜視図であり、図7(b)はサブキャリア81に光ファイバ89,受光素子88を結合させた様子を説明する上面図である。変形例2で示したものと同様な電極パッド82、83が形成されたサブキャリア81に、PDチップ88の受光面を遮らないような貫通孔84が形成されている。PDチップ88の実装面85と光ファイバの突き当て面86は数度から数十度の角度が設けられている。このような設計にすることによって、PDチップ88の受光面での反射光が光ファイバ89へ戻ることが避けられ、光通信で非常に問題となる反射光を避けることができる。ここで、反射光を効果的に防止するために角度87は1°以上が望ましく、より好適には1°〜10°とする。

【0027】

〔変形例5〕図8(a)は本発明のサブキャリアのさらに他の変形例を示す斜視図であり、図8(b)はサブキャリア91に光ファイバ99,受光素子98を結合させた側面図である。変形例4で示したファイバ突き当て面とPD実装面の角度を図8に示したように上下方向へつけることも可能である。この際キャリア底面側を広くすることによって実装時のキャリアの安定性が増すというメリットが得られる。なお、図中94は導光路であり、92,93は電極パッドである。

【0028】

〔変形例6〕図9はサブキャリア101に光ファイバ109,受光素子108を光結合させた様子を示す横断面図である。

【0029】

このように、例えば変形例1で示したサブキャリアのファイバ突き当て面に光ファイバ径とほぼ同等もしくは若干大きめの径を持つ窪み102を形成する。この窪み102に光ファイバ109をはめ込むことによって光ファイバ109の光軸と垂直な方向の位置合わせを簡便に行なうことが可能となる。なお、図中104は導光路である。

【0030】

〔変形例7〕図10はサブキャリア112に光ファイバ111,受光素子118を光結合させた横断面図である。

【0031】

このように、変形例1で示したサブキャリアのファイバ実装側にファイバを保持するV溝111を形成する。光ファイバの実装の際、V溝111によりファイバを固定することでファイバ接続部分を安定に保持することが可能となる。なお、図中114は導光路である。

【0032】

〔変形例8〕図11は本発明のサブキャリアに受光素子を実装させた受光素子実装用サブキャリアS2の斜視図である。

【0033】

サブキャリア121に貫通孔122と電気接続用配線123が引き回されている。配線123はサブキャリア121の底面にまで引き回されておりプラットフォーム上で電気的接触が可能となっている。また、サブキャリア121の上面へも配線されており、PDチップ128の駆動に必要となるプリアンプなどのICチップ124を実装する。このような構造をとることによって光軸方向の位置決めだけでなくプリアンプの搭載をPDチップ128の近距離で行なうことができるため、高速度の通信に好適なPDチップやIC実装が可能となる。

【0034】

〔変形例9〕図12は本発明のサブキャリアの一変形例を示す斜視図である。サブキャリア131は少なくとも導光路となる領域がガラスなどの光(特に、光通信で使用される1.3〜1.5μmの光)を透過する材質で形成されており、変形例1と同様な電極132、133が底面まで形成されている。このようにすることで、実施例1で必要となる貫通孔が必要なくなりサブキャリアの量産性が向上する。なお138はPDチップである。この変形例の場合、PDとしてアモルファスSiシリコン等のpin型の薄膜光センサーを使用するとガラス基板等に容易に成膜することができ好適である。

【0035】

なお、本実施の形態において例えば配線をITO等の透明電極で構成してもよく、また基板、板状体、導光路、受光素子、光導波路体等の構成部材及びそれらの態様等において、本発明の要旨を逸脱しない範囲内で適宜変更し実施が可能である。

【0036】

【発明の効果】

以上説明の本発明によれば、光ファイバと面受光を行なう受光素子とを簡便にかつ最適な距離で精度よく再現性よく位置決めすることが可能な優れた光モジュールを提供することができる。

【図面の簡単な説明】

【図1】 従来の光モジュールを説明する全体概略斜視図である。

【図2】 本発明を構成する受光素子実装サブキャリアを説明する斜視図である。

【図3】 本発明の光モジュールを説明する全体概略斜視図である。

【図4】 (a)は本発明を構成するサブキャリアの斜視図であり、(b)は受光素子の斜視図である。

【図5】 本発明を構成するサブキャリアの一変形例を示す斜視図である。

【図6】 本発明を構成するサブキャリアの一変形例を示す斜視図である。

【図7】 (a)は本発明を構成するサブキャリアの一変形例を示す斜視図であり、(b)はサブキャリアに光ファイバ及び受光素子を結合させた様子を説明する上面図である。

【図8】 (a)は本発明を構成するサブキャリアの一変形例を示す斜視図であり、(b)はサブキャリアに光ファイバ及び受光素子を結合させた様子を説明する側面図である。

【図9】 本発明を構成するサブキャリアに光ファイバ及び受光素子を結合させた様子を説明する断面図である。

【図10】 本発明を構成するサブキャリアに光ファイバ及び受光素子を結合させた様子を説明する断面図である。

【図11】 本発明を構成するサブキャリアに受光素子を実装させた様子を説明する斜視図である。

【図12】 本発明を構成する受光素子実装サブキャリアを説明する斜視図である。

【符号の説明】

21,41,51,61,81,91,101,112,121,131:サブキャリア(板状体)

22,42,62,84,94,122:貫通孔(導光路)

27,47,88,98,108,118,128,138:PDチップ(受光素子)

31:基板

33,89,99,109,119:光ファイバ(光導波路体)

M1:光モジュール

Claims (4)

- V溝と、電極パッドとが設けられた基板と、

両主面に端部を有する導光路と、一主面にキャリア電極パッドと、底面に底面電極と、該キャリア電極パッドと該底面電極とを結ぶ配線パターンとを有するとともに、該底面電極を前記基板の前記電極パッドにバンプ接合した板状体と、

受光面側に表面電極を有するとともに、該表面電極を前記板状体の前記キャリア電極パッドにフェイスダウンでバンプ接合した受光素子と、

前記基板の前記V溝に載置され、一端が前記板状体の他主面側に当接して、前記受光素子の前記受光面と光結合する光ファイバとを備えたことを特徴とする光モジュール。 - 前記板状体の前記導光路は、前記受光素子の前記受光面とほぼ同じ、もしくは前記受光面よりも小さい貫通孔によって構成されたことを特徴とする請求項1に記載の光モジュール。

- 前記板状体の前記配線パターンは、上面にも配線され、該上面に前記受光素子を駆動するプリアンプのICチップが搭載されていることを特徴とする請求項1に記載の光モジュール。

- 前記板状体の両主面が非平行であることを特徴とする請求項1に記載の光モジュール。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33069197A JP3764573B2 (ja) | 1997-12-01 | 1997-12-01 | 光モジュール |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33069197A JP3764573B2 (ja) | 1997-12-01 | 1997-12-01 | 光モジュール |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11160585A JPH11160585A (ja) | 1999-06-18 |

| JP3764573B2 true JP3764573B2 (ja) | 2006-04-12 |

Family

ID=18235502

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33069197A Expired - Fee Related JP3764573B2 (ja) | 1997-12-01 | 1997-12-01 | 光モジュール |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3764573B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100814394B1 (ko) | 2005-12-28 | 2008-03-18 | 삼성전자주식회사 | 광 모듈 및 이를 이용한 광 연결 방법 |

| JP2012013916A (ja) * | 2010-06-30 | 2012-01-19 | Hitachi Cable Ltd | 光学部品および光モジュール |

| WO2017203786A1 (ja) * | 2016-05-23 | 2017-11-30 | オリンパス株式会社 | 光信号送信モジュール |

| WO2017203785A1 (ja) | 2016-05-23 | 2017-11-30 | オリンパス株式会社 | 光信号送信モジュール |

-

1997

- 1997-12-01 JP JP33069197A patent/JP3764573B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11160585A (ja) | 1999-06-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3795877B2 (ja) | 光半導体モジュール及びその製造方法 | |

| JP3731542B2 (ja) | 光モジュール及び光モジュールの実装方法 | |

| US8027553B2 (en) | Connected body and optical transceiver module | |

| US7438481B2 (en) | Optical semiconductor module and semiconductor device including the same | |

| EP1020747A1 (en) | Optical module | |

| US20060078248A1 (en) | Structure and method for mounting LSI package onto photoelectric wiring board, information processing apparatus, optical interface, and photoelectric wiring board | |

| JP4060023B2 (ja) | 光導波路送受信モジュール | |

| JP2004518156A (ja) | 透過性基材およびヒンジ付き光学アセンブリ | |

| KR19980030121A (ko) | 브이홈에 정렬된 렌즈를 가진 광모듈 및 그 제작방법 | |

| WO2005091036A1 (ja) | 光モジュールおよびその製造方法 | |

| JPH09138325A (ja) | 光ファイバ実装構造とその製造方法 | |

| JP2001100062A (ja) | 光通信装置 | |

| JP2002090586A (ja) | 光・電子回路モジュール及びその製造方法 | |

| JP2000501239A (ja) | チップ組立ての方法とデバイス | |

| KR100211985B1 (ko) | 하이브리드 광집적회로용 마이크로 거울, 그의 제조방법, 마이크로 거울-광검출기 어셈블리 및 광수신용 하이브리드 광집적회로 어셈블리 | |

| US6693304B2 (en) | Laminated lead frame, and optical communication module and method of manufacturing the same | |

| JP3764573B2 (ja) | 光モジュール | |

| JP3042453B2 (ja) | 受光モジュール | |

| JP2006047682A (ja) | 基板および光素子相互接続用基板 | |

| JPH09186348A (ja) | 半導体モジュール | |

| JP2001201670A (ja) | 光モジュール | |

| JP2930178B2 (ja) | 導波路型光デバイスの受光構造 | |

| JP2527054B2 (ja) | 光モジュ―ル用サブマウント及びその製造方法 | |

| JPH04241477A (ja) | 半導体デバイス用サブマウントおよび半導体光デバイスモジュール | |

| US20030031428A1 (en) | Parellel electro-optic interface assembly |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20031202 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20031222 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050322 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050523 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060117 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060120 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100127 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110127 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110127 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120127 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120127 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130127 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |