JP3649878B2 - デジタル無線通信装置の検波方法及びその回路 - Google Patents

デジタル無線通信装置の検波方法及びその回路 Download PDFInfo

- Publication number

- JP3649878B2 JP3649878B2 JP28734597A JP28734597A JP3649878B2 JP 3649878 B2 JP3649878 B2 JP 3649878B2 JP 28734597 A JP28734597 A JP 28734597A JP 28734597 A JP28734597 A JP 28734597A JP 3649878 B2 JP3649878 B2 JP 3649878B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- circuit

- phase

- quantized data

- average

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/06—DC level restoring means; Bias distortion correction ; Decision circuits providing symbol by symbol detection

- H04L25/068—DC level restoring means; Bias distortion correction ; Decision circuits providing symbol by symbol detection by sampling faster than the nominal bit rate

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

Description

【発明の属する技術分野】

本発明はデジタル無線通信装置の検波方法及びその回路に関し、PSK(フェイズシフトキーイング)変調信号を受信するデジタル無線通信装置の検波方法及びその回路に関する。

【0002】

【従来の技術】

図13は従来のデジタル無線通信装置の検波回路の一例のブロック図を示す。同図中、端子10にはデジタル無線通信装置で受信した、例えばPSK(フェイズシフトキーイング)信号の中間周波信号(IF)が入来し量子化回路11に供給される。量子化回路11では中間周波信号の位相を量子化して図14( A)に示すような位相の量子化データをサンプリング回路12に供給する。サンプリング回路12にはPLL(フェーズロックトループ)13から図14(B)に示すような再生クロックが供給されており、サンプリング回路12は再生クロックの立ち上がりエッジで上記の量子化データをサンプリングして図14(C)に示す位相の量子化データをPLL13及びデータ判定回路14に供給する。

【0003】

PLL13はサンプリングされた量子化データに同期した再生クロックを生成する。データ判定回路14はサンプリングされた位相の量子化データから位相に応じた複数ビットのデータを判定することによりPSK復調(検波)を行い、得られたデータを端子15から出力する。

【0004】

【発明が解決しようとする課題】

従来回路は、再生クロックの1周期に1点のサンプリングポイントで位相の量子化データをサンプリングして、このサンプリングされた1周期に1点の量子化データを判定しているため、この1点のサンプリングポイントで突発的な位相ずれが発生した場合には、データの判定を誤ってしまうという問題があった。

【0005】

また、前段にリミッタを設けて振幅制限し位相のみを再生に用いる方式では、リミッタがない場合に比してアイパターンの開口点が狭くなり、再生クロックによるサンプリングポイントが厳密でなければならず、サンプリングポイントが多少でも前後にずれた状態では良好な検波を行うことができない。また、デジタル無線通信装置の受信能力や内部で発生するスプリアスの影響があると、アイパターンがぼやけるため良好な検波を行うことができず、データの判定を誤ってしまうおそれがあるという問題があった。

【0006】

本発明は、上記の点に鑑みなされたもので、データの判定を誤るおそれの少ないデジタル無線通信装置の検波方法及び回路を提供することを目的とする。

【0007】

【課題を解決するための手段】

請求項1に記載の発明は、PSK変調信号を受信するデジタル無線通信装置の検波方法において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波方法であって、

前記再生クロックを中心とする前後の複数ポイントのサンプリングは、前記PSK変調信号の周期で離散的に行い、

前記位相データの合成は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする。

【0008】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。

【0013】

請求項2に記載の発明は、請求項1記載のデジタル無線通信装置の検波方法において、

前記位相データの合成は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均して得る。

【0014】

これにより、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

請求項3に記載の発明は、PSK変調信号を受信するデジタル無線通信装置の検波回路において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成する合成手段を有し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波回路であって、

前記再生クロックを中心とする前後の複数ポイントは、前記PSK変調信号の周期で離散的に行い、

前記位相データの合成手段は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする頻度判定手段を有する。

【0015】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、請求項1の発明を実現できる。

【0021】

請求項4記載の発明は、請求項3記載のデジタル無線通信装置の検波回路において、

前記位相データの合成手段は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均する重み付け平均手段を有する。

【0022】

これにより、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成でき、請求項2の発明を実現できる。

【0023】

【発明の実施の形態】

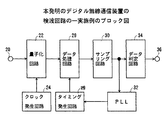

図1は本発明のデジタル無線通信装置の検波回路の一実施例のブロック図を示す。同図中、端子20にはデジタル無線通信装置で受信した、例えばPSK(フェイズシフトキーイング)信号の中間周波信号(IF)が入来し量子化回路22に供給される。量子化回路22ではクロック発生回路24から供給される高速クロックを用いて中間周波信号を量子化して図2( A)に示すような位相の量子化データを得て、時系列の量子化データをデータ処理回路(合成手段)26に供給する。

【0024】

データ処理回路26は図2(B)に示す再生クロックの立ち上がりを中心として前後の複数の量子化データm−2,m−1,m、m+1,m+2から図2(C)に示す位相データmを合成してサンプリング回路30に供給する。タイミング発生回路28はクロック及びタイミング信号を生成してデータ処理回路26及びサンプリング回路30それぞれに供給している。サンプリング回路30はタイミング発生回路28よりのシンボルクロック周波数のタイミング信号によって合成位相データをラッチしてPLL(フェーズロックトループ)32及びデータ判定回路34に供給する。

【0025】

PLL32はサンプリングされた合成位相データに同期して図2(B)に示すようなシンボルクロック周波数の再生クロックを生成し、タイミング発生回路28に供給する。タイミング発生回路28はこの再生クロックを基準としてクロック及びタイミング信号を生成する。データ判定回路34はサンプリングされた合成位相データから位相に応じた複数ビットのデータを判定することによりPSK復調を行い、得られたデータを端子36から出力する。

【0026】

ここで、PSKのシンボル周波数、つまり再生クロック周波数は例えば21KHzであり、中間周波信号の周波数は例えば450KHzであり、量子化周波数は例えば14.4MHzである。

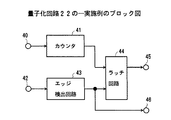

図3は量子化回路22の一実施例のブロック図を示す。同図中、カウンタ41には端子40を介してクロック発生回路24より、例えば周波数14.4MHzのクロックが供給され、カウンタ41はこのクロックをカウントしてラッチ回路44に供給する。また、エッジ検出回路43は端子42から供給される中間周波信号の立ち上がりエッジを検出してラッチ回路44に供給する。ラッチ回路44はエッジ検出信号の供給時にカウンタ41のカウント値を位相の量子化データとしてラッチして端子45より出力する。また、エッジ検出信号が端子46より出力される。

【0027】

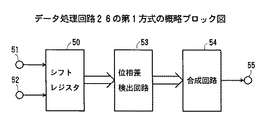

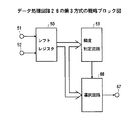

データ処理回路26は図4又は図5又は図6に示す構成である。図4はデータ処理回路26の第1方式の概略ブロック図を示す。同図中、端子51,52から入来する位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれはシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは位相差検出回路(位相差検出手段)53に供給され各量子化データの位相差が検出される。これらの各位相差データは合成回路(ベクトル合成手段)54に供給され、ここでベクトル合成により合成位相データが得られ、端子55から出力される。

【0028】

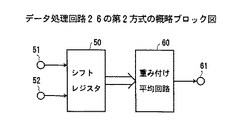

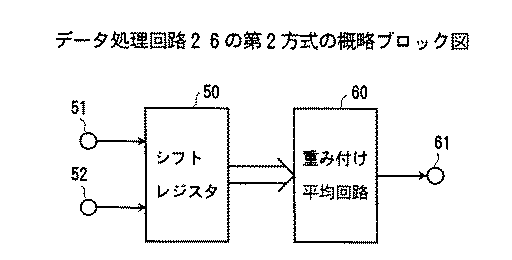

図5はデータ処理回路26の第2方式の概略ブロック図を示す。同図中、端子51,52から入来する位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれはシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは重み付け平均回路(重み付け平均手段)60に供給され各量子化データの重み付けした平均値が算出される。この量子化データの重み付け平均値は合成位相データとして端子61から出力される。

【0029】

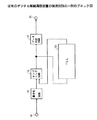

図6はデータ処理回路26の第3の概略ブロック図を示す。同図中、端子51,52から入来する位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれはシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは頻度判定手段としての頻度判定回路65及び選択回路66に供給される。頻度判定回路65はこれらの各量子化データから頻度の最も高い量子化データを検出し、検出した量子化データを選択するための制御信号を選択回路66に供給する。これによって、選択回路66は頻度の最も高い量子化データを選択し、選択された量子化データが合成位相データとして端子67から出力される。

【0030】

図7はデータ処理回路26の第1方式の一実施例のブロック図を示す。同図中、端子70,71には量子化回路22から位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれがが入来し、シフトレジスタ50を構成する遅延素子72〜75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの遅延素子73の出力量子化データを中心として、遅延素子74,75の出力量子化データを中心+1,中心+2と呼び、遅延素子72の出力量子化データを中心−1、端子70の入力量子化データを中心−2と呼ぶ。

【0031】

減算器80は中心ー1と中心ー2の量子化データの減算を行って減算値θをテーブル81に供給する。テーブル81にはθに対応して(1)式により得られる位相差が予め格納されている。

【0032】

【数1】

【0033】

但し、Aは中心ー1と中心ー2とに同一感度を与える振幅差としての定数。

この(1)式について説明するに、長さA1 位相θ1 のベクトルと、長さA2 位相θ2 のベクトルとを合成したベクトルの位相は(2)式で表される。

【0034】

【数2】

【0035】

(2)式では4つの変数があるため、計算が複雑である。このため、A1 とA2 との比をAとし、θ1 とθ2 との差をθとすると、合成ベクトルの位相θG は(3)式で表す。

【0036】

【数3】

【0037】

(3)式では変数が2つである上に、Aの値がある程度大きくなると位相差の値が小さくなり影響が小さくなるためAの範囲を限定できる。本実施例ではAの値として、中心からずれた位相で中心と同一のレベル(同一感度)を得る振幅を考慮している。これは中心が最も良好で、中心から位相がずれた位置でのレベルの劣化に応じて影響を小さくするためであり、即ち中心から位相がずれた位置でのレベルの大きさを表すものである。この(3)式に基づいて(1)式の演算を行う。

【0038】

減算器80の出力する位相差は加算器82で遅延素子73の出力する中心の量子化データに加算されてベクトル合成された後、減算器83に供給される。また、減算器86は中心+1と中心+2の量子化データの減算を行って減算値θをテーブル87に供給する。テーブル87にはθに対応して(1)式により得られる位相差が予め格納されている。但し、Aは中心+1と中心+2とに同一感度を与える振幅差としての定数である。テーブル87からは(1)式による位相差が得られ、この位相差は加算器88で遅延素子74の出力する中心+1の量子化データに加算されてベクトル合成された後、減算器83に供給される。

【0039】

減算器83は加算器82,88出力の量子化データの減算を行って減算値θをテーブル84に供給する。テーブル84にはθに対応して(1)式により得られる位相差が予め格納されている。但し、Aは中心+側と中心−側とに同一感度を与える振幅差としての定数である。テーブル84からは(1)式による位相差が得られ、この位相差は加算器85で加算器88の出力する中心−側の量子化データに加算されてベクトル合成された後、減算器89に供給される。

【0040】

減算器89は加算器85,遅延素子73出力の量子化データの減算を行って減算値θをテーブル90に供給する。テーブル90にはθに対応して(1)式により得られる位相差が予め格納されている。但し、Aは中心+側と中心−側とに同一感度を与える振幅差としての定数である。テーブル90からは(1)式による位相差が得られ、この位相差は加算器91で遅延素子73の出力する中心の量子化データに加算されてベクトル合成された後、合成位相データとして端子92から出力される。 上記の減算器80,83,86,89及びテーブル81,84,87,90が位相差検出回路53に対応し、加算器82,85,88,91が合成回路54に対応する。

【0041】

この実施例では、合成する量子化データの一方を基準として他方の位相差を求め、その位相差に応じたテーブルを参照して合成後の位相差を得て、基準の量子化データに合成後の位相差を足し込むことで合成位相差を求めている。これにより、簡単な演算で正確な合成位相差を求めることができる。

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は多少回路規模が大きくなるものの、各信号の合成により等価的にエネルギーの増加を図ることができ、C/Nが改善され、良好な特性を得ることができる。

【0042】

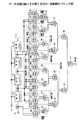

図8はデータ処理回路26の第2方式の一実施例のブロック図を示す。同図中、端子70,71には量子化回路22から位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれがが入来し、シフトレジスタ50を構成する遅延素子72〜75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの端子71の入力量子化データをSD0とし、遅延素子72〜75それぞれの出力する量子化データをSD1〜SD4とする。

【0043】

平均回路101は2つの量子化データSD0の平均を取り、平均回路102は2つの量子化データSD0,SD4の平均を取り、平均回路103,104それぞれは2つの量子化データSD1の平均を取り、平均回路105〜110それぞれは2つの量子化データSD2の平均を取る。平均回路111〜113それぞれは2つの量子化データSD3の平均を取り、平均回路114は2つの量子化データSD3,SD4の平均を取り、平均回路115は2つの量子化データSD1の平均を取り、平均回路116は2つの量子化データSD4の平均を取る。

【0044】

平均回路121は2つの平均回路101,102出力の量子化データの平均を取り、平均回路122は2つの平均回路103,104出力の量子化データの平均を取り、平均回路123は2つの平均回路105,106出力の量子化データの平均を取り、平均回路124は2つの平均回路107,108出力の量子化データの平均を取り、平均回路125は2つの平均回路109,110出力の量子化データの平均を取り、平均回路126は2つの平均回路111,112出力の量子化データの平均を取り、平均回路127は2つの平均回路113,114出力の量子化データの平均を取り、平均回路128は2つの平均回路115,116出力の量子化データの平均を取る。

【0045】

更に、平均回路131は2つの平均回路121,122出力の量子化データの平均を取り、平均回路132は2つの平均回路123,124出力の量子化データの平均を取り、平均回路133は2つの平均回路125,126出力の量子化データの平均を取り、平均回路134は2つの平均回路127,128出力の量子化データの平均を取る。更に、平均回路141は2つの平均回路131,132出力の量子化データの平均を取り、平均回路142は2つの平均回路133,134出力の量子化データの平均を取り、平均回路151は2つの平均回路141,142出力の量子化データの平均を取り、合成位相データとして端子152より出力する。

【0046】

ここで、平均回路102,103〜113,115,116,122〜126,132は同一データを平均しているため、実際には不要である。この実施例では平均回路102〜116に供給する量子化データのうち中心の量子化データSD2の数を多くして大きな重み付けを行い、次に中心に近い量子化データSD1,SD3の数を減らし重み付けを減らし、更に中心から遠い量子化データSD0,SD4の数を減らし重み付けを減らしている。

【0047】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は簡易的、かつ、柔軟な重み付けを行う回路構成とすることができる。

【0048】

図9はデータ処理回路26の第3方式の一実施例のブロック図を示す。同図中、端子70,71には量子化回路22から位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれがが入来し、シフトレジスタ50を構成する遅延素子72〜75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの遅延素子72〜75それぞれの出力する量子化データをSD1〜SD4とする。この量子化データSD1〜SD4は頻度判定回路65を構成するセレクタ200に供給される。

【0049】

演算用高速クロック発生器201は量子化データSD1〜SD4を選択するために、シンボルクロックの4倍の周波数のクロックを発生してカウンタ202に供給する。カウンタ202は4進のカウンタであり、1〜4のカウント値をセレクタ200に供給する。セレクタ200はこのカウント値に対応する量子化データSD1〜SD4のいずれかを選択してデコーダ203に供給する。

【0050】

デコーダ203は供給される量子化データSD1〜SD4それぞれを順次デコードして、量子化データの値に応じた端子からカウンタ2051 〜205N のいずれかに値1の信号を出力し、他の端子から残りのカウンタ2051 〜205N に値0の信号を出力する。なお、本実施例では量子化データの値は0〜32であり、N=33である。カウンタ2051 〜205N それぞれは量子化のタイミング信号の入来毎にリセットされて、値1の信号を供給されたときカウントアップを行い、それぞれのカウント値をイクスクルーシブオア回路2061 〜206N それぞれに供給する。

【0051】

レジスタ210は量子化のタイミング信号の供給によりカウンタ202の出力するカウント値をプリセットされ、その後、減算器211により値を1ずつ減じる。これによりレジスタ210の出力値はカウンタ202の出力するカウント値を上限として1ずつ値が減少し、この値はイクスクルーシブオア回路2061 〜206N それぞれに供給される。なお、遅延素子72〜75それぞれの遅延時間をxとし、遅延素子72〜75の個数をyとしたとき、減算器211の減算周期はx/(y+1)以下である。

【0052】

イクスクルーシブオア回路2061 〜206N それぞれは供給される2つの値が一致したときにのみ値1の信号を出力する。イクスクルーシブオア回路2061 〜206N それぞれの出力値は加算器212及びアンド回路2131 〜213N に供給され、加算器212はこれらの値を加算してコンパレータ214,215それぞれに供給する。

【0053】

コンパレータ214,215それぞれには値1が供給されている。加算器212出力が1のときコンパレータ214は値1の頻度選択信号を生成して端子216から出力し、加算器212出力が1を超えるときコンパレータ215は値1の平均選択信号を生成して端子216から出力する。つまり、カウンタ2051 〜205N のうちカウント値がレジスタ210の値と一致するカウンタの数が1のとき頻度選択信号が出力され、2以上のとき平均選択信号が出力される。この頻度選択信号又は平均選択信号はオア回路217を介してレジスタ210,減算器211に供給され、レジスタ210に値を保持させると共に、減算器211の演算を停止させる。

【0054】

アンド回路2131 〜213N それぞれには量子化データの値1〜Nが供給されており、イクスクルーシブオア回路2061 〜206N の出力値が値1のとき、対応する量子化データの値が出力されてオア回路220を介しアンド回路221に供給され、アンド回路221は頻度選択信号が値1のとき、この量子化データの値を合成位相データとして端子222より出力する。上記のセレクタ200からアンド回路221が頻度判定回路65を構成している。

【0055】

これにより、量子化データSD1〜SD4が例えば全て「16」の場合、カウンタ205I (1<I<N)のカウント値が4となり、イクスクルーシブオア回路206I 出力が1、加算器212出力が1となって頻度選択信号が出力され、アンド回路213I から出力される量子化データの値「16」が端子222より出力される。量子化データSD1〜SD4が例えば「16,16,17,17」の場合、カウンタ205I (1<I<N)のカウント値が2、カウンタ205J (I<J<N)のカウント値が2となり、イクスクルーシブオア回路206I ,206J 出力が1、加算器212出力が2となって平均選択信号が出力され、アンド回路213I から出力される量子化データの値は端子222から出力されない。

【0056】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は小さい回路規模で構成することが可能であり、この回路の追加による品質の劣化が少ない。また、頻度判定のサンプル数を増加することでよりいっそうの改善が可能となる。

【0057】

図10は第2方式と第3方式を組み合わせたデータ処理回路26の一実施例のブロック図を示す。同図中、端子300,301には量子化回路22から位相の量子化データ,タイミング発生回路28からのタイミング信号それぞれがが入来し、位相の量子化データはセレクタ309を通してシフトレジスタ50を構成する遅延素子302〜305に供給され、遅延素子302〜305を位相の量子化データが順次シフトされる。

【0058】

ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの端子300の入力量子化データをDQとし、遅延素子302の入力量子化データをDQ1とし、遅延素子302〜305それぞれの出力する量子化データをDQ1〜DQ4とする。この量子化データDQ,DQ1〜DQ4は頻度判定回路306と判定及び平均回路307に供給される。頻度判定回路306は図9と同一構成であり、頻度判定回路306の出力する頻度選択信号、平均選択信号、合成位相データそれぞれはモード回路308に供給される。

【0059】

判定及び平均回路307内の判定回路310は平均回路311から供給される量子化データの平均値を最新の量子化データDQと比較してその差が端子311より供給される設定値SASETより大なるときのみ値1で、その他の場合値0の制御信号をセレクタ309及び平均回路311に供給する。セレクタ309はこの信号が0のときは最新の量子化データDQをDQ0として出力するが、この信号が1で量子化データDQの信頼性が低いときは平均回路311から供給される量子化データの平均値を最新の量子化データDQの代わりに選択してDQ0として出力する。

【0060】

平均回路311は図11に示す構成である。この構成は第2方式の他の実施例でもある。図11において、端子320〜324には量子化データDQ,DQ1〜DQ4が供給され、端子325,326には重み付けを変更するための制御信号SELA,SELBが供給される。セレクタ330は制御信号SELAが1のとき量子化データDQ2を選択し、制御信号SELAが0のときDQ1を選択して平均演算回路332に供給する。セレクタ331は制御信号SELBが1のとき量子化データDQ2を選択し、制御信号SELBが0のときDQ3を選択して平均演算回路332に供給する。このセレクタ330,331での選択によってどの量子化データの重みを大きくするかの重み付けを変更している。

【0061】

平均演算回路332はセレクタ330,331から供給される量子化データの平均を取って平均演算回路334,337に供給し、平均演算回路333は量子化データDQ1,DQ3の平均を取って平均演算回路334に供給し、平均演算回路334は平均演算回路332,333出力の量子化データの平均を取って平均演算回路335に供給する。平均演算回路335は平均演算回路334出力の量子化データと量子化データDQ2との平均を取って平均演算回路339に供給する。

【0062】

平均演算回路336は量子化データDQ0,DQ4の平均を取って平均演算回路337に供給し、平均演算回路337は平均演算回路333,336出力の量子化データの平均を取って平均演算回路339に供給する。平均演算回路339は平均演算回路335,339出力の量子化データの平均を取って合成位相データとして端子340から出力する。

【0063】

ここで、平均演算回路332,333,336それぞれは供給される2つの量子化データの位相差が180度異なるときマスク信号を出力する。平均演算回路334,335,337,339それぞれはマスク信号を供給されると、マスク信号を供給してない方の量子化データを平均として出力し、更に平均演算回路334,337それぞれは双方からマスク信号を供給されると、マスク信号を出力する。これはノイズが混入したときにその影響を除去するためである。

【0064】

平均演算回路339の出力する合成位相データは端子340から出力されると共に、平均値保存回路341に供給される。平均値保存回路341は端子327から量子化のタイミング信号を供給されるタイミングで、平均演算回路339からの合成位相データを保存して、端子341から出力する。

図10に戻って説明するに、平均回路311が端子340から出力する合成位相データはモード回路308に供給され、端子341から出力する保存された合成位相データはセレクタ309に供給される。モード回路308は端子350からのモード信号に応じて頻度判定回路306又は平均回路311からの合成位相データを端子352からのクロックに同期して端子353から出力する。

【0065】

通常モード時には、頻度判定回路306から頻度選択信号が供給されると、頻度判定回路306よりの合成位相データを端子353より出力し、頻度判定回路306から平均選択信号が供給されると、平均回路311よりの合成位相データを端子353より出力する。つまり、同一値の量子化データの頻度が高いときは、この量子化データが正常であるとして出力し、同一値の量子化データの頻度が低いときは平均値を取ってノイズ等の影響を低減し、出力している。

【0066】

この実施例では、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

図12はタイミング発生回路28の一実施例のブロック図を示す。同図中、位相レジスタ360には外部の図示しない制御回路より端子361を介して再生クロックに対する中心の量子化データの位相差を指示する位相値が設定され、位相値はカウンタ362に供給される。また、合成数レジスタ364には外部の図示しない制御回路より端子365を介して合成する量子化データ数を指示する合成数が設定され、合成数はカウンタ362に供給される。

【0067】

カウンタ362には、このほかに、PLL32からの再生クロックが端子366を介して供給され、端子367を介して例えば周波数14.4MHzのクロックが供給されており、カウンタ362は再生クロックの立ち上がりから上記位相値だけ移相したタイミングを中心として、周波数450KHzの周期で前記中心及び中心の前後に合成数だけのパルスを発生して、これをタイミング信号として端子368からデータ処理回路26に供給する。また、前記中心で発生したパルスを端子369よりサンプリング回路30に供給している。

【0068】

なお上記実施例では、4相のPSK信号の検波を例にして説明したが、これは8相又は16相のPSK信号のデジタル無線通信装置の検波回路等にも適用でき、上記実施例に限定されない。

【0069】

【発明の効果】

上述の如く、請求項1に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。

【0076】

また、請求項2に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

また、請求項3に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、請求項1の発明を実現できる。

【0084】

また、請求項4に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成でき、請求項2の発明を実現できる。

【図面の簡単な説明】

【図1】本発明のデジタル無線通信装置の検波回路の一実施例のブロック図である。

【図2】本発明の信号タイミングチャートである。

【図3】量子化回路22の一実施例のブロック図である。

【図4】データ処理回路26の第1方式の概略ブロック図である。

【図5】データ処理回路26の第2方式の概略ブロック図である。

【図6】データ処理回路26の第3方式の概略ブロック図である。

【図7】データ処理回路26の第1方式の一実施例のブロック図である。

【図8】データ処理回路26の第2方式の一実施例のブロック図である。

【図9】データ処理回路26の第3方式の一実施例のブロック図である。

【図10】第2方式と第3方式を組み合わせたデータ処理回路26の一実施例のブロック図である。

【図11】データ処理回路26の第2方式の他の実施例のブロック図である。

【図12】タイミング発生回路28の一実施例のブロック図

【図13】従来のデジタル無線通信装置の検波回路の一例のブロック図である。

【図14】従来回路の信号タイミングチャートである。

【符号の説明】

22 量子化回路

24 クロック発生回路

26 データ処理回路

28 タイミング発生回路

30 サンプリング回路

32 PLL

34 データ判定回路

50 シフトレジスタ

53 位相差検出回路

54 合成回路

60 平均回路

65 頻度判定回路

66 選択回路

Claims (4)

- PSK変調信号を受信するデジタル無線通信装置の検波方法において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波方法であって、

前記再生クロックを中心とする前後の複数ポイントのサンプリングは、前記PSK変調信号の周期で離散的に行い、

前記位相データの合成は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする

ことを特徴とするデジタル無線通信装置の検波方法。 - 請求項1記載のデジタル無線通信装置の検波方法において、

前記位相データの合成は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均して得る

ことを特徴とするデジタル無線通信装置の検波方法。 - PSK変調信号を受信するデジタル無線通信装置の検波回路において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成する合成手段を有し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波回路であって、

前記再生クロックを中心とする前後の複数ポイントは、前記PSK変調信号の周期で離散的に行い、

前記位相データの合成手段は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする頻度判定手段を有する

ことを特徴とするデジタル無線通信装置の検波回路。 - 請求項3記載のデジタル無線通信装置の検波回路において、

前記位相データの合成手段は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均する重み付け平均手段を有する

ことを特徴とするデジタル無線通信装置の検波回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP28734597A JP3649878B2 (ja) | 1997-10-20 | 1997-10-20 | デジタル無線通信装置の検波方法及びその回路 |

| US09/052,091 US5977821A (en) | 1997-10-20 | 1998-03-31 | Digital detection method and circuit for PSK modulated signals |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP28734597A JP3649878B2 (ja) | 1997-10-20 | 1997-10-20 | デジタル無線通信装置の検波方法及びその回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11127207A JPH11127207A (ja) | 1999-05-11 |

| JP3649878B2 true JP3649878B2 (ja) | 2005-05-18 |

Family

ID=17716178

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP28734597A Expired - Fee Related JP3649878B2 (ja) | 1997-10-20 | 1997-10-20 | デジタル無線通信装置の検波方法及びその回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US5977821A (ja) |

| JP (1) | JP3649878B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6570944B2 (en) * | 2001-06-25 | 2003-05-27 | Rambus Inc. | Apparatus for data recovery in a synchronous chip-to-chip system |

| US6760389B1 (en) * | 1998-06-01 | 2004-07-06 | Agere Systems Inc. | Data recovery for non-uniformly spaced edges |

| US6584163B1 (en) * | 1998-06-01 | 2003-06-24 | Agere Systems Inc. | Shared data and clock recovery for packetized data |

| US7283011B2 (en) * | 2003-10-10 | 2007-10-16 | Atmel Corporation | Method for performing dual phase pulse modulation |

| US6947493B2 (en) * | 2003-10-10 | 2005-09-20 | Atmel Corporation | Dual phase pulse modulation decoder circuit |

| US7103110B2 (en) * | 2003-10-10 | 2006-09-05 | Atmel Corporation | Dual phase pulse modulation encoder circuit |

| WO2005106678A1 (en) * | 2004-04-30 | 2005-11-10 | Research In Motion Limited | System and method of operation control on an electronic device |

| US7079577B2 (en) * | 2004-09-08 | 2006-07-18 | Atmel Corporation | Wide window decoder circuit for dual phase pulse modulation |

| US8045958B2 (en) | 2005-11-21 | 2011-10-25 | Research In Motion Limited | System and method for application program operation on a wireless device |

| EP1826944B1 (en) * | 2006-02-27 | 2009-05-13 | Research In Motion Limited | Method of customizing a standardized IT policy |

| CN101681670B (zh) * | 2007-04-19 | 2014-02-05 | 拉姆伯斯公司 | 存储器系统中的时钟同步 |

| JP2008294730A (ja) * | 2007-05-24 | 2008-12-04 | Sony Corp | 信号処理装置および方法、並びにプログラム |

| US9923741B2 (en) | 2016-03-24 | 2018-03-20 | The United States Of America As Represented By Secretary Of The Navy | Method for detecting presence or absence of phase shift keying modulations |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4773083A (en) * | 1985-11-08 | 1988-09-20 | Raytheon Company | QPSK demodulator |

| FR2662890B1 (fr) * | 1990-05-29 | 1992-09-04 | Europ Agence Spatiale | Demodulateur numerique pour signal module par deplacement de phase a plusieurs etats. |

-

1997

- 1997-10-20 JP JP28734597A patent/JP3649878B2/ja not_active Expired - Fee Related

-

1998

- 1998-03-31 US US09/052,091 patent/US5977821A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11127207A (ja) | 1999-05-11 |

| US5977821A (en) | 1999-11-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3649878B2 (ja) | デジタル無線通信装置の検波方法及びその回路 | |

| JP3072833B2 (ja) | ディジタルpll回路 | |

| US7920664B2 (en) | Clock synchronization circuit | |

| JPH09266499A (ja) | デジタル復調回路、最大値検出回路及び受信装置 | |

| US5889826A (en) | Apparatus and method for diversity combining | |

| US5475705A (en) | Demodulator for Manchester-coded FM signals | |

| US5455847A (en) | Clock recovery phase detector | |

| CA1294334C (en) | Digital data separator | |

| US5859551A (en) | Digital PLL circuit | |

| US5793250A (en) | Phase demodulator selectively using a first or a second detector | |

| JP2000151733A (ja) | 期間幅ウインド技法を用いる位相偏移キ―イング復調器および復調方法 | |

| US4815107A (en) | Digital code decoding apparatus | |

| JP3350290B2 (ja) | 受信装置 | |

| US5572550A (en) | Decision directed carrier recovery circuit using phase error detector | |

| US6204725B1 (en) | Circuit for demodulating digital signal undergoing different modulation schemes | |

| JP3819469B2 (ja) | 周波数補償機能を備えた無線通信装置 | |

| JP3212385B2 (ja) | クロック再生回路 | |

| JPH06261030A (ja) | フレーム同期検出回路 | |

| JPH06177786A (ja) | インパルス性雑音除去装置 | |

| US7200189B1 (en) | Method and system for providing adaptive timing recovery for low power application | |

| US6356612B1 (en) | Clock signal reproducing apparatus | |

| KR100219880B1 (ko) | 완전 디지털 위상 검출 장치를 이용한 디지털수신기 및디지털 위상 검출 방법 | |

| JPH0863888A (ja) | 信号処理装置 | |

| US5652769A (en) | Costas loop and data identification apparatus | |

| JP4182594B2 (ja) | Palシーケンス判別方法及び回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041111 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041124 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050215 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050216 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080225 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090225 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090225 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100225 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110225 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110225 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120225 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130225 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130225 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140225 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |