JP3642062B2 - 高周波スイッチ - Google Patents

高周波スイッチ Download PDFInfo

- Publication number

- JP3642062B2 JP3642062B2 JP2003191342A JP2003191342A JP3642062B2 JP 3642062 B2 JP3642062 B2 JP 3642062B2 JP 2003191342 A JP2003191342 A JP 2003191342A JP 2003191342 A JP2003191342 A JP 2003191342A JP 3642062 B2 JP3642062 B2 JP 3642062B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- transmission

- reception

- electrode

- diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000005540 biological transmission Effects 0.000 claims description 234

- 239000003990 capacitor Substances 0.000 claims description 40

- 238000003475 lamination Methods 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 8

- 239000002184 metal Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/58—Structural electrical arrangements for semiconductor devices not otherwise provided for

- H01L2223/64—Impedance arrangements

- H01L2223/66—High-frequency adaptations

- H01L2223/6661—High-frequency adaptations for passive devices

- H01L2223/6677—High-frequency adaptations for passive devices for antenna, e.g. antenna included within housing of semiconductor device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16227—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

Landscapes

- Waveguide Switches, Polarizers, And Phase Shifters (AREA)

- Transceivers (AREA)

Description

【発明の属する技術分野】

本発明は、複数の送受信系を取り扱う高周波スイッチに関するものである。

【0002】

【従来の技術】

デジタル携帯電話などにおいて、アンテナANTと送信回路TXとの接続及びアンテナANTと受信回路RXとの接続を切り換えるために、高周波スイッチが用いられている。この高周波スイッチとしては、特開平6−197040号公報に開示されているものがある。

【0003】

この従来の高周波スイッチは、送信回路側にアノードが接続されアンテナ側にカソードが接続される第1のダイオード、アンテナと受信回路との間に接続されるストリップライン、および受信回路側にアノードが接続されアース側にカソードが接続される第2のダイオードを含み、ストリップラインは多層基板に内蔵され、第1のダイオード及び第2のダイオードは多層基板上に実装されたものである。また、この従来の高周波スイッチは、単に一つの送受信系(シングルバンド)に対応しているものである。

【0004】

【発明が解決しようとする課題】

近年の携帯電話の普及には、目を見張るものがあり、携帯電話の機能、サービスの向上が図られている。この新たな携帯電話として、デュアルバンド携帯電話、トリプルバンド携帯電話等の提案がなされている。このデュアルバンド携帯電話は、通常の携帯電話が一つの送受信系のみを取り扱うのに対し、2つの送受信系を取り扱うものであり、トリプルバンド携帯電話は、3つの送受信系を取り扱うものである。これにより、利用者は都合の良い送受信系を選択して利用することができるものである。

【0005】

このデュアル、又はトリプルバンド携帯電話において、それぞれの送受信系にそれぞれ専用の回路を構成すれば、機器の大型化、高コスト化を招く。共通部分はできるだけ共通部品を用いることが、機器の小型化、低コスト化に有利となる。

【0006】

本発明は、アンテナを共通とし、複数の送受信系の送信回路と受信回路を切り換えることが可能な高周波スイッチを小型に構成することを目的とし、これを用いて通過帯域の異なる3つの送受信系を扱うトリプルバンド用高周波スイッチモジュールをワンチップで構成することができる。

【0007】

【課題を解決するための手段】

第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置され、前記伝送線路を介して前記第1及び第2のダイオードと接続する第3のダイオードと、前記第1のダイオードと前記共通の送信回路との間に接続される他の伝送線路を備え、前記他の伝送線路と前記第1のダイオードとの間にはローパスフィルタ回路が配置されており、アンテナ側回路と第2の送受信系の受信回路との間に配置された前記伝送線路は、誘電体層と電極パターンとの積層体内にライン電極として形成され、該ライン電極に対して上側及び下側には、誘電体層を介してグランド電極が形成されている高周波スイッチ。

ここで、前記第1乃至第3のダイオードが前記積層体に搭載されていることが好ましい。

【0008】

また本発明は、第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、前記伝送線路は、誘電体層と電極パターンとの積層体内に、ライン電極として形成され、前記第1乃至第3のダイオードは前記積層体に搭載され、さらに、前記積層体にはローパスフィルタ回路用の電極パターンを有し、前記ライン電極の形成された誘電体層と前記第1乃至第3のダイオードが搭載された前記積層体の面との間に、グランド電極が形成された誘電体層が設けられ、前記ローパスフィルタ回路用の電極パターンと前記グランド電極とでコンデンサを構成した高周波スイッチである。

【0009】

また本発明は、第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、

前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、

前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、

前記伝送線路は、誘電体層と電極パターンとの積層体内に、ライン電極として形成され、

前記第1乃至第3のダイオードは前記積層体に搭載され、

前記伝送線路の一端は、スルーホール電極を介して前記第1及び第2のダイオードのアノード側と接続する高周波スイッチである。

ここで、前記ライン電極の形成された誘電体層と前記第1及び第2のダイオードが搭載された前記積層体の面との間に、グランド電極が形成された誘電体層が設けられており、前記グランド電極が形成された誘電体層に形成されたスルーホール電極を介して、前記第1及び第2のダイオードと前記伝送線路とが接続されていることが好ましい。

【0010】

また本発明は、第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、前記伝送線路は、誘電体層と電極パターンとの積層体内にライン電極で形成され、異なる誘電体層に形成されたライン電極の一端どうしをスルーホール電極で接続し積層方向に巻回させた高周波スイッチである。

ここで、前記伝送線路に対して上側及び下側には、誘電体層を介してグランド電極を形成するのが好ましい。

【0011】

本発明においては、前記送信回路側にローパスフィルタ回路を有し、前記ローパスフィルタ回路をライン電極、グランド電極、コンデンサ電極などの電極パターンで前記積層体に形成するのも好ましい。

そして、前記第1乃至第3のダイオードは前記積層体に搭載し、前記第1のダイオードは、前記伝送線路を構成するライン電極と前記ローパスフィルタ回路を構成するライン電極と、前記積層体に形成されたスルーホール電極を介して接続するのも好ましい。

前記第1のダイオードには前記ローパスフィルタ回路を構成するライン電極を介して電圧が加えるように構成しても良い。

【0012】

上記本発明において、 前記伝送線路の一端を前記第1及び第2のダイオードのカソード側に接続し、前記伝送線路の他端を前記第3のダイオードのアノード側に接続すること、又、前記伝送線路の一端を前記第1及び第2のダイオードのアノード側に接続し、前記伝送線路の他端を前記第3のダイオードのカソード側に接続することができる。また、アンテナ側回路が分波回路であることが好ましく、前記分波回路はインダクタンス成分と容量成分で形成したフィルタ回路を組み合わせて構成するのが好ましい。

【0013】

そして、アンテナと送受信回路との間に、このような高周波スイッチを配置して携帯電話とするのも好ましい。

【0014】

【発明の実施の形態】

本発明は、通過帯域の異なる複数の送受信系を扱う高周波スイッチであり、積層構造体及びその積層体上にチップ部品を配置することにより、小型に構成したものである。本発明のスイッチ回路を用いて構成したトリプルバンド用高周波スイッチモジュールを基に、以下本発明の実施の形態を説明する。このトリプルバンド用高周波スイッチモジュールは、アンテナを共用とし、第3の送受信系の送信系と受信系、その第3の送受信系と通過帯域の異なる第1の送受信系の送信系と受信系、更に異なる通過帯域の第2の送受信系の送信系と受信系と、アンテナとを接続し、適宜切り換えることができるトリプルバンド用高周波スイッチモジュールであり、例えばトリプルバンド携帯電話等において有効なものである。

【0015】

前記トリプルバンド用高周波スイッチモジュールでは、アンテナ側回路の分波回路により、第3の送受信系と、第1及び第2の送受信系とを分け、その第3の送受信系に第2のスイッチ回路を設け、第3の送受信系の送信系と受信系を分けている。また、第1及び第2の送受信系に第1のスイッチ回路(本発明の高周波スイッチ)を設け、第1と第2の送受信系に共通の送信系と、第1の送受信系の受信系と、第2の送受信系の受信系とを分け、第1の送受信系の送信系端子と第2の送受信系の送信端子を共用としている。

【0016】

本発明では、複数の送受信系の共通端子、各送受信系のそれぞれの送信系端子、受信系端子を積層体の側面に形成し、面実装可能としている。この側面に形成した各端子は、その上面又は下面に延長されていてもかまわない。そして、各側面には、少なくとも1つのグランド端子を形成している。この各側面にグランド端子を配置することにより、本発明のトリプルバンド用高周波スイッチモジュールの低損失化を計ることが出来る。

【0017】

本発明の各送受信系のスイッチ回路は、ダイオードスイッチ回路を用いることができる。このダイオードスイッチ回路では、ダイオードに所定の電圧を加えるための制御端子を用いる。この制御端子を積層体の側面に形成する。

【0018】

また本発明では、送信系端子と受信系端子とは、送信系端子どうし、又受信系端子どうしが近接して配置されることが好ましい。また、積層体を積層方向にみて、長手方向に2分する中心線に対し、別々の領域に、それぞれ送信系端子、受信系端子を配置することが好ましい。このように構成することにより、高周波スイッチモジュールが実装される複数の送受信系を扱う装置において、送信系回路、受信系回路と接続し易い、又、余分な損失を防止できる。

【0019】

また本発明は、共通端子と、それぞれの送受信系の送信端子及び受信端子とは、積層体を実装面に垂直な面で2分した場合、別領域に形成することが好ましい。つまり、積層体を積層方向にみて、短手方向に2分する中心線に対し、片側に共通端子を配置し、他方に送信端子及び受信端子を配置するものである。この高周波スイッチモジュールは、アンテナと送受信回路の間に配置されるので、この端子配置により、アンテナと高周波スイッチモジュール、及び送受信回路と高周波スイッチモジュールを最短の線路で接続することができ、余分な損失を防止できる。

【0020】

本発明の積層体は、分波回路、及びスイッチ回路の伝送線路を内蔵することができる。このスイッチ回路の伝送線路は、グランド電極に挟まれた領域に形成されることが好ましい。また、分波回路は、インダクタンス成分と容量成分とにより構成することができる。この分波回路は、積層体内で、伝送線路よりも上側に配置されることが好ましい。そして、伝送線路を挟むグランド電極の上側のグランド電極のさらに上部に容量成分を配置し、更にその上部にインダクタンス成分を配置する構造とすることが好ましい。

【0021】

本発明では、各送信系にローパスフィルタ機能を設けることが好ましい。このローパスフィルタ機能を設ける一手段として、ローパスフィルタ回路を積層体内に内蔵することができる。このローパスフィルタ回路は、インダクタンス成分と容量成分とにより構成することができる。そして、このローパスフィルタ回路は、積層体内で、伝送線路よりも上側に配置されることが好ましい。つまり、伝送線路を挟むグランド電極の上側のグランド電極のさらに上部に容量成分を配置し、更にその上部にインダクタンス成分を配置する構造とすることが好ましい。また、このローパスフィルタ回路と分波回路は、積層体の水平方向の別領域に構成されることが好ましい。

【0022】

この伝送線路を挟むグランド電極の上側のグランド電極には、切り欠き部を設け、この切り欠き部に、伝送線路に導通するスルーホールを形成し、上側の分波回路、ローパスフィルタ回路と接続することができる。

【0023】

本発明では、積層体上に配置されたチップ部品を囲むように金属ケースを配置することが好ましい。この金属ケースは、積層体の側面の端子電極を露出させた状態で装着することが好ましい。また、金属ケースは、積層体の上面に半田付けで固定することができる。また、この金属ケースにより、マウンタ装置により、本発明の高周波スイッチモジュールを実装することができる。

【0024】

【実施例】

本発明に係る第1実施例の回路ブロック図を図1に示す。図1において、本発明の高周波スイッチは図中下側のスイッチ回路であり、破線で囲った部分がトリプルバンド用高周波スイッチモジュールとなる。本発明の高周波スイッチを用いたトリプルバンド用高周波スイッチモジュールは、例えば、第3の送受信系としてGSMシステム(送信TX.880〜915MHz、受信RX.925〜960MHz)、第2の送受信系としてDCS1800システム(送信TX.1710〜1785MHz、受信RX.1805〜1880MHz)、第1の送受信系としてPCSシステム(送信TX.1850〜1910MHz、受信RX.1930〜1990MHz)の3つのシステムに対応した構成として、トリプルバンド携帯電話のアンテナANTと、GSM系、DCS系、PCS系のそれぞれの送受信回路との振り分けに用いることができる。また、DCS系の送信系とPCS系の送信系は、共用としている。

【0025】

この第1実施例は、ANTに接続される端子から第3の送受信系(GSM)と、第2、第1の送受信系(DCS、PCS)を分波する分波回路を有し、その分波回路で分波された第3の送受信系(GSM)の送信信号(GSM TX)と受信信号(GSM RX)を切り換える第2のスイッチ回路SWを有し、第2のスイッチ回路の送信ラインに接続される第2のローパスフィルタ回路(LPF)を有している。また分波回路で分波された第1、第2の送受信系(DCS、PCS)では、第2の送受信系(DCS)の受信信号(DCS RX)と、第1の送受信系(PCS)の受信信号(PCS RX)と、第2、第1の送信信号(DCS、PCS TX)を切り換える第1のスイッチ回路SWを有し、第1のスイッチ回路の送信ラインに接続される第1のローパスフィルタ回路(LPF)を有している。

【0026】

また本発明に係る一実施例の等価回路図を図2に示す。アンテナANTに接続される分波回路部分は、2つのノッチ回路が主回路となっている。つまり、インダクタLF1とコンデンサCF1で一つのノッチ回路を構成し、インダクタLF2とコンデンサCF2でもう一つのノッチ回路を構成している。そして、一つのノッチ回路には、アースに接続されるコンデンサCF3が接続されている。このコンデンサCF3は、分波特性のローパスフィルタ特性を向上させる目的で接続されている。また、もう一つのノッチ回路には、アースに接続されるインダクタLF3と、コンデンサCF4を直列に接続している。このインダクタLF3とコンデンサCF4は、分波特性のハイパスフィルタ特性を向上させる目的で接続されている。

【0027】

この分波回路は、2つのノッチ回路のみでも良い。また、この分波回路は、ノッチ回路以外、例えばバンドパス回路、ローパス回路、ハイパス回路などを用いてもよく、これらを適宜組み合わせて構成することも出来る。

【0028】

次に、第2のスイッチ回路について説明する。第2のスイッチ回路は、図2上側のスイッチ回路であり、GSM系の送信回路TXと受信回路RXを切り換えるものである。このスイッチ回路は、2つのダイオードDG1、DG2と、2つの伝送線路LG1、LG2を主構成とし、ダイオードDG1はアンテナANT側にアノードが接続され、送信回路TX側にカソードが接続され、そのカソード側にアースに接続される伝送線路LG1が接続されている。そして、アンテナ側と受信回路RX間に伝送線路LG2が接続され、その受信回路側RXにカソードが接続されたダイオードDG2が接続され、そのダイオードDG2のアノードには、アースとの間にコンデンサCG6が接続され、その間にインダクタLG、抵抗R1の直列回路が接続され、コントロール回路VC1に接続される。

【0029】

そして、送信TX回路側に挿入されるローパスフィルタ回路は、インダクタLG3と、コンデンサCG3、CG4、CG7から構成され、スイッチ回路のダイオードDG1と伝送線路LG1の間に挿入されている。

【0030】

次に、本発明に係る高周波スイッチの第1のスイッチ回路について説明する。第1のスイッチ回路は、図2下側のスイッチ回路であり、DCS系の受信回路RXと、PCS系の受信回路RXと、DCS系及びPCS系の送信回路TXとを切り換えるものである。このスイッチ回路は、3つのダイオードDP1、DP2、DP3(第1乃至第3のダイオード)と、2つの伝送線路LP1、LP2を主構成とし、ダイオードDP1(第1のダイオード)はアンテナANT側にカソードが接続され、DCS及びPCSの送信回路TX側にアノードが接続され、そのアノード側に、コンデンサCGPを介してアースに接続される伝送線路LP1が接続されている。この伝送線路LP1とコンデンサCGPとの間にコントロール回路VC3が接続される。そして、アンテナ側とDCSの受信回路RX間に伝送線路LP2が接続され、そのDCS受信回路RX側にアノードが接続されたダイオードDP2(第3のダイオード)が接続され、そのダイオードDP2のカソードには、アースとの間にコンデンサCP6、抵抗R3が接続されている。そして、アンテナ側とPCSの受信回路RX間にダイオードDP3(第2のダイオード)が接続され、そのアンテナ側にダイオードDP3のカソードが接続され、アノード側には、インダクタLP、抵抗R2を介してコントロール回路VC2が接続される。

【0031】

そして、DCSとPCSの送信回路TX側に挿入されるローパスフィルタ回路は、インダクタLP3と、コンデンサCP3、CP4、CP7から構成され、スイッチ回路SWのダイオードDP1と伝送線路LP1の間に挿入されている。

【0032】

この実施例のスイッチモジュールの各コントロール回路VC1、VC2、VC3の制御ロジックを表1に示す。これにより、各モードを変更する。

【0033】

【表1】

【0034】

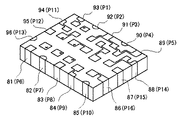

次に、本発明に係る一実施例の平面図を図3に、その実施例の積層体部分の斜視図を図4に、その積層体の内部構造図を図5に示す。この実施例では、分波回路、ローパスフィルタ回路、スイッチ回路の伝送線路を積層体内に構成し、ダイオード、チップコンデンサをその積層体上に搭載して、ワンチップ化されたトリプルバンド用高周波スイッチモジュールを構成したものである。図4に示す斜視部の外部端子に付与したP1〜P16は、図2の等価回路のP2、P4等のP数字と合致している。

【0035】

この積層体の内部構造について説明する。この積層体は、低温焼成が可能なセラミック誘電体材料からなるグリーンシートを用意し、そのグリーンシート上にAgを主体とする導電ペーストを印刷して、所望の電極パターンを形成し、それを適宜積層し、一体焼成させて構成される。

【0036】

この内部構造を積層順に従って説明する。まず、下層のグリーンシート11上には、グランド電極31がほぼ全面に形成されている。そして、側面に形成される端子電極81、83、87、89、91、93、95に接続するための接続部が設けられている。

【0037】

次に、電極パターンの印刷されていないダミーのグリーンシート12を積層する。その上のグリーンシート13には、1つのライン電極41が形成され、その上のグリーンシート14には、4つのライン電極42、43、44、45が形成され、その上のグリーンシート15には、4つのライン電極46、47、48、49が形成されている。その上に、2つのスルーホール電極(図中、十字の印を付けたものがスルーホール電極である、以下同様)が形成されたグリーンシート16を積層し、その上に、グランド電極32が形成されたグリーンシート17が積層される。

【0038】

この2つのグランド電極31、32に挟まれた領域に形成されたライン電極は適宜接続され、第1及び第2のスイッチ回路SW用の伝送線路を形成している。ライン電極41と42と46はスルーホール電極で接続され、等価回路の伝送線路LG1を構成し、ライン電極45と49はスルーホール電極で接続され、等価回路の伝送線路LG2を構成し、ライン電極43と47はスルーホール電極で接続され、等価回路の伝送線路LP1を構成し、ライン電極44と48はスルーホール電極で接続され、等価回路の伝送線路LP2を構成している。

【0039】

グリーンシート17の上に積層されるグリーンシート18には、コンデンサ用の電極61、62、63、64、65、66が形成されている。その上に積層されるグリーンシート19にもコンデンサ用の電極67、68、69が形成されている。その上に積層されるグリーンシート20には、コンデンサ電極70が形成されている。

【0040】

更にその上には、ライン電極50、51、52、53、54が形成されたグリーンシート21が積層され、その上に、ライン電極55、56、57、58、59が形成されたグリーンシート22が積層される。そして、最上部のグリーンシート23には、搭載素子接続用のランドが形成されている。

【0041】

上側のグランド電極32が形成されたグリーンシート17の上に積層されたグリーンシート18のコンデンサ用電極の61、62、63、64、66は、グランド電極32との間で容量を形成し、コンデンサ用電極61は、等価回路のCP3を、コンデンサ用電極62は、等価回路のCP4を、コンデンサ用電極63は、等価回路のCG4を、コンデンサ用電極64は、等価回路のCG3を、コンデンサ用電極66は、等価回路のCF3を構成している。

【0042】

またグリーンシート18、19、20に形成されたコンデンサ電極は互の間で容量を形成し、コンデンサ電極65と68の間で、等価回路のCF4を構成し、同様にコンデンサ電極61、62と67の間で、等価回路のCP7を構成し、コンデンサ電極69と70の間で、等価回路のCF1を構成し、コンデンサ電極68と70の間で、等価回路のCF2を構成している。このコンデンサ電極65では、コンデンサ電極68と対向して容量を形成するが、このとき、グランド電極32とは対向しないように、グランド電極32には、切り欠き部が形成されている。また、この切り欠き部を利用して、伝送線路に導通するスルーホール電極が形成されている。

【0043】

またグリーンシート21、22では、ライン電極52、59が等価回路のLF1を構成し、ライン電極54、58が等価回路のLF2を構成し、ライン電極53が等価回路のLF3を構成し、ライン電極51、57が等価回路のLG3を構成し、ライン電極55が等価回路のLP3を構成している。また、ライン電極50、56は配線用のラインである。また、ライン電極51、57とにより等価回路のLG3を構成しているが、このライン電極51、57とは一部対向するように形成され、その対向部分で等価回路のCG7を構成している。

【0044】

これらのグリーンシートを圧着し、一体焼成して積層体を得た。この積層体の側面に端子電極81、82、83、84、85、86、87、88、89、90、91、92、93、94、95、96を形成した。この外観図を図4に示す。

【0045】

この積層体の上に、ダイオードDG1、DG2、DP1、DP2、DP3、チップコンデンサCG1、CG6、CGP、CP6、チップ抵抗R3を搭載した。図3に、この搭載素子を搭載した様子を示す平面図を示す。また、図3に、この高周波スイッチモジュールの実装構成(各端子の接続構造)を合わせて示す。この図3で、GRDはグランド接続される端子であることを意味する。この実施例では、図2に示す等価回路のうち、CP2、CP5、CG2、CG5、R1、LG、R2、LP、CP7は、この実施例のチップ部品の搭載される回路上に形成される。

【0046】

この実施例によれば、第1及び第2のスイッチ回路の伝送線路を積層体内に形成する際に、グランド電極で挟まれた領域内に配置している。これにより、スイッチ回路と分波回路、ローパスフィルタ回路との干渉を防いでいる。そして、このグランド電極で挟まれた領域を積層体の下部に配置し、グランド電位を取り易くしている。そして、グランドとの間に接続されるコンデンサを構成する電極を、その上側のグランド電極に対向させて形成している。

【0047】

また、この実施例では、積層体の側面に各端子が形成され、面実装可能な構造となっている。側面の各端子は、それぞれANT端子、DCS系/PCS系のTX端子、GSM系TX端子、GSM系RX端子、DCS系RX端子、PCS系RX端子、グランド端子(GRD)又はコントロール端子(VC1、VC2、VC3)となっている。また、この積層体の各側面には、少なくとも1つのグランド端子が配置されている。

【0048】

また、この実施例の積層体の側面に形成された端子電極において、アンテナANT端子に対して積層体を実装面に垂直な面で2分した反対側に、DCS系/PCS系のTX端子、GSM系TX端子、GSM系RX端子、DCS系RX端子、PCS系RX端子がそれぞれ形成されている。さらに、そのTX端子群、RX端子群が形成されているANT端子の反対側において、その半分の片側に、送信TX端子群が形成され、もう一方の片側に受信RX端子群が形成されている。

【0049】

また、この実施例では、アンテナANT端子はグランド端子で挟まれ、送信TX端子もグランド端子で挟まれ、受信RX端子群もグランド端子で挟まれている。また、アンテナANT端子、送信TX端子、受信RX端子のそれぞれの間にはグランド端子が形成されている。また、VC1、VC2、VC3もグランド端子で挟まれている。

【0050】

本発明の実施例によれば、GSMシステムとDCS1800システムとPCSシステムの3つのバンドを扱うトリプルバンド携帯電話において、アンテナANTと、GSM系の送信系、受信系、DCS1800系の送信系、受信系、PCS系の送信系、受信系を切り換えることができる高周波スイッチモジュールを得ることができた。また、本発明は、上記実施例に限られるものでなく、通過帯域の異なる3つの送受信系を取り扱うトリプルバンド用高周波スイッチモジュールを得ることができるものである。

【0051】

また、DCS系の送信系とPCS系の送信も分ける回路とすると、スイッチ回路が2つ必要であるが、DCS系とPCS系の送信系の端子を共用とすることにより、スイッチ回路を2個で構成することができる。また、これにより、トリプルバンド用高周波スイッチモジュールのDCS系とPCS系の送信系の端子の前段のアンプの共用化も可能となる。

【0052】

本発明に係る別の実施例の等価回路図を図6に、平面図を図7に、積層体の内部構造図を図8に示す。この実施例は、上記した実施例と類似する部分が多く、異なる部分を説明する。

【0053】

まず、分波器部分は同一である。第3の送受信系(GSM)の第2のスイッチ回路部分もほぼ同一であり、異なるのは、伝送線路LG1がアースに接続されるのではなく、第1のスイッチ回路の伝送線路LP1とともに、コントロール回路VC3に接続されるところである。第1のスイッチ回路においては、ダイオードDP1、DP2、DP3(第1乃至第3のダイオード)の向きが逆となっている。そして、ダイオードDP2(第3のダイオード)とコンデンサCP6との間に、インダクタLDと抵抗R3の直列回路を経て、コントロール回路VC4が接続されている。

【0054】

積層構造では、グリーンシート11のグランド電極31の端子電極89への接続部を無くしている。グリーンシート15では、ライン電極46の引き出し端子が変更されている。グリーンシート17では、グランド電極32の端子電極89への接続部を無くしている。また、グリーンシート21では、ライン電極71が追加されている。ライン電極71は、配線用のラインである。グリーンシート22では、ライン電極71に接続されるスルーホールが追加されている。また、グリーンシート23では、ランド形状が適宜変更されている。

【0055】

そして、積層体上には、ダイオードDG1、DG2、DP1、DP2、DP3、チップコンデンサCG1、CG6、CGP、CP6を搭載した。図7に、この搭載素子を搭載した様子を示す平面図を示す。また、図7に、この高周波スイッチモジュールの実装構成(各端子の接続構造)を合わせて示す。この図7で、GRDはグランド接続される端子であることを意味する。この実施例では、図6に示す等価回路のうち、CP2、CP5、CG2、CG5、R1、LG、R2、LP、CP7、R3、LDは、この実施例のチップ部品の搭載される回路上に形成される。

【0056】

尚、この実施例のスイッチモジュールの各コントロール回路VC1、VC2、VC3、VC4の制御ロジックを表2に示す。これにより、各モードを変更する。

【0057】

【表2】

【0058】

この実施例においても、トリプルバンド用高周波スイッチモジュールとして、上記実施例と同様の効果を有している。

【0059】

【発明の効果】

本発明によれば、アンテナを共通とし、複数の送受信系の送信回路と受信回路を切り換えることが可能な高周波スイッチを小型に構成することが出来、例えばトリプルバンド携帯電話などにおいて、極めて有益となるトリプルバンド用高周波スイッチモジュールを提供することができる。本発明によれば、このトリプルバンド用高周波スイッチモジュールを、積層構造を用いることにより、小型に、しかもワンチップに構成できるものである。これにより、トリプルバンド携帯電話などにおいて、機器の小型化に有効なものとなる。

【図面の簡単な説明】

【図1】本発明に係る一実施例の回路ブロック図である。

【図2】本発明に係る一実施例の等価回路図である。

【図3】本発明に係る一実施例の平面図である。

【図4】本発明に係る一実施例の積層体の斜視図である。

【図5】本発明に係る一実施例の積層体の内部構造図である。

【図6】本発明に係る別の実施例の等価回路図である。

【図7】本発明に係る別の実施例の平面図である。

【図8】本発明に係る別の実施例の積層体の内部構造図である。

【符号の説明】

11、12、13、14、15、16、17、18、19、20、21、22、23 誘電体グリーンシート

31、32グランド電極

41、42、43、44、45、46、47、48、49、50、51、52、53、54、55、56、57、58、59、71 ライン電極

61、62、63、64、65、66、67、68、69、70 コンデンサ電極

81、82、83、84、85、86、87、88、89、90、91、92、93、94、95、96 端子電極

Claims (15)

- 第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、

前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置され、前記伝送線路を介して前記第1及び第2のダイオードと接続する第3のダイオードと、前記第1のダイオードと前記共通の送信回路との間に接続される他の伝送線路を備え、前記他の伝送線路と前記第1のダイオードとの間にはローパスフィルタ回路が配置されており、

アンテナ側回路と第2の送受信系の受信回路との間に配置された前記伝送線路は、誘電体層と電極パターンとの積層体内にライン電極として形成され、

該ライン電極に対して上側及び下側には、誘電体層を介してグランド電極が形成されていることを特徴とする高周波スイッチ。 - 前記第1乃至第3のダイオードが前記積層体に搭載されていることを特徴とする請求項1に記載の高周波スイッチ。

- 第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、

前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、

前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、

前記伝送線路は、誘電体層と電極パターンとの積層体内に、ライン電極として形成され、前記第1乃至第3のダイオードは前記積層体に搭載され、さらに、前記積層体にはローパスフィルタ回路用の電極パターンを有し、前記ライン電極の形成された誘電体層と前記第1乃至第3のダイオードが搭載された前記積層体の面との間に、グランド電極が形成された誘電体層が設けられ、前記ローパスフィルタ回路用の電極パターンと前記グランド電極とでコンデンサを構成したことを特徴とする高周波スイッチ。 - 第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、

前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、

前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、

前記伝送線路は、誘電体層と電極パターンとの積層体内に、ライン電極として形成され、

前記第1乃至第3のダイオードは前記積層体に搭載され、

前記伝送線路の一端は、スルーホール電極を介して前記第1及び第2のダイオードのア

ノード側と接続することを特徴とする高周波スイッチ。 - 前記ライン電極の形成された誘電体層と前記第1及び第2のダイオードが搭載された前記積層体の面との間に、グランド電極が形成された誘電体層が設けられており、前記グランド電極が形成された誘電体層に形成されたスルーホール電極を介して、前記第1及び第2のダイオードと前記伝送線路とが接続されていることを特徴とする請求項4に記載の高周波スイッチ。

- 第1及び第2の送受信系に共通の送信回路とアンテナ側回路との接続、前記アンテナ側回路と第1の送受信系の受信回路との接続、前記アンテナ側回路と第2の送受信系の受信回路との接続を切り換える高周波スイッチであって、

前記共通の送信回路とアンテナ側回路との間に配置された第1のダイオードと、前記アンテナ側回路と第1の送受信系の受信回路との間に配置された第2のダイオードと、前記アンテナ側回路と第2の送受信系の受信回路との間に配置された伝送線路と、前記伝送線路の第2の送受信系の受信回路側とアース側との間に配置された第3のダイオードを備え、

前記第3のダイオードは、前記伝送線路を介して前記第1及び第2のダイオードと接続し、

前記伝送線路は、誘電体層と電極パターンとの積層体内にライン電極で形成され、異なる誘電体層に形成されたライン電極の一端どうしをスルーホール電極で接続し積層方向に巻回させたことを特徴とする高周波スイッチ。 - 前記伝送線路の形成された誘電体層に対して上側及び下側には、誘電体層を介してグランド電極が形成されていることを特徴とする請求項6に記載の高周波スイッチ。

- 前記共通の送信回路側にローパスフィルタ回路を有し、前記ローパスフィルタ回路をライン電極、グランド電極、コンデンサ電極などの電極パターンで前記積層体に形成したことを特徴とする請求項4乃至7のいずれかに記載の高周波スイッチ。

- 前記第1乃至第3のダイオードは前記積層体に搭載され、前記第1のダイオードは、前記伝送線路を構成するライン電極と前記ローパスフィルタ回路を構成するライン電極とに、前記積層体に形成されたスルーホール電極を介して接続されることを特徴とする請求項8に記載の高周波スイッチ。

- 前記第1のダイオードには前記ローパスフィルタ回路を構成するライン電極を介して電圧が加えられることを特徴とする請求項9に記載の高周波スイッチ。

- 前記伝送線路の一端を前記第1及び第2のダイオードのカソード側に接続し、前記伝送線路の他端を前記第3のダイオードのアノード側に接続することを特徴とする請求項1乃至3、請求項6乃至10のいずれかに記載の高周波スイッチ。

- 前記伝送線路の一端を前記第1及び第2のダイオードのアノード側に接続し、前記伝送線路の他端を前記第3のダイオードのカソード側に接続することを特徴とする請求項1乃至10のいずれかに記載の高周波スイッチ。

- アンテナ側回路が分波回路であることを特徴とする請求項1乃至12のいずれかに記載

の高周波スイッチ。 - 前記分波回路はインダクタンス成分と容量成分で形成されたフィルタ回路を組み合わせて構成することを特徴とする請求項13に記載の高周波スイッチ。

- 請求項1乃至14のいずれかに記載の高周波スイッチをアンテナと送受信回路との間に配置したことを特徴とする携帯電話。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003191342A JP3642062B2 (ja) | 2003-07-03 | 2003-07-03 | 高周波スイッチ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003191342A JP3642062B2 (ja) | 2003-07-03 | 2003-07-03 | 高周波スイッチ |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP07323499A Division JP2002064301A (ja) | 1999-03-18 | 1999-03-18 | トリプルバンド用高周波スイッチモジュール |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004007756A JP2004007756A (ja) | 2004-01-08 |

| JP2004007756A5 JP2004007756A5 (ja) | 2004-10-28 |

| JP3642062B2 true JP3642062B2 (ja) | 2005-04-27 |

Family

ID=30438417

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003191342A Expired - Lifetime JP3642062B2 (ja) | 2003-07-03 | 2003-07-03 | 高周波スイッチ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3642062B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1873923A4 (en) | 2005-04-18 | 2013-12-04 | Murata Manufacturing Co | HIGH FREQUENCY MODULE |

| JP5168505B2 (ja) * | 2009-04-30 | 2013-03-21 | 株式会社村田製作所 | 高周波複合部品 |

| JP2011072013A (ja) * | 2010-11-15 | 2011-04-07 | Hitachi Metals Ltd | 高周波回路部品およびこれを用いた通信装置 |

-

2003

- 2003-07-03 JP JP2003191342A patent/JP3642062B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004007756A (ja) | 2004-01-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100503647B1 (ko) | 멀티밴드용 고주파 스위치 모듈 | |

| JP4257481B2 (ja) | 高周波スイッチモジュール | |

| JP2983016B2 (ja) | マルチバンド用高周波スイッチモジュール | |

| JP3903456B2 (ja) | マルチバンド用高周波スイッチモジュール | |

| JP3191213B2 (ja) | 高周波スイッチモジュール | |

| JPH11168303A (ja) | 高周波スイッチモジュール | |

| JP4120902B2 (ja) | マルチバンド用高周波スイッチモジュール | |

| JP3925771B2 (ja) | 高周波スイッチモジュール | |

| JP3642062B2 (ja) | 高周波スイッチ | |

| JP4247722B2 (ja) | 高周波スイッチモジュール | |

| JP3925804B2 (ja) | トリプルバンド用高周波スイッチモジュール | |

| JP3824230B2 (ja) | マルチバンド用高周波スイッチモジュール | |

| JP2002064400A (ja) | 高周波スイッチモジュール | |

| JP2000049651A (ja) | マルチバンド用高周波スイッチモジュール | |

| JP4135015B2 (ja) | 高周波スイッチモジュール | |

| JP4174779B2 (ja) | 高周波スイッチモジュール | |

| JP2004007756A5 (ja) | ||

| JP3550668B2 (ja) | 高周波スイッチモジュール | |

| JP3824229B2 (ja) | マルチバンド用高周波スイッチモジュール | |

| JP4565368B2 (ja) | 高周波スイッチモジュール | |

| JP3824231B2 (ja) | スイッチ回路 | |

| JP2002064401A (ja) | 高周波スイッチモジュール | |

| JP2005237019A (ja) | 高周波スイッチ | |

| JP2001352202A (ja) | 高周波スイッチモジュール | |

| JP4210861B2 (ja) | 高周波スイッチモジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20031027 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20031027 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20031027 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20040115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040130 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040323 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050104 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050117 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080204 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090204 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100204 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110204 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120204 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130204 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140204 Year of fee payment: 9 |

|

| EXPY | Cancellation because of completion of term |