JP3588018B2 - 信号分配器 - Google Patents

信号分配器 Download PDFInfo

- Publication number

- JP3588018B2 JP3588018B2 JP30584999A JP30584999A JP3588018B2 JP 3588018 B2 JP3588018 B2 JP 3588018B2 JP 30584999 A JP30584999 A JP 30584999A JP 30584999 A JP30584999 A JP 30584999A JP 3588018 B2 JP3588018 B2 JP 3588018B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- capacitor

- capacitors

- current

- predetermined

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Manipulation Of Pulses (AREA)

- Pulse Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、等しい振幅を有する所定の位相差の複数の信号を発生する信号分配器に関する。

【0002】

【従来の技術】

この種の信号分配器を使用している装置の一例として、図15に示すようなイメージリジェクションミキサがある。このようなミキサを使用することにより不要な周波数成分であるイメージ周波数成分を抑圧することができるが、このミキサにおいて使用されている従来の信号分配器は、位相差が90°でかつ同振幅の2つの信号を出力しているが、この2つの信号の位相差および振幅の誤差が大きいとイメージ抑圧効果が著しく低下する。

【0003】

このような信号分配器として、従来は図16に示すようなキャパシタと抵抗による回路が使用されている。この従来の信号分配器において、例えばキャパシタの値を12pFとし、抵抗の値を100Ωとした時の出力1および2の入力に対する振幅比および出力1および2の位相差を計算すると、図17に示すようになる。

【0004】

【発明が解決しようとする課題】

上述したように、図16に示す従来の信号分配器では、出力1および2の入力に対する振幅比および出力1および2の位相差は、図17に示すようになり、位相差90°かつ同振幅の正確な信号分配は、限られた狭い周波数範囲でしか行なうことができないという問題がある。

【0005】

本発明は、上記に鑑みてなされたもので、その目的とするところは、広い周波数帯域にわたって等しい振幅かつ所望の位相差の複数の信号を容易に発生することができる信号分配器を提供することにある。

【0006】

【課題を解決するための手段】

上記目的を達成するため、請求項1記載の本発明は、所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックと、前記キャパシタの各々に対して前記所定の電流を供給する電流源と、を具備し、該複数の基本ブロックは、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを要旨とする。

請求項1記載の本発明にあっては、所定の電流を供給されて充放電するキャパシタの電圧を所定の電圧と比較し、両電圧が所定の条件になったとき出力信号を発生する基本ブロックを複数設け、キャパシタの各々は電流源から所定の電流を供給されるので、この複数の基本ブロックにおいて各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて位相の異なる複数の出力信号が複数の基本ブロックから出力されるため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0007】

また、請求項2記載の本発明は、所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックと、前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方と、を具備し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを要旨とする。

請求項2記載の本発明にあっては、所定の電流を供給されて充放電するキャパシタの電圧を所定の電圧と比較し、両電圧が所定の条件になったとき出力信号を発生する基本ブロックを複数設け、1つまたは複数の可変容量キャパシタの容量を可変することができる可変容量キャパシタおよび1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有するため、可変容量キャパシタおよび電流可変手段の少なくとも一方の値を任意の値に設定することにより位相差を任意の値に設定することができ、この複数の基本ブロックにおいて各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて位相の異なる複数の出力信号が複数の基本ブロックから出力されるため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0008】

また、請求項3記載の本発明は、所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックで構成される信号分配回路を複数並列に設け、この並列に設けられた複数の信号分配回路を順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを要旨とする。

【0009】

請求項3記載の本発明にあっては、所定の電流を供給されて充放電するキャパシタの電圧を所定の電圧と比較し、両電圧が所定の条件になったとき出力信号を各々が発生する複数の基本ブロックからなる信号分配回路を複数並列に設け、この並列に設けられた複数の信号分配回路を順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0010】

また、請求項4記載の本発明は、請求項3記載の発明において、前記キャパシタの各々に対して前記所定の電流を供給する電流源を有することを要旨とする。

【0011】

請求項4記載の本発明にあっては、キャパシタの各々は電流源から所定の電流を供給される。

【0012】

請求項5記載の本発明は、請求項3記載の発明において、前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有することを要旨とする。

【0013】

請求項5記載の本発明にあっては、1つまたは複数の可変容量キャパシタの容量を可変することができる可変容量キャパシタおよび1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有するため、可変容量キャパシタおよび電流可変手段の少なくとも一方の値を任意の値に設定することにより位相差を任意の値に設定することができる。

【0014】

また、請求項6記載の本発明は、所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器と、前記複数のキャパシタに所定の複数の電流をそれぞれ供給する複数の電流源と、を有し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを要旨とする。

請求項6記載の本発明にあっては、複数のキャパシタに対して複数の電流源から異なる所定の複数の電流をそれぞれ供給し、所定の電流を供給されて充放電する複数のキャパシタのそれぞれの電圧を所定の電圧と複数の電圧比較器でそれぞれ比較し、それぞれの両電圧が所定の条件になったとき複数の出力信号を発生する場合において各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0015】

また、請求項7記載の本発明は、所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器と、前記複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方と、を有し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生すること要旨とする。

請求項7記載の本発明にあっては、所定の電流を供給されて充放電する複数のキャパシタのそれぞれの電圧を所定の電圧と複数の電圧比較器でそれぞれ比較し、それぞれの両電圧が所定の条件になったとき複数の出力信号を発生する場合において各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができ、複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタでおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有するため、可変容量キャパシタおよび電流可変手段のそれぞれの値を任意の値に設定することにより位相差を任意の値に設定することができる。

【0016】

更に、請求項8記載の本発明は、所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器とを有する基本ブロックを複数設け、この複数の基本ブロックを順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを要旨とする。

【0017】

請求項8記載の本発明にあっては、所定の電流を供給されて充放電する複数のキャパシタのそれぞれの電圧を所定の電圧と比較し、それぞれの両電圧が所定の条件になったとき複数の出力信号を発生する基本ブロックを複数設け、この複数の基本ブロックを順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するため、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0018】

請求項9記載の本発明は、請求項8記載の発明において、前記複数のキャパシタに所定の複数の電流をそれぞれ供給する複数の電流源を有することを要旨とする。

【0019】

請求項9記載の本発明にあっては、複数のキャパシタに対して複数の電流源から異なる所定の複数の電流をそれぞれ供給する。

【0020】

また、請求項10記載の本発明は、請求項8記載の発明において、前記複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタでおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有することを要旨とする。

【0021】

請求項10記載の本発明にあっては、複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタでおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有するため、可変容量キャパシタおよび電流可変手段のそれぞれの値を任意の値に設定することにより位相差を任意の値に設定することができる。

【0022】

更に、請求項11記載の本発明は、請求項1乃至10のいずれかに記載の発明において、前記所望の位相差の複数の出力信号を正弦波信号に変換する波形変換手段を有することを要旨とする。

【0023】

請求項11記載の本発明にあっては、所望の位相差の複数の出力信号を正弦波信号に変換して出力する。

【0024】

請求項12記載の本発明は、請求項1乃至11のいずれかに記載の発明において、前記電圧発生手段が、充放電過程において前記所定の電圧を発生し得るように所定の電流を供給されるキャパシタを有して構成されることを要旨とする。

【0025】

請求項12記載の本発明にあっては、電圧発生手段からの所定の電圧は所定の電流を供給されるキャパシタからの電圧である。

【0026】

また、請求項13記載の本発明は、請求項12記載の発明において、前記キャパシタに対して所定の電流を供給する電流源を有することを要旨とする。

【0027】

請求項13記載の本発明にあっては、キャパシタは電流源から所定の電流を供給される。

【0028】

【発明の実施の形態】

以下、図面を用いて本発明の実施の形態を説明する。図1は、本発明の第1の実施形態に係る信号分配器の構成を示す回路図である。同図に示す信号分配器は、同じ回路構成の複数の基本ブロックB1,B2で構成され、各基本ブロックB1(B2)は、一端が電源電圧VDDに供給され、容量値1を有するキャパシタC1(C3)、このキャパシタC1(C3)の電圧を放電するように該キャパシタの両端を接続するスイッチS1(S3)、電流値1の電流をキャパシタC1(C3)に供給するようにキャパシタC1(C3)の他端とグランドとの間に接続された電流源K1(K3)、一端が電源電圧VDDに接続され、容量値a1(a2)を有するキャパシタC2(C4)、このキャパシタC2(C4)の電圧を放電するように該キャパシタの両端を接続するスイッチS2(S4)、電流値b1(b2)の電流をキャパシタC2(C4)に供給するようにキャパシタC2(C4)の他端とグランドとの間に接続された電流源K2(K4)、キャパシタC1(C3)と電流源K1(K3)との接続点の電圧VR1(VR2)とキャパシタC2(C4)と電流源K2(K4)との接続点の電圧VT1(VT2)とを比較し、両電圧が等しくなったときに出力電圧V1(V2)を発生する電圧比較器H1(H2)から構成されている。なお、この構成の記載でカッコ内の符号は基本ブロックB2の構成要素の符号である。

【0029】

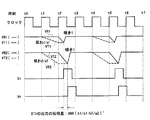

次に、以上のように構成される信号分配器の作用について図2に示すタイミング図を参照して説明する。

【0030】

まず、時刻t1以前ではすべてのスイッチS1〜S4はオン状態にあり、これによりすべてのキャパシタC1〜C4は十分に放電されている。このような状態において、時刻t1で基本ブロックB1のスイッチS1をオフとし、電流源K1を動作させ、これによりキャパシタC1を電流値1の割合で時刻t2まで充電すると同時に、基本ブロックB2のスイッチS3もオフとし、電流源K3も動作させ、これによりキャパシタC3を電流1の割合で時刻t2まで充電する。

【0031】

そして、時刻t2になると、電流源K1および電流源K3をオフとする。この結果、キャパシタC1と電流源K1との接続点の電圧VR1およびキャパシタC3と電流源K3との接続点の電圧VR2は、時刻t1までは電源電圧VDDに等しい電圧であるが、時刻t1から時刻t2の間は図2に示すように傾き1の割合で低下し、時刻t2からは一定の電圧で保持される。

【0032】

次に、時刻t2において、基本ブロックB1のスイッチS2をオフとし、電流源K2を動作させ、これによりキャパシタC2を電流値b1の割合で充電すると同時に、基本ブロックB2のスイッチS4もオフとし、電流源K4も動作させ、これによりキャパシタC4を電流値b2の割合で充電する。

【0033】

この結果、キャパシタC2と電流源K2との接続点の電圧VT1およびキャパシタC4と電流源K4との接続点の電圧VT2は、時刻t2までは電源電圧VDDに等しい電圧であるが、時刻t2からは図2に示すように容量a1,a2のキャパシタC2,C4を電流値b1,b2の割合で充電するため、両電圧VT1,VT2はそれぞれ傾きb1/a1,b2/a2の割合で低下していく。

【0034】

このように低下していく電圧VT1,VT2は、基本ブロックB1の電圧比較器H1および基本ブロックB2の電圧比較器H2に供給されて、電圧VR1,VR2とそれぞれ比較され、この比較の結果、電圧VT1,VT2がそれぞれ電圧VR1,VR2に一致すると、電圧比較器H1,H2は、それぞれ出力電圧V1,V2を発生する。以上の動作を繰り返し行なうことにより、位相差360|a1/b1−a2/b2|°の2つの出力信号V1,V2を発生することができる。

【0035】

このように出力電圧V1,V2が出力された時点において、スイッチS1〜S4をオンとして、キャパシタC1〜C4の放電を行なってもよい。または、電流源K2,K4をこの時点でオフとしてもよい。この場合は、次のクロックが来るまで電圧比較器H1,H2から信号を出力させないようにすることが必要である。また、この時点でキャパシタC2,C4の充電を継続してもよい。この場合、時刻t3から放電を行なう。なお、図2に示す動作では、キャパシタC2,C4の充電を継続し、時刻t3でスイッチS1〜S4をオンとして、キャパシタC1〜C4を放電させる場合について図示している。

【0036】

なお、図1に示す実施形態では、基本ブロックとして、2つの基本ブロックB1,B2を有する場合について説明したが、この基本ブロックは2つに限定されるものでなく、任意の複数の基本ブロックを使用することができるものである。

【0037】

図3は、図1に示した回路構成の信号分配器において、キャパシタC1およびC3を最初に充電する代わりに、キャパシタC2およびC4の充電を最初に行ない、その後でキャパシタC1およびC3の充電を行ない、これにより電圧比較器H1,H2から出力電圧V1,V2を発生し、この時点で各キャパシタC1〜C4の放電を行なった場合の各ブロックの動作を示すタイミング図である。このように動作させた場合において、電圧比較器H1,H2から出力される出力電圧V1,V2の位相差は、360|b1/a1−b2/a2|°となる。

【0038】

なお、上述した各動作において、各電流源をオフとする場合に、電流源の動作は継続したまま、該電流源をキャパシタから切り離すように構成してもよい。また、上記回路構成において、電源電圧VDDの代わりにグランドを接続し、グランドの代わりに負の電源電圧を接続するように構成してもよい。更に、上記各説明において、放電を行なった箇所で充電を行ない、また充電を行なった箇所で放電を行なうように動作させても同様の効果が得られるものである。

【0039】

図4は、図1に示した信号分配器に使用されている電流源K2等の代わりに使用し得る電流源の構成を示す回路図である。図4に示す電流源は、複数の電流源Ka,Kb,Kc,…,Kn、およびこれら複数の電流源Ka,Kb,Kc,…,Knのそれぞれに直列に接続された複数のスイッチSa,Sb,Sc,…,Snから構成されている。このように構成される電流源では、複数のスイッチSa,Sb,Sc,…,Snのうちのいくつかをオンすることにより、図4の電流源から出力される全体の電流値を可変することができる。上述したように、電圧比較器H1,H2から出力される出力電圧V1,V2の位相差は、キャパシタの容量と電流源からの電流値とによって変化するものであるため、図4のよううに電流源からの電流値を可変し得るように構成することにより出力電圧V1,V2の位相差を選択的に可変することができる。

【0040】

図5は、本発明の第2の実施形態に係る信号分配器の回路構成を示す回路図である。同図に示す信号分配器は、図1に示した複数の基本ブロックB1,B2からなる信号分配器を3つ並列に設けて、順番に動作させ、これにより所望の位相差の2つの出力電圧V0,V1を発生するように構成したものである。

【0041】

図5に示す信号分配器は、図1の基本ブロックB1と基本ブロックB2からなる第1の信号分配器と、図1の基本ブロックB1に相当する基本ブロックB3と図1の基本ブロックB2に相当する基本ブロックB4からなる第2の信号分配器と、図1の基本ブロックB1に相当する基本ブロックB5と図1の基本ブロックB2に相当する基本ブロックB6からなる第3の信号分配器とを並列に接続して構成されるとともに、基本ブロックB1、基本ブロックB3、基本ブロックB5の出力信号が入力され、出力電圧V0を出力するオア回路OR1および基本ブロックB2、基本ブロックB4、基本ブロックB6の出力信号が入力され、出力電圧V1を出力するオア回路OR2を有する。

【0042】

なお、この実施形態では、各基本ブロックの出力はオア回路で接続されているが、本発明はこれに限定されるものでなく、直接接続してもよいし、または他の形態の信号合成手段で接続してもよい。また、本実施形態では、各信号分配器を構成する基本ブロックは2つのみであり、またこのように構成される3つの信号分配器のみが使用されているが、本発明はこれに限定されるものでなく、各信号分配器を任意の複数の基本ブロックで構成し、また信号分配器を任意の複数の信号分配器で構成してもよいものである。

【0043】

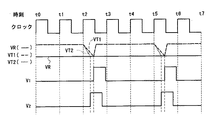

次に、図6に示すタイミング図を参照して、上述したように構成される図5に示す実施形態の信号分配器の動作について説明する。

【0044】

図5のように構成される信号分配器の各基本ブロックを図2で説明したように動作させることにより、図6に示すように、時刻t2から時刻t3の間では基本ブロックB1およびB2から位相差360|a1/b1−a2/b2|°の2つの出力信号V0,V1を発生し、時刻t3から時刻tb4の間では基本ブロックB3およびB4から位相差360|a1/b1−a2/b2|°の2つの出力信号V0,V1を発生し、また時刻t4から時刻t5の間では基本ブロックB5およびB6から位相差360|a1/b1−a2/b2|°の2つの出力信号V0,V1を発生する。

【0045】

そして、基本ブロックB1,B3,B5からの出力信号V0は、オア回路OR1に入力され、基本ブロックB2,B4,B6からの出力信号V1は、オア回路OR2に入力される。従って、オア回路OR1およびオア回路OR2からは、時刻t2から時刻t3の間、時刻t3から時刻t4の間、時刻t4から時刻t5の間にそれぞれ位相差360|a1/b1−a2/b2|°の出力信号V0,V1が出力される。時刻t5以降は、上述した時刻t2から時刻t5の動作を繰り返し行なう。このように、本実施形態の信号分配器からは、クロックと同じ周期の位相差360|a1/b1−a2/b2|°の出力信号V0,V1を発生することができる。

【0046】

図7は、本発明の第3の実施形態に係る信号分配器の回路構成を示す回路図である。同図に示す信号分配器は、一端が電源電圧VDDに接続され、容量値1を有する基準キャパシタC10、このキャパシタC10の電圧を放電するように該キャパシタの両端を接続するスイッチS10、電流値1の電流をキャパシタC10に供給するようにキャパシタC10の他端とグランドとの間に接続された電流源K10からなり、キャパシタC10と電流源K10との接続点から電圧VRを発生する基準直列回路と、一端が電源電圧VDDに接続され、容量値a1を有するキャパシタC11、このキャパシタC11の電圧を放電するように該キャパシタの両端を接続するスイッチS11、電流値b1の電流をキャパシタC11に供給するようにキャパシタC11の他端とグランドとの間に接続された電流源K11からなり、キャパシタC11と電流源K11との接続点から電圧VT1を発生する第1の直列回路と、一端が電源電圧VDDに接続され、容量値a2を有するキャパシタC12、このキャパシタC12の電圧を放電するように該キャパシタの両端を接続するスイッチS12、電流値b2の電流をキャパシタC12に供給するようにキャパシタC12の他端とグランドとの間に接続された電流源K12からなり、キャパシタC12と電流源K12との接続点から電圧VT2を発生する第2の直列回路と、一端が電源電圧VDDに接続され、容量値a3を有するキャパシタC13、このキャパシタC13の電圧を放電するように該キャパシタの両端を接続するスイッチS13、電流値b3の電流をキャパシタC13に供給するようにキャパシタC13の他端とグランドとの間に接続された電流源K13からなり、キャパシタC13と電流源K13との接続点から電圧VT3を発生する第3の直列回路と、前記基準直列回路から発生する電圧VRと第1の直列回路から発生する電圧VT1とを比較し、両電圧が等しくなったときに出力電圧V1を発生する電圧比較器H11とを、基準直列回路から発生する電圧VRと第2の直列回路から発生する電圧VT2とを比較し、両電圧が等しくなったときに出力電圧V2を発生する電圧比較器H12と、基準直列回路から発生する電圧VRと第3の直列回路から発生する電圧VT3とを比較し、両電圧が等しくなったときに出力電圧V3を発生する電圧比較器H13とから構成されている。

【0047】

次に、図8に示すタイミング図を参照して、図7に示す実施形態の信号分配器の作用を説明する。

【0048】

時刻t1以前にはスイッチS10〜S13はすべてオンの状態に設定し、これによりキャパシタC10からC13は十分に放電しておく。そして、時刻t1において、スイッチS10をオフとし、電流源K10を動作させ、これにより電流値1の割合で時刻t2までキャパシタC10を充電する。

【0049】

次に、時刻t2において電流源K10をオフにする。この結果、基準直列回路からの電圧VRは、図8に示すように、時刻t1までは電源電圧VDDに等しい電圧となっていたが、時刻t1から時刻t2までは傾き1の割合で低下し、時刻t2からは一定の電圧に保持される。

【0050】

次に、時刻t2において、スイッチS11からスイッチS13をオフとし、電流源K11から電流源K13を動作させ、それぞれ電流値b1,b2,b3の割合でキャパシタC11からC13を充電する。この結果、第1、第2および第3の直列回路からそれぞれ出力される電圧VT1,VT2,VT3は、時刻t2までは電源電圧VDDに等しい電圧となっていたが、時刻t2からはそれぞれ容量値a1,a2,a3のキャパシタC11,C12,C13を電流値b1,b2,b3の割合で充電するため、電圧VT1,VT2,VT3は、それぞれ傾きb1/a1,b2/a2,b3/a3の割合で図8に示すように低下していく。

【0051】

このように低下していく第1、第2および第3の直列回路からの電圧VT1,VT2,VT3は、それぞれ電圧比較器H11,H12,H13において基準直列からの電圧VRと比較され、電圧VT1,VT2,VT3が電圧VRに一致した時刻において電圧比較器H11,H12,H13からそれぞれ出力電圧V1,V2,V3が発生する。以上の動作を繰り返し行なうことにより、図8のように所望の位相差の3つの出力信号を発生することができる。

【0052】

なお、上述したように、出力電圧V1,V2,V3が出力された時点において、スイッチS10〜S13をオンとして、キャパシタC10〜C13を放電してもよい。または、この時点において、電流源K11〜K13をオフとしてもよい。この場合、次のクロックが来るまで電圧比較器H11〜H13から信号を出力させないようにすることが必要である。また、この時点において、キャパシタC11からC13の充電を継続してもよい。この場合には、時刻t3からキャパシタC10からC13の放電を行なう。図8に示す例では、出力電圧V1,V2,V3が発生した時点でキャパシタC10からC13の放電を行なった場合を示している。

【0053】

また、上述した動作において、電流源をオフとするところで、電流源を動作させたまま、キャパシタとの接続を切り離すようにしてもよい。また、上記回路構成において、電源電圧VDDの代わりにグランドを接続し、グランドの代わりに負の電源電圧を接続するように構成してもよい。更に、上記各説明において、放電を行なった箇所で充電を行ない、また充電を行なった箇所で放電を行なうように動作させても同様の効果が得られるものである。

【0054】

上述した図7に示す実施形態では、電圧VT1,VT2,VT3をそれぞれ発生する第1、第2および第3の直列回路および電圧比較器H11,H12,H13は、それぞれ3個の場合の構成について示しているが、本発明ではこれらの回路は3つに限定されるものでなく、任意の複数個でもよいものである。

【0055】

図9は、本発明の第4の実施形態に係る信号分配器の回路構成を示す回路図である。図9に示す実施形態の信号分配器は、図7に示した信号分配器を基本ブロックとし、この基本ブロックを2つ設けて構成したものであり、基本ブロックとしてB10およびB20を有するが、各基本ブロックB10(B20)は、図7の信号分配器において電圧VT3を発生するキャパシタC13、スイッチS13、電流源K13からなる第3の直列回路および電圧比較器H13を除去し、1つの基準直列回路、第1および第2の2つの直列回路、および2つの電圧比較器H11(H21),H12(H22)で構成したものである。なお、この構成の記載でカッコ内の符号は基本ブロックB2の構成要素の符号である。

【0056】

そして、基本ブロックB10の電圧比較器H11からの出力電圧V11と基本ブロックB20の電圧比較器H21からの出力電圧V21は、オア回路OR11に入力され、オア回路OR11から出力電圧V1として出力され、また基本ブロックB10の電圧比較器H12からの出力電圧V12と基本ブロックB20の電圧比較器H22からの出力電圧V22は、オア回路OR12に入力され、オア回路OR12から出力電圧V2として出力されている。

【0057】

なお、図9に示す実施形態の信号分配器は、基本ブロックの数が2個であり、また各基本ブロック内の電圧VTを発生する直列回路および電圧比較器が2個のみであるが、本発明はこれに限定されるものでなく、基本ブロックおよび各基本ブロック内の電圧VTを発生する直列回路および電圧比較器は任意の複数個を有することができるものである。

【0058】

このように構成される図9の実施形態の信号分配器の動作は、図10のタイミング図に示すとおりである。同図に示すように、まず、基本ブロックB10において第2の直列回路および第1の直列回路からそれぞれ出力される電圧VT2,VT1がこの記載順に基準直列回路からの電圧VR1に等しくなると、電圧比較器H12,H11から順に出力される電圧がそれぞれオア回路OR11,OR12を介して出力電圧V1,V2としてそれぞれ出力される。それから、基本ブロックB20において第2の直列回路および第1の直列回路からそれぞれ出力される電圧VT4,VT3がこの記載順に基準直列回路からの電圧VR2に等しくなると、電圧比較器H21,H22から順に出力される電圧がそれぞれオア回路OR11,OR12を介して出力電圧V1,V2としてそれぞれ出力される。以上の動作を繰り返し行なうことにより、所望の位相差の2つの信号が順次発生することになる。

【0059】

図11は、本発明の第5の実施形態に係る信号分配器の構成を示す回路図である。同図に示す実施形態の信号分配器は、図9に示した実施形態においてオア回路OR11,OR12の出力に波形変換手段を構成するローパスフィルタ(LPF)L1,L2を接続し、このローパスフィルタL1,L2によりオア回路OR11,OR12から出力される信号V1,V2を正弦波信号V3,V4に変換して出力するように構成した点が異なるものであり、その他の構成および作用は同じである。

【0060】

図12は、図11に示した信号分配器の各部の信号波形を示す図であるが、同図に示すようにローパスフィルタL1,L2からの信号V3,V4は、所望の位相差の2つの正弦波信号として出力されている。なお、図11に示すように、ローパスフィルタを出力に接続して、出力信号を正弦波信号に変換する方法は、図11に示したように図9の実施形態に適用し得るのみでなく、本発明の他の実施形態のすべてに適用し得るものである。

【0061】

図13は、本発明の第6の実施形態に係る信号分配器の構成を示す回路図である。同図に示す信号分配器は、図7の信号分配器においてキャパシタC10、スイッチS10、電流源K10からなる基準直列回路を削除し、その代わりに外部からの直流電圧VRを使用するとともに、電圧VT3を発生するキャパシタC13は、スイッチS13、電流源K13からなる第3の直列回路および電圧比較器H13を除去し、1つの直流電圧VR、第1および第2の2つの直列回路、および2つの電圧比較器H11(H21),H12(H22)で構成したものである。すなわち、直流電圧VRは、キャパシタC10、スイッチS10、電流源K10からなる基準直列回路で電圧を発生する代わりに外部からの電圧VRを直接供給するようにしたものである。

【0062】

次に、図14に示すタイミング図を参照して、図13に示す実施形態の信号分配器の作用を説明する。

【0063】

時刻t2以前にはスイッチS11およびS12をオフとし、キャパシタC11,C12を十分に放電しておく。そして、時刻t2においてスイッチS11,S12をオフとし、電流源K11,K12を動作させ、これによりキャパシタC11,C12をそれぞれ電流値b1,b2の割合で充電する。この結果、電圧比較器H11,H12にそれぞれ入力される第1の直列回路からの電圧VT1および第2の直列回路からの電圧VT2は、図14に示すように、時刻t2までは電源電圧VDDと等しい電圧になっているが、時刻t2からはそれぞれ容量値a1,a2のキャパシタC11,C12を電流値b1,b2の割合で充電するため、傾きb1/a1,b2/a2の割合でそれぞれ低下していく。そして、これらの電圧VT1,VT2は電圧比較器H11,H12で電圧VRとそれぞれ比較され、電圧VT1,VT2がそれぞれ外部からの電圧VRに一致すると、電圧比較器H11,H12から出力電圧V1,V2がそれぞれ発生する。以上の動作を繰り返すことにより所望の位相差の2つの出力電圧V1,V2を得ることができる。

【0064】

なお、上述したように、出力電圧V1,V2が発生した時点において、スイッチS11,S12をオンとしてキャパシタC11,C12の放電を行なってもよいし、または電流源K11,K12をこの時点でオフとしてもよい。この場合は、次のクロックが来るまで電圧比較器H11,H12から信号を出力させないようにしておく必要がある。また、この時点でキャパシタC11,C12の充電を継続してもよい。この場合は、時刻t3からキャパシタC11,C12の放電を行なう。図14に示す例では、出力電圧V1,V2が発生した時点でキャパシタC11,C12の放電を行なった場合を図示している。

【0065】

なお、図13に示すように、外部からの電圧VRを利用する方法は、図7の実施形態に対して適用しているが、本発明はこれに限定されるものでなく、図1、図5、図9、図11を含むすべての実施形態に適用し得るものである。

【0066】

また、上述した各実施形態では、複数のキャパシタの各々の容量値および複数の電流源の各々の電流値を固定しているように説説明したが、本発明はこれに限定されるものでなく、複数のキャパシタの容量値および複数の電流源の電流値の1つまたは複数の値を可変にし、これにより所望の複数の位相差の出力電圧を発生させるようにしてもよいものである。

【0067】

また、上記各実施形態では、出力信号の振幅については特に説明していないが、振幅の等しい出力信号を出力するためには、例えばCMOSからなるコンパレータなどの電圧比較手段を用いて容易に実現することができるものである。

【0068】

【発明の効果】

以上説明したように、本発明によれば、所定の電流を供給されて充放電するキャパシタの電圧を所定の電圧と比較し、両電圧が所定の条件になったとき出力信号を発生する基本ブロックを複数設け、この複数の基本ブロックにおいて各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて位相の異なる複数の出力信号が複数の基本ブロックから出力されるので、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0069】

また、本発明によれば、所定の電流を供給されて充放電するキャパシタの電圧を所定の電圧と比較し、両電圧が所定の条件になったとき出力信号を各々が発生する複数の基本ブロックからなる信号分配回路を複数並列に設け、この並列に設けられた複数の信号分配回路を順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するので、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0070】

更に、本発明によれば、所定の電流を供給されて充放電する複数のキャパシタのそれぞれの電圧を所定の電圧と複数の電圧比較器でそれぞれ比較し、それぞれの両電圧が所定の条件になったとき複数の出力信号を発生する場合において各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するので、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【0071】

本発明によれば、所定の電流を供給されて充放電する複数のキャパシタのそれぞれの電圧を所定の電圧と比較し、それぞれの両電圧が所定の条件になったとき複数の出力信号を発生する基本ブロックを複数設け、この複数の基本ブロックを順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生するので、周波数による位相の変動要因がなく、広い周波数帯域にわたって所望の位相差でかつ等しい出力レベルの信号を得ることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る信号分配器の構成を示す回路図である。

【図2】図1に示す実施形態の信号分配器の作用を示すタイミング図である。

【図3】図1に示した回路構成の信号分配器においてキャパシタの充電順序を変更した場合の動作を示すタイミング図である。

【図4】図1に示した信号分配器に使用されている電流源の代わりに使用し得る電流源の構成を示す回路図である。

【図5】本発明の第2の実施形態に係る信号分配器の回路構成を示す回路図である。

【図6】図5に示す第2の実施形態の信号分配器の作用を示すタイミング図である。

【図7】本発明の第3の実施形態に係る信号分配器の回路構成を示す回路図である。

【図8】図7に示す第3の実施形態の信号分配器の作用を示すタイミング図である。

【図9】本発明の第4の実施形態に係る信号分配器の回路構成を示す回路図である。

【図10】図9に示す第4の実施形態の信号分配器の動作を示すタイミング図である。

【図11】本発明の第5の実施形態に係る信号分配器の構成を示す回路図である。

【図12】図11に示す第5の実施形態の信号分配器の動作を示すタイミング図である。

【図13】本発明の第6の実施形態に係る信号分配器の構成を示す回路図である。

【図14】図13に示す第6の実施形態の信号分配器の作用を示すタイミング図である。

【図15】従来の信号分配器を使用しているイメージリジェクションミキサの構成を示す図である。

【図16】図15に示すイメージリジェクションミキサに使用されている従来の信号分配器の構成を示す回路図である。

【図17】図16に示す従来の信号分配器の出力特性を示すグラフである。

【符号の説明】

B1−B6,B10,B20 基本ブロック

C1−C13 キャパシタ

H1−H6,H11−H22 電圧比較器

K1−K13 電流源

L1,L2 ローパスフィルタ

S1−S13 スイッチ

Claims (13)

- 所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックと、前記キャパシタの各々に対して前記所定の電流を供給する電流源と、を具備し、該複数の基本ブロックは、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックと、前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方と、を具備し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 所定の電圧を発生する電圧発生手段と、所定の電流を供給されるキャパシタと、該キャパシタの電圧を放電するスイッチと、前記所定の電圧および前記キャパシタの電圧を比較し、両電圧が所定の条件になったとき出力信号を発生する電圧比較器とを各々が有する複数の基本ブロックで構成される信号分配回路を複数並列に設け、この並列に設けられた複数の信号分配回路を順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 前記キャパシタの各々に対して前記所定の電流を供給する電流源を有することを特徴とする請求項3記載の信号分配器。

- 前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数の基本ブロックの複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有することを特徴とする請求項3記載の信号分配器。

- 所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器と、前記複数のキャパシタに所定の複数の電流をそれぞれ供給する複数の電流源と、を有し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器と、前記複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方と、を有し、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 所定の電圧を発生する電圧発生手段と、各々が所定の複数の電流を供給される複数のキャパシタと、該複数のキャパシタの電圧を放電するスイッチと、各々が前記所定の電圧と前記複数のキャパシタの各々の電圧とを比較し、両電圧が所定の条件になったとき出力信号を発生する複数の電圧比較器とを有する基本ブロックを複数設け、この複数の基本ブロックを順番に動作させ、各キャパシタに供給される電流の大きさおよび各キャパシタの容量に応じて所望の位相差の複数の出力信号を発生することを特徴とする信号分配器。

- 前記複数のキャパシタに所定の複数の電流をそれぞれ供給する複数の電流源を有することを特徴とする請求項8記載の信号分配器。

- 前記複数のキャパシタのうちの1つまたは複数のキャパシタの容量を可変することができる可変容量キャパシタおよび前記複数のキャパシタのうちの1つまたは複数のキャパシタに供給する電流を可変し得る電流可変手段の少なくとも一方を有することを特徴とする請求項8記載の信号分配器。

- 前記所望の位相差の複数の出力信号を正弦波信号に変換する波形変換手段を有することを特徴とする請求項1乃至10のいずれかに記載の信号分配器。

- 前記電圧発生手段は、充放電過程において前記所定の電圧を発生し得るように所定の電流を供給されるキャパシタを有して構成されることを特徴とする請求項1乃至11のいずれかに記載の信号分配器。

- 前記キャパシタに対して所定の電流を給する電流源を有することを特徴とする請求項12記載の信号分配器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP30584999A JP3588018B2 (ja) | 1999-10-27 | 1999-10-27 | 信号分配器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP30584999A JP3588018B2 (ja) | 1999-10-27 | 1999-10-27 | 信号分配器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001127604A JP2001127604A (ja) | 2001-05-11 |

| JP3588018B2 true JP3588018B2 (ja) | 2004-11-10 |

Family

ID=17950113

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP30584999A Expired - Fee Related JP3588018B2 (ja) | 1999-10-27 | 1999-10-27 | 信号分配器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3588018B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100861919B1 (ko) | 2006-07-18 | 2008-10-09 | 삼성전자주식회사 | 다 위상 신호 발생기 및 그 방법 |

-

1999

- 1999-10-27 JP JP30584999A patent/JP3588018B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001127604A (ja) | 2001-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3001916B2 (ja) | アナログ信号波形発生装置 | |

| JPS6412420B2 (ja) | ||

| US9008251B2 (en) | Adaptive phase-shifted synchronization clock generation circuit and method for generating phase-shifted synchronization clock | |

| JP2011061839A (ja) | 精密三角波形生成器 | |

| GB2618498A (en) | DC voltage converters | |

| JP2011102798A (ja) | 試験装置および電子デバイス | |

| JP2011166745A (ja) | 出力装置および試験装置 | |

| JP3923150B2 (ja) | 周波数シンセサイザ | |

| CN115735332A (zh) | 用于产生振荡器信号的振荡器电路、设备和方法 | |

| US7679543B2 (en) | Current sampling mixer with harmonic rejection | |

| US8344794B2 (en) | Signal monitoring systems | |

| EP1332558B1 (en) | Method and apparatus for analog-to-digital conversion | |

| JPH04152715A (ja) | ディジタル・アナログ変換器 | |

| JP3588018B2 (ja) | 信号分配器 | |

| CN106289333B (zh) | 电容充放电控制模块以及电流频率转换电路 | |

| CN101331682B (zh) | 采样滤波器设备 | |

| JP2004282352A (ja) | 鋸波発生回路 | |

| US6259311B1 (en) | Method and apparatus for tuning filters | |

| US20110221503A1 (en) | Semiconductor integrated circuit including constant adjusting circuit | |

| GB2427085A (en) | Variable signal delaying circuit, quadrature frequency converter and radio frequency tuner | |

| JP3588019B2 (ja) | 移相器 | |

| JP2006311144A (ja) | デジタルアナログ変換器、およびそれを用いた逐次比較型アナログデジタル変換器 | |

| US9100036B2 (en) | Receiving device and data interpolation processing method | |

| JP3331941B2 (ja) | タイム・インターリーブa/d変換装置 | |

| CN100588122C (zh) | 脉冲发生器、光盘写入器和调谐器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040323 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040519 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040720 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040811 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080820 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080820 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090820 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090820 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100820 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100820 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110820 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120820 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130820 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |