JP3587457B2 - Circuit board and its manufacturing method - Google Patents

Circuit board and its manufacturing method Download PDFInfo

- Publication number

- JP3587457B2 JP3587457B2 JP2001344073A JP2001344073A JP3587457B2 JP 3587457 B2 JP3587457 B2 JP 3587457B2 JP 2001344073 A JP2001344073 A JP 2001344073A JP 2001344073 A JP2001344073 A JP 2001344073A JP 3587457 B2 JP3587457 B2 JP 3587457B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- inner via

- via hole

- density

- sectional area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Production Of Multi-Layered Print Wiring Board (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

Description

【0001】

【発明が属する技術分野】

本発明は、回路基板とその製造方法に関する。とくに平面方向に密度差のある補強シートを用いた回路基板とその製造方法に関する。

【0002】

【従来の技術】

近年、電子機器の小型軽量化、高機能高性能化に伴い、産業用にとどまらず広く民生用機器の分野においても大規模集積回路(LSI)等の半導体チップを高密度に実装できる多層回路基板を安価に供給することが強く要望されている。

【0003】

このような市場の要望に対しては、従来のセラミック多層基板に変わり、より安価に供給することができる樹脂多層回路基板を、高密度実装に好適な基板(高密度配線基板)にする技術開発が行われている。

【0004】

このような回路基板としては、特開平6−268345号公報に開示されている全層インナービアホール構造の樹脂多層基板がある。これは、任意の配線層の、任意の位置を導電ペーストにより接続できるインナービア接続法すなわち全層インナービアホール構造を採用し多樹脂多層基板であり、高密度実装に好適な回路基板を安価に提供できるものである。

【0005】

この回路基板の製造方法では、まず被圧縮性の絶縁体層(アラミドエポキシプリプレグ)にインナービアホールを形成し、貫通孔に導電ペーストを充填する。その後、銅箔を両側に重ね熱プレスで加熱加圧して、絶縁体層と導電ペースト樹脂を硬化させ、銅箔と絶縁体層の接着と図る、と同時に、両側の銅箔を導電ペーストを通して電気的に接続を図る。最後に、両側の銅箔を配線パターンに加工し両面回路基板が完成する。

【0006】

この基板は高密度配線と低くばらつきの少ない接続抵抗を実現し、市場から高い評価を得ている。

【0007】

高密度配線の必要性は前記したとおりであるが、ばらつきの少ない接続抵抗の有用性は次の通りである。すなわち、接続抵抗を含む回路抵抗は、回路設計をする上で重要なパラメーターであり、製品ごとに回路抵抗が異なると、回路設計ができない、あるいは、製品の回路抵抗が設計値からずれてしまい動作しない等の不具合が起こってしまう。このため、接続抵抗には、ばらつきが少ないことが要求される。

【0008】

特にインナービアによる接続では、従来のスルーホールによる接続にくらべて、一つの回路に関与するインナービアの数が多くなるために、ばらつきに対する要求は厳しくなる。

【0009】

しかしながら、前記した全層インナービアホール構造の回路基板技術では、次のような課題があった。すなわち、絶縁体層にアラミド不織布の補強材とエポキシ樹脂の複合材料(アラミドエポキシ基材)を用いているが、アラミド繊維は吸湿しやすい材料であるため、真空包装するなど、吸湿しないように管理しなければならず、このような管理はコストアップにつながるという課題である。

【0010】

一方、一般の回路基板に用いられているガラスエポキシ基材は、ガラス繊維の織布にエポキシ樹脂を含浸した基材で、ガラス繊維は吸湿しないので、吸湿管理の点で有利である。さらに、機械強度が高いという利点もあるため、ガラスエポキシ基材を絶縁体層にしてインナービア接続の全層インナービアホール構造の回路基板を実現することが望まれていた。

【0011】

しかし、前記した全層インナービアホール技術を単純にガラスエポキシ基材に当てはめようとするとインナービアの接続抵抗のばらつきが大きくなってしまうと言う課題がある。これは、本発明者等の検討の結果、補強材のガラス織布が面内方向に密度のばらつき(たて糸とよこ糸が織り重なった部分とそうでない部分)を持っていることに起因することが判った。詳細には、熱プレス工程で加熱加圧するときに、補強材の密度が小さいところ(たて糸とよこ糸が織り重なっていなところ)に設けられたインナービアでは、側壁面に補強材が少ないため、プレス中にインナービアが横方向に広がる、つまり、プレス圧力が横方向に散逸してしまう。このため、インナービアの縦方向に充分な圧縮力が加わらず、導電体同士の接続が充分に行われないため、電気的接続抵抗が大きくなってしまうからであることが判った。

【0012】

以上の電気的接続抵抗のバラツキは、エポキシ樹脂を含浸させたガラスクロスのみならず、不織布、シート、フィルムにおいても、面方向の厚みムラや密度のムラにより発現するという問題がある。

【0013】

【発明が解決しようとする課題】

本発明は、上記した課題を解決するためになされたものであり、たとえば、ガラスエポキシ基材をはじめとする平面方向に密度分布のある補強材シートを含有する基材を絶縁体層に用いた場合にでも、高密度配線でしかもばらつきの少ないインナービア接続抵抗を実現する回路基板とその製造方法を提供することを目的とする。

【0014】

【課題を解決するための手段】

前記目的を達成するため、本発明の回路基板は、平面方向に密度分布のある補強材シートを含む電気絶縁体層と、前記電気絶縁体層の厚さ方向に空けられた複数のインナービアホールに導電体が充填され、かつ前記導電体に接続されている配線層を具備する回路基板であって、

前記補強材シートの密度の大きな部分に設けられた前記インナービアホールの断面積を、前記補強材シートの密度の小さな部分に設けられた前記インナービアホールの断面積よりも小さく形成することを特徴とする。

また、本発明の別の回路基板は、平面方向に密度分布のある補強材シートを含む電気絶縁体層と、前記電気絶縁体層の厚さ方向に空けられ、導電体が充填された第1のインナービアホールと、

前記電気絶縁体層の厚さ方向に空けられ、導電体が充填され、第1のビアホールの断面積より大きな断面積を有する第2のインナービアホールと、

前記電気絶縁体層の厚さ方向に空けられ、導電体が充填され、第2のビアホールの断面積より大きな断面積を有する第3のインナービアホールと、を備え、

第3のビアホールが設けられた部分の補強材シートの密度より、第2のインナービアホールが設けられた部分の補強材シートの密度が大きく、

第2のビアホールが設けられた部分の補強材シートの密度より、第1のインナービアホールが設けられた部分の補強材シートの密度が大きいことを特徴とする。

【0015】

次に本発明の回路基板の製造方法は、平面方向に密度分布のある補強材シートを含む絶縁体層に導電体を充填するための複数のインナービアホールを形成するに際し、

前記補強材シートの密度の大きな部分に設けるインナービアホールの断面積を、前記補強材シートの密度の小さな部分に設けるインナービアホールの断面積より小さく形成し、

次に前記インナービアホールに導電体を充填し、

前記導電体に接続するように配線層または配線層を形成するための金属箔を積層し、加熱加圧することを含むことを特徴とする。

【0016】

【発明の実施の形態】

インナービアの接続抵抗は、導電ペーストで圧接するタイプでは、(絶縁体層厚み/ビア径)の比が1よりも大きくなると急激に不安定になり、ばらつきが大きくなる。このため、回路基板の小径ビア(例えば直径50μm)を実現するためには、絶縁体層の厚みを50μm以下にすることが好ましい。しかし、コアの回路基板は、ガラスエポキシ基材、アラミドエポキシ基材などでは通常50μm以上の厚みがある。また、コア基板をあまり薄くすると機械強度が小さくなり、好ましくない。したがって、薄い絶縁体層は50μm以下で、かつ絶縁体層厚み/ビア径の比が1以下であることが好ましい。

【0017】

本発明においては、平面方向に密度分布のある補強材シートが、合成繊維及び無機繊維から選ばれる少なくとも一つの繊維で構成される織布または不織であることが好ましい。

【0018】

また、平面方向に密度分布のある補強材シートが、ガラス繊維からなる織布であることが好ましい。

【0019】

また、ガラス繊維からなる織布のたて糸とよこ糸の重なった部分に設けられたインナービアの断面積が、それ以外の部分に設けられたインナービアの断面積に比べて小さいことが好ましい。

【0020】

また、断面積が大きいインナービアホールの側壁面の突出繊維の突出量に比較して、断面積が小さいインナービアホールの側壁面の突出繊維の突出量が多いことが好ましい。

【0021】

また、配線層が複数層存在し、そのうちの少なくとも1層の前記配線層が前記絶縁体層に埋設していることが好ましい。

【0022】

また、補強材シートの密度が大きいところではインナービアの断面積が小さく、補強材シートの密度が小さいところではインナービアの断面積が大きいことが好ましい。

【0023】

また、本発明の回路基板の片面に、さらに被圧縮性の電気絶縁材料により構成された回路基板が積層されていてもよい。

【0024】

また、本発明の回路基板が両外側に配置され、その間にさらに被圧縮性の電気絶縁材料により構成された回路基板がコア基板として積層されていてもよい。

【0025】

また、本発明の回路基板をコア基板とし、前記コア基板の少なくとも片面に、さらにコア基板の絶縁体層よりも薄い絶縁体層からなる回路基板が少なくとも1層積層されていてもよい。

【0026】

また、インナービアホールの大きな断面積が小さな断面積に比較して、1.15倍以上10倍以下が好ましく、さらに好ましくは1.4倍以上5倍以下、特に好ましくは1.4倍以上2倍以下の面積である。1.15倍未満では補強シートの密度差によるを電気抵抗のバラツキを小さくすることが困難であり、10倍を越えるとビア抵抗が低くなりすぎてビア抵抗のバラツキを小さくすることが困難になる。

【0027】

次に本発明方法においては、前記補強材シートの密度の大きな部分に設けるインナービアホールの断面積を、前記補強材シートの密度の小さな部分に設けるインナービアホールの断面積より小さく形成する方法が、前記補強材シートの厚さ方向に回転ドリルを挿入して貫通孔を形成した後、ドリルを回転させたまま一旦静止し、その後に前記ドリルを引き抜く方法であることが好ましい。

【0028】

また、前記補強材シートの密度の大きな部分に設けるインナービアホールの断面積を、前記補強材シートの密度の小さな部分に設けるインナービアホールの断面積より小さく形成する方法が、熱加工型のレーザー加工法であることが好ましい。

【0029】

また、配線層が複数層であり、そのうちの少なくとも1層の配線層を前記絶縁体層に埋設することが好ましい。

【0030】

前記において、ガラスエポキシ基材の場合は、ガラスクロスのたて糸とよこ糸の織り重なった部分とガラスクロスの目が開いた部分で、好ましくはビアの断面積の比が1.15倍以上、更に好ましくは、1.4倍以上である。この範囲であれば、ビア抵抗のばらつきは少なくなる。

【0031】

本発明の回路基板によれば、ばらつきの少ない接続抵抗を具備した回路基板を実現できる。

【0032】

本発明の別の回路基板によれば、ばらつきの少ない接続抵抗と高い接続信頼性を具備した回路基板を実現できる。

【0033】

また、本発明の別の回路基板においては、少なくとも1層の前記配線層が前記絶縁体層に埋設していることが好ましい。この例によれば、さらにばらつきの少ない接続抵抗を具備した回路基板を実現できる。

【0034】

次に本発明の多層回路基板によれば、全層にわたり、さらにばらつきの少ない接続抵抗を具備した多層回路基板を実現できる。

【0035】

次に本発明の多層回路基板によれば、ばらつきの少ない接続抵抗を具備した回路基板をコア基板として、表層に微細配線層を具備した多層回路基板を実現できる。

【0036】

次に本発明の回路基板の製造方法によれば、ばらつきの少ない接続抵抗を具備した回路基板の製造を容易に実現できる。

【0037】

本発明の第1回路基板の製造方法においては、少なくとも1層の配線層を前記絶縁体層に埋設する工程を含むことが好ましい。この例によれば、さらにばらつきの少ない接続抵抗を具備した回路基板の製造を容易に実現できる。

【0038】

次に本発明の多層回路基板の製造方法によれば、全層にわたり、ばらつきの少ない接続抵抗を具備した多層回路基板の製造を容易に実現できる。

【0039】

次に本発明の多層回路基板の製造方法によれば、ばらつきの少ない接続抵抗を具備した回路基板をコア基板として、表層に微細配線層を具備した多層回路基板の製造を容易に実現できる。

【0040】

まず本発明に用いる材料について説明する。

【0041】

(インナービア形成用導電体)

インナービアを形成する導電体は、導電性粉体を含有した樹脂組成物(導電ペースト)を用いることができる。導電ペーストは圧縮することで導電性が向上するので好ましい。

【0042】

導電性フィラーは、金、銀、銅、ニッケル、パラジウム、鉛、錫、インジウム、ビスマスから選ばれた少なくとも1種の金属、これらの合金、または混合物からなるフィラーを用いることができる。また、前記した金属・合金、あるいは、アルミナ、シリカなどの酸化物、あるいは有機合成樹脂などからなるボールに前記した金属・合金をコートしたコートフィラーを用いることもできる。

【0043】

形状は特に限定される物ではないが、粉体、繊維状フィラー、粉体の造粒体、球状ボールあるいはこれらの混合物などを用いることができる。

【0044】

樹脂組成物のバインダーに用いる樹脂としては、液状のエポキシ樹脂、ポリイミド樹脂、シアネートエステル樹脂、フェノールレゾール樹脂などを用いることができる。エポキシ樹脂としてはビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ビスフェノールAD型エポキシ樹脂等のグリシジルエーテル型のエポキシ樹脂、脂環式エポキシ樹脂、グリシジルアミン型エポキシ樹脂、グリシジルエステル型エポキシ樹脂等のエポキシ基を2つ以上含有したエポキシ樹脂などを使用することができる。また、エポキシ基が1つのエポキシ化合物も反応性希釈剤として含有させることができる。

【0045】

必要に応じて、ブチルセルソルブ、エチルセルソルブ、ブチルカルビトール、エチルカルビトール、ブチルカルビトールアセテート、エチルカルビトールアセテート、α−ターピネオール等の溶剤や分散剤などの添加剤を含有させることもできる。

【0046】

また、本発明の導電体としては、前記した導電ペーストに限定される物ではなく、金、銀、銅、ニッケル、パラジウム、鉛、錫、インジウム、ビスマス等の金属よりなるビアポストなど、圧接により導通を得るタイプのインナービア接続材を使用することができる。

【0047】

(平面方向に密度分布のある電気絶縁体層)

平面方向に密度分布のある電気絶縁体層の材料としては、ガラスエポキシ基材があげられる。ガラスエポキシ基材は、ガラス織布にエポキシ樹脂を含浸した複合材で、回路基板用材料としてBステージ(半硬化状態)のもの、Cステージ(硬化状態)のものが市販されている。機械強度に優れ、安価に入手できるので好ましい。この中でもCステージ(硬化状態)の基材よりもBステージ(半硬化状態)の基材を用いるのが好ましい。樹脂が硬化した状態よりも半硬化状態のほうが、レーザーにより穴あけ加工しやすく、補強材のガラスクロスとの加工性の差が大きく、また半硬化状態のほうが導電ペーストを圧縮するための実効的な圧力が小さくてすむからである。しかし、電気絶縁体層はこの基材の例に限定されるものではなく、平面方向に密度分布(密度差)のある補強材シートを含有する絶縁体層を用いることができる。例としては、PBO(ポリパラフェニレンベンゾビスオキサゾール)繊維、PBI(ポリベンゾイミダゾール)繊維、アラミド繊維、PTFE(ポリテトラフルオロエチレン)繊維、PBZT(ポリパラフェニレンベンゾビスチアゾール)繊維または全芳香族ポリエステル繊維などの有機繊維やガラス繊維などの無機繊維からなる織布または不織布に対して、エポキシ樹脂、ポリイミド樹脂、フェノール樹脂、フッ素樹脂、不飽和ポリエステル樹脂、PPE(ポリフェニレンエーテル)樹脂、ビスマレイミドトリアジン樹脂またはシアネートエステル樹脂などの熱硬化性樹脂または熱可塑性樹脂を含浸させた複合材シートなどを用いることが可能である。

【0048】

電気絶縁体層の厚みに特に限定はないが、通常、市販されている0.02mm〜0.5mm程度のものを用いることができる。絶縁体層の単位面積当たりの重量は、50g/m2以上800g/m2以下の範囲が好ましい。

【0049】

(カバーフィルム)

カバーフィルムは、製造工程中で、ゴミによる汚染防止と、導電体を充填するときのマスクとしての機能を果たし、最終的には取り除かれる。このため、プリプレグの少なくとも導電体を充填する側にカバーフィルムを配置する事が好ましい。また、プリプレグと接触する面には離型処理を施すことが好ましい。カバーフィルムの材料に限定は無いが、例を挙げると、PET(ポリエチレンテレフタレート)フィルムやPEN(ポリエチレンナフタレート)フィルムにシリコーン系離型剤を塗布したものを用いることができる。また、導電ペーストを印刷法で充填するときは、カバーフィルムの厚み分だけ余分にインナービア上に導電ペーストが充填される。最後にフィルムを剥離するとインナービアから導電ペーストが突出した構造になり、熱プレス工程では、この突出した分が圧縮される厚さとなる。このため厚みが厚いほどインナービアはよく圧縮され低い接続抵抗を実現できるが、逆に厚すぎると剥離するときに導電ペーストがカバーフィルムにとられてしまう。一例を挙げると200μm以下の孔径の場合は厚みは35μm以下、100μm以下の孔径の場合は厚みは20μm以下であることが好ましい。

【0050】

(金属箔)

金属箔の具体例としては、電解銅箔や圧延銅箔を用いることができる。電解銅箔の例では、厚み3μm〜70μm程度のものが市販されており、これらを用いることができる。厚みの薄いもの、特に9μm以下のものは取り扱いのため支持キャリアをつけた銅箔を用いることができる。また、金属箔の表面粗さは、一例として平均粗さRzが0.5〜10μmの範囲である。

【0051】

次に、本発明の実施の形態について図面を用いて説明する。

【0052】

(実施の形態1)

図1は第1の実施の形態の回路基板の模式平面図である。本実施の形態では、平面方向に密度分布のある補強材シート101を含有する絶縁体層に、ガラスエポキシ基板を用いる場合について説明する。図1では、説明のため基材内部のガラス織布の横糸102a、たて糸102bを図示している。ガラス繊維の織り重なった部分(補強材シートの密度の大きな部分)以外に設けるインナービア103は、織り重なっている部分(補強材シートの密度の大きな部分)に設けるインナービア104より断面積が大きくなっている。前記において、ガラスクロスの織り重なった部分とガラスクロスの目が開いた部分で、好ましくはビアの断面積の比が1.15倍以上、更に好ましくは、1.4倍以上である。この範囲であれば、ビア抵抗のばらつきは少なくなる。

【0053】

本実施の形態の、回路基板は次のように作製することができる。

【0054】

まず、接続中間体を作製する。Bステージ(半硬化状態)のガラスエポキシ基材(ガラスエポキシプリプレグ:201)の両側面に前記カバーフィルム202を熱圧着し、所望の位置に機械ドリルでインナービアホール(本実施の形態では貫通孔:203,203’を形成する(図2A)。

【0055】

つぎに、インナービアホールに導電ペースト204を印刷法などで充填し、充填後にカバーフィルム202を剥離除去して接続中間体205が完成する(図2B)。

【0056】

図2Aにおける孔加工条件の一例としては、ドリル径:150μm、加工速度:約133穴/分、ドリル下降速度:2m/分で貫通孔203,203’を形成できる。このとき孔貫通後にドリルを例えば約0.2秒の間、下降した状態で回転したまま静止させ、その後にドリルを引き抜く。

【0057】

この場合、繊維が密なところは繊維が突っ張りとなって穴径203はそのままであるが繊維が粗の部分(樹脂リッチのところ)203’は、加工による発熱、ドリルのわずかな芯ぶれ等により穴径が拡大する。つまり、穴径は加工部の繊維量によって連続的に変化し、結果として、穴をあける部分の繊維の密度に反比例した穴径が得られる。ここで、「反比例」とは、数学的な意味の反比例ではなく、「補強材密度の大きな部分では孔径が小さく、補強材密度の小さな部分では孔径が大きくなる」ことを言う。この語句は、以下の明細書中でも同一の意味で用いる。

【0058】

通常の回路基板の作製では、ドリルが材料を貫通した後、即座にドリルを上昇させるのが普通である。これは、穴品質(同じ孔径にそろえるという意味で)、ドリル折れ防止およびタクトアップのためである。この場合は繊維の粗密に関係なくほぼ一定の穴が加工されることになる。

【0059】

例えば、約70μmの厚みのプリプレグを用い本実施の形態の孔加工を行ったところ、ガラスクロスのたて糸とよこ糸が織り重なった部分(ガラス繊維の密度の最も高い部分)では、孔径は直径150μm、クロスの目の開いた部分(ガラス繊維の密度の最も低い部分)では、孔径は180μm、それ以外の場所は孔径は150μmから180μmの間でガラス繊維の密度に反比例して小さくなった。ガラスクロスを構成する繊維糸の立て糸とよこ糸の織り重なった場所に設けた孔は、織り重なりに収まる孔径以下の大きさになった。

【0060】

次に、前記した接続中間体205の両面に配線パターンを形成するための厚さ18μmの金属箔206を重ね合わせ、熱プレスで加熱加圧した(図2C)。熱プレスの条件は、一般的な回路基板の熱プレス条件を用いることができ、例としては、180℃〜250℃、30〜200kgf/cm2、0.5〜2時間である。この工程では、プリプレグの樹脂と導電ペーストの樹脂を硬化させ、金属箔と接着させると同時に両側の金属箔同士を導電ペーストを通して電気的に接続させた。

【0061】

最後に、金属箔を配線パターン207に加工して両面回路基板208が完成した(図2D)。配線パターンの加工法は、フォトリソ法など一般の回路基板の配線加工法を用いることができる。

【0062】

インナービアの接続抵抗は、インナービアの断面積が大きいほど低くなる。また、導電フィラー同士(導電フィラーと銅箔)に加わる実効的な圧力が大きいほど接点は多くなりまた各々の接点も大きくなり、接続抵抗は低くなる。実効的な圧力を大きくするには、熱プレスの圧力を大きくすると同時に、インナービアホールの側壁面が横に広がらない構成にすることが必要である。ここで、側壁面が横に広がらない構成とは、本実施例の形態でいえば、ガラスクロスの織り重なった場所に設けた孔は、織り重なりに収まる孔径以下の大きさにすることである。

【0063】

本実施の形態では、補強材の密度の最も大きな部分(ガラスクロスの繊維の織り重なった部分)は側壁面が広がりにくい構成のため直径150μmのインナービアホール(貫通孔)を、補強材の密度の最も小さな部分(ガラスクロスの目の開いた部分)では実効圧が最もかかりにくいので孔径は180μm、それ以外の部分では孔径は150〜180μmの間でガラス繊維の密度に反比例して小さく形成したものである。前記した孔加工条件で作製した本実施の形態のインナービアでは約2〜3mΩと非常にばらつきの少ない接続抵抗を実現できる。インナービアホールの孔径は前記した孔径に限定されない。

【0064】

本実施の形態の両面回路基板208をコア基板としてその両側に、前記した接続中間体205と金属箔206を重ね(図3A)、両面基板と同様に熱プレスでコア基板とプリプレグを積層して、最後に金属箔を配線パターン209に加工することで4層基板を作製することができる(図3B)。

【0065】

さらなる多層基板は、コア基板に多層基板を用いて前記した積層工程を繰り返すことで作製することができる。

【0066】

なお、本実施の形態の多層基板では、コア基板の両側に積層するプリプレグには、コア基板の配線層207が埋設することになる。すなわち、インナービア部分にも配線層が埋設されるため、プレス工程中のインナービアの圧縮率が高くなり、接続抵抗をさらに低く、ばらつきを小さくすることができる。

【0067】

また、両面回路基板においても配線転写法を用いれば配線層を埋設することができ、同様に、さらに低く、ばらつきの小さい接続抵抗が実現できる。詳細には、図4Aに示すように支持基板(キャリア)に金属箔を形成したいわゆるキャリア付き金属箔を用いることができる。キャリア付き金属箔211の例としては、アルミキャリアに離型層を介して銅箔が積層されたものなどが市販されている。本発明の実施の形態に用いる場合には、銅箔を塩化鉄水溶液、過硫酸アンモニウム水溶液などでエッチングによりあらかじめパターニングして、配線層210を接続中間体205に埋設するように積層した後、アルミキャリアを塩酸などでエッチングして除去することができる(図4B)。

【0068】

本実施の形態の機械ドリルを用いた貫通孔の形成方法としては上記以外にも、当然、異なる径のドリルを用いることも可能である。つまり、ガラス繊維の織り重なった部分(補強材シートの密度の大きな部分)以外に設けるインナービアホールは、織り重なっている部分(補強材シートの密度の大きな部分)に設けられたものより径の小さなドリルを用いるのである。補強材の密度分布が不規則な場合は各ワーク毎に密度分布に応じてドリル径を選択する必要があるが、ガラス織布のような密度分布が規則的な補強材を用いる場合は、このような余分の工程が要らず(または少なく簡便になり)好ましい。

【0069】

貫通孔の形成方法としてはこの他にも通常の回路基板の孔加工法、すなわち、炭酸ガス、YAG、エキシマなどのレーザー孔加工法や、パンチングなども用いても同様に本実施の形態のインナービアホール(貫通孔)を形成することができる。

【0070】

次に図11に示すように、炭酸ガスレーザー孔加工法により貫通孔を形成した場合は、ガラス繊維の密度の大きい部分に形成したインナービア(孔径の小さいインナービア)702には、多くのガラス繊維704がインナービアの内部に突出した構成となる。これに対して、ガラス繊維の密度の小さい部分に形成したインナービア(孔径の大きいインナービア)701には、相対的に少ないガラス繊維703がインナービアの内部に突出した構成となる。このような構成とすることで、インナービアと周りの絶縁体層のガラスエポキシ基材がアンカー効果によりよく接着し、機械的(及び熱的)な応力に対して強度が増し、小さな孔径のインナービアの接続信頼性を向上させることができる。小さな孔径のインナービアは、導電体の接触点数が少ないため、大きなインナービアよりも接続信頼性が低くなりがちである。しかし、上記した方法で小さなインナービアの接続信頼性を向上させることで基板全体としての接続信頼性向上させることができる。

【0071】

炭酸ガスレーザーを用いた場合の例としては、波長9.4μmまたは10.6μmの炭酸ガスレーザーを使用できる。ショット回数は1〜3回が適正である。このような例の場合、波長は長くショット回数が少ないほど本発明の効果は顕著だった。孔あけ加工は、同一のレーザーを照射したときに、ガラスクロス基材の密度分布の差に起因する被加工性の違いを利用する。この関係は次の表1のようになる。

【0072】

【表1】

【0073】

次にレーザー光の波長に関して説明する。同一エネルギーのレーザーであれば、一般に、波長が短い方がレーザースポット径が小さくなり、この結果、レーザーのエネルギー密度が大きくなる。エネルギー密度の大きなレーザーでは、一般的には穴の開けにくい材料であるガラスクロスを用いたシートに穴を開けることが容易になり、基材の密度分布によらず、バラツキの少ない孔径の孔を形成できる。逆に波長が短ければ、レーザーのスポット径が大きくなり、この結果、エネルギー密度は小さくなる。このため、穴の開けやすい材料であるマトリックス樹脂の部分の穴は開けやすいが、ガラスクロスの部分は穴が開けにくくなり、基材の密度分布の影響を受けやすくなる。すなわち、ガラスクロスのたて糸とよこ糸の織り重なった部分は小さな孔となり、織り目があいているの部分は大きな孔となる。したがって、レーザー光の波長は長いほうが好ましい。

【0074】

次にショット回数について説明する。レーザー照射はショット回数が多いほど投入するエネルギー総量は大きくなる。例えば2ショットでは1ショットの2倍のエネルギー総量になる。このため、同一箇所に複数回ショットすると、エネルギー総量が大きくなり、最初のショットで加工できなかったガラスクロスも、2回目、3回目のショットで順次穴あけ加工されて、基材の密度分布によらず孔径が均一になる。逆にショット回数が少なければ、基材の密度分布の影響を受けやすくなる。すなわち、ガラスクロスのたて糸とよこ糸の織り重なった部分は小さな孔となり、織り目があいているの部分は大きな孔となる。したがって、ショット回数は1〜3回が適正である。

【0075】

本実施の形態では、インナービアホールは、貫通孔について説明したが、非貫通孔としてもよい。非貫通孔の場合の回路基板の作成方法は、図5A〜図5Dに示すようにする。

【0076】

まず、プリプレグ301の片面に配線パターン302を形成した前記配線転写材の配線がプリプレグの側に来るように、もう片面に前記カバーフィルム304を仮圧着する。つぎに、所望の位置にブラインドビアホール(非貫通孔)305を炭酸ガスレーザー孔加工法などで形成して(図5A)、導電体(導電ペースト)306を充填する。カバーフィルムを除去して(図5B)、カバーフィルムを除去した側に金属箔307を重ねて、熱プレスで加熱加圧する(図5C)。金属箔を配線パターン308に加工して、配線転写材の支持基板303を除去すると両面回路基板が完成する(図5D)。金属箔のパターンに加工後の積層体(回路基板転写材)を配線転写材の替わりの用いて前記した工程を必要回数繰り返せば多層回路基板を作製することができる。この方法によれば、配線パターンの位置に合わせてビアホールを形成するために、寸法合致精度を向上させることができる。

【0077】

(実施の形態2)

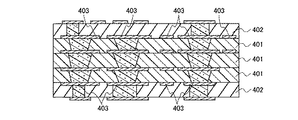

図6は本発明の第2の実施の形態の多層回路基板の断面模式図である。本実施の形態の多層基板は、被圧縮性の絶縁基材からなるコア基板の少なくとも片面に実施の形態1で説明した回路基板が積層された構成である。図では、アラミドエポキシ基板の両面基板401をコア基板として用いて、第1の実施の形態で説明した構成のガラスエポキシ基材による回路基板402をコア基板の両側に積層した構成である。

【0078】

本実施の形態の多層回路基板は次のように作製することができる。

【0079】

まず、アラミドエポキシプリプレグを用いて両面回路基板を作製する。両面回路基板の作成方法は、まず、アラミドエポキシプリプレグの両面にカバーフィルムを仮圧着して、貫通孔を形成する。貫通孔は、例えば炭酸ガスレーザーで、孔径200μmのものを形成することができる。アラミドエポキシプリプレグは、アラミド繊維の不織布にエポキシ樹脂を含浸した複合材で、内部に空隙が多数存在するために被圧縮性をもつため、実施の形態1で示した方法によらなくともインナービアはばらつきの少ない接続抵抗を実現できる。もちろん、実施の形態に示したように、補強材(この場合はアラミド不織布)の密度により孔径を変えればよりばらつきが少なくなり好ましいことは言うまでもない。

【0080】

つぎに、貫通孔に導電ペーストを充填してカバーフィルムを除去すれば、アラミドエポキシ基材による接続中間体の完成である。この後は実施の形態1と同様にアラミドエポキシ基板の両面回路基板を得ることができる。また、貫通孔はレーザーを用いてあけても良いし、ドリルを用いてあけても良い。

【0081】

これをコア基板として両側から実施の形態1で説明した接続中間体と金属箔を重ね、実施の形態1と同様に熱プレスにより積層し、前記金属箔を配線パターンに加工する。これにより4層基板(ここで4層とは配線層をいう。)は完成する。なお、被圧縮性のコア基板は多層回路基板でもよい。コア基板の配線層が4層の例を図12に示す。

【0082】

さらに高多層が必要なときには、本実施の形態の多層基板をコア基板として本実施の形態の工程を繰り返すことで作製することができる。

【0083】

本実施の形態の多層基板では、ガラスエポキシ基材による絶縁体層のすべてに、配線層が埋設している構成であり、実施の形態1で説明したように、さらに、ばらつきの少ない接続抵抗を実現できる。また、コア基板には配線層は埋設しないが、アラミドエポキシプリプレグの被圧縮性がこれを補いインナービアは充分圧縮される構成となっている。つまり、本実施の形態の多層回路基板は全層にわたりさらに、ばらつきの少ない接続抵抗を実現できる。さらに、両側にガラスエポキシ基材を積層した場合は、アラミドエポキシ基材が外部にさらされることが無くなり、吸湿しにくい構成となる。その上、ガラスポキシ基材は機械強度に優れるため、アラミドエポキシ基材のみで構成した多層基板に比べて機械強度に優れた基板を実現できる。

【0084】

(実施の形態3)

図7は本発明の第3の実施の形態の多層基板の断面模式図である。本実施の形態の多層基板は、第1または第2の実施の形態の回路基板501をコア基板として、コア基板の少なくとも片面に、コア基板の絶縁体層よりも薄い絶縁体層の回路基板502を積層した構成である。薄い絶縁体層には、より微細なインナービアを低抵抗で形成することができる。これは、同じ孔径でもインナービアの長さつまり絶縁体層の厚みを薄くすれば接続抵抗が小さくなるからである。

【0085】

実施の形態2の4層多層基板をコア基板として、コア基板の絶縁体層より薄い絶縁体層としてポリイミドフィルムを用いた場合について説明する。

【0086】

本実施の形態の多層基板はつぎのように作製することができる。まず、ポリイミドフィルムによる絶縁体層の基板の作成方法を説明する。図8Aに示すように、ポリイミドフィルム601の両面に接着剤層602を形成したフィルム(薄い絶縁体層603)の片面に、図8Bに示すようにカバーフィルム604を、もう一方の片面にキャリア付配線パターン605を仮圧着する。接着剤層602はポリイミド系やエポキシ系の接着剤を用いることができる。フィルムの厚みは、一例としては、ポリイミドフィルム13μmに対して接着剤層を各々5μm形成する。カバーフィルムは、実施の形態1と同様にすることができる。また、配線パターンは、実施の形態1で説明した、転写法に用いるキャリア付銅箔に配線パターンを形成したものを用いることができる。

【0087】

次に、図8Cに示すようにフィルムに非貫通孔を形成して導電体606を充填してカバーフィルムを除去する。これにより、両面回路転写材中間体614が完成する。非貫通孔の形成はレーザー孔加工法を用いることができる。一例としてはUV−YAGレーザー(3倍高調波:波長355nm)を用いることができる。UV−YAGレーザーによれば銅箔にダメージを与えることなく微細な非貫通孔(本実施の形態では30〜50μm程度となる)を形成できるので好ましい。

【0088】

導電体としては、実施の形態1と同様に導電ペーストを用いることができる。導電ペーストの充填は、スキージによる印刷法を用いることができる。非貫通孔の充填では、充填時あるいは、充填後に減圧することが好ましい。これは、開口部からペーストを充填したときにかみこんだ気泡を減圧することにより取り除くためである。また銅箔は、表面に凹凸を設けた粗化銅箔を用いて、接着層との間に隙間(銅箔表面の凸凹に対応した微細な隙間で、導電ペーストの導電フィラーよりも小さくする)を残して仮圧着するのが好ましい。これは、導電ペーストの充填時及びプレス時に、導電ペーストの樹脂がこの隙間から排出され、インナービアの中の導電粉の割合が高まりさらに低抵抗が得られるからである。

【0089】

次に図8Dに示すように、両面回路転写材中間体614のカバーフィルムを取り除いた側に金属箔607を重ね、熱プレスにより加熱加圧する。このとき配線パターンは接着剤層602に埋め込まれる。熱プレスの条件は、実施の形態1と同様にすることができる。

【0090】

次に金属箔を通常のフォトリソ法で配線パターン608に加工して、キャリア付両面回路転写材609が完成する(図9A)。

【0091】

キャリア付金属箔の替わりに前記キャリア付両面回路転写材609を用いて前記工程を繰り返せば多層転写材中間体610(図9B)や多層回路転写材611(図9C)を作製できる。

【0092】

コア基板の絶縁体層より薄い絶縁体層としてポリイミドフィルムを用いた場合について説明したが、BCB(ベンゾシクロブテン)、PTFE(ポリテトラフルオロエチレン)、アラミド、PBO(ポリパラフェイレンベンゾビスオキサゾール)または全芳香族ポリエステルなどフィルムに接着剤を形成して用いることもできる。熱可塑性フィルムの場合は、フィルム自体が加熱すると接着性を持つので接着剤無しで用いることもできる。

【0093】

次に、転写材をコア基板に積層する。

【0094】

コア基板としては、実施の形態1または2で説明した回路基板612を用いることができる。コア基板612の少なくとも片側に転写材中間体610を図10Aのように重ね合わせ、熱プレスにより積層する。熱プレスの条件は実施の形態1と同様にすることができる。最後に、転写材中間体のキャリアをエッチングにより除去すれば、本実施の形態の多層基板が完成する。

【0095】

また、転写材中間体を用いる替わりに、実施の形態1または2の接続中間体613を介して、本実施の形態の(多層)回路転写材611をコア基板612に積層して、本実施の形態の多層基板を作製することもできる(図10B)。

【0096】

本実施の形態では、薄い絶縁体層を配線転写材でコア基板に転写する方法を示したが、この方法によれば薄い絶縁体層に形成したより微細な回路と、コア基板を別に作製することができるので、コア基板の上に順に積み上げていく方法に比べて、微細な回路部分のゴミによる汚染が少なくまた、全体の歩留まりを向上させることができる。

【0097】

本実施の形態の多層回路基板では、実施の形態1及び2で説明したばらつきの少ない接続抵抗を具備した全層IVH構造の回路基板をコア基板としてその上に、より高密度な配線層を形成できる。薄いポリイミドフィルムの絶縁体層だけで基板を作った場合は、機械強度が要求される分野に使用することは難しいが、本実施の形態の多層基板は、機械強度と高密度微細配線(コア基板部分を含めて)が実現可能であり、特に比較的大きな半導体を直接実装するためのパッケージ用基板に好適である。

【0098】

コア基板としては、一般の回路基板(ガラスエポキシスルーホール基板、ビルドアップ基板、エポキシ樹脂含浸させたアラミド繊維不織布を用いた多層基板など)を用いてもよい。また、図に示すように、前記転写材を接続中間体を介して配線形成用の金属箔に直接積層することもできる。

【0099】

【発明の効果】

本発明によれば、ガラスエポキシ基材をはじめとする平面方向に密度分布のある補強材シートを含有する基材を絶縁体層に用いた場合にでも、高密度配線でしかも、ばらつきの少ないインナービア接続抵抗を実現する回路基板とその製造方法を提供できる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態における回路基板の模式的平面図

【図2】A〜Dは、本発明の第1の実施の形態における回路基板の製造方法(貫通孔)の各工程の説明図

【図3】A〜Bは、本発明の第1の実施の形態における回路基板の製造方法(貫通孔)の各工程の説明図

【図4】A〜Bは、本発明の第1の実施の形態における回路基板の製造方法(貫通孔)の各工程の説明図

【図5】A〜Dは、本発明の第1の実施の形態における回路基板の製造方法(非貫通孔)の説明図

【図6】本発明の第2の実施の形態における多層回路基板の断面模式図

【図7】本発明の第3の実施の形態における多層回路基板の断面模式図

【図8】A〜Dは、本発明の第3の実施の形態における多層回路基板の製造方法の説明図

【図9】A〜Cは、本発明の第3の実施の形態における多層回路基板の製造方法の説明図

【図10】A〜Bは、本発明の第3の実施の形態における多層回路基板の製造方法の説明図

【図11】本発明のガラス繊維が突出したインナービアを具備した第1の実施の形態における回路基板の断面模式図

【図12】本発明の第2の実施の形態で得られた4層の回路基板の断面模式図

【符号の説明】

101 補強材シート

102a ガラス織布のよこ糸

102b ガラス織布のたて糸

103,104,701,702 インナービア

201 ガラスエポキシプリプレグ

202,304,604 カバーフィルム

203,203’ インナービアホール(貫通孔)

204,306,606 導電ペースト

205 接続中間体

206,307,607 金属箔

207,209,302,308,608 配線パターン

208 両面回路基板

210,403 埋設された配線層(配線パターン)

211 キャリア付金属箔

301 プリプレグ

303 支持基板(キャリア)

305 ブラインドビアホール(非貫通孔)

401,501 コア基板

402 第1の実施の形態の回路基板

502 薄い絶縁体層による回路基板

601 ポリイミドフィルム

602 接着剤層

603 薄い絶縁体層

605 キャリア付配線パターン

609 両面回路転写材

610 多層回路転写材中間体

611 多層回路転写材

612 第1または2の実施の形態の回路基板(コア基板)

613 接続中間体

614 両面回路転写材中間体

701 大きな径のインナービアホール

702 小さな径のインナービアホール

703 数が少ない突出したガラス繊維

704 数が多い突出したガラス繊維[0001]

TECHNICAL FIELD OF THE INVENTION

The present invention relates to a circuit board and a method for manufacturing the same. In particular, the present invention relates to a circuit board using a reinforcing sheet having a density difference in a plane direction and a method of manufacturing the same.

[0002]

[Prior art]

2. Description of the Related Art In recent years, as electronic devices have become smaller and lighter and have higher functions and higher performance, multilayer circuit boards on which semiconductor chips such as large-scale integrated circuits (LSIs) can be mounted at a high density not only in industrial applications but also in the field of consumer devices. There is a strong demand for inexpensive supplies.

[0003]

In response to such market demands, technology development has been developed to make a resin multilayer circuit board that can be supplied at lower cost, instead of a conventional ceramic multilayer board, a board suitable for high-density mounting (high-density wiring board). Has been done.

[0004]

As such a circuit board, there is a resin multilayer board having an all-layer inner via hole structure disclosed in JP-A-6-268345. This is a multi-resin multilayer board that adopts an inner via connection method that can connect an arbitrary position of an arbitrary wiring layer with a conductive paste, that is, an all-layer inner via hole structure, and provides a circuit board suitable for high-density mounting at low cost. You can do it.

[0005]

In this method of manufacturing a circuit board, first, an inner via hole is formed in a compressible insulator layer (aramid epoxy prepreg), and a through-hole is filled with a conductive paste. Then, the copper foil is placed on both sides and heated and pressed by a hot press to cure the insulating layer and the conductive paste resin, thereby bonding the copper foil and the insulating layer. To establish a connection. Finally, the copper foil on both sides is processed into a wiring pattern to complete a double-sided circuit board.

[0006]

This substrate achieves high-density wiring and low and low-variation connection resistance, and has been highly evaluated by the market.

[0007]

The necessity of the high-density wiring is as described above, but the usefulness of the connection resistance with little variation is as follows. That is, the circuit resistance including the connection resistance is an important parameter in circuit design.If the circuit resistance differs for each product, the circuit cannot be designed, or the circuit resistance of the product will deviate from the design value and will operate. Failures, such as no, occur. For this reason, the connection resistance is required to have little variation.

[0008]

In particular, in connection using inner vias, the number of inner vias involved in one circuit increases compared to connection using conventional through-holes, so that the requirement for variation becomes severe.

[0009]

However, the circuit board technology having the all-layer inner via hole structure has the following problems. In other words, although a composite material of an aramid nonwoven fabric reinforcing material and an epoxy resin (aramid epoxy base material) is used for the insulator layer, the aramid fiber is a material that easily absorbs moisture. The problem is that such management leads to increased costs.

[0010]

On the other hand, a glass epoxy base material used for a general circuit board is a base material obtained by impregnating a glass fiber woven fabric with an epoxy resin, and since glass fiber does not absorb moisture, it is advantageous in terms of moisture absorption management. Further, since there is also an advantage that the mechanical strength is high, it has been desired to realize a circuit board having an all-layer inner via hole structure of inner via connection using a glass epoxy base material as an insulating layer.

[0011]

However, there is a problem that if the above-described all-layer inner via hole technique is simply applied to a glass epoxy base material, the variation in connection resistance of the inner via becomes large. This is due to the fact that the glass woven fabric of the reinforcing material has a variation in density in the in-plane direction (a portion where warp and weft are woven and a portion where it is not overlapped) as a result of the study by the present inventors. understood. In detail, when heating and pressing in the hot pressing process, the inner via provided in the place where the density of the reinforcing material is low (where the warp and weft yarns are not woven and overlapped) has little reinforcing material on the side wall surface. The inner via spreads in the lateral direction, that is, the press pressure is dissipated in the lateral direction. For this reason, it was found that a sufficient compressive force was not applied in the vertical direction of the inner via, and the electrical connection was not sufficiently performed between the conductors, thereby increasing the electrical connection resistance.

[0012]

The above-described variation in the electrical connection resistance is problematic not only in glass cloth impregnated with an epoxy resin but also in nonwoven fabrics, sheets, and films due to uneven thickness and density in the plane direction.

[0013]

[Problems to be solved by the invention]

The present invention has been made in order to solve the above-mentioned problems, and for example, a base material containing a reinforcing material sheet having a density distribution in a planar direction such as a glass epoxy base material is used for an insulator layer. Even in such a case, it is an object of the present invention to provide a circuit board which realizes an inner via connection resistance with high density wiring and little variation, and a method of manufacturing the same.

[0014]

[Means for Solving the Problems]

In order to achieve the above object, a circuit board of the present invention has a reinforcing material sheet having a density distribution in a planar direction.includingAn electric insulator layer, a circuit board comprising a wiring layer filled with a conductor in a plurality of inner via holes opened in a thickness direction of the electric insulator layer, and a wiring layer connected to the conductor,

A cross-sectional area of the inner via hole provided in a portion where the density of the reinforcing material sheet is large is formed to be smaller than a cross-sectional area of the inner via hole provided in a portion where the density of the reinforcing material sheet is small. .

Further, another circuit board of the present invention includes an electric insulator layer including a reinforcing material sheet having a density distribution in a plane direction, and a first material filled with an electric conductor, which is spaced in the thickness direction of the electric insulator layer. And the inner beer hall,

A second inner via hole having a cross-sectional area larger than the cross-sectional area of the first via hole, the second inner via hole being filled in the thickness direction of the electric insulator layer and filled with a conductor;

A third inner via hole having a cross-sectional area larger than the cross-sectional area of the second via hole, the third inner via hole being filled in the thickness direction of the electric insulator layer, filled with a conductor,

The density of the reinforcing material sheet in the portion where the second inner via hole is provided is higher than the density of the reinforcing material sheet in the portion where the third via hole is provided,

It is characterized in that the density of the reinforcing material sheet in the portion where the first inner via hole is provided is higher than the density of the reinforcing material sheet in the portion where the second via hole is provided.

[0015]

Next, the method of manufacturing a circuit board of the present invention, when forming a plurality of inner via holes for filling a conductor in the insulator layer including a reinforcing material sheet having a density distribution in the planar direction,

The cross-sectional area of the inner via hole provided in the portion where the density of the reinforcing material sheet is large is formed smaller than the cross-sectional area of the inner via hole provided in the portion where the density of the reinforcing material sheet is small,

Next, a conductor is filled in the inner via hole,

The conductiveOn the bodyThe method includes laminating a wiring layer or a metal foil for forming a wiring layer so as to be connected, and applying heat and pressure.

[0016]

BEST MODE FOR CARRYING OUT THE INVENTION

In the connection resistance of the inner via, in the type in which the conductive paste is used for pressure contact, when the ratio of (insulator layer thickness / via diameter) becomes larger than 1, the connection resistance becomes abruptly unstable and the variation increases. Therefore, in order to realize a small-diameter via (for example, a diameter of 50 μm) of the circuit board, it is preferable that the thickness of the insulator layer be 50 μm or less. However, the core circuit board usually has a thickness of 50 μm or more when using a glass epoxy substrate, an aramid epoxy substrate, or the like. Further, if the core substrate is too thin, the mechanical strength decreases, which is not preferable. Therefore, the thickness of the thin insulator layer is preferably 50 μm or less, and the ratio of the thickness of the insulator layer / the diameter of the via is preferably 1 or less.

[0017]

In the present invention, the reinforcing material sheet having a density distribution in the plane direction is preferably a woven or non-woven fabric composed of at least one fiber selected from synthetic fibers and inorganic fibers..

[0018]

Further, the reinforcing material sheet having a density distribution in the plane direction is preferably a woven fabric made of glass fiber.

[0019]

Further, it is preferable that the cross-sectional area of the inner via provided in the overlapping portion of the warp and the weft of the woven fabric made of glass fiber is smaller than the cross-sectional area of the inner via provided in other portions.

[0020]

Further, it is preferable that the amount of protrusion of the protruding fiber on the side wall surface of the inner via hole having a small cross-sectional area is larger than the amount of protrusion of the protruding fiber on the side wall surface of the inner via hole having a large cross-sectional area.

[0021]

It is preferable that a plurality of wiring layers exist, and at least one of the wiring layers is embedded in the insulator layer.

[0022]

Further, it is preferable that the cross-sectional area of the inner via is small where the density of the reinforcing material sheet is high, and that the cross-sectional area of the inner via is large where the density of the reinforcing material sheet is low.

[0023]

Further, a circuit board made of a compressible electric insulating material may be further laminated on one surface of the circuit board of the present invention.

[0024]

Further, the circuit boards of the present invention may be arranged on both outer sides, and a circuit board made of a compressible electric insulating material may be further laminated between the outer sides as a core board.

[0025]

Further, the circuit board of the present invention may be a core board, and at least one circuit board made of an insulator layer thinner than the insulator layer of the core board may be laminated on at least one surface of the core board.

[0026]

The large cross-sectional area of the inner via hole is preferably 1.15 to 10 times, more preferably 1.4 to 5 times, and particularly preferably 1.4 to 2 times, as compared with the small cross-sectional area. The area is as follows. If it is less than 1.15 times, it is difficult to reduce the variation in electric resistance depending on the density difference of the reinforcing sheet, and if it exceeds 10 times, the via resistance becomes too low and it becomes difficult to reduce the variation in via resistance. .

[0027]

Next, in the method of the present invention, a method of forming a cross-sectional area of an inner via hole provided in a portion where the density of the reinforcing material sheet is large is smaller than a cross-sectional area of an inner via hole provided in a portion where the density of the reinforcing material sheet is small, It is preferable to insert a rotary drill in the thickness direction of the reinforcing sheet to form a through hole, temporarily stop the drill while rotating, and then pull out the drill.

[0028]

A method of forming a cross-sectional area of an inner via hole provided in a portion where the density of the reinforcing material sheet is large is smaller than a cross-sectional area of an inner via hole provided in a portion where the density of the reinforcing material sheet is low is a laser processing method of a thermal processing type. It is preferable that

[0029]

Further, it is preferable that there are a plurality of wiring layers, and at least one of the wiring layers is embedded in the insulator layer.

[0030]

In the above, in the case of the glass epoxy base material, the ratio of the cross-sectional area of the via is preferably 1.15 times or more, more preferably, in the portion where the warp yarn and the weft yarn of the glass cloth overlap and the portion where the eyes of the glass cloth are open. Is 1.4 times or more. Within this range, the variation in via resistance is reduced.

[0031]

ADVANTAGE OF THE INVENTION According to the circuit board of this invention, the circuit board provided with the connection resistance with little variation can be realized.

[0032]

According to another circuit board of the present invention, a circuit board having a connection resistance with little variation and a high connection reliability can be realized.

[0033]

In another circuit board of the present invention, it is preferable that at least one wiring layer is embedded in the insulator layer. According to this example, it is possible to realize a circuit board having a connection resistance with less variation.

[0034]

Next, according to the multilayer circuit board of the present invention, it is possible to realize a multilayer circuit board having connection resistance with less variation over all layers.

[0035]

Next, according to the multilayer circuit board of the present invention, it is possible to realize a multilayer circuit board having a fine wiring layer on a surface layer, using a circuit board having connection resistance with little variation as a core board.

[0036]

Next, according to the circuit board manufacturing method of the present invention, it is possible to easily realize the manufacture of a circuit board having a connection resistance with little variation.

[0037]

The method for manufacturing a first circuit board of the present invention preferably includes a step of embedding at least one wiring layer in the insulator layer. According to this example, it is possible to easily manufacture a circuit board having a connection resistance with less variation.

[0038]

Next, according to the method for manufacturing a multilayer circuit board of the present invention, it is possible to easily manufacture a multilayer circuit board having connection resistances with little variation over all layers.

[0039]

Next, according to the method of manufacturing a multilayer circuit board of the present invention, it is possible to easily realize the manufacture of a multilayer circuit board having a fine wiring layer on the surface layer, using a circuit board having connection resistance with little variation as a core board.

[0040]

First, the materials used in the present invention will be described.

[0041]

(Electric conductor for inner via formation)

As the conductor forming the inner via, a resin composition (conductive paste) containing conductive powder can be used. The conductive paste is preferable because the conductivity is improved by compression.

[0042]

As the conductive filler, a filler made of at least one metal selected from gold, silver, copper, nickel, palladium, lead, tin, indium, and bismuth, an alloy thereof, or a mixture thereof can be used. Further, a coat filler obtained by coating a ball made of the above-mentioned metal or alloy, an oxide such as alumina or silica, or an organic synthetic resin with the above-mentioned metal or alloy can also be used.

[0043]

The shape is not particularly limited, but powder, fibrous filler, granulated powder, spherical ball, or a mixture thereof can be used.

[0044]

As a resin used as a binder of the resin composition, a liquid epoxy resin, a polyimide resin, a cyanate ester resin, a phenol resole resin, or the like can be used. Examples of the epoxy resin include glycidyl ether type epoxy resins such as bisphenol A type epoxy resin, bisphenol F type epoxy resin, bisphenol AD type epoxy resin, alicyclic epoxy resin, glycidylamine type epoxy resin and glycidyl ester type epoxy resin. An epoxy resin containing two or more groups can be used. Also, an epoxy compound having one epoxy group can be contained as a reactive diluent.

[0045]

If necessary, additives such as solvents and dispersants such as butyl cellosolve, ethyl cellosolve, butyl carbitol, ethyl carbitol, butyl carbitol acetate, ethyl carbitol acetate and α-terpineol can also be contained. .

[0046]

Further, the conductor of the present invention is not limited to the above-described conductive paste, and may be electrically connected by pressure welding, such as via posts made of metal such as gold, silver, copper, nickel, palladium, lead, tin, indium, and bismuth. Can be used.

[0047]

(Electric insulator layer with density distribution in the plane direction)

As a material of the electric insulator layer having a density distribution in the plane direction, a glass epoxy base material can be given. The glass epoxy base material is a composite material obtained by impregnating a glass woven fabric with an epoxy resin, and B-stage (semi-cured) and C-stage (cured) materials are commercially available as circuit board materials. It is preferable because it has excellent mechanical strength and can be obtained at low cost. Among them, it is preferable to use a B-stage (semi-cured state) substrate rather than a C-stage (cured state) substrate. The semi-cured state is easier to drill with a laser than the cured state of the resin, the difference in workability with the glass cloth of the reinforcing material is large, and the semi-cured state is more effective for compressing the conductive paste. This is because the pressure is small. However, the electric insulator layer is not limited to this example of the base material, and an insulator layer containing a reinforcing material sheet having a density distribution (density difference) in a planar direction can be used. Examples include PBO (polyparaphenylene benzobisoxazole) fiber, PBI (polybenzimidazole) fiber, aramid fiber, PTFE (polytetrafluoroethylene) fiber, PBZT (polyparaphenylene benzobisthiazole) fiber or wholly aromatic polyester Epoxy resin, polyimide resin, phenol resin, fluorine resin, unsaturated polyester resin, PPE (polyphenylene ether) resin, bismaleimide triazine resin for woven or non-woven fabrics made of organic fibers such as fibers or inorganic fibers such as glass fibers Or, a composite sheet impregnated with a thermosetting resin such as a cyanate ester resin or a thermoplastic resin.GoodIt is possible to use any of them.

[0048]

Although the thickness of the electric insulator layer is not particularly limited, a commercially available one having a thickness of about 0.02 mm to 0.5 mm can be used. The weight per unit area of the insulator layer is 50 g / m2800 g / m or more2The following ranges are preferred.

[0049]

(Cover film)

The cover film functions as a mask for preventing contamination by dust and filling the conductor during the manufacturing process, and is finally removed. For this reason, it is preferable to arrange a cover film on at least the side of the prepreg where the conductor is filled. Further, it is preferable to perform a mold release treatment on the surface that comes into contact with the prepreg. The material of the cover film is not limited. For example, a PET (polyethylene terephthalate) film or a PEN (polyethylene naphthalate) film coated with a silicone release agent can be used. Further, when the conductive paste is filled by the printing method, the inner paste is additionally filled with the conductive paste by the thickness of the cover film. Finally, when the film is peeled off, the conductive paste has a structure in which the conductive paste protrudes from the inner via. In the hot pressing step, the protruding portion has a thickness to be compressed. For this reason, as the thickness increases, the inner vias are more compressed and a lower connection resistance can be realized. On the other hand, when the thickness is too large, the conductive paste is taken on the cover film when peeling. For example, the thickness is preferably 35 μm or less for a pore diameter of 200 μm or less, and preferably 20 μm or less for a pore diameter of 100 μm or less.

[0050]

(Metal foil)

As a specific example of the metal foil, an electrolytic copper foil or a rolled copper foil can be used. As examples of the electrolytic copper foil, those having a thickness of about 3 μm to 70 μm are commercially available, and these can be used. If the thickness is small, particularly 9 μm or less, a copper foil provided with a support carrier can be used for handling. The surface roughness of the metal foil is, for example, an average roughness Rz in a range of 0.5 to 10 μm.

[0051]

Next, embodiments of the present invention will be described with reference to the drawings.

[0052]

(Embodiment 1)

FIG. 1 is a schematic plan view of the circuit board according to the first embodiment. In this embodiment, a case where a glass epoxy substrate is used for an insulator layer containing a reinforcing

[0053]

The circuit board of this embodiment can be manufactured as follows.

[0054]

First, a connection intermediate is produced. The

[0055]

Next, the inner via hole is filled with a

[0056]

As an example of the hole processing conditions in FIG. 2A, the through

[0057]

In this case, where the fiber is dense, the fiber is stretched and the

[0058]

In normal circuit board fabrication, it is common to raise the drill immediately after the drill has penetrated the material. This is for hole quality (meaning that the hole diameter is the same), prevention of drill breakage, and tact-up. In this case, a substantially constant hole is formed regardless of the density of the fibers.

[0059]

For example, when the hole processing of this embodiment was performed using a prepreg having a thickness of about 70 μm, the hole diameter was 150 μm in the portion where the warp yarn and the weft yarn of glass cloth were woven and overlapped (the highest density portion of the glass fiber). In the open part of the cloth (the part where the density of the glass fiber is the lowest), the pore diameter was 180 μm, and in other places, the pore diameter was smaller in inverse proportion to the density of the glass fiber between 150 μm and 180 μm. The hole provided at the place where the standing yarns and the weft yarns of the fiber yarns constituting the glass cloth overlap was smaller than the hole diameter that can be accommodated in the weaving overlap.

[0060]

Next, a

[0061]

Finally, the metal foil was processed into a

[0062]

The connection resistance of the inner via decreases as the cross-sectional area of the inner via increases. Also, as the effective pressure applied to the conductive fillers (the conductive filler and the copper foil) increases, the number of contacts increases and the size of each contact also increases, and the connection resistance decreases. In order to increase the effective pressure, it is necessary to increase the pressure of the hot press and at the same time, to make the side wall surface of the inner via hole not widen. Here, the configuration in which the side wall surface does not spread laterally means that, in the case of the present embodiment, the hole provided in the place where the glass cloth is overlapped has a size not larger than the hole diameter that can be accommodated in the overlap. .

[0063]

In the present embodiment, the portion with the highest density of the reinforcing material (the portion where the fibers of the glass cloth are woven and overlapped) has an inner via hole (through hole) with a diameter of 150 μm because the side wall surface is hard to spread, and the density of the reinforcing material is In the smallest part (open part of the glass cloth), the effective pressure is the least applied, so the hole diameter is 180 μm, and in the other parts, the hole diameter is 150 to 180 μm, which is small in inverse proportion to the density of the glass fiber. It is. With the inner via of the present embodiment manufactured under the above-described hole processing conditions, a connection resistance with a very small variation of about 2 to 3 mΩ can be realized. The hole diameter of the inner via hole is not limited to the hole diameter described above.

[0064]

Using the double-

[0065]

A further multilayer substrate can be manufactured by repeating the above-described lamination process using the multilayer substrate as the core substrate.

[0066]

In the multilayer board of the present embodiment, the wiring layers 207 of the core board are embedded in the prepregs stacked on both sides of the core board. That is, since the wiring layer is buried also in the inner via portion, the compression ratio of the inner via during the pressing step is increased, and the connection resistance can be further reduced and the variation can be reduced.

[0067]

Also, the wiring layer can be embedded in the double-sided circuit board by using the wiring transfer method, and similarly, a lower and less variable connection resistance can be realized. Specifically, a so-called metal foil with a carrier in which a metal foil is formed on a supporting substrate (carrier) as shown in FIG. 4A can be used. As an example of the

[0068]

As a method of forming a through hole using the mechanical drill according to the present embodiment, a drill having a different diameter can be used as well as the above. In other words, the inner via hole provided in the portion other than the woven portion of the glass fiber (the portion where the density of the reinforcing material sheet is large) has a smaller diameter than that provided in the woven portion (the portion where the density of the reinforcing material sheet is large). Use a drill. When the density distribution of the reinforcing material is irregular, it is necessary to select the drill diameter according to the density distribution for each work. Such an extra step is not required (or is simple and simple), which is preferable.

[0069]

As a method of forming a through hole, other than the above, a hole forming method for a normal circuit board, that is, a laser hole forming method such as carbon dioxide gas, YAG, excimer, or punching may also be used. Via holes (through holes) can be formed.

[0070]

Next, as shown in FIG. 11, when the through-holes are formed by the carbon dioxide laser drilling method, the inner vias (inner vias with a small hole diameter) 702 formed in the portion where the density of the glass fiber is large include many pieces of glass. The

[0071]

As an example using a carbon dioxide laser, a carbon dioxide laser having a wavelength of 9.4 μm or 10.6 μm can be used. An appropriate number of shots is one to three. In such an example, the effect of the present invention was more remarkable as the wavelength was longer and the number of shots was smaller. Drilling utilizes a difference in workability due to a difference in density distribution of the glass cloth substrate when the same laser is irradiated. This relationship is as shown in Table 1 below.

[0072]

[Table 1]

[0073]

Next, the wavelength of the laser beam will be described. In general, if the laser has the same energy, the shorter the wavelength, the smaller the laser spot diameter becomes. As a result, the energy density of the laser increases. With a laser with a large energy density, it is generally easy to make holes in a sheet using glass cloth, which is a material that is difficult to make holes, and it is possible to make holes with a small diameter regardless of the density distribution of the base material. Can be formed. Conversely, when the wavelength is short, the spot diameter of the laser increases, and as a result, the energy density decreases. For this reason, the holes of the matrix resin, which is a material that is easy to make holes, are easy to make holes, but the holes of the glass cloth are hard to make holes, and are easily affected by the density distribution of the base material. That is, a portion where the warp yarn and the weft yarn of the glass cloth overlap is a small hole, and a portion where the texture is open is a large hole. Therefore, it is preferable that the wavelength of the laser beam is long.

[0074]

Next, the number of shots will be described. In laser irradiation, the greater the number of shots, the greater the total energy input. For example, two shots have twice the total energy amount of one shot. For this reason, if the same location is shot a plurality of times, the total amount of energy increases, and the glass cloth that could not be processed in the first shot is also sequentially drilled in the second and third shots, and the glass cloth is changed according to the density distribution of the substrate. The hole diameter becomes uniform. Conversely, if the number of shots is small, the influence of the density distribution of the base material is increased. That is, a portion where the warp yarn and the weft yarn of the glass cloth overlap is a small hole, and a portion where the texture is open is a large hole. Therefore, the appropriate number of shots is one to three.

[0075]

In the present embodiment, the inner via hole has been described as a through hole, but may be a non-through hole. The method of producing the circuit board in the case of a non-through hole is as shown in FIGS. 5A to 5D.

[0076]

First, the

[0077]

(Embodiment 2)

FIG. 6 is a schematic sectional view of a multilayer circuit board according to a second embodiment of the present invention. The multilayer board of the present embodiment has a configuration in which the circuit board described in Embodiment 1 is laminated on at least one surface of a core board made of a compressible insulating base material. In the figure, a double-

[0078]

The multilayer circuit board of the present embodiment can be manufactured as follows.

[0079]

First, a double-sided circuit board is manufactured using aramid epoxy prepreg. In the method for producing a double-sided circuit board, first, cover films are temporarily pressure-bonded to both sides of an aramid epoxy prepreg to form through holes. The through-hole can be formed, for example, with a carbon dioxide laser and having a hole diameter of 200 μm. Aramid epoxy prepreg is a composite material in which an aramid fiber nonwoven fabric is impregnated with an epoxy resin and has compressibility due to the presence of a large number of voids therein. A connection resistance with little variation can be realized. Of course, as shown in the embodiment, it is needless to say that it is preferable to change the pore diameter depending on the density of the reinforcing material (in this case, the aramid nonwoven fabric), because the variation is further reduced.

[0080]

Next, if the cover film is removed by filling the through-hole with the conductive paste, the connection intermediate using the aramid epoxy base material is completed. Thereafter, a double-sided circuit board of an aramid epoxy board can be obtained as in the first embodiment. Further, the through holes may be formed using a laser or a drill.

[0081]

Using this as a core substrate, the connection intermediate described in the first embodiment and the metal foil are overlapped from both sides, and laminated by hot pressing as in the first embodiment, and the metal foil is processed into a wiring pattern. Thus, a four-layer substrate (here, four layers means a wiring layer) is completed. The compressible core substrate may be a multilayer circuit substrate. FIG. 12 shows an example in which the core substrate has four wiring layers.

[0082]

When a higher multilayer is required, the multi-layer substrate can be manufactured by repeating the steps of the present embodiment using the multilayer substrate of the present embodiment as a core substrate.

[0083]

In the multilayer board of the present embodiment, the wiring layer is embedded in all of the insulator layers made of the glass epoxy base material. As described in the first embodiment, the connection resistance with less variation is further reduced. realizable. Although the wiring layer is not embedded in the core substrate, the compressibility of the aramid epoxy prepreg compensates for this, and the inner via is sufficiently compressed. That is, the multilayer circuit board according to the present embodiment can realize connection resistance with less variation over all layers. Further, when the glass epoxy base material is laminated on both sides, the aramid epoxy base material is not exposed to the outside, and the structure is hard to absorb moisture. In addition, since the glass epoxy substrate has excellent mechanical strength, a substrate having excellent mechanical strength can be realized as compared with a multilayer substrate composed of only an aramid epoxy substrate.

[0084]

(Embodiment 3)

FIG. 7 is a schematic sectional view of a multilayer substrate according to a third embodiment of the present invention. The multilayer board of the present embodiment has a

[0085]

A case in which the four-layer multilayer substrate of Embodiment 2 is used as a core substrate and a polyimide film is used as an insulator layer thinner than the insulator layer of the core substrate will be described.

[0086]

The multilayer substrate of the present embodiment can be manufactured as follows. First, a method for forming a substrate of an insulator layer using a polyimide film will be described. As shown in FIG. 8A, a

[0087]

Next, as shown in FIG. 8C, a non-through hole is formed in the film, the

[0088]

As the conductor, a conductive paste can be used as in Embodiment 1. The conductive paste can be filled by a printing method using a squeegee. In filling the non-through holes, it is preferable to reduce the pressure during filling or after filling. This is to remove the air bubbles that have entered when the paste is filled from the opening by reducing the pressure. The copper foil is made of a roughened copper foil having irregularities on the surface, and has a gap between it and the adhesive layer (a minute gap corresponding to the unevenness of the copper foil surface, which is smaller than the conductive filler of the conductive paste). It is preferable to perform temporary compression bonding while leaving This is because the resin of the conductive paste is discharged from this gap at the time of filling and pressing of the conductive paste, the ratio of the conductive powder in the inner via is increased, and further low resistance is obtained.

[0089]

Next, as shown in FIG. 8D, a

[0090]

Next, the metal foil is processed into a

[0091]

By repeating the above process using the double-sided circuit transfer material with

[0092]

Although the case where a polyimide film is used as an insulator layer thinner than the insulator layer of the core substrate has been described, BCB (benzocyclobutene), PTFE (polytetrafluoroethylene), aramid, PBO (polyparaphenylenebenzobisoxazole) or An adhesive may be formed on a film such as a wholly aromatic polyester and used. In the case of a thermoplastic film, it can be used without an adhesive because the film itself has adhesiveness when heated.

[0093]

Next, a transfer material is laminated on the core substrate.

[0094]

As the core substrate, the

[0095]

Also, instead of using the transfer material intermediate, the (multi-layer)

[0096]

In this embodiment mode, a method of transferring a thin insulator layer to a core substrate with a wiring transfer material has been described. According to this method, a finer circuit formed on the thin insulator layer and a core substrate are separately manufactured. Therefore, as compared with the method of sequentially stacking on the core substrate, contamination of fine circuit portions by dust can be reduced, and the overall yield can be improved.

[0097]

In the multilayer circuit board of the present embodiment, a circuit board having an all-layer IVH structure having a connection resistance with little variation described in Embodiments 1 and 2 is used as a core substrate, and a higher-density wiring layer is formed thereon. it can. It is difficult to use a substrate made of only a thin polyimide film insulator layer in a field where mechanical strength is required. However, the multilayer substrate of this embodiment has a mechanical strength and a high-density fine wiring (core substrate). (Including parts), and is particularly suitable for a package substrate for directly mounting a relatively large semiconductor.

[0098]

As the core substrate, a general circuit substrate (a glass epoxy through-hole substrate, a build-up substrate, a multilayer substrate using an aramid fiber nonwoven fabric impregnated with an epoxy resin, or the like) may be used. Further, as shown in the figure, the transfer material can be directly laminated on a metal foil for wiring formation via a connection intermediate.

[0099]

【The invention's effect】

According to the present invention, even when a base material containing a reinforcing material sheet having a density distribution in a planar direction such as a glass epoxy base material is used for an insulator layer, an inner wiring with high density wiring and little variation is used. A circuit board realizing a via connection resistance and a manufacturing method thereof can be provided.

[Brief description of the drawings]

FIG. 1 is a schematic plan view of a circuit board according to a first embodiment of the present invention.

FIGS. 2A to 2D are explanatory views of each step of a circuit board manufacturing method (through-hole) according to the first embodiment of the present invention; FIGS.

FIGS. 3A and 3B are explanatory diagrams of each step of a method (through-hole) of manufacturing a circuit board according to the first embodiment of the present invention; FIGS.

FIGS. 4A and 4B are explanatory views of each step of a method for manufacturing a circuit board (through-hole) according to the first embodiment of the present invention; FIGS.

FIGS. 5A to 5D are explanatory diagrams of a circuit board manufacturing method (non-through holes) according to the first embodiment of the present invention; FIGS.

FIG. 6 is a schematic cross-sectional view of a multilayer circuit board according to a second embodiment of the present invention.

FIG. 7 is a schematic cross-sectional view of a multilayer circuit board according to a third embodiment of the present invention.

FIGS. 8A to 8D are explanatory diagrams of a method for manufacturing a multilayer circuit board according to a third embodiment of the present invention.

9A to 9C are explanatory diagrams of a method for manufacturing a multilayer circuit board according to a third embodiment of the present invention.

FIGS. 10A and 10B are explanatory diagrams of a method of manufacturing a multilayer circuit board according to a third embodiment of the present invention. FIGS.

FIG. 11 is a schematic cross-sectional view of a circuit board according to the first embodiment having an inner via from which glass fibers protrude according to the present invention.

FIG. 12 is a schematic cross-sectional view of a four-layer circuit board obtained in a second embodiment of the present invention.

[Explanation of symbols]

101 Reinforcement sheet

102a Glass woven weft

102b Warp yarn of glass woven cloth

103, 104, 701, 702 Inner via

201 Glass epoxy prepreg

202, 304, 604 Cover film

203, 203 'inner via hole (through hole)

204, 306, 606 conductive paste

205 Connection intermediate

206, 307, 607 Metal foil

207, 209, 302, 308, 608 Wiring pattern

208 Double-sided circuit board

210,403 embedded wiring layer (wiring pattern)

211 Metal foil with carrier

301 Prepreg

303 Supporting substrate (carrier)

305 Blind via hole (non-through hole)

401,501 core substrate

402 Circuit Board of First Embodiment

502 Circuit board with thin insulator layer

601 Polyimide film

602 adhesive layer

603 thin insulator layer

605 Wiring pattern with carrier

609 Double-sided circuit transfer material

610 Multi-layer circuit transfer material intermediate

611 Multi-layer circuit transfer material

612 Circuit Board (Core Board) of First or Second Embodiment

613 connection intermediate

614 Double-sided circuit transfer material intermediate

701 Large inner via hole

702 Inner via hole with small diameter

703 few protruding glass fibers

704 many protruding glass fibers

Claims (19)

前記補強材シートの密度の大きな部分に設けるインナービアホールの断面積を、前記補強材シートの密度の小さな部分に設けるインナービアホールの断面積より小さく形成し、

次に前記インナービアホールに導電体を充填し、

前記導電体に接続するように配線層または配線層を形成するための金属箔から選ばれる少なくとも一つを積層し、加熱加圧することを含むことを特徴とする回路基板の製造方法。When forming a plurality of inner via holes for filling the conductor in the insulator layer including a reinforcing material sheet having a density distribution in the planar direction,

The cross-sectional area of the inner via hole provided in the portion where the density of the reinforcing material sheet is large is formed smaller than the cross-sectional area of the inner via hole provided in the portion where the density of the reinforcing material sheet is small,

Next, a conductor is filled in the inner via hole,

A method of manufacturing a circuit board, comprising laminating at least one selected from a wiring layer or a metal foil for forming a wiring layer so as to be connected to the conductor, and applying heat and pressure.

前記電気絶縁体層の厚さ方向に空けられ、導電体が充填され、第2のビアホールの断面積より大きな断面積を有する第3のインナービアホールと、を備え、

第3のビアホールが設けられた部分の補強材シートの密度より、第2のインナービアホールが設けられた部分の補強材シートの密度が大きく、

第2のビアホールが設けられた部分の補強材シートの密度より、第1のインナービアホールが設けられた部分の補強材シートの密度が大きい回路基板。An electrical insulator layer including a reinforcing material sheet having a density distribution in a planar direction; a first inner via hole that is opened in a thickness direction of the electrical insulator layer and is filled with a conductor; A second inner via hole that is vacated in the thickness direction, is filled with a conductor, and has a cross-sectional area larger than the cross-sectional area of the first via hole;

A third inner via hole having a cross-sectional area larger than the cross-sectional area of the second via hole, the third inner via hole being filled in the thickness direction of the electric insulator layer, filled with a conductor,

The density of the reinforcing material sheet in the portion where the second inner via hole is provided is higher than the density of the reinforcing material sheet in the portion where the third via hole is provided,

A circuit board wherein the density of the reinforcing material sheet in the portion where the first inner via hole is provided is higher than the density of the reinforcing material sheet in the portion where the second via hole is provided.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001344073A JP3587457B2 (en) | 2000-11-09 | 2001-11-09 | Circuit board and its manufacturing method |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000-341646 | 2000-11-09 | ||

| JP2000341646 | 2000-11-09 | ||

| JP2001344073A JP3587457B2 (en) | 2000-11-09 | 2001-11-09 | Circuit board and its manufacturing method |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002208763A JP2002208763A (en) | 2002-07-26 |

| JP2002208763A5 JP2002208763A5 (en) | 2004-10-28 |

| JP3587457B2 true JP3587457B2 (en) | 2004-11-10 |

Family

ID=26603641

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001344073A Expired - Fee Related JP3587457B2 (en) | 2000-11-09 | 2001-11-09 | Circuit board and its manufacturing method |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3587457B2 (en) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4054269B2 (en) | 2003-03-20 | 2008-02-27 | Tdk株式会社 | Electronic component manufacturing method and electronic component |

| EP2056655B1 (en) | 2007-09-03 | 2012-06-20 | Panasonic Corporation | Wiring board |

| JP5284146B2 (en) * | 2008-03-13 | 2013-09-11 | 日本特殊陶業株式会社 | Multilayer wiring board and manufacturing method thereof |

| JP2011119611A (en) * | 2009-12-07 | 2011-06-16 | Furukawa Electric Co Ltd:The | Injection-molded substrate and injection-molded component |

| JP2013157366A (en) | 2012-01-27 | 2013-08-15 | Kyocer Slc Technologies Corp | Wiring board and packaging structure including the same |

| JP6301595B2 (en) * | 2013-06-14 | 2018-03-28 | 日本特殊陶業株式会社 | Wiring board and method for manufacturing multilayer wiring board |

| KR102149793B1 (en) * | 2013-10-24 | 2020-08-31 | 삼성전기주식회사 | Printed circuit board and control method of warpage of printed circuit board |

| JP7128857B2 (en) * | 2020-06-02 | 2022-08-31 | Fict株式会社 | CIRCUIT BOARD, CIRCUIT BOARD MANUFACTURING METHOD, AND ELECTRONIC DEVICE |

| WO2023013348A1 (en) * | 2021-08-05 | 2023-02-09 | 住友電気工業株式会社 | Optical module, optical connector cable, and method for producing optical module |

-

2001

- 2001-11-09 JP JP2001344073A patent/JP3587457B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002208763A (en) | 2002-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6996902B2 (en) | Method for manufacturing a circuit board | |

| US6799369B2 (en) | Printed circuit board and method for producing the same | |

| US6518514B2 (en) | Circuit board and production of the same | |

| US5888627A (en) | Printed circuit board and method for the manufacture of same | |

| US7572500B2 (en) | Method of manufacturing circuit-forming board and material of circuit-forming board | |

| WO2001045478A1 (en) | Multilayered printed wiring board and production method therefor | |

| JP2587596B2 (en) | Circuit board connecting material and method for manufacturing multilayer circuit board using the same | |

| US20080308304A1 (en) | Multilayer Wiring Board and Its Manufacturing Method | |

| JP3587457B2 (en) | Circuit board and its manufacturing method | |

| WO2002034023A1 (en) | Circuit forming board producing method, circuit forming board, and material for circuit forming board | |

| TW517504B (en) | Circuit board and a method of manufacturing the same | |

| KR20080045824A (en) | Carbon fiber stiffener for printed circuit board | |

| JPWO2003009656A1 (en) | Circuit forming substrate manufacturing method and circuit forming substrate | |

| KR100775353B1 (en) | Method for processing carbon fiber stiffener for printed circuit board | |

| JP3640911B2 (en) | Circuit board and manufacturing method thereof | |

| JP2006348225A (en) | Composite, prepreg, metallic foil clad laminate and printed wiring substrate using the same, and method for manufacturing printed wiring substrate | |

| JP3695844B2 (en) | Manufacturing method of multilayer printed wiring board | |

| JP2002151813A (en) | Printing wiring board and its manufacturing method | |

| JP2000252631A (en) | Multilayer printed wiring board and its manufacture | |

| JP2003008220A (en) | Method of manufacturing circuit board | |

| JP2004349729A (en) | Circuit board and its producing process | |

| JP2004356324A (en) | Method and apparatus of manufacturing wiring board | |

| JP2004022873A (en) | Multilayer printed wiring board and its manufacturing method | |

| JP2004260196A (en) | Substrate material for circuit-forming and its manufacturing method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20040209 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040217 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040401 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040804 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040806 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20070820 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080820 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080820 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090820 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090820 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100820 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110820 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110820 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120820 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130820 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |