JP2023070990A - 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 - Google Patents

半導体発光素子、発光モジュール、及び発光モジュールの製造方法 Download PDFInfo

- Publication number

- JP2023070990A JP2023070990A JP2021183532A JP2021183532A JP2023070990A JP 2023070990 A JP2023070990 A JP 2023070990A JP 2021183532 A JP2021183532 A JP 2021183532A JP 2021183532 A JP2021183532 A JP 2021183532A JP 2023070990 A JP2023070990 A JP 2023070990A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- region

- light emitting

- bonding

- semiconductor light

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/04—Processes or apparatus for excitation, e.g. pumping, e.g. by electron beams

- H01S5/042—Electrical excitation ; Circuits therefor

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Optics & Photonics (AREA)

- Electromagnetism (AREA)

- Led Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Lasers (AREA)

Abstract

【課題】電気抵抗が低減された電極を備える半導体発光素子などを提供する。【解決手段】半導体発光素子10は、半導体積層体10Sと、半導体積層体10Sの上方に配置されるコンタクト電極40と、コンタクト電極40の上方に配置され、Auを含むパッド層50とを備え、パッド層50は、パッド層50とコンタクト電極40とが接する領域の上方に配置される第一層51aと、第一層51aの上方に配置され、第一層51aと接する第二層51bとを有し、コンタクト電極40の主面に平行な方向において、第二層51bにおけるAuの平均粒径は、第一層51aにおけるAuの平均粒径より大きい。【選択図】図1

Description

本開示は、半導体発光素子、発光モジュール、及び発光モジュールの製造方法に関する。

従来、半導体レーザ素子などの半導体発光素子が知られている。このような半導体発光素子において、高効率化、及び発熱抑制が求められている。例えば、特許文献1に記載された半導体レーザ素子では、P側電極上に配置されるパッド電極において、導電性が良好なAuが用いられている。これにより、特許文献1に記載された半導体レーザ素子においては、高効率化、及び発熱抑制を実現しようとしている。

しかしながら、特許文献1に記載された半導体レーザ素子のように、パッド電極においてAuを用いる場合にも、半導体レーザ素子の電気抵抗には改善の余地がある。例えば、特許文献1に記載された半導体レーザ素子のように、パッド電極と、サブマウントとをAuSn半田を用いて接合する場合、Snがパッド電極を介してP側電極にまで拡散し、半導体層とP側電極との間のコンタクト抵抗を増大させるおそれがある。

本開示は、このような課題を解決するものであり、電気抵抗が低減された電極を備える半導体発光素子などを提供することを目的とする。

上記課題を解決するために、本開示に係る窒化物半導体発光素子の一態様は、半導体積層体と、前記半導体積層体の上方に配置されるコンタクト電極と、前記コンタクト電極の上方に配置され、Auを含むパッド層とを備え、前記パッド層は、前記パッド層と前記コンタクト電極とが接する領域の上方に配置される第一層と、前記第一層の上方に配置され、前記第一層と接する第二層とを有し、前記コンタクト電極の主面に平行な方向において、前記第二層におけるAuの平均粒径は、前記第一層におけるAuの平均粒径より大きい。

本開示に係る発光モジュールの一態様は、半導体発光素子と、前記半導体発光素子が接合される基台とを備え、前記半導体発光素子は、半導体積層体と、前記半導体積層体と前記基台との間に配置されるコンタクト電極と、前記コンタクト電極と前記基台とに接合され、AuSnを含む接合層とを備え、前記接合層は、前記接合層と前記コンタクト電極とが接する領域と対向する位置に配置される第一接合領域を有し、前記第一接合領域のうち、前記第一接合領域の厚さ方向の中央より前記コンタクト電極に近い領域におけるSnの平均含有量は、前記第一接合領域のうち前記中央より前記コンタクト電極から遠い領域におけるSnの平均含有量より少ない。

本開示に係る発光モジュールの製造方法の一態様は、半導体発光素子及び基台を準備する準備工程と、AuSnを含む接合材を用いて、前記基台に前記半導体発光素子を接合する接合工程とを含み、前記半導体発光素子は、半導体積層体と、前記半導体積層体の上方に配置されるコンタクト電極と、前記コンタクト電極と電気的に接続され、前記コンタクト電極の上方に配置される、Auを含むパッド層とを備え、前記パッド層は、前記パッド層と前記コンタクト電極とが接する領域の上方に配置される第一層と、前記第一層の上方に配置され、前記第一層と接する第二層とを含み、前記第二層におけるAuの結晶粒の形状は、柱状であり、前記コンタクト電極の主面に平行な方向において、前記第二層の平均粒径は、前記第一層の平均粒径より大きく、前記接合工程において、前記接合材は、前記基台と、前記パッド層とを接合する。

本開示によれば、電気抵抗が低減された電極を備える半導体発光素子などを提供できる。

以下、本開示の実施の形態について、図面を参照しながら説明する。なお、以下に説明する実施の形態は、いずれも本開示の一具体例を示すものである。したがって、以下の実施の形態で示される、数値、形状、材料、構成要素、及び、構成要素の配置位置や接続形態などは、一例であって本開示を限定する主旨ではない。

また、各図は模式図であり、必ずしも厳密に図示されたものではない。したがって、各図において縮尺等は必ずしも一致していない。なお、各図において、実質的に同一の構成に対しては同一の符号を付しており、重複する説明は省略又は簡略化する。

また、本明細書において、「上方」及び「下方」という用語は、絶対的な空間認識における上方向(鉛直上方)及び下方向(鉛直下方)を指すものではなく、積層構成における積層順を基に相対的な位置関係により規定される用語として用いる。また、「上方」及び「下方」という用語は、2つの構成要素が互いに間隔をあけて配置されて2つの構成要素の間に別の構成要素が存在する場合のみならず、2つの構成要素が互いに接する状態で配置される場合にも適用される。

(実施の形態1)

実施の形態1に係る半導体発光素子について説明する。

実施の形態1に係る半導体発光素子について説明する。

[1-1.全体構成]

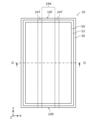

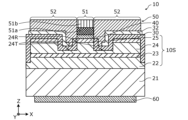

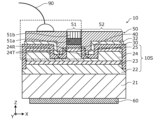

まず、本実施の形態に係る半導体発光素子の全体構成について図1、及び図2を用いて説明する。図1及び図2は、それぞれ本実施の形態に係る半導体発光素子10の全体構成を示す模式的な平面図及び断面図である。図2には、図1のII-II線における断面が示されている。なお、各図には、互いに直交するX軸、Y軸、及びZ軸が示されている。X軸、Y軸、及びZ軸は、右手系の直交座標系である。半導体発光素子10の積層方向は、Z軸方向に平行であり、光(本実施の形態では、レーザ光)の主な出射方向は、Y軸方向に平行である。

まず、本実施の形態に係る半導体発光素子の全体構成について図1、及び図2を用いて説明する。図1及び図2は、それぞれ本実施の形態に係る半導体発光素子10の全体構成を示す模式的な平面図及び断面図である。図2には、図1のII-II線における断面が示されている。なお、各図には、互いに直交するX軸、Y軸、及びZ軸が示されている。X軸、Y軸、及びZ軸は、右手系の直交座標系である。半導体発光素子10の積層方向は、Z軸方向に平行であり、光(本実施の形態では、レーザ光)の主な出射方向は、Y軸方向に平行である。

半導体発光素子10は、図2に示されるように、半導体積層体10Sを備え、半導体積層体10Sの積層方向(つまり、Z軸方向)に垂直な方向の端面10F(図1参照)から光を出射する。本実施の形態では、半導体発光素子10は、共振器を形成する二つの端面10F及び10Rを有する窒化物半導体レーザ素子である。端面10Fは、レーザ光を出射するフロント端面であり、端面10Rは、端面10Fより反射率が高いリア端面である。本実施の形態では、端面10F及び10Rの反射率は、それぞれ、6%及び98%である。また、半導体発光素子10は、端面10Fと端面10Rとの間に形成された導波路を有する。本実施の形態に係る半導体発光素子10の共振器長(つまり、端面10Fと端面10Rと間の距離)は1000μm程度である。また、半導体発光素子10は、例えば、405nm帯にピーク波長を有する青紫光を出射する。

図2に示されるように、半導体発光素子10は、基板21と、半導体積層体10Sと、絶縁層30と、密着補助層32と、コンタクト電極40と、パッド層50と、N側電極60とを備える。

基板21は、半導体発光素子10の基台となる板状部材である。本実施の形態では、基板21は、N型GaN基板である。

半導体積層体10Sは、窒化物半導体を含む積層体である。半導体積層体10Sは、積層方向(つまり、各図のZ軸方向)に積層された複数の半導体層を有する。本実施の形態では、半導体積層体10Sは、N側半導体層22と、活性層23と、P側半導体層24と、コンタクト層25とを有する。

N側半導体層22は、基板21の上方であって、活性層23の下方に配置される第一導電型の第一半導体層の一例である。N側半導体層22は、窒化物半導体を含む。本実施の形態では、N側半導体層22は、活性層23より屈折率が低いN型クラッド層を含む。N側半導体層22は、例えば、N型AlGaN層である。なお、N側半導体層22は、N型クラッド層以外の層を含んでもよい。N側半導体層22は、例えば、バッファ層、光ガイド層などを含んでもよい。

活性層23は、N側半導体層22の上方に配置される発光層である。本実施の形態では、活性層23は、窒化物半導体を含み、量子井戸構造を有する。活性層23は、単一の量子井戸を有していてもよいし、複数の量子井戸を有していてもよい。本実施の形態では、活性層23は、InGaNからなる複数のバリア層と、InGaNからなる複数のウェル層と有する。

P側半導体層24は、活性層23の上方に配置される第二導電型の第二半導体層の一例である。P側半導体層24は、窒化物半導体を含む。本実施の形態では、P側半導体層24は、活性層23より屈折率が低いP型クラッド層を含む。P側半導体層24は、例えば、P型AlGaN層である。なお、P側半導体層24は、P型クラッド層以外の層を含んでもよい。P側半導体層24は、例えば、光ガイド層、電子障壁層などを含んでもよい。また、P側半導体層24は、超格子構造を有してもよい。

P側半導体層24には、リッジ24Rが形成されている。リッジ24Rは、P側半導体層24のうち、Z軸方向に突出する部分であり、Y軸方向に延在する。また、P側半導体層24には、リッジ24Rに沿って配置され、Y軸方向に延びる二つの溝24Tが形成されている。本実施の形態では、リッジ幅(つまり、リッジ24RのX軸方向の寸法)は、30μm程度である。図1における点線は、溝24Tの側面(上面からは見えない)の位置に対応する。

コンタクト層25は、P側半導体層24の上方に配置され、コンタクト電極40とオーミック接触する層である。本実施の形態では、コンタクト層25は、P型GaN層である。

絶縁層30は、半導体積層体10Sとパッド層50との間に配置され、電気的に絶縁性を有する層である。絶縁層30は、リッジ24Rの上面に対応する位置に開口部(又はスリット)を有する。本実施の形態では、絶縁層30は、P側半導体層24の上面のうち、リッジ24Rの上面以外の領域に配置される。なお、絶縁層30は、リッジ24Rの上面の一部に配置されていてもよい。絶縁層30を形成する材料は絶縁材料であれば、特に限定されない。本実施の形態では、絶縁層30は、SiO2からなる。

密着補助層32は、絶縁層30の上方に配置される層である。密着補助層32は、絶縁層30とパッド層50との間に配置され、パッド層50と絶縁層30との間の密着性を高める機能を有する。密着補助層32は、絶縁層30の開口部に対応する位置に開口部(又はスリット)を有する。本実施の形態では、基板21の上面視において、密着補助層32の開口部の内部に絶縁層30の開口部が配置される。密着補助層32は、Ti及びCrの少なくとも一方を含んでもよい。密着補助層32がTiを含み、かつ、絶縁層30が酸化物である場合には、密着補助層32と絶縁層30との密着性をより一層高めることができる。絶縁層30が酸化物の場合、金属膜からなる密着補助層32も酸化物を形成しやすい材料であると、強力に結合するからである。本実施の形態では、密着補助層32は、絶縁層30の上に配置されるTi膜と、Ti膜の上に配置されるPt膜とを含む積層構造を有する。

コンタクト電極40は、半導体積層体10Sの上方に配置される電極である。コンタクト電極40は、コンタクト層25の上方において、コンタクト層25と対向し、かつ、コンタクト層25に接する。本実施の形態では、コンタクト電極40は、リッジ24Rの上方に配置される。コンタクト電極40は、例えば、Ag、Ni、Pd、Cr、及びPtの少なくとも一つで形成された単層膜又は多層膜や、酸化インジウムスズ(ITO;Indium Tin Oxide)、酸化インジウム亜鉛(IZO;Indium Zinc Oxide)、酸化亜鉛(ZnO;Zinc Oxide)、又は、InGaZnOx(IGZO)等の透明金属酸化物からなる透明導電膜などでもよい。本実施の形態では、コンタクト電極40は、コンタクト層25に接するPd層と、Pt層の上方に配置されるPt層とを有する。

パッド層50は、コンタクト電極40の上方に配置され、コンタクト電極40と接する導電層である。パッド層50は、Auを含む。本実施の形態では、パッド層50は、厚さ約4μmのAu層である。パッド層50の詳細構成については、後述する。

N側電極60は、基板21の下面(つまり、基板21の半導体積層体10Sが配置される主面の反対側の主面)に配置される導電層である。N側電極60は、例えば、Cr、Ti、Ni、Pd及びPtの少なくとも一つで形成された単層膜又は多層膜であり、N側電極60上にはAuからなるパッド層が形成されている。

[1-2.パッド層の詳細構成及び効果]

次に、本実施の形態に係るパッド層50の詳細構成及び効果について説明する。

次に、本実施の形態に係るパッド層50の詳細構成及び効果について説明する。

図2に示されるように、パッド層50は、コンタクト領域51と、外部領域52とを有する。

コンタクト領域51は、パッド層50のうち、パッド層50とコンタクト電極40とが接する領域の上方に配置される領域である。コンタクト領域51は、パッド層50とコンタクト電極40とが接する領域の上方に配置される第一層51aと、第一層51aの上方に配置され、第一層51aと接する第二層51bとを有する。本実施の形態では、半導体積層体10Sとパッド層50との間の領域のうち、半導体積層体10Sと第一層51aとの間の領域には、絶縁層30は配置されない。

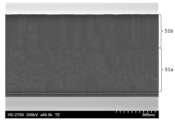

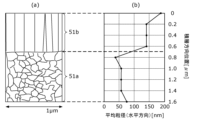

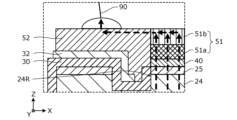

続いて、第一層51a及び第二層51bの結晶の形状について図3及び図4を用いて説明する。図3は、本実施の形態に係るコンタクト領域51の結晶の形状を示す透過電子顕微鏡(TEM)写真である。図3においては、コンタクト領域51の積層方向に平行な断面における結晶粒の形状が示されている。図4は、本実施の形態に係るコンタクト領域51の結晶粒の形状を示す図である。図4には、図3に示されるTEM写真に対応する断面における結晶粒界の概略図(a)と、平均粒径の積層方向における分布を示すグラフ(b)とが示されている。図4のグラフ(b)には、コンタクト電極40の主面に平行な方向(つまり、各図のXY平面に平行な方向)における平均粒径が示される。以下では、コンタクト電極40の主面に平行な方向のことを「水平方向」、垂直な方向のことを「垂直方向」とも称する。

本実施の形態では、第一層51aは、厚さ約0.9μmのAu層であり、図3及び図4の概略図(a)に示されるように、第一層51aにおけるAuの結晶粒は粒径の水平方向と垂直方向のアスペクト比が0.5以上2以下の、いわゆる粒状である。第二層51bは、厚さ約0.7μmのAu層であり、図3及び図4の概略図(a)に示されるように、第二層51bにおけるAuの結晶粒は、柱状である。第二層51bにおける各結晶は、積層方向(つまり、各図のZ軸方向)に延在する。水平方向において、第二層51bにおけるAuの平均粒径(つまり、平均結晶粒径)は、第一層におけるAuの平均粒径より大きい。本実施の形態では、水平方向において、第一層51aにおけるAuの平均粒径は、約60nmであり、第二層51bにおけるAuの平均粒径は、約150nmである。ここで、Auの平均粒径が大きいほど電気抵抗率が低くなるために、水平方向において、第二層51bの電気抵抗率は、第一層51aの電気抵抗率より低い。

第一層51aにおけるAuの平均粒径の方向を特定しない場合の平均値は、約60nmであり、第二層51bにおけるAuの平均粒径の方向を特定しない場合の平均値は、約320nmである。以下では、方向を特定しない場合は「平均粒径の方向を特定しない場合の平均値」のことを単に「平均粒径」とも称する。Auの平均粒径の測定方法については後述する。以上のように、第二層51bにおけるAuの平均粒径は、第一層51aにおける平均粒径より大きいため、第二層51bの電気抵抗率は、第一層51aの電気抵抗率より低い。

図2に示される外部領域52は、パッド層50のうち絶縁層30の上方に配置される領域である。本実施の形態では、外部領域52は、絶縁層30に直接接続される(つまり、接する)領域と、密着補助層32を介して絶縁層30に接続される領域とを有する。本実施の形態では、外部領域52におけるAuの結晶粒の形状は、第一層51aよりもランダムである。外部領域52におけるAuの平均粒径は、第一層51aにおけるAuの平均粒径より大きく、第二層51bにおけるAuの平均粒径より小さい。本実施の形態では、外部領域52におけるAuの平均粒径は、約100nmである。

本実施の形態に係るパッド層50の効果について、比較例と比較しながら説明する。まず、半導体発光素子10の電流供給態様について図5を用いて説明する。図5は、本実施の形態に係る半導体発光素子10の電流供給態様の一例を示す図である。

図5に示されるように、半導体発光素子10の電流供給態様の一例として、パッド層50にワイヤ90をボンディングによって接続する態様が考えられる。ワイヤ90は、導電性の線状部材であり、導電性材料として、例えば、Auを含む。図5に示されるように、ワイヤ90は、パッド層50の上面のうち、半導体発光素子10のリッジ24Rの上方以外の領域、つまり、外部領域52に配置される。これにより、リッジ24R、並びに、リッジ24Rの上方及び下方に位置する各層へのボンディングに起因するダメージを抑制できる。さらに、本実施の形態では、外部領域52におけるAuの結晶粒の形状は第一層51aよりもランダムであり、かつ、Auの平均粒径が、第一層51aにおけるAuの平均粒径より大きいため、外部領域52の方が、第一層51aより硬度が低い。したがって、外部領域52にワイヤ90をボンディングすることで、半導体積層体10Sへのボンディングに起因するダメージを抑制できる。

図5に示されるような電流供給態様を用いる場合の半導体発光素子10における電流経路について、比較例と比較しながら、図6及び図7を用いて説明する。図6は、比較例の半導体発光素子のパッド層950における電流の経路の概要を示す図である。図7は、本実施の形態に係るパッド層50における電流の経路の概要を示す図である。図6及び図7には、図5に示される破線枠内に対応する領域が示されている。図6及び図7には、電子の移動経路の概要が破線矢印で示されている。

図6に示される比較例の窒化物半導体発光素子は、パッド層950の構成において、本実施の形態に係る半導体発光素子10と相違し、その他の構成において一致する。比較例のパッド層950は、コンタクト領域951と外部領域52とを有する。比較例のコンタクト領域951は、本実施の形態に係るコンタクト領域51の第一層51aと同様の結晶粒の形状を有する。つまり、比較例のコンタクト領域951におけるAuの結晶粒は、粒状である。また、比較例のコンタクト領域951におけるAuの平均粒径は、約60nmである。

比較例の半導体発光素子のコンタクト領域951におけるAuの平均粒径が小さいため、コンタクト領域951における電気抵抗率が比較的大きい。このため、図6に示されるように、比較例の半導体発光素子において、電子は、コンタクト領域951を通過する距離が短い経路に沿って移動する。つまり、電流経路は、リッジ24Rのうち、ワイヤ90のボンディング位置に近い方の端部付近の領域に集中する。これに伴い、比較例の半導体発光素子では、リッジ24Rの幅方向における発光強度分布に偏りが生じるため、活性層23の発光強度のピーク位置付近において劣化が進みやすくなる。

これに対して、本実施の形態に係る半導体発光素子10では、パッド層50のコンタクト領域51が第一層51aの上方に配置される第二層51bを有する。第二層51bにおけるAuの水平方向における平均粒径は、第一層51aにおけるAuの水平方向における平均粒径より大きいため、第二層51bの水平方向における電気抵抗率は、第一層51aの水平方向における電気抵抗率より小さい。つまり、本実施の形態に係る半導体発光素子10によれば、パッド層50を含む電極の電気抵抗を、比較例の電極の電気抵抗より低減することができる。これにより、第二層51bにおいて電子は水平方向に移動しやすくなる。したがって、図7に示されるように、電流経路を、リッジ24Rの幅方向に分散させることができる。つまり、本実施の形態に係る半導体発光素子10では、リッジ24Rの幅方向における発光強度分布を均一化することができる。このため、活性層23の局所的な劣化の進行を抑制できる。

さらに、本実施の形態では、第二層51bにおけるAuの結晶粒は積層方向に延在する柱状であるため、第二層51bにおける積層方向の電気抵抗率も低減できる。したがって、パッド層50における電気抵抗をより一層低減できる。

以上のように、本実施の形態に係る半導体発光素子10によれば、電極の電気抵抗を低減することができる。

[1-3.平均粒径の測定方法]

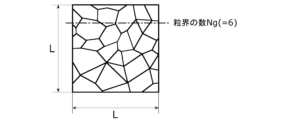

パッド層50におけるAuの平均粒径の測定方法について図8を用いて説明する。図8は、平均粒径の測定方法を説明するための図である。本実施の形態では、集束イオンビーム(Focused Ion Beam:FIB)を用いてパッド層50の断面を形成した後、走査型顕微鏡によるScannig Ion Microscopy像(SIM像)にて観察した観察領域に対してインターセプト法を適用して結晶粒径を測定した。

パッド層50におけるAuの平均粒径の測定方法について図8を用いて説明する。図8は、平均粒径の測定方法を説明するための図である。本実施の形態では、集束イオンビーム(Focused Ion Beam:FIB)を用いてパッド層50の断面を形成した後、走査型顕微鏡によるScannig Ion Microscopy像(SIM像)にて観察した観察領域に対してインターセプト法を適用して結晶粒径を測定した。

このとき、図8に示されるように、一辺がLの正方形の中に平均粒径dを持つ結晶が一辺当りNg個存在した場合、正方形の面積はL2で、1つの結晶粒の面積はπ(d/2)2となる。そして、結晶粒に対して観察領域が相対的に大きい場合、結晶粒は正方形の中にNg2個あるため結晶粒全部が占める面積はNg2×π(d/2)2となり、正方形の面積=結晶粒全部が占める面積となるので、L2=Ng2×π(d/2)2となる。これをdで表すと、d=2L/Ng/(π)1/2の関係式で表される。この関係式を用いて観察領域L×Lに直線(図8の一点鎖線)をひき、この直線に交わる粒界の数を結晶の数Ngとしてパッド層50の水平方向及び積層方向の平均粒径dを求めた。図8では、一点鎖線の直線が6つの粒界と交わっているので、Ng=6である。なお、平均粒径の方向を特定しない場合の平均値は、水平方向における平均粒径と積層方向における平均粒径とを相乗平均することで求めることができる。

[1-4.製造方法]

本実施の形態に係る半導体発光素子10の製造方法について、図2及び図9~16を用いて説明する。図9~図16の各々は、本実施の形態に係る半導体発光素子10の製造方法の各工程を示す断面図である。図9~図16には、図2と同様の断面が示されている。

本実施の形態に係る半導体発光素子10の製造方法について、図2及び図9~16を用いて説明する。図9~図16の各々は、本実施の形態に係る半導体発光素子10の製造方法の各工程を示す断面図である。図9~図16には、図2と同様の断面が示されている。

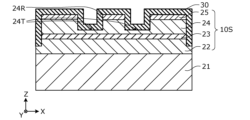

まず、図9に示されるように、基板21を準備する。本実施の形態では、基板21として、N型GaNからなるウエハ(GaN基板)を準備する。続いて、基板21の上に、MOCVD(Metal Organic Chemical Vapor Deposition)法によるエピタキシャル成長技術により、N側半導体層22と、活性層23と、P側半導体層24と、コンタクト層25とを順に積層する。これにより、半導体積層体10Sを形成することができる。

続いて、図10に示されるように、半導体発光素子10を個片化するための素子分離溝10Dを形成する。素子分離溝10Dは、半導体発光素子10のX軸方向の両端部に対応する位置に形成される。本実施の形態では、素子分離溝10Dは、半導体積層体10Sの上面からN側半導体層22の内部にまで到達する。素子分離溝10Dの形成方法は特に限定されない。素子分離溝10Dは、例えば、フォトリソグラフィ技術及びエッチングを用いて形成されてもよいし、レーザ加工によって形成されてもよい。

続いて、図11に示されるように、リッジ24Rを形成する。本実施の形態では、半導体積層体10Sに二つの溝24Tを形成することによって、リッジ24Rを形成する。二つの溝24Tの各々は、半導体積層体10Sの上面からP側半導体層24の内部にまで到達する。素子分離溝10Dの形成方法は特に限定されない。素子分離溝10Dは、例えば、フォトリソグラフィ技術及びエッチングを用いて形成される。

続いて、図12に示されるように、半導体積層体10Sの上面に絶縁層30を形成する。本実施の形態では、絶縁層30としてSiO2膜を、プラズマCVD(Chemical Vapor Deposition)法などを用いて形成する。これにより、アモルファスSiO2からなる絶縁層30が形成される。

続いて、図13に示されるように、リッジ24Rの上方に位置する絶縁層30をフォトリソグラフィ技術及びエッチングを用いて除去した後、リッジ24Rのコンタクト層25上にコンタクト電極40を形成する。本実施の形態では、コンタクト電極40として、Pd層及びPt層を形成する。コンタクト電極40は、例えば、フォトリソグラフィ技術及び蒸着法を用いて、リッジ24Rの上方のみに形成される。

続いて、図14に示されるように、密着補助層32を形成する。具体的には、絶縁層30の上に、フォトリソグラフィ技術及び蒸着法を用いて、Ti膜及びPt膜からなる密着補助層32を形成する。絶縁層30は、アモルファスSiO2であるため、密着補助層32は、単結晶上に形成したTi膜及びPt膜よりもランダムな結晶粒の形状を有する。

続いて、図15に示されるように、パッド層50の一部を形成する。具体的には、基板21の温度を約100℃に維持して、コンタクト電極40及び絶縁層30の上方に、蒸着法によりAu膜を形成する。これにより、コンタクト電極40の上には、粒状で小さな結晶粒を有する第一層51aが形成される。一方、絶縁層30の上、及び、密着補助層32の上には、外部領域52の一部が形成される。絶縁層30はアモルファスSiO2であるため、絶縁層30の上に形成される外部領域52は、ランダムな結晶粒の形状であり、粒間空隙等の欠陥を多く有するAu膜となる。また、密着補助層32は絶縁層30と同様のランダムな結晶粒の形状を有するため、密着補助層32の上に形成される外部領域52も、ランダムな結晶粒の形状であり、粒間空隙等の欠陥を多く有するAu膜となる。

続いて、図16に示されるように、パッド層50の残りの部分を形成する。具体的には、図15に示されるパッド層50の一部を形成した後、形成を中断して、基板21の温度を、一旦、約50℃まで低下させる。続いて、Au膜の形成を再開する。この際、基板21の温度は、Au蒸着の進行に伴って上昇してもよい。これにより、第一層51a上には、Auがエピタキシャル的に成長する。これにより、柱状の結晶粒を有し、水平方向におけるAuの平均粒径が、第一層51aにおけるAuの水平方向における平均粒径より大きい第二層51bを形成することができる。特にコンタクト電極40がPdの場合に柱状の結晶粒の平均粒径を最も大きくできる。

続いて、図2に示されるように、基板21の下面にN側電極60を形成する。具体的には、フォトリソグラフィ技術及び蒸着法を用いて、Ti膜、Pt膜、及び、Au膜を順に形成したN側電極60を形成する。

以上のような製造方法により、本実施の形態に係る半導体発光素子10を製造できる。

(実施の形態2)

実施の形態2に係る発光モジュール及びその製造方法について説明する。本実施の形態に係る発光モジュールは、実施の形態1に係る半導体発光素子を用いて製造されるモジュールである。

実施の形態2に係る発光モジュール及びその製造方法について説明する。本実施の形態に係る発光モジュールは、実施の形態1に係る半導体発光素子を用いて製造されるモジュールである。

[2-1.全体構成]

本実施の形態に係る発光モジュールの全体構成について、図17を用いて説明する。図17は、本実施の形態に係る発光モジュール12の全体構成を示す模式的な断面図である。

本実施の形態に係る発光モジュールの全体構成について、図17を用いて説明する。図17は、本実施の形態に係る発光モジュール12の全体構成を示す模式的な断面図である。

図17に示されるように、発光モジュール12は、半導体発光素子110と、基台80とを備える。発光モジュール12は、実施の形態1に係る半導体発光素子10を基台80にジャンクションダウン実装することによって得られるモジュールである。発光モジュール12の製造方法については後述する。

基台80は、半導体発光素子110が接合される部材である。本実施の形態では、基台80は、半導体発光素子110が実装されるサブマウントである。基台80は、矩形板状の形状を有する。基台80として、例えば、アルミナ、AlN、SiC、ダイヤモンドなどの材料で構成されるセラミック基板、多結晶基板、単結晶基板などを用いることができる。なお、基台80は、サブマウントに限定されない。基台80は、半導体発光素子110が実装される実装基板であってもよい。

本実施の形態に係る半導体発光素子110は、基板21と、半導体積層体10Sと、コンタクト電極40と、密着補助層32と、接合層70と、N側電極60とを備える。半導体発光素子110は、パッド層50に代えて、接合層70を備える点において、実施の形態1に係る半導体発光素子10と相違し、その他の点において一致する。

本実施の形態に係るコンタクト電極40は、半導体積層体10Sと基台80との間に配置される。本実施の形態に係る絶縁層30は、半導体積層体10Sと接合層70との間に配置される。

接合層70は、半導体発光素子110のコンタクト電極40と、基台80とに接合され、AuSnを含む層である。接合層70は、接合層70とコンタクト電極40とが接する領域と対向する位置に配置される第一接合領域71と、絶縁層30と対向する位置に配置される第二接合領域72とを有する。本実施の形態では、密着補助層32は、第二接合領域72と絶縁層30との間に配置される。接合層70は、コンタクト電極40、絶縁層30、及び密着補助層32と、基台80とを接合する。

[2-2.製造方法]

本実施の形態に係る発光モジュール12の製造方法について、図18及び図19を用いて説明する。図18は、本実施の形態に係る発光モジュール12の製造方法の流れを示すフローチャートである。図19は、本実施の形態に係る発光モジュール12の準備工程を説明する模式的な断面図である。

本実施の形態に係る発光モジュール12の製造方法について、図18及び図19を用いて説明する。図18は、本実施の形態に係る発光モジュール12の製造方法の流れを示すフローチャートである。図19は、本実施の形態に係る発光モジュール12の準備工程を説明する模式的な断面図である。

まず、図19に示されるように、実施の形態1に係る半導体発光素子10と、基台80とを準備する(図18の準備工程S10)。本実施の形態では、基台80の一つの主面に接合材56が配置される。本実施の形態では、接合材56は、後述する接合工程S20において、基台80と、半導体発光素子10のパッド層50とを接合する部材である。本実施の形態では、接合材56は、AuSnを含む半田である。

続いて、図18に示されるように、AuSnを含む接合材56を用いて、基台80に半導体発光素子10を接合する(接合工程S20)。接合工程S20は、配置工程S21と、第一加熱工程S22と、第一降温工程S23と、第二加熱工程S24と、第二降温工程S25とを含む。

接合工程S20において、最初に、半導体発光素子10を基台80に配置する(配置工程S21)。具体的には、図19に示される半導体発光素子10のパッド層50を基台80に配置された接合材56と対向させた状態で、半導体発光素子10を基台80に向けて移動し、半導体発光素子10のパッド層50を、基台80に配置された接合材56に接触させる。

配置工程S21の後に、図18に示されるように、基台80を接合材56の融点Tmより高い第一のピーク温度T1まで加熱し接合材56を溶融する(第一加熱工程S22)。具体的には、基台80をヒータ上に配置し、ヒータの温度を上昇させることによって、基台80を加熱する。この第一加熱工程S22において、基台80の温度が、接合材56の融点Tmに到達する前に、半導体発光素子10への荷重の印加を開始することで、半導体発光素子10を基台80に押し付ける。これにより、接合材56が溶融した後で、半導体発光素子10の接合材56と対向する面と、接合材56との接触面積を増大させることができる。言い換えると、半導体発光素子10と、接合材56との間にボイドが形成されることを抑制できる。

続いて、図18に示されるように、第一加熱工程S22の後に、基台80の温度を接合材56の融点Tm未満の温度である切換温度Tvまで降下させる(第一降温工程S23)。この第一降温工程S23において、基台80の温度が接合材56の融点Tmに到達する前に、半導体発光素子10への荷重の印加を止める。荷重の印加を止める温度は、必ずしも融点Tmより高い必要はなく、融点Tmより低い温度であってもよい。

第一降温工程S23の後に、基台80を接合材56の融点Tmより高い第二のピーク温度T2まで加熱し接合材56を再度溶融する(第二加熱工程S24)。ここで、第一のピーク温度T1と、第二のピーク温度T2と、接合材56の融点Tmとは、Tm<T1<T2の関係を満たす。

第二加熱工程S24の後に、基台80の温度を接合材56の融点Tm未満の温度まで降下させる(第二降温工程S25)。ここでは、第一加熱工程S22を行う前の温度(つまり、スタンバイ温度)まで基台80の温度を降下させる。

第二加熱工程S60及び第二降温工程S70においては、半導体発光素子10への荷重を印加してもよいし、しなくてもよい。

以上のような工程により、図17に示されるような発光モジュール12を製造することができる。発光モジュール12においては、半導体発光素子10のパッド層50と、接合材56とが一体化された接合層70が形成される。具体的には、Auからなるパッド層50に接合材56に含まれるSnが拡散し、AuSnを含む接合層70が形成される。

[2-3.効果]

本実施の形態に係る発光モジュール12の効果について説明する。

本実施の形態に係る発光モジュール12の効果について説明する。

上述したとおり、本実施の形態に係る発光モジュール12の接合層70は、実施の形態1に係る半導体発光素子10のパッド層50と、接合材56とが一体化された層である。接合層70の第一接合領域71及び第二接合領域72は、それぞれ、パッド層50のコンタクト領域51及び外部領域52に対応する領域である。つまり、コンタクト領域51と接合材56の一部とから第一接合領域71が形成され、外部領域52と接合材56の他の一部とから第二接合領域72が形成される。コンタクト領域51と外部領域52との結晶粒の形状の相違に伴い、第一接合領域71と第二接合領域72とでは、Snの分布態様が異なる。以下、第一接合領域71及び第二接合領域72におけるSnの分布態様について図20~図23を用いて説明する。図20及び図21は、それぞれ、本実施の形態に係る第一接合領域71及び第二接合領域72の厚さ方向(つまり、各図のZ軸方向)に沿った直線上でのEDX(Energy Dispersive X-ray Spectroscopy)分析で得られたSn強度の分布を示すグラフである。図22及び図23は、それぞれ、本実施の形態に係る第一接合領域71及び第二接合領域72の厚さ方向に沿った領域でのEDX分析で得られた平均Sn強度の分布を示すグラフである。各図の横軸は、厚さ方向の位置を示す。横軸の数値が大きくなるにしたがって、位置は、基台80に近づき、横軸の数値が小さくなるにしたがって、位置は半導体積層体10Sに近づく。図22及び図23における平均Sn強度は、それぞれ、図17の破線枠R1及びR2に対応する領域におけるSn強度である。破線枠R1及びR2は、接合層70の厚さ方向における長さ、及び、X軸方向における長さの各々が5μmの領域である。図20~図23におけるSn強度および平均Sn強度は、接合層70における厚さ方向の各位置におけるSnの含有量及び平均含有量に対応する。

本実施の形態では、接合層70の第一接合領域71のうち、パッド層50の第二層51bに対応する領域においては、Auの結晶粒の形状が柱状であるため、厚さ方向にSnが拡散しやすい。このため、図20及び図22に示されるように、第一接合領域71のうち、パッド層50の第二層51bに対応する領域においては、Sn含有量が多い。このように、接合層70のうち、パッド層50に対応する領域におけるSnの含有量を増大させることで、接合層70と基台80との接合強度を高めることができる。したがって、基台80から半導体発光素子110が脱離することを抑制できる。

また、接合層70の第一接合領域71のうち、パッド層50の第一層51aに対応する領域においては、Auの結晶が粒状を有し、かつ、平均粒径が第二層51bにおけるAuの平均粒径より小さいため、第二層51bに対応する領域よりSnが拡散しにくい。このため、図20及び図22に示されるように、第一接合領域71のうち、パッド層50の第一層51aに対応する領域においては、Sn含有量が少ない。このため、図20に示されるように、第一接合領域71の厚さ方向に沿った直線上において、Snの含有量は、コンタクト電極40から遠ざかるにしたがって、階段状に上昇する。また、図22に示されるように、第一接合領域71の厚さ方向に沿った領域においては、第一接合領域71は、コンタクト電極40から遠ざかるにしたがってのSnの平均含有量が徐々に上昇する第一遷移領域Rg1を有する。このように、第一接合領域71がSnの平均含有量が徐々に上昇する第一遷移領域Rg1することで、厚さ方法におけるSnの含有量の急激な変化を抑制できるため、Snの含有量が変化する領域における熱膨張係数の急激な変化を抑制できる。したがって、第一接合領域71の温度変化に伴う破損を抑制できる。

ここで、第一接合領域71に接するコンタクト電極40を介してコンタクト層25に到達すると、コンタクト層25とコンタクト電極40との間の接触抵抗が増大する。本実施の形態では、第一接合領域71のうち、パッド層50の第一層51aに対応する領域によって、Snの拡散が抑制されるため、コンタクト層25へのSnの拡散を抑制できる。したがって、コンタクト層25とコンタクト電極40との間の接触抵抗の増大を抑制できる。つまり、半導体発光素子110のコンタクト電極40及び接合層70を含む電極の電気抵抗を低減することができる。

以上のように、本実施の形態に係る発光モジュール12においては、第一接合領域71のうち、第一接合領域71の厚さ方向の中央よりコンタクト電極40に近い領域におけるSnの平均含有量は、第一接合領域71のうち当該中央よりコンタクト電極40から遠い領域におけるSnの平均含有量より少ない。これにより、コンタクト層25とコンタクト電極40との間の接触抵抗の増大を抑制できる。

第二接合領域72は、パッド層50のうちAuの粒間空隙等の欠陥が多い外部領域52に対応する領域であるため、Snが拡散しやすい。このため、図21及び図23に示されるように、第二接合領域72の絶縁層30に近い側の端部にまで多くのSnが拡散する。したがって、接合層70と基台80との接合強度を高めることができる。したがって、基台80から半導体発光素子110が脱離することを抑制できる。

また、図21に示されるように、第二接合領域72の厚さ方向の中央におけるSnの含有量は、第二接合領域72の厚さ方向の両方の端部におけるSnの含有量より少ない。このように、第二接合領域72の厚さ方向の基台80側の端部だけでなく、絶縁層30側の端部においてもSnの平均含有量が多いのは、第二接合領域72に局所的にSnが特に拡散しやすい粒界又は欠陥が存在することに起因すると推測される。Snは、局所的な粒界又は欠陥を介して、第二接合領域72の厚さ方向の基台80側の端部から、絶縁層30側の端部付近にまで速やかに拡散し、絶縁層30側の端部付近において水平方向に拡散すると考えられる。また、第二接合領域72の厚さ方向の中央において、粒界又は欠陥は局所的にしか存在しないため、第二接合領域72の厚さ方向の中央におけるSnの平均含有量はそれほど多くならないと推測される。

また、図23に示されるように、第二接合領域72の厚さ方向に沿った領域においては、第二接合領域72は、絶縁層30から遠ざかるにしたがってのSnの平均含有量が徐々に上昇する第二遷移領域Rg2を有する。このように、第二接合領域72がSnの平均含有量が徐々に上昇する第二遷移領域Rg2することで、厚さ方法におけるSnの含有量の急激な変化を抑制できるため、Snの含有量が変化する領域における熱膨張係数の急激な変化を抑制できる。したがって、第二接合領域72の温度変化に伴う破損を抑制できる。

(変形例など)

以上、本開示に係る半導体発光素子などについて、各実施の形態に基づいて説明したが、本開示は、上記各実施の形態に限定されるものではない。

以上、本開示に係る半導体発光素子などについて、各実施の形態に基づいて説明したが、本開示は、上記各実施の形態に限定されるものではない。

実施の形態1に係る半導体発光素子10のパッド層50の第一層51a及び第二層51bの平均粒径は、上述した値に限定されない。水平方向において、第一層51aにおけるAuの平均粒径は、30nm以上80nm以下であってもよく、第二層51bにおけるAuの平均粒径は、120nm以上200nm以下であってもよい。方向を特定しない場合において、第一層51aにおけるAuの平均粒径は、30nm以上80nm以下であってもよく、第二層51bにおけるAuの平均粒径は、240nm以上630nm以下であってもよい。

また、実施の形態1に係る半導体発光素子10では、パッド層50の第一層51a及び第二層51bの厚さは、同程度であったが、第一層51a及び第二層51bの厚さの相対的な関係は、これに限定されない。例えば、第二層51bは、第一層51aより厚くてもよい。これにより、パッド層50における電気抵抗率が小さい第二層51bの割合が大きくなるため、パッド層50の電気抵抗率を低減できる。

また、上記各実施の形態においては、半導体発光素子が窒化物半導体レーザ素子である例を示したが、半導体発光素子は、半導体レーザ素子に限定されない。例えば、半導体発光素子は、スーパールミネッセントダイオードであってもよい。

この場合、窒化物半導体発光素子が備える半導体積層体の端面の半導体積層体からの出射光に対する反射率は、0.1%以下であってもよい。このような反射率は、例えば、端面に、誘電体多層膜などからなる反射防止膜を形成することによって実現できる。又は、導波路となるリッジがフロント端面の法線方向から5°以上傾いてフロント端面と交わる傾斜ストライプ構造とすれば、フロント端面で反射した導波光が再び導波路と結合し導波光となる成分の割合を0.1%以下の小さい値とすることができる。さらに半導体発光素子は、発光ダイオードであってもよい。

この場合、窒化物半導体発光素子が備える半導体積層体の端面の半導体積層体からの出射光に対する反射率は、0.1%以下であってもよい。このような反射率は、例えば、端面に、誘電体多層膜などからなる反射防止膜を形成することによって実現できる。又は、導波路となるリッジがフロント端面の法線方向から5°以上傾いてフロント端面と交わる傾斜ストライプ構造とすれば、フロント端面で反射した導波光が再び導波路と結合し導波光となる成分の割合を0.1%以下の小さい値とすることができる。さらに半導体発光素子は、発光ダイオードであってもよい。

また、上記各実施の形態に対して当業者が思いつく各種変形を施して得られる形態や、本開示の趣旨を逸脱しない範囲で上記各実施の形態における構成要素及び機能を任意に組み合わせることで実現される形態も本開示に含まれる。

本開示の窒化物半導体発光素子などは、例えば、高効率な光源として加工機用の光源などに適用できる。

10、110 窒化物半導体発光素子

10D 素子分離溝

10F、10R 端面

10S 半導体積層体

12 発光モジュール

21 基板

22 N側半導体層

23 活性層

24 P側半導体層

24R リッジ

24T 溝

25 コンタクト層

30 絶縁層

32 密着補助層

40 コンタクト電極

50 パッド層

51 コンタクト領域

51a 第一層

51b 第二層

52 外部領域

56 接合材

60 N側電極

70 接合層

71 第一接合領域

72 第二接合領域

80 基台

90 ワイヤ

10D 素子分離溝

10F、10R 端面

10S 半導体積層体

12 発光モジュール

21 基板

22 N側半導体層

23 活性層

24 P側半導体層

24R リッジ

24T 溝

25 コンタクト層

30 絶縁層

32 密着補助層

40 コンタクト電極

50 パッド層

51 コンタクト領域

51a 第一層

51b 第二層

52 外部領域

56 接合材

60 N側電極

70 接合層

71 第一接合領域

72 第二接合領域

80 基台

90 ワイヤ

Claims (12)

- 半導体積層体と、

前記半導体積層体の上方に配置されるコンタクト電極と、

前記コンタクト電極の上方に配置され、Auを含むパッド層とを備え、

前記パッド層は、

前記パッド層と前記コンタクト電極とが接する領域の上方に配置される第一層と、

前記第一層の上方に配置され、前記第一層と接する第二層とを有し、

前記コンタクト電極の主面に平行な方向において、前記第二層におけるAuの平均粒径は、前記第一層におけるAuの平均粒径より大きい

半導体発光素子。 - 前記第二層におけるAuの結晶粒の形状は、柱状である

請求項1に記載の半導体発光素子。 - 前記半導体積層体と前記パッド層との間に配置される絶縁層をさらに備え、

前記半導体積層体と前記パッド層との間の領域のうち、前記半導体積層体と前記第一層との間の領域には、前記絶縁層は配置されない

請求項1又は2に記載の半導体発光素子。 - 前記パッド層は、前記絶縁層の上方に配置される外部領域を含み、

前記外部領域におけるAuの平均粒径は、前記第一層におけるAuの平均粒径より大きい

請求項3に記載の半導体発光素子。 - 前記第二層の電気抵抗率は、前記第一層の電気抵抗率より低い

請求項1~4のいずれか1項に記載の半導体発光素子。 - 前記第二層は、前記第一層より厚い

請求項1~5のいずれか1項に記載の半導体発光素子。 - 発光モジュールであって、

半導体発光素子と、

前記半導体発光素子が接合される基台とを備え、

前記半導体発光素子は、

半導体積層体と、

前記半導体積層体と前記基台との間に配置されるコンタクト電極と、

前記コンタクト電極と前記基台とに接合され、AuSnを含む接合層とを備え、

前記接合層は、前記接合層と前記コンタクト電極とが接する領域と対向する位置に配置される第一接合領域を有し、

前記第一接合領域のうち、前記第一接合領域の厚さ方向の中央より前記コンタクト電極に近い領域におけるSnの平均含有量は、前記第一接合領域のうち前記中央より前記コンタクト電極から遠い領域におけるSnの平均含有量より少ない

発光モジュール。 - 前記半導体発光素子は、前記半導体積層体と前記接合層との間に配置される絶縁層をさらに備え、

前記接合層は、前記絶縁層と対向する位置に配置される第二接合領域を有し、

前記第二接合領域の厚さ方向の中央におけるSnの平均含有量は、

前記第二接合領域の厚さ方向の両方の端部におけるSnの平均含有量より少ない

請求項7に記載の発光モジュール。 - 前記第一接合領域の厚さ方向に沿った直線上において、Snの含有量は、前記コンタクト電極から遠ざかるにしたがって、階段状に上昇する

請求項7又は8に記載の発光モジュール。 - 前記第一接合領域は、前記コンタクト電極から遠ざかるにしたがってのSnの平均含有量が徐々に上昇する第一遷移領域を有する

請求項7又は8に記載の発光モジュール。 - 前記第二接合領域は、前記絶縁層から遠ざかるにしたがってSnの平均含有量が徐々に変化する第二遷移領域を有する

請求項8に記載の発光モジュール。 - 発光モジュールの製造方法であって、

半導体発光素子及び基台を準備する準備工程と、

AuSnを含む接合材を用いて、前記基台に前記半導体発光素子を接合する接合工程とを含み、

前記半導体発光素子は、

半導体積層体と、

前記半導体積層体の上方に配置されるコンタクト電極と、

前記コンタクト電極と電気的に接続され、前記コンタクト電極の上方に配置される、Auを含むパッド層とを備え、

前記パッド層は、前記パッド層と前記コンタクト電極とが接する領域の上方に配置される第一層と、

前記第一層の上方に配置され、前記第一層と接する第二層とを含み、

前記第二層におけるAuの結晶粒の形状は、柱状であり、

前記コンタクト電極の主面に平行な方向において、前記第二層の平均粒径は、前記第一層の平均粒径より大きく、

前記接合工程において、前記接合材は、前記基台と、前記パッド層とを接合する

発光モジュールの製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021183532A JP2023070990A (ja) | 2021-11-10 | 2021-11-10 | 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 |

| PCT/JP2022/040764 WO2023085161A1 (ja) | 2021-11-10 | 2022-10-31 | 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021183532A JP2023070990A (ja) | 2021-11-10 | 2021-11-10 | 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2023070990A true JP2023070990A (ja) | 2023-05-22 |

Family

ID=86335930

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021183532A Pending JP2023070990A (ja) | 2021-11-10 | 2021-11-10 | 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2023070990A (ja) |

| WO (1) | WO2023085161A1 (ja) |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006278463A (ja) * | 2005-03-28 | 2006-10-12 | Dowa Mining Co Ltd | サブマウント |

| JP2012227383A (ja) * | 2011-04-20 | 2012-11-15 | Showa Denko Kk | 半導体発光素子、電極構造および発光装置 |

| KR101541056B1 (ko) * | 2011-09-13 | 2015-07-31 | 아데스토 테크놀러지스 코포레이션 | 합금 전극을 갖는 저항 스위칭 디바이스 및 그 형성 방법 |

| JP6001956B2 (ja) * | 2012-08-10 | 2016-10-05 | 株式会社東芝 | 半導体装置 |

| US11183615B2 (en) * | 2018-02-01 | 2021-11-23 | Nuvoton Technology Corporation Japan | Semiconductor device |

| US10923451B2 (en) * | 2019-07-16 | 2021-02-16 | Nxp Usa, Inc. | Semiconductor dies having ultra-thin wafer backmetal systems, microelectronic devices containing the same, and associated fabrication methods |

-

2021

- 2021-11-10 JP JP2021183532A patent/JP2023070990A/ja active Pending

-

2022

- 2022-10-31 WO PCT/JP2022/040764 patent/WO2023085161A1/ja unknown

Also Published As

| Publication number | Publication date |

|---|---|

| WO2023085161A1 (ja) | 2023-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6337036B2 (ja) | 半導体レーザダイオード | |

| US9130106B2 (en) | Method for manufacturing semiconductor light emitting apparatus by mounting semiconductor light emitting device having stacked dielectric films having different refractive indexes on mounting member | |

| US7892874B2 (en) | Nitride-based light-emitting device and method of manufacturing the same | |

| JP6926205B2 (ja) | 半導体レーザーダイオード | |

| US9735314B2 (en) | Nitride semiconductor light emitting device | |

| US20080267238A1 (en) | Semiconductor laser diode element and method of manufacturing the same | |

| JP2020524407A (ja) | 半導体レーザーダイオード | |

| JP2009206265A (ja) | 半導体発光素子及び半導体発光素子の製造方法 | |

| JP2020532100A (ja) | 端面発光型のレーザバー | |

| US9006013B2 (en) | Method for manufacturing semiconductor light emitting device and semiconductor light emitting device wafer | |

| WO2022079971A1 (ja) | 赤外led素子 | |

| WO2023085161A1 (ja) | 半導体発光素子、発光モジュール、及び発光モジュールの製造方法 | |

| US9287481B2 (en) | Vertical nitride semiconductor device and method for manufacturing same | |

| JP2013258207A (ja) | 半導体発光素子及びその製造方法 | |

| WO2022019054A1 (ja) | 半導体レーザおよび半導体レーザ装置 | |

| JP4960777B2 (ja) | 端面発光型半導体レーザチップ | |

| US20230335972A1 (en) | Semiconductor laser and semiconductor laser device | |

| JP2008294421A (ja) | 半導体レーザ素子およびその製造方法 | |

| JP2004088000A (ja) | 半導体レーザ素子の製造方法及び半導体レーザ素子 |