JP2019180621A - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP2019180621A JP2019180621A JP2018072828A JP2018072828A JP2019180621A JP 2019180621 A JP2019180621 A JP 2019180621A JP 2018072828 A JP2018072828 A JP 2018072828A JP 2018072828 A JP2018072828 A JP 2018072828A JP 2019180621 A JP2019180621 A JP 2019180621A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- signal

- power supply

- pattern

- shape

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

Description

本発明は、遊技を行うことが可能な遊技機に関する。 The present invention relates to a gaming machine capable of playing a game.

従来、複数の電子部品が実装された基板を備える遊技機において、基板に実装されているROMの管理情報が記されたシールを、基板を構成するフレキシブル基板に貼付したものがある(例えば、特許文献1参照)。 2. Description of the Related Art Conventionally, in a gaming machine including a board on which a plurality of electronic components are mounted, there is one in which a sticker on which management information of a ROM mounted on a board is written is attached to a flexible board constituting the board (for example, a patent Reference 1).

しかしながら、特許文献1にあっては、遊技機の製造時における搬送工程や基板を組み付ける工程等において、シールの縁部に物が接触する等によって、シールが剥がれたり、位置がずれたり、或いは一部が離れて折れ曲がってしまうことがあり、該シールに記されている情報の確認や読み取りを良好に行うことができなくなってしまうという問題があった。

However, in

本発明は、このような問題点に着目してなされたもので、シールに記されている情報の確認や読み取りを良好に行うことができなくなってしまうことを防ぐことのできる遊技機を提供することを目的とする。 The present invention has been made paying attention to such problems, and provides a gaming machine capable of preventing a situation in which confirmation and reading of information written on a sticker cannot be performed satisfactorily. For the purpose.

前記課題を解決するために、本発明の手段1に記載の遊技機は、

遊技を行うことが可能な遊技機(例えば、パチンコ遊技機1)であって、

複数の電子部品(例えば、演出制御用CPU120、ROM121、RAM122等)が実装された基板(例えば、演出制御基板12)を備え、

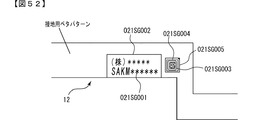

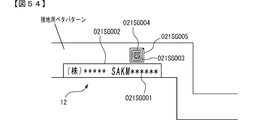

前記基板は、当該基板に関する情報が読み取り可能に記されたシールが貼着されるシール貼着部(例えば、製造日やロット番号やシリアル番号等の第2情報が読み取り可能にシンボル化された二次元バーコードが印刷されたシール021SG003が貼着される第2情報表示部021SG004)を有し、

前記シール貼着部は、基板上に形成された配線パターン及び接地パターンとは異なる部分に設けられている(例えば、第2情報表示部021SG004は、配線パターンや接地用ベタパターンを構成する銅箔021SG010がエッチングによって除去されることで、配線パターンや接地用ベタパターンが形成されていない部分に設けられている)

ことを特徴としている。

この特徴によれば、シールに記されている基板に関する情報の確認や読み取りを良好に行うことができなくなってしまうことを防ぐことができる。

In order to solve the above-described problem, a gaming machine according to

A gaming machine capable of performing a game (for example, a pachinko gaming machine 1),

Provided with a board (for example, effect control board 12) on which a plurality of electronic components (for example,

The board has a sticker pasted with a sticker on which information about the board is readable (for example, second information such as a manufacturing date, a lot number, a serial number, etc. is symbolized so that it can be read. A second information display unit 021SG004) to which a sticker 021SG003 printed with a dimension barcode is attached,

The seal sticking portion is provided in a portion different from the wiring pattern and the ground pattern formed on the substrate (for example, the second information display portion 021SG004 is a copper foil constituting the wiring pattern or the ground solid pattern). (021SG010 is removed by etching so that the wiring pattern and the grounding solid pattern are not formed)

It is characterized by that.

According to this feature, it is possible to prevent the information related to the substrate written on the sticker from being properly confirmed and read.

本発明の手段2の遊技機は、手段1に記載の遊技機であって、

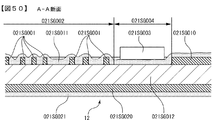

前記シール貼着部は、前記配線パターン及び前記接地パターンを構成する導電材が形成されていない部分である(例えば、第2情報表示部021SG004は、図50に示すように、配線パターンや接地用ベタパターンを構成する銅箔021SG010がエッチングによって除去されて凹んだ部分である)

ことを特徴としている。

この特徴によれば、シール貼着部が、導電材の厚み分だけ凹んだ部分となるので、基板に関する情報の確認や読み取りを良好に行うことができなくなってしまうことを、より一層防ぐことができる。

The gaming machine of

The seal sticking portion is a portion where the conductive material constituting the wiring pattern and the ground pattern is not formed (for example, the second information display portion 021SG004 has a wiring pattern or grounding portion as shown in FIG. 50). (The copper foil 021SG010 constituting the solid pattern is removed by etching and is a recessed portion)

It is characterized by that.

According to this feature, since the sticking portion of the seal is a portion that is recessed by the thickness of the conductive material, it is possible to further prevent the information related to the substrate from being unable to be confirmed and read satisfactorily. it can.

本発明の手段3の遊技機は、手段1または手段2に記載の遊技機であって、

前記シール貼着部は、前記基板の1の面のみに設けられている(例えば、第2情報表示部021SG004は、演出制御基板12の表面(部品実装面)のみに設けられている)

ことを特徴としている。

この特徴によれば、1の面のみにシールを貼着するだけでよいので、シール貼着部を設けるための負荷を低減できる。

The gaming machine of

The seal sticking portion is provided only on one surface of the substrate (for example, the second information display portion 021SG004 is provided only on the surface (component mounting surface) of the effect control substrate 12).

It is characterized by that.

According to this feature, since it is only necessary to stick the seal on only one surface, the load for providing the seal attaching portion can be reduced.

本発明の手段4の遊技機は、手段1〜手段3のいずれかに記載の遊技機であって、

前記基板(例えば、演出制御基板12)は、前記シールに記された情報とは異なる情報であって、当該基板を識別するための識別情報(例えば、製造会社名と型式IDとから成る第1情報)が読み取り可能に表示された識別情報表示部(例えば、第1情報表示部021SG002)を有し、

前記識別情報表示部は、前記シール貼着部の近傍に設けられている(例えば、図49において、第1情報表示部021SG002が、第2情報表示部021SG004に隣接して設けられている)

ことを特徴としている。

この特徴によれば、基板に関する情報と識別情報の読み取り効率を向上できる。

The gaming machine of

The board (for example, the production control board 12) is information different from the information written on the sticker, and includes identification information for identifying the board (for example, a first name consisting of a manufacturer name and a model ID). Information) is displayed in a readable manner (for example, the first information display unit 021SG002),

The identification information display part is provided in the vicinity of the sticker sticking part (for example, in FIG. 49, the first information display part 021SG002 is provided adjacent to the second information display part 021SG004).

It is characterized by that.

According to this feature, it is possible to improve the reading efficiency of information on the substrate and identification information.

本発明の手段5の遊技機は、手段4に記載の遊技機であって、

前記識別情報表示部は、前記基板の表裏面の双方に設けられている(例えば、第1情報表示部021SG002における第1情報021SG001と同一の記号021SG006が、演出制御基板12の裏面側に設けられた第3情報表示部021SG007に記されている)

ことを特徴としている。

この特徴によれば、基板の表裏面のいずれにおいても、第1情報を確認することができる。

The gaming machine of

The identification information display unit is provided on both the front and back surfaces of the substrate (for example, the same symbol 021SG006 as the first information 021SG001 in the first information display unit 021SG002 is provided on the back side of the

It is characterized by that.

According to this feature, the first information can be confirmed on both the front and back surfaces of the substrate.

本発明の手段6の遊技機は、手段4または手段5に記載の遊技機であって、

前記シール貼着部と前記識別情報表示部とは、前記基板の同一辺に沿って並んで設けられている(例えば、第2情報表示部021SG004と第1情報表示部021SG002とが、図49に示すように、演出制御基板12の切り欠きを有する外周辺に沿って並んで設けられている)

ことを特徴としている。

この特徴によれば、基板に関する情報と識別情報とを認識し易くでき、的確な読み取りを行うことができる。

The gaming machine of means 6 of the present invention is the gaming machine according to

The seal sticking part and the identification information display part are provided side by side along the same side of the substrate (for example, the second information display part 021SG004 and the first information display part 021SG002 are shown in FIG. As shown, the

It is characterized by that.

According to this feature, it is possible to easily recognize the information about the substrate and the identification information and perform accurate reading.

本発明の手段7の遊技機は、手段4〜手段6のいずれかに記載の遊技機であって、

前記シール貼着部と前記識別情報表示部との間には、電子部品が実装されていない(例えば、第2情報表示部021SG004と第1情報表示部021SG002との境界に位置する銅箔021SG010が全てエッチングされて除去されていることで、図49並びに図50に示すように、該境界には、いずれの電子部品も実装されていない部分)

ことを特徴としている。

この特徴によれば、基板に関する情報と識別情報の読み取りが、電子部品に邪魔されてしまうことを防ぐことができる。

A gaming machine of means 7 of the present invention is the gaming machine according to any one of

No electronic component is mounted between the seal sticking part and the identification information display part (for example, the copper foil 021SG010 located at the boundary between the second information display part 021SG004 and the first information display part 021SG002) (Each part is not mounted with any electronic component at the boundary, as shown in FIGS. 49 and 50).

It is characterized by that.

According to this feature, reading of information related to the substrate and identification information can be prevented from being disturbed by electronic components.

本発明の手段8の遊技機は、手段4〜手段7のいずれかに記載の遊技機であって、

前記基板(例えば、演出制御基板12)が収納されている基板ケース(例えば、基板ケース800)を備え、

前記シール貼着部と前記識別情報表示部とは、前記基板が前記基板ケースに収納されている状態においても、前記基板ケースの外側から視認可能である(例えば、基板ケース800の外部から、基板ケース800の内部に収納されている演出制御基板12における第1情報表示部021SG002と第2情報表示部021SG004とを視認可能である)

ことを特徴としている。

この特徴によれば、基板ケースの外側から、基板に関する情報と識別情報を読み取ることができる。

The gaming machine of

A substrate case (for example, substrate case 800) in which the substrate (for example, the production control substrate 12) is stored;

The seal sticking portion and the identification information display portion are visible from the outside of the substrate case even when the substrate is housed in the substrate case (for example, from the outside of the

It is characterized by that.

According to this feature, information on the substrate and identification information can be read from the outside of the substrate case.

尚、本発明は、本発明の請求項に記載された発明特定事項のみを有するものであって良いし、本発明の請求項に記載された発明特定事項とともに該発明特定事項以外の構成を有するものであってもよい。 In addition, this invention may have only the invention specific matter described in the claim of this invention, and has a structure other than this invention specific matter with the invention specific matter described in the claim of this invention. It may be a thing.

図1は、この実施の形態に係るパチンコ遊技機1の正面図である。パチンコ遊技機1は、遊技盤2と、遊技機用枠3とを備えている。その他、パチンコ遊技機1は、遊技機用枠3を回動可能に支持する外枠などを備えている。遊技盤2は、遊技盤面を構成するゲージ盤である。遊技機用枠3は、遊技盤2を固定する台枠である。遊技盤2には、ガイドレールなどによって囲まれた遊技領域が形成されている。発射装置から発射された遊技球(遊技媒体)は、発射通路を通過して、遊技領域に打ち込まれる。遊技機用枠3には、ガラス窓を有するガラス扉枠が回動可能に設けられている。

FIG. 1 is a front view of a

遊技盤2の所定位置には、第1特別図柄表示装置4A、第2特別図柄表示装置4B、画像表示装置5、普通入賞球装置6A、普通可変入賞球装置6B、特別可変入賞球装置7、普通図柄表示器20、第1保留表示器25A、第2保留表示器25B、普図保留表示器25C、通過ゲート41などが設けられている。その他、遊技領域における遊技盤面には、風車や多数の障害釘、一般入賞口、アウト口などが設けられていればよい。遊技領域の周辺部には遊技効果ランプ9が設けられている。遊技機用枠3の左右上部位置にはスピーカ8L、8Rが設けられている。

At predetermined positions on the

遊技機用枠3の右下部位置には、打球操作ハンドル(操作ノブ)が設けられている。打球操作ハンドルは、遊技球を遊技領域に向けて発射するために遊技者等によって操作され、その操作量(回転量)に応じて遊技球の弾発力が調整される。遊技領域の下方における遊技機用枠3の所定位置には、遊技球を保持(貯留)する上皿(打球供給皿)と、上皿からの余剰球などを保持(貯留)する下皿が設けられている。下皿を形成する部材にはスティックコントローラ31Aが取り付けられ、上皿を形成する部材にはプッシュボタン31Bが設けられている。

A hitting operation handle (operation knob) is provided at the lower right position of the

第1特別図柄表示装置4A、第2特別図柄表示装置4B、画像表示装置5の画面上などでは、特別図柄や飾り図柄の可変表示が行われる。これらの可変表示は、普通入賞球装置6Aに形成された第1始動入賞口を遊技球が通過(進入)したことによる第1始動入賞の発生に基づいて、あるいは、普通可変入賞球装置6Bに形成された第2始動入賞口を遊技球が通過(進入)したことによる第2始動入賞の発生に基づいて、実行可能となる。第1特別図柄表示装置4Aと第2特別図柄表示装置4Bはそれぞれ、例えば7セグメントやドットマトリクスのLED(発光ダイオード)などを用いて構成され、可変表示ゲームの一例となる特図ゲームにおいて、識別情報(特別識別情報)である特別図柄(特図)が、変動可能に表示(可変表示)される。画像表示装置5は、例えばLCD(液晶表示装置)などを用いて構成され、各種の演出画像を表示する表示領域を形成している。画像表示装置5の画面上では、特図ゲームにおける第1特別図柄表示装置4Aによる特別図柄(第1特図)の可変表示や第2特別図柄表示装置4Bによる特別図柄(第2特図)の可変表示のそれぞれに対応して、例えば3つといった複数の可変表示部となる飾り図柄表示エリアにて、識別情報(装飾識別情報)である飾り図柄が可変表示される。この飾り図柄の可変表示も、可変表示ゲームに含まれる。一例として、画像表示装置5の画面上には、「左」、「中」、「右」の飾り図柄表示エリア5L、5C、5Rが配置されている。

On the screens of the first special

画像表示装置5の画面上には、保留記憶表示エリア5Hが配置されている。保留記憶表示エリア5Hでは、特図ゲームに対応した可変表示の保留数(特図保留記憶数)を特定可能に表示する保留表示が行われる。保留表示は、可変表示に関する情報の保留記憶に対応して表示可能なものであればよい。保留記憶表示エリア5Hとともに、あるいは、保留記憶表示エリア5Hに代えて、第1保留表示器25Aと第2保留表示器25Bとを用いた保留表示が行われてもよい。

On the screen of the

図2は、各種基板や周辺装置などの構成例を示すブロック図である。パチンコ遊技機1には、例えば図2に示すような主基板11、演出制御基板12、音声制御基板13、ランプ制御基板14といった、各種制御基板が搭載されている。また、パチンコ遊技機1には、中継基板15、ドライバ基板19、電源基板92なども搭載されている。その他にも、例えば払出制御基板、情報端子基板、発射制御基板、インタフェース基板、タッチセンサ基板などといった、各種の基板が搭載されてもよい。各種制御基板は、導体パターンが形成されて電気部品が実装されるプリント配線板などの電子回路基板だけではなく、電子回路基板に電気部品が実装(搭載)されて特定の電気的機能を実現するように構成された電子回路実装基板を含む概念である。

FIG. 2 is a block diagram illustrating a configuration example of various substrates and peripheral devices. The

電源基板92は、外部電源(商用電源)である交流電源からの電力を、主基板11や演出制御基板12などの各種制御基板を含めた電気部品に供給可能となるように構成されている。電源基板92は、例えば交流(AC)を直流(DC)に変換するための整流回路、所定の直流電圧を特定の直流電圧(例えば直流12Vや直流5Vなど)に変換するための電源回路などを、備えている。電源基板92にて生成された電圧は、ドロア中継基板を介して主基板11や演出制御基板12などに供給されてもよい。

The

主基板11には、遊技制御用マイクロコンピュータ100、スイッチ回路110、ソレノイド回路111などが搭載されている。主基板11では、ゲートスイッチ21、始動口スイッチ(第1始動口スイッチ22Aおよび第2始動口スイッチ22B)、カウントスイッチ23といった、各種検出用のスイッチから取り込んだ信号が、スイッチ回路110を介して遊技制御用マイクロコンピュータ100に伝送される。ゲートスイッチ21は、通過ゲート41を通過した遊技球(ゲート通過球)を検出する。ゲートスイッチ21によるゲート通過球の検出に基づいて、普通図柄表示器20による普通図柄の可変表示が実行可能となる。第1始動口スイッチ22Aは、第1始動入賞口を通過(進入)した遊技球を検出する。第2始動口スイッチ22Bは、第2始動入賞口を通過(進入)した遊技球を検出する。カウントスイッチ23は、大入賞口を通過(進入)した遊技球を検出する。第1始動入賞口や第2始動入賞口、大入賞口といった、各種の入賞口を通過した遊技球が検出された場合には、それぞれの入賞口に対応して予め個数が定められた賞球としての遊技球が払い出される。

On the

主基板11では、遊技制御用マイクロコンピュータ100からのソレノイド駆動信号が、ソレノイド回路111を介して普通電動役物用のソレノイド81や大入賞口扉用のソレノイド82に伝送される。普通電動役物用のソレノイド81は、普通可変入賞球装置6Bに形成された第2始動入賞口を遊技球が通過しにくい状態(または通過しない状態)と通過しやすい状態(または通過する状態)とに変化可能にする。大入賞口扉用のソレノイド82は、特別可変入賞球装置7に形成された大入賞口を遊技球が通過不可能な状態と通過可能な状態とに変化可能にする。主基板11からは、第1特別図柄表示装置4A、第2特別図柄表示装置4B、普通図柄表示器20などの表示制御を行うための指令信号が伝送される。

On the

主基板11に搭載された遊技制御用マイクロコンピュータ100は、例えば1チップのマイクロコンピュータであり、遊技制御用のプログラムや固定データ等を記憶するROM101と、遊技制御用のワークエリアを提供するRAM102と、遊技制御用のプログラムを実行して制御動作を行うCPU103と、CPU103とは独立して乱数値を示す数値データの更新を行う乱数回路104と、I/O(Input/Output port)105とを備えて構成される。一例として、遊技制御用マイクロコンピュータ100では、CPU103がROM101から読み出したプログラムを実行することにより、パチンコ遊技機1における遊技の進行を制御するための処理が実行される。主基板11に搭載された遊技制御用マイクロコンピュータ100では、例えば乱数回路104やRAM102の所定領域に設けられた遊技用ランダムカウンタなどにより、遊技の進行を制御するために用いられる各種の乱数値を示す数値データが更新可能にカウント(生成)される。遊技の進行を制御するために用いられる乱数は、遊技用乱数ともいう。

The

演出制御基板12は、中継基板15を介して主基板11から伝送された制御信号(演出制御コマンド)の受信に基づいて、画像表示装置5、スピーカ8L、8R、遊技効果ランプ9、演出用モータ60および演出用LED61といった演出用の電気部品による演出動作を制御可能とする。演出制御基板12には、演出制御用CPU120やROM121、RAM122、表示制御部123、乱数回路124、I/O125などが搭載されている。

The

演出制御基板12に搭載された演出制御用CPU120は、ROM121から読み出した演出制御用のプログラムや固定データ等を用いて、演出用の電気部品による演出動作を制御するための処理を実行する。演出制御基板12に搭載された表示制御部123は、演出制御用CPU120からの表示制御指令などに基づき、画像表示装置5における表示動作の制御内容を決定する。例えば、表示制御部123は、画像表示装置5の表示画面内に表示させる演出画像の切換タイミングを決定することなどにより、飾り図柄の可変表示や各種の演出表示を実行させるための制御を行う。

The

演出制御基板12には、コントローラセンサユニット35Aと、プッシュセンサ35Bとが接続されている。コントローラセンサユニット35Aは、傾倒方向センサと、トリガセンサとを含んでいる。傾倒方向センサは、スティックコントローラ31Aの操作桿に対する傾倒操作が行われたときに、複数のセンサを用いて操作桿の傾倒方向を検出可能にする。トリガセンサは、スティックコントローラ31Aの操作桿に設けられたトリガボタンに対する押引操作の有無を検出可能にする。すなわち、コントローラセンサユニット35Aにより、スティックコントローラ31Aの操作桿に対する傾倒動作やトリガボタンに対する押引動作といった、スティックコントローラ31Aを用いた遊技者の動作を検出することができる。プッシュセンサ35Bにより、プッシュボタン31Bに対する押下動作といった、プッシュボタン31Bを用いた遊技者の動作を検出することができる。演出制御基板12では、例えば乱数回路124やRAM122の所定領域に設けられた演出用ランダムカウンタなどにより、演出の実行を制御するために用いられる各種の乱数値を示す数値データが更新可能にカウント(生成)される。演出の実行を制御するために用いられる乱数は、演出用乱数ともいう。

A

演出制御基板12は、第1基板12Aと、該第1基板12Aに対し基板対基板接続される第2基板12Bとを有する。第1基板12Aには、演出制御用CPU120や表示制御部123のグラフィックスプロセッサなどが搭載され、第2基板12Bには、ROM121や画像データメモリといった機種に固有なデータなどが記憶された電気部品が搭載されている。表示制御部123のグラフィックスプロセッサは、演出制御用CPU120の機能を統合したマイクロプロセッサであってもよいし、演出制御用CPU120とは別個のチップとして構成されたマイクロプロセッサであってもよい。

The

音声制御基板13は、演出制御基板12とは別個に設けられた音声出力制御用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、スピーカ8L、8Rから音声を出力させるための音声信号処理を実行する処理回路などが搭載されている。なお、演出制御基板12に搭載された表示制御部123を構成するグラフィックスコントローラなどが音声信号処理を実行可能であれば、音声制御基板13に帯域フィルタや増幅回路などを搭載すればよい。あるいは、音声制御基板13を省略して、演出制御基板12の基板上に帯域フィルタや増幅回路などを搭載してもよい。ランプ制御基板14は、演出制御基板12とは別個に設けられたランプ出力制御用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、遊技効果ランプ9などにおける点灯や消灯を行うランプドライバ回路などが搭載されている。ドライバ基板19は、演出制御基板12とは別個に設けられた電気部品駆動用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、演出用モータ60に含まれる各種モータの回動制御や演出用LED61に含まれる各種LEDの点灯制御などを行うためのドライバ回路などが搭載されている。ドライバ基板19からの出力信号は、演出用モータ60に含まれる各モータと、演出用LED61に含まれる各LEDとに向けて伝送される。

The

パチンコ遊技機1においては、遊技媒体としての遊技球を用いた所定の遊技が行われ、その遊技結果に基づいて所定の遊技価値が付与可能となる。遊技球を用いた遊技の一例として、パチンコ遊技機1における遊技機用枠3の右下部位置に設けられた打球操作ハンドルが遊技者によって所定操作(例えば回転操作)されたことに基づいて、所定の打球発射装置が備える発射モータなどにより、遊技媒体としての遊技球が遊技領域に向けて発射される。遊技領域を流下した遊技球が、各種の入賞口を通過(進入)した場合に、賞球としての遊技球が払い出される。特別図柄や飾り図柄の可変表示結果が「大当り」となった場合には、大入賞口が開放されて遊技球が通過(進入)しやすい状態となることで、遊技者にとって有利な有利状態としての大当り遊技状態となる。

In the

有利状態は大当り遊技状態に限定されず、時短状態や確変状態といった特別遊技状態が含まれてもよい。その他、大当り遊技状態にて実行可能なラウンド遊技の上限回数が第2ラウンド数(例えば「7」)よりも多い第1ラウンド数(例えば「15」)となること、時短状態にて実行可能な可変表示の上限回数が第2回数(例えば「50」)よりも多い第1回数(例えば「100」)となること、確変状態における大当り確率が第2確率(例えば1/50)よりも高い第1確率(例えば1/20)となること、通常状態に制御されることなく大当り遊技状態に繰り返し制御される回数である連チャン回数が第2連チャン数(例えば「5」)よりも多い第1連チャン数(例えば「10」)となることの一部または全部といった、遊技者にとってより有利な遊技状況となることが含まれていてもよい。 The advantageous state is not limited to the big hit gaming state, and may include a special gaming state such as a short time state or a probable change state. In addition, the upper limit number of round games that can be executed in the big hit game state is the first round number (for example, “15”) larger than the second round number (for example, “7”), and it can be executed in the short time state. The upper limit number of variable displays is a first number (for example, “100”) greater than the second number (for example, “50”), and the big hit probability in the probability variation state is higher than the second probability (for example, 1/50). The number of consecutive chunks, which is one probability (for example, 1/20), and the number of repeated control that is repeatedly controlled to the big hit gaming state without being controlled to the normal state is greater than the second consecutive number of channels (for example, “5”). It may include a game situation that is more advantageous for the player, such as a part or all of the fact that the number of consecutive channels (for example, “10”) is reached.

主基板11では、電源基板92からの電力供給が開始されると、遊技制御用マイクロコンピュータ100のCPU103が起動し、CPU103によって遊技制御メイン処理の実行が開始される。遊技制御メイン処理において、CPU103は、割込み禁止に設定した後、必要な初期設定を行う。初期設定が終了すると、割込み許可とした後、ループ処理に入る。以後、所定時間(例えば2ミリ秒)ごとにCTCから割込み要求信号がCPU103へ送出され、CPU103は定期的に遊技制御用タイマ割込み処理を実行する。

In the

遊技制御用タイマ割込み処理は、スイッチ処理、メイン側エラー処理、情報出力処理、遊技用乱数更新処理、特別図柄プロセス処理、普通図柄プロセス処理、コマンド制御処理などを含んでいる。スイッチ処理では、各種スイッチから入力される検出信号の状態を判定する。メイン側エラー処理では、パチンコ遊技機1の異常診断を行い、必要ならば警告を発生可能とする。情報出力処理では、ホール管理コンピュータに供給される所定のデータを出力する。遊技用乱数更新処理では、遊技用乱数の少なくとも一部をソフトウェアにより更新する。特別図柄プロセス処理では、特別図柄の表示制御や大入賞口の開閉動作設定などを、所定の手順で行うために、各種の処理が選択されて実行される。普通図柄プロセス処理では、普通図柄の表示制御や普通可変入賞球装置6Bにおける可動翼片の傾動動作設定などを、所定の手順で行うために、各種の処理が選択されて実行される。

Game control timer interrupt processing includes switch processing, main-side error processing, information output processing, game random number update processing, special symbol process processing, normal symbol process processing, command control processing, and the like. In the switch processing, the state of detection signals input from various switches is determined. In the main-side error processing, abnormality diagnosis of the

特別図柄プロセス処理では、まず、始動入賞判定処理が実行される。始動入賞判定処理を実行した後には、特図プロセスフラグの値に応じて選択した処理が実行される。このとき選択可能な処理は、特別図柄通常処理、変動パターン設定処理、特別図柄変動処理、特別図柄停止処理、大当り開放前処理、大当り開放中処理、大当り開放後処理、大当り終了処理などを含んでいればよい。 In the special symbol process, a start winning determination process is first executed. After the start winning determination process is executed, the process selected according to the value of the special figure process flag is executed. Processes that can be selected at this time include special symbol normal processing, variation pattern setting processing, special symbol variation processing, special symbol stop processing, big jackpot release pre-processing, jackpot release middle processing, jackpot release post-processing, jackpot end processing, etc. It only has to be.

始動入賞判定処理では、第1始動入賞や第2始動入賞が発生したか否かを判定し、発生した場合には特図保留記憶数を更新するための設定などが行われる。特別図柄通常処理では、特図ゲームの実行を開始するか否かの判定が行われる。また、特別図柄通常処理では、特別図柄や飾り図柄の可変表示結果を「大当り」とするか否かの判定が行われる。さらに、特別図柄通常処理では、可変表示結果に対応して、特図ゲームにおける確定特別図柄の設定などが行われる。変動パターン設定処理では、可変表示結果などに基づいて、変動パターンの決定などが行われる。特別図柄変動処理では、特別図柄を変動させるための設定や、変動開始からの経過時間を計測するための設定などが行われる。特別図柄停止処理では、特別図柄の変動を停止させ、可変表示結果となる確定特別図柄を停止表示(導出)させるための設定などが行われる。 In the start winning determination process, it is determined whether or not a first start winning or a second start winning has occurred, and if it has occurred, a setting for updating the special figure holding memory number is performed. In the special symbol normal process, it is determined whether or not to start execution of the special symbol game. In the special symbol normal process, it is determined whether or not the variable display result of the special symbol or the decorative symbol is “big hit”. Further, in the special symbol normal process, setting of a confirmed special symbol in the special symbol game is performed in accordance with the variable display result. In the variation pattern setting process, the variation pattern is determined based on the variable display result. In the special symbol variation process, a setting for varying the special symbol, a setting for measuring the elapsed time from the start of variation, and the like are performed. In the special symbol stop process, the setting for stopping the change of the special symbol and stopping and displaying (deriving) the fixed special symbol that is the variable display result is performed.

大当り開放前処理では、可変表示結果が「大当り」に対応して、大当り遊技状態において大入賞口を開放状態とするための設定などが行われる。大当り開放中処理では、大入賞口を開放状態から閉鎖状態に戻すか否かの判定などが行われる。大当り開放後処理では、大入賞口を閉鎖状態に戻した後、ラウンドの実行回数が上限値に達したか否かを判定し、達していなければ次回のラウンドを実行可能とし、達していれば大当り遊技状態を終了させるための設定などが行われる。大当り終了処理では、大当り遊技状態の終了を報知するエンディング演出の実行期間に対応した待ち時間が経過するまで待機した後、確変制御や時短制御を開始するための設定などが行われる。 In the big hit release pre-processing, the variable display result corresponds to “big hit”, and settings are made to open the big winning opening in the big hit gaming state. In the big hit opening process, it is determined whether or not to return the big prize opening from the open state to the closed state. In the process after opening the jackpot, after returning the grand prize opening to the closed state, it is determined whether or not the number of rounds has reached the upper limit. If not, the next round can be executed. Settings for ending the big hit gaming state are performed. In the big hit end process, after waiting until a waiting time corresponding to the execution period of the ending effect for notifying the end of the big hit gaming state elapses, settings for starting the probability change control and the short time control are performed.

演出制御基板12では、電源基板92からの電力供給が開始されると、演出制御用CPU120が演出制御メイン処理の実行を開始する。演出制御メイン処理では、所定の初期化が行われた後、タイマ割込みが発生する毎に、コマンド解析処理、演出制御プロセス処理、演出用乱数更新処理が実行される。コマンド解析処理では、主基板11から伝送された演出制御コマンドを解析し、解析結果に応じたフラグがセットされる。演出制御プロセス処理では、演出用の電気部品を所定の手順に従って制御するために、各種の処理が選択されて実行される。演出用乱数更新処理では、演出用乱数を生成するためのカウント値などをソフトウェアにより更新する。

In the

演出制御プロセス処理では、まず、保留表示更新処理が実行される。保留表示更新処理を実行した後には、演出プロセスフラグの値に応じて選択した処理が実行される。このとき選択可能な処理は、可変表示開始待ち処理、可変表示開始設定処理、可変表示中演出処理、可変表示停止処理、大当り表示処理、大当り中演出処理、エンディング演出処理などを含んでいればよい。 In the production control process, first, a hold display update process is executed. After executing the hold display update process, the process selected according to the value of the effect process flag is executed. Processes that can be selected at this time may include variable display start waiting processing, variable display start setting processing, variable display effect processing, variable display stop processing, jackpot display processing, jackpot effect processing, ending effect processing, and the like. .

保留表示更新処理では、保留記憶表示エリア5Hの表示を、特図保留記憶数に応じて更新するための設定などが行われる。可変表示開始待ち処理では、特別図柄や飾り図柄の可変表示を開始するか否かの判定などが行われる。可変表示開始設定処理では、飾り図柄の可変表示を開始するための設定などが行われる。可変表示中演出処理では、飾り図柄の可変表示に対応して、演出用の電気部品を演出制御パターンに従って制御するための設定などが行われる。可変表示停止処理では、飾り図柄の可変表示を停止して可変表示結果となる確定飾り図柄を導出する制御などが行われる。

In the hold display update process, settings for updating the display of the hold

大当り表示処理では、可変表示結果が「大当り」に対応して、大当りの発生を報知する演出(ファンファーレ演出)を実行するための制御などが行われる。大当り中演出処理では、大当り遊技状態に対応して、演出用の電気部品を演出制御パターンに従って制御するための設定などが行われる。エンディング演出処理では、大当り遊技状態の終了に対応して、エンディング演出の実行を制御するための設定などが行われる。 In the jackpot display process, control for executing an effect (fanfare effect) for notifying the occurrence of the jackpot corresponding to the variable display result corresponding to “big hit” is performed. In the big hit effect processing, setting for controlling the electric parts for the production according to the production control pattern is performed corresponding to the big hit gaming state. In the ending effect process, setting for controlling the execution of the ending effect is performed in response to the end of the big hit gaming state.

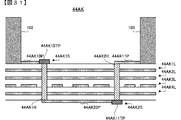

図3は、パチンコ遊技機1が備える遊技機用枠3の背面図である。遊技機用枠3の背面上部には、球タンク150、ターミナル基板154が設けられている。また、補給通路151、払出装置152、賞球通路153も設けられている。遊技盤2の背面には、遊技制御基板用の基板ケース400、演出制御基板用の基板ケース800、カバー体301が設けられている。基板ケース400は、主基板11を収納する。基板ケース800は、演出制御基板12を収納する。カバー体301は、透明な合成樹脂などを用いて構成され、基板ケース800と基板ケース400の上部とを覆っている。遊技制御基板用の基板ケース400の下方位置には、払出制御基板91と、電源基板92とが、前後に重畳するように設けられている。

FIG. 3 is a rear view of the

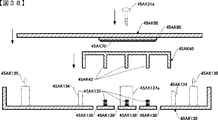

図4〜図7を参照して、演出制御基板用の基板ケース800の構造を説明する。図4は、基板ケース800を左後部の斜め上方から見た状態を示す分解斜視図である。図5は、基板ケース800を右前部の斜め上方から見た状態を示す分解斜視図である。図6は、ベース部材801を示す6面図である。図7は、カバー部材802を示す6面図である。基板ケース800は、ベース部材801と、カバー部材802とから構成され、演出制御基板12を前後から挟持するように組み付けられる。ベース部材801は演出制御基板12の前面側を覆い、カバー部材802は演出制御基板12の背面側を覆う。

With reference to FIGS. 4-7, the structure of the board |

ベース部材801は、透明な熱可塑性合成樹脂からなり、縦長略長方形状に形成されるベース板801aと、上下及び左右側辺に背面側に向けて立設される側壁801b〜801eとから構成され、背面側に向けて開口する箱状に形成されている。ベース板801aには、ボス803、804、係止バー805、係止フック806、係止孔807、被係止部808、ワンウェイネジ809のネジ穴810、取付孔811、基板支持用リブ812、813、段部814a、814b、リブ815が設けられている。

The

カバー部材802は、透明な熱可塑性合成樹脂からなり、縦長略長方形状に形成されるベース板821aと、上下及び左右側辺に背面側に向けて立設される側壁821b〜811eとから構成され、背面側に向けて開口する箱状に形成されている。ベース板821aには、ネジ822が螺入されるネジ穴823、位置決め凸部824、ネジ825が螺入されるネジ穴826、位置決め凸部827、係止フック831、係止片832、係止部833、ワンウェイネジ809の取付孔834aが形成された取付片834、音量調整用スイッチ835aを外部に臨ませるスイッチ用開口835、コネクタ用開口836、837が設けられている。

The

コネクタ用開口836は、ベース板821aの上部右側にて、第1基板12Aに搭載された各種基板側コネクタKCN10を外部に臨ませるために、縦長形状となるように形成されている。各種基板側コネクタKCN10は、レセプタクルKRE1〜KRE4を含んでいればよい。レセプタクルKRE1は、主基板配線用のコネクタポートである。レセプタクルKRE2は、電源基板配線用のコネクタポートである。レセプタクルKRE3は、ドライバ基板配線用のコネクタポートである。レセプタクルKRE4は、音声制御基板配線用のコネクタポートである。なお、レセプタクルの配置や接続される配線は、パチンコ遊技機1の仕様に応じて任意に変更されたものであってもよい。

The

主基板配線用のレセプタクルKRE1は、主基板11との間で電気的に接続される信号配線(主基板配線)を着脱自在に接続可能な配線接続装置の構成を有している。電源基板配線用のレセプタクルKRE2は、電源基板92との間で電気的に接続される信号配線(電源基板配線)を着脱自在に接続可能な配線接続装置の構成を有している。ドライバ基板配線用のレセプタクルKRE3は、ドライバ基板19との間で電気的に接続される信号配線(ドライバ基板配線)を着脱自在に接続可能な配線接続装置の構成を有している。音声制御基板配線用のレセプタクルKRE4は、音声制御基板13との間で電気的に接続される信号配線(音声制御基板配線)を着脱自在に接続可能な配線接続装置の構成を有している。

The receptacle KRE1 for main board wiring has a configuration of a wiring connection device that can detachably connect signal wiring (main board wiring) electrically connected to the

図8〜図10は、レセプタクルKRE1の構成例を示している。図8(A)は、左後部の斜め下方から見た状態を示す斜視図である。図8(B)は、左後部の斜め上方から見た状態を示す斜視図である。図9は、カバー部材802の外部にてレセプタクルKRE1の付近を背面側(後部側)から見た状態を示す背面図である。図10は、レセプタクルKRE1の付近を下方側から見た状態を示す断面図である。レセプタクルKRE1は、差込口OP1が形成されたハウジングと、端子TA01〜TA03とを備えている。

8 to 10 show a configuration example of the receptacle KRE1. FIG. 8A is a perspective view showing a state in which the left rear portion is viewed obliquely from below. FIG. 8B is a perspective view showing a state in which the left rear portion is viewed obliquely from above. FIG. 9 is a rear view showing a state in which the vicinity of the receptacle KRE1 is viewed from the back side (rear side) outside the

差込口OP1は、主基板配線に設けられたコネクタプラグを差し込んで装着可能な開口部である。端子TA01〜TA03は、例えば銅などの金属を用いて構成され、差込口OP1に主基板配線のコネクタプラグが差し込まれたときに、コネクタプラグに設けられた複数の端子のうちで、対応する位置に配置された端子と接触して電気的に導通する金属部材である。レセプタクルKRE1では、信号端子となる端子TA02の両側を挟む位置で、一対の接地端子となる端子TA01、TA03が演出制御基板12の基板上に表面実装されている。主基板配線では、信号伝送線となる信号ラインの両側を挟む位置で、一対の接地電圧線となる接地ラインが設けられていてもよい。あるいは、主基板配線として同軸ケーブルを用いて、同軸ケーブルの内部導体が端子TA02と電気的に接続され、同軸ケーブルの外部導体が端子TA01、TA03と電気的に接続されるように構成してもよい。

The insertion port OP1 is an opening through which a connector plug provided on the main board wiring can be inserted and attached. Terminals TA01 to TA03 are made of metal such as copper, for example, and correspond to a plurality of terminals provided in the connector plug when the connector plug of the main board wiring is inserted into the insertion port OP1. It is a metal member that is in electrical contact with a terminal disposed at a position. In the receptacle KRE1, the terminals TA01 and TA03 serving as a pair of ground terminals are surface-mounted on the board of the

レセプタクルKRE1は、端子配置面となる側面PL1にて、端子TA01〜TA03が外部に引き出され、演出制御基板12(第1基板12A)の基板上に設けられた接続パッドに接合させることができる。端子を接続パッドに接合させる方式は、はんだなどを用いた金属接合方式であってもよいし、導電性樹脂接合や異方性導電部材接合などの接着接合方式であってもよい。側面PL1の背面側となる側面PL2の側には、固定用金具SS01、SS02が設けられている。

In the receptacle KRE1, the terminals TA01 to TA03 are drawn to the outside at the side surface PL1 serving as a terminal arrangement surface, and can be joined to a connection pad provided on the board of the effect control board 12 (

基板ケース800のカバー部材802において、コネクタ用開口836のうちで、レセプタクルKRE1に対応して形成された開口領域836aは、他のレセプタクルに対応して形成された開口領域に比べて開口幅が狭くなるように形成されてもよい。レセプタクルKRE1の端子TA01〜TA03は、それぞれ開口領域836aにて基板ケース800から露出する露出部と基板ケース800に被覆されて露出しない被覆部とを有するように形成されている。例えば、端子TA01〜TA03において、対応する接続パッドに接合する先端部は、基板ケース800のカバー部材802に被覆されて露出しない被覆部に含まれていればよい。

In the

基板ケース800のカバー部材802には、部品収容部802aと、開口領域836aにおける内側端面となる内周壁面836bを形成する開口周縁部840とが、勾配部821e1を介して一体形成されていればよい。部品収容部802aは、演出制御基板12の基板上に実装された電気部品の少なくとも一部を収容可能に形成されている。開口領域836aにおいて、内周壁面836bとレセプタクルKRE1との間隔は、部品収容部802aに遠い側の内周壁面836bとレセプタクルKRE1の側面PL2との間隔が開口幅W1であり、部品収容部802aに近い側の内周壁面836bとレセプタクルKRE1の端子配置面となる側面PL1との間隔が開口幅W2である。そして、開口幅W2は、開口幅W1よりも広くなるように、開口領域836aやレセプタクルKRE1の配置が調整されていればよい。レセプタクルKRE1の端子TA01〜TA03において、対応する接続パッドに接合されて表面実装された実装位置となる先端部は、開口領域836aにおける内周壁面836bを形成する開口周縁部840により被覆される。カバー部材802における開口周縁部840と演出制御基板12の基板面とにより、レセプタクルKRE1の実装位置に近接して、空間としてのスペースSP1が形成されている。

If the

端子TA01は、演出制御基板12の基板上に設けられたダミーパッドDP1に接合される。端子TA03は、演出制御基板12の基板上に設けられたダミーパッドDP2に接合される。また、端子TA01、TA03は、接続パッドGPA1に接合される。接続パッドGPA1は、演出制御基板12に設けられたスルーホールを介して、接地用の配線パターンが形成された配線層LY4に接続されていればよい。図10に示す演出制御基板12の基板断面は、絶縁層LY1と絶縁層LY3との間に配線層LY2が形成され、レセプタクルKRE1が表面実装される側には、例えばポリイミドなどを用いて、保護層LY0が形成されていればよい。このように、演出制御基板12における配線パターンは、演出制御基板12の基板内にて内層部となる絶縁層LY1と絶縁層LY3との間に設けられた配線層LY2に形成されてもよい。あるいは、演出制御基板12における配線パターンは、演出制御基板12の基板上にて表面形成されてもよい。端子TA02は、信号伝送用の配線パターンと電気的に接続された接続パッドに接合される。

Terminal TA01 is joined to dummy pad DP1 provided on the substrate of

レセプタクルKRE1が備える固定用金具SS01は、演出制御基板12の基板上に設けられたダミーパッドDP3に接合される。レセプタクルKRE1が備える固定用金具SS02は、演出制御基板12の基板上に設けられたダミーパッドDP4に接合される。このように、端子TA01〜TA03が配置される側面PL1の背面側となる側面PL2の側にて、固定用金具SS01、SS02が、演出制御基板12の基板上に設けられたダミーパッドDP3、DP4に接合されるようにすればよい。

Fixing bracket SS01 provided in receptacle KRE1 is joined to dummy pad DP3 provided on the board of

主基板11から演出制御基板12に対しては、演出制御コマンドが送信されるところ、そのコマンドを伝送するための主基板配線では、信号伝送線となる信号ラインが1本のみとなる場合がある。これに対応して、演出制御基板12の基板上に表面実装されるレセプタクルKRE1では、信号端子となる端子TA02のみを設ける場合も考えられる。この場合には、レセプタクルKRE1の高さに応じた演出制御基板12の基板表面からの突出量に対して、レセプタクルKRE1の横幅や奥行きに応じた演出制御基板12の基板上における接合面の面積が減少しやすくなるので、レセプタクルKRE1の表面実装による接合強度を十分に確保できなくなるおそれがある。そこで、レセプタクルKRE1では、信号端子となる端子TA02の両側を挟む位置で、一対の接地端子となる端子TA01、TA03が演出制御基板12の基板上に表面実装されるようにする。これにより、レセプタクルKRE1の表面実装による接合強度を十分に確保できる適切な基板構成が可能になる。また、信号端子となる端子TA02の両側が一対の接地端子となる端子TA01、TA03で挟まれているので、ノイズの影響を受けにくい適切な基板構成が可能になる。

When an effect control command is transmitted from the

レセプタクルKRE1において、端子TA01は演出制御基板12の基板上に設けられたダミーパッドDP1に接合され、端子TA03は演出制御基板12の基板上に設けられたダミーパッドDP2に接合される。また、端子TA01〜TA03の先端部は、基板ケース800のカバー部材802に被覆されるように配置する。このように、端子TA01、TA03がダミーパッドDP1、DP2に接合されているので、レセプタクルKRE1の表面実装による接合強度を十分に確保できる適切な基板構成が可能になる。端子TA01〜TA03の先端部が基板ケース800のカバー部材802に被覆されるので、端子と基板面との接合部分といった、表面実装における重要な部位を保護できる適切な基板構成が可能になる。なお、信号端子となる端子TA02については、ダミーパッドに接合されてもよいし、ダミーパッドには接合されないようにしてもよい。信号端子となる端子TA02をダミーパッドには接合されないようにすることで、導体形状の影響による信号劣化を防止してもよい。

In receptacle KRE1, terminal TA01 is joined to dummy pad DP1 provided on the board of

レセプタクルKRE1において、端子TA01〜TA03が配置される側面PL1の背面側となる側面PL2の側にて、固定用金具SS01は演出制御基板12の基板上に設けられたダミーパッドDP3に接合され、固定用金具SS02は演出制御基板12の基板上に設けられたダミーパッドDP4に接合される。このように、固定用金具SS01、SS02がダミーパッドDP3、DP4に接合されているので、レセプタクルKRE1の表面実装による接合強度を十分に確保できる適切な基板構成が可能になる。なお、固定用金具SS01、SS02などの金属部材を基板上に接合する方法によらず、例えばレセプタクルKRE1のハウジングと同様の合成樹脂などを用いた固定部材を基板上に接着させるといった、任意の固定部材を基板上に接合できるものであればよい。

In receptacle KRE1, fixing metal fitting SS01 is joined and fixed to dummy pad DP3 provided on the board of

基板ケース800のカバー部材802における部品収容部802aは、演出制御基板12の基板上に実装された電気部品の少なくとも一部を収容可能に形成され、開口領域836aにおける内周壁面836bとレセプタクルKRE1との間隔は、部品収容部802aに近い側の開口幅W2が遠い側の開口幅W1よりも広く形成されている。部品収容部802aに近い側は、レセプタクルKRE1において端子TA01〜TA03が外部に引き出される端子配置面となる側面PL1の側となる。これに対し、部品収容部802aに遠い側は、レセプタクルKRE1において端子配置面の背面側となる側面PL2の側となる。したがって、開口領域836aにおける内周壁面836bとレセプタクルKRE1との間隔は、端子配置面となる側面PL1に対応する側の開口幅W2が端子配置面の背面となる側面PL2に対応する側の開口幅W1よりも広く形成されている。このように開口幅が調整されているので、例えばカバー部材802を容易に取り付けたり取り外したり位置合わせができる適切な基板構成が可能になる。また、カバー部材802の取付け時や取外し時にレセプタクルKRE1の端子配置面とカバー部材802とが衝突することによる破損を抑制できる適切な基板構成が可能になる。

The

レセプタクルKRE1の端子TA01〜TA03は、それぞれ開口領域836aにて基板ケース800のカバー部材802により被覆されず露出する露出部と基板ケース800のカバー部材802により被覆されて露出しない被覆部とが形成される。このように、各端子TA01〜TA03には、露出部とは異なり、被覆されて露出しない被覆部が形成されるので、端子と基板面との接合部分といった、表面実装における重要な部位を保護できる適切な基板構成が可能になる。

Terminals TA01 to TA03 of receptacle KRE1 are each formed with an exposed portion that is not covered and exposed by

レセプタクルKRE1の端子TA01〜TA03において、演出制御基板12の基板上で対応する接続パッドに接合するように表面実装された実装位置は、開口領域836aにおける内周壁面836bを形成するカバー部材802の開口周縁部840により被覆される。そして、カバー部材802の開口周縁部840と演出制御基板12の基板面とにより、レセプタクルKRE1の実装位置に近接するスペースSP1が形成される。このように、カバー部材802の開口周縁部840と演出制御基板12の基板面とが位置調整可能に配置されるので、レセプタクルKRE1の実装位置を保護できる適切な基板構成が可能になる。

At the terminals TA01 to TA03 of the receptacle KRE1, the mounting positions that are surface-mounted so as to be joined to the corresponding connection pads on the board of the

図11(A)は、主基板配線に対応する伝送経路を示している。図11(A)に示すように、主基板配線用のレセプタクルKRE1にて、端子TA02に供給された信号SCDは、入力ドライバ回路130を介して、演出制御用CPU120に入力される。レセプタクルKRE1の端子TA01、TA03は、接地(グランドラインに接続)されている。

FIG. 11A shows a transmission path corresponding to the main board wiring. As shown in FIG. 11A, the signal SCD supplied to the terminal TA02 at the receptacle KRE1 for main board wiring is input to the

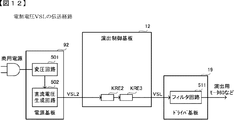

図11(B)は、電源基板配線に対応する伝送経路を示している。電源基板配線用のレセプタクルKRE2は、端子TA11〜TA30を備えている。このうち、レセプタクルKRE2において外側に対応する端子TA11、TA12と端子TA29、TA30とは、いずれも接地(グランドラインに接続)されている。また、端子TA11、TA12、TA29、TA30の他にも、端子TA25、TA26は、接地(グランドラインに接続)されている。レセプタクルKRE2の端子TA13、TA14には、直流34Vの電源電圧VSL2が供給される。レセプタクルKRE2の端子TA15〜TA20には、直流12Vの電源電圧VDD2が供給される。レセプタクルKRE2の端子TA21〜TA24には、直流5Vの電源電圧VCC2が供給される。レセプタクルKRE2の端子TA27、TA28には、直流12Vの電源電圧VDD3が供給される。 FIG. 11B shows a transmission path corresponding to the power supply substrate wiring. The receptacle KRE2 for wiring the power supply board includes terminals TA11 to TA30. Among these, the terminals TA11 and TA12 and the terminals TA29 and TA30 corresponding to the outside in the receptacle KRE2 are all grounded (connected to the ground line). In addition to the terminals TA11, TA12, TA29, and TA30, the terminals TA25 and TA26 are grounded (connected to the ground line). A power supply voltage VSL2 of DC 34V is supplied to the terminals TA13 and TA14 of the receptacle KRE2. A power supply voltage VDD2 of DC 12V is supplied to terminals TA15 to TA20 of the receptacle KRE2. A power supply voltage VCC2 of DC 5V is supplied to terminals TA21 to TA24 of the receptacle KRE2. A DC 12V power supply voltage VDD3 is supplied to the terminals TA27 and TA28 of the receptacle KRE2.

電源基板配線用のレセプタクルKRE2に接続された電源基板配線を経由して電源基板92から演出制御基板12に供給された直流34Vの電源電圧VSL2は、そのまま電源電圧VSLとして演出制御基板12から出力され、ドライバ基板配線用のレセプタクルKRE3に接続されたドライバ基板配線を経由して、ドライバ基板19に供給される。例えば、電源基板配線用のレセプタクルKRE2において、電源電圧VSL2の供給を受ける端子TA13、TA14は、電源ラインLSLに接続され、電源ラインLSLがドライバ基板配線用のレセプタクルKRE3における所定端子に接続されている。図4に示すように、電源基板配線用のレセプタクルKRE2はドライバ基板配線用のレセプタクルKRE3と隣接して設けられ、電源ラインLSLは演出制御基板12における主要な電気回路や電気部品に接近しない演出制御基板12の端部を通過するように配置されていればよい。

The direct current 34V power supply voltage VSL2 supplied from the

図12は、電源電圧VSLの伝送経路を示している。電源基板92では、変圧回路501、直流電圧生成回路502などを用いて、外部電源である商用電源から直流34Vの電源電圧VSL2が生成される。例えば変圧回路501では、交流24Vの電源電圧が生成される。直流電圧生成回路502は、整流回路や平滑回路を含み、交流24Vの電源電圧を整流、平滑して直流34Vの電源電圧VSL2を生成する。直流34Vの電源電圧VSL2は、フィードバック制御などによる電圧制御が行われていないので、交流24Vの電源電圧の変動により、直流34Vの電源電圧VSL2も変動する。このように、レセプタクルKRE2の端子TA13、TA14に供給される直流34Vの電源電圧VSL2は、電圧制御が行われていない変動幅(リップル成分)が大きい直流電圧である。これに対し、レセプタクルKRE2の端子TA15〜TA20に供給される直流12Vの電源電圧VDD2、レセプタクルKRE2の端子TA21〜TA24に供給される直流5Vの電源電圧VCC2、レセプタクルKRE2の端子TA27、TA28に供給される直流12Vの電源電圧VDD3は、いずれも電源基板92において、フィードバック制御による電圧制御が行われ、直流34Vの電源電圧VSLと比較して、変動幅(リップル成分)が少ない直流電圧であればよい。

FIG. 12 shows a transmission path of the power supply voltage VSL. In the

演出制御基板12において、直流34Vの電源電圧VSLに対応する電源ラインLSLにはフィルタ回路などの電圧を安定化する安定化回路が介在しない。その一方で、ドライバ基板19では、直流34Vの電源電圧VSLをフィルタ回路511に入力して、電圧を安定化する。また、演出制御基板12において、直流34Vの電源電圧VSLとは異なる電源電圧に対応する電源ラインにはフィルタ回路などにより電圧を安定化する安定化回路が介在する。

In the

例えば電源基板配線用のレセプタクルKRE2において、直流12Vの電源電圧VDD2が供給される端子TA15〜TA20は、フィルタ回路131aに接続され、直流5Vの電源電圧VCC2が供給される端子TA21〜TA24は、フィルタ回路131bに接続され、直流12Vの電源電圧VDD3が供給される端子TA27、TA28は、フィルタ回路131cに接続されている。フィルタ回路131aの出力部は直流12Vの電源電圧VDSを供給する電源ラインLDSに接続され、フィルタ回路131bの出力部は直流5Vの電源電圧VCCを供給する電源ラインLCCに接続され、フィルタ回路131cの出力部は直流12Vの電源電圧VDCを供給する電源ラインLDCに接続されている。こうして、フィルタ回路131aはレセプタクルKRE2の端子TA15〜TA20と直流12Vの電源電圧VDSに対応する電源ラインLDSとの間に介在し、フィルタ回路131bはレセプタクルKRE2の端子TA21〜TA24と直流5Vの電源電圧VCCに対応する電源ラインLCCとの間に介在し、フィルタ回路131cはレセプタクルKRE2の端子TA27、TA28と直流12Vの電源電圧VDCに対応する電源ラインLDCとの間に介在する。

For example, in the receptacle KRE2 for power supply substrate wiring, the terminals TA15 to TA20 to which the DC 12V power supply voltage VDD2 is supplied are connected to the

電源ラインLSLは、直流34Vの電源電圧VSLを供給するために設けられている。電源ラインLDSは、直流12Vの電源電圧VDSを供給するために設けられている。電源ラインLCCは、直流5Vの電源電圧VCCを供給するために設けられている。電源ラインLDCは、直流12Vの電源電圧VDCを供給するために設けられている。したがって、フィルタ回路が介在しない電源ラインLSLは、フィルタ回路が介在する電源ラインLDS、LCC、LDCのいずれと比較しても、高い電源電圧を供給するために設けられている。 The power supply line LSL is provided to supply a power supply voltage VSL of DC 34V. The power supply line LDS is provided to supply a power supply voltage VDS of DC 12V. The power supply line LCC is provided for supplying a power supply voltage VCC of DC 5V. The power supply line LDC is provided for supplying a power supply voltage VDC of 12V DC. Therefore, the power supply line LSL without the filter circuit is provided to supply a higher power supply voltage than any of the power supply lines LDS, LCC, and LDC with the filter circuit interposed.

レセプタクルKRE2では、直流12Vの電源電圧VDD2が供給される6つの端子TA15〜TA20、直流5Vの電源電圧VCC2が供給される4つの端子TA21〜TA24、直流12Vの電源電圧VDD3が供給される2つの端子TA27、TA28が設けられる一方で、直流34Vの電源電圧VSL2が供給される2つの端子TA13、TA14が設けられる。そのため、レセプタクルKRE2では、電源電圧が供給される端子のうちで、フィルタ回路に接続された端子TA15〜TA20、TA21〜TA24、TA27、TA28の端子数が、フィルタ回路に接続されていない端子TA13、TA14の端子数よりも多くなる。なお、それぞれの電源電圧に対応した端子数は、電源容量や負荷電流に応じて設定したものであればよい。 In the receptacle KRE2, six terminals TA15 to TA20 to which a DC 12V power supply voltage VDD2 is supplied, four terminals TA21 to TA24 to which a DC 5V power supply voltage VCC2 is supplied, and two terminals to which a DC 12V power supply voltage VDD3 is supplied. While terminals TA27 and TA28 are provided, two terminals TA13 and TA14 to which a power supply voltage VSL2 of DC 34V is supplied are provided. Therefore, in the receptacle KRE2, among the terminals to which the power supply voltage is supplied, the number of terminals TA15 to TA20, TA21 to TA24, TA27, and TA28 connected to the filter circuit is equal to the terminal TA13 that is not connected to the filter circuit. More than the number of terminals of TA14. The number of terminals corresponding to each power supply voltage may be set according to the power supply capacity and load current.

レセプタクルKRE2では、端子TA15〜TA20に直流12Vの電源電圧VDD2が供給され、端子TA21〜TA24に直流5Vの電源電圧VCC2が供給され、端子TA27、TA28に直流12Vの電源電圧VDD3が供給される一方で、端子TA13、TA14に直流34Vの電源電圧VSL2が供給される。そして、レセプタクルKRE2の端子TA15〜TA20と直流12Vの電源電圧VDSを供給する電源ラインLDSとの間にはフィルタ回路131aが介在し、レセプタクルKRE2の端子TA21〜TA24と直流5Vの電源電圧VCCを供給する電源ラインLCCとの間にはフィルタ回路131bが介在し、レセプタクルKRE2の端子TA27、TA28と直流12Vの電源電圧VDCを供給する電源ラインLDCとの間にはフィルタ回路131cが介在する。これに対し、レセプタクルKRE2の端子TA13、TA14と直流34Vの電源電圧VSLを供給する電源ラインLSLとの間にはフィルタ回路が介在しない。このように、フィルタ回路が介在する電源ラインLDS、LCC、LDCは、直流12Vあるいは直流5Vといった複数種類の電源電圧を供給可能であり、フィルタ回路が介在しない電源ラインLSLは、直流34Vという一種類の電源電圧を供給可能である。レセプタクルKRE2では、端子TA13、TA14が端子TA15〜TA24などよりも外側に配置されている。あるいは、レセプタクルKRE2では、端子TA15〜TA24、TA27、TA28のうちで、例えば端子TA15〜TA24のように、端子TA13、TA14よりも内側に配置された端子が含まれている。

In the receptacle KRE2, a 12V DC power supply voltage VDD2 is supplied to the terminals TA15 to TA20, a 5V DC power supply voltage VCC2 is supplied to the terminals TA21 to TA24, and a 12V DC power supply voltage VDD3 is supplied to the terminals TA27 and TA28. Thus, the power supply voltage VSL2 of DC 34V is supplied to the terminals TA13 and TA14. A

レセプタクルKRE2では、端子TA11、TA12と、端子TA29、TA30との間に、端子TA13〜TA24、TA27、TA28が配置される。端子TA13〜TA24、TA27、TA28は、いずれも電源電圧が供給される端子であり、各種の電源電圧に接続される電源電圧端子となる。これに対し、端子TA11、TA12と、端子TA29、TA30とは、いずれも電源電圧が供給されない端子であり、接地電圧に接続される接地端子となる。したがって、レセプタクルKRE2では、接地端子となる端子TA11、TA12と端子TA29、TA30との間に、電源電圧端子となる端子TA13〜TA24、TA27、TA28が配置される。 In the receptacle KRE2, terminals TA13 to TA24, TA27, and TA28 are arranged between the terminals TA11 and TA12 and the terminals TA29 and TA30. Terminals TA13 to TA24, TA27, and TA28 are all terminals to which a power supply voltage is supplied, and serve as power supply voltage terminals connected to various power supply voltages. On the other hand, the terminals TA11 and TA12 and the terminals TA29 and TA30 are terminals to which no power supply voltage is supplied, and are ground terminals connected to the ground voltage. Therefore, in the receptacle KRE2, terminals TA13 to TA24, TA27, and TA28 that are power supply voltage terminals are arranged between the terminals TA11 and TA12 that are ground terminals and the terminals TA29 and TA30.

レセプタクルKRE2では、端子TA11、TA12と、端子TA25、TA26との間に、端子TA13、TA14と、端子TA15〜TA24とが配置され、端子TA25、TA26と、端子TA29、TA30との間に、端子TA27、TA28が配置される。端子TA13、TA14は、直流34Vの電源電圧VSL2が供給される端子であり、電源電圧VSL2に接続される電源電圧端子である。端子TA15〜TA20は、直流12Vの電源電圧VDD2が供給される端子であり、電源電圧VDD2に接続される電源電圧端子である。端子TA21〜TA24は、直流5Vの電源電圧VCC2が供給される端子であり、電源電圧VCC2に接続される電源電圧端子である。端子TA27、TA28は、直流12Vの電源電圧VDD3が供給される端子であり、電源電圧VDD3に接続される電源電圧端子である。そのため、直流34Vの電源電圧VSL2に接続される電源電圧端子としての端子TA13、TA14と、直流34Vの電源電圧VSL2以外の電源電圧に接続される電源電圧端子としての端子TA15〜TA24、TA27、TA28のうちの一部である端子TA15〜TA24とが、接地端子となる端子TA11、TA12と端子TA25、TA26との間に配置される。また、直流34Vの電源電圧VSL2以外の電源電圧に接続される電源電圧端子としての端子TA15〜TA24、TA27、TA28のうちで、他の一部である端子TA27、TA28が、接地端子となる端子TA25、TA26と端子TA29、TA30との間に配置される。 In the receptacle KRE2, the terminals TA13 and TA14 and the terminals TA15 to TA24 are arranged between the terminals TA11 and TA12 and the terminals TA25 and TA26, and the terminals TA25 and TA26 are connected between the terminals TA29 and TA30. TA27 and TA28 are arranged. Terminals TA13 and TA14 are terminals to which a power supply voltage VSL2 of DC 34V is supplied, and are power supply voltage terminals connected to the power supply voltage VSL2. Terminals TA15 to TA20 are terminals to which a 12V DC power supply voltage VDD2 is supplied and are connected to the power supply voltage VDD2. Terminals TA21 to TA24 are terminals to which a power supply voltage VCC2 of DC 5V is supplied, and are power supply voltage terminals connected to the power supply voltage VCC2. Terminals TA27 and TA28 are terminals to which a DC power supply voltage VDD3 of 12V is supplied, and are power supply voltage terminals connected to the power supply voltage VDD3. Therefore, terminals TA13 and TA14 as power supply voltage terminals connected to the power supply voltage VSL2 of DC 34V, and terminals TA15 to TA24, TA27 and TA28 as power supply voltage terminals connected to power supply voltages other than the power supply voltage VSL2 of DC 34V. The terminals TA15 to TA24, which are part of the terminals TA15 and TA24, are arranged between the terminals TA11 and TA12 serving as ground terminals and the terminals TA25 and TA26. Among the terminals TA15 to TA24, TA27, and TA28 as power supply voltage terminals connected to a power supply voltage other than the DC 34V power supply voltage VSL2, the other terminals TA27 and TA28 serve as ground terminals. Arranged between TA25, TA26 and terminals TA29, TA30.

端子TA27、TA28に供給される直流12Vの電源電圧VDD3は、降圧コンバータ回路132により直流1.05Vの電源電圧を生成するために用いられる。直流1.05Vの電源電圧は、例えば表示制御部123のグラフィックスプロセッサといった、特定のマイクロプロセッサに供給される。したがって、レセプタクルKRE2では、電源電圧に接続される端子TA13〜TA24、TA27、TA28のうちで、変動幅(リップル成分)が比較的に大きい直流34Vの電源電圧VSL2に接続される端子TA13、TA14は、表示制御部123のグラフィックスプロセッサといった特定のマイクロプロセッサに供給する電源電圧の生成に用いられる直流12Vの電源電圧VDD3に接続されるTA27、TA28から最も離れて配置される。

The DC 12V power supply voltage VDD3 supplied to the terminals TA27 and TA28 is used by the step-down

演出制御基板12では、直流34Vの電源電圧VSL2を安定化してから電源電圧VSLとして出力する場合も考えられる。しかしながら、演出制御基板12では直接的な用途のない直流34Vの電源電圧VSL2を安定化する回路素子の設置は、部品点数や基板容積の増大を招き、電力損失や製造コストも増加する。また、特別な回路素子の設置により、演出制御基板12のリユースや共通化が困難になるおそれもある。そこで、電圧制御が行われていない直流34Vの電源電圧VSL2は、そのまま電源電圧VSLとして演出制御基板12から出力され、ドライバ基板19にてフィルタ回路511に入力して電圧を安定化する。これにより、部品点数や基板容積の増大、電力損失や製造コストの増加を防止する適切な基板構成が可能になる。また、演出制御基板12のリユースや共通化が容易に行われる適切な基板構成が可能になる。また、電源ラインLSLは、演出制御基板12における主要な電気回路や電気部品から離れて配置されることにより、変動幅(リップル成分)が大きい直流電圧によるノイズの悪影響を防止する適切な基板構成が可能になる。

In the

演出制御基板12において、直流34Vの電源電圧VSLを供給する電源ラインLSLは、直流12Vの電源電圧VDSを供給する電源ラインLDS、直流5Vの電源電圧VCCを供給する電源ラインLCC、直流12Vの電源電圧VDSを供給する電源ラインLDSのいずれと比較しても、高い電源電圧となる直流34Vを供給する。一般的に、高い電源電圧を安定化する安定化回路は、低い電源電圧を安定化する安定化回路よりも、回路素子の容積や電力損失が大きなものになりやすく、回路素子の値段が高価なものになりやすい。そこで、高い電源電圧となる直流34Vの電源電圧VSLを供給する電源ラインLSLにはフィルタ回路が介在しないことにより、基板容積の増大、電力損失や製造コストの増加を防止する適切な基板構成が可能になる。

In the

レセプタクルKRE2において、2つの端子TA13、TA14には直流34Vの電源電圧VSLが供給される。これに対し、レセプタクルKRE2において、6つの端子TA15〜TA20には直流12Vの電源電圧VDD2が供給され、4つの端子TA21〜TA24には直流5Vの電源電圧VCC2が供給され、2つの端子TA27、TA28には直流12Vの電源電圧VDD3が供給される。したがって、演出制御基板12では、レセプタクルKRE2にて電源電圧が供給される端子のうちで、フィルタ回路131a〜131cのいずれかに接続される端子TA15〜TA24、TA27、TA28の端子数が、フィルタ回路に接続されない端子TA13、TA14の端子数よりも多くなる。このように端子数が設定されているので、例えば演出制御基板12にて電圧を安定化する対象となる電源電圧の用途や電源容量などに応じて、配線設計の自由度を向上させる適切な基板構成が可能になる。

In the receptacle KRE2, a power supply voltage VSL of DC 34V is supplied to the two terminals TA13 and TA14. In contrast, in the receptacle KRE2, a DC 12V power supply voltage VDD2 is supplied to the six terminals TA15 to TA20, and a DC 5V power supply voltage VCC2 is supplied to the four terminals TA21 to TA24. Is supplied with a power supply voltage VDD3 of DC 12V. Therefore, in the

レセプタクルKRE2において、電源電圧が供給される端子のうちで、演出制御基板12にてフィルタ回路131a〜131cのいずれかに接続される端子TA15〜TA24、TA27、TA28は、直流12Vの電源電圧VDD2を供給可能な端子TA15〜TA20と、直流5Vの電源電圧VCC2を供給可能な端子TA21〜TA24と、直流12Vの電源電圧VDD3を供給可能な端子TA27、TA28とを、含んでいる。これに対し、レセプタクルKRE2において、電源電圧が供給される端子のうちで、演出制御基板12ではフィルタ回路に接続されない端子TA13、TA14は、直流34Vの電源電圧VSL2を供給可能であり、他の種類の電源電圧は供給しない。そのため、フィルタ回路が介在する電源ラインであるか、フィルタ回路が介在しない電源ラインであるかに応じて、供給可能な電源電圧の種類数が異なっている。より具体的には、フィルタ回路が介在する電源ラインは、直流12Vの電源電圧VDD2、直流5Vの電源電圧VCC2、直流12Vの電源電圧VDD2といった、複数種類の電源電圧を供給可能であり、フィルタ回路が介在しない電源ラインは、直流34Vの電源電圧VSLという一種類の電源電圧を供給可能である。このように、電源ラインに対応して供給可能な電源電圧の種類数が異なるので、例えば演出制御基板12にて電圧を安定化する対象となる電源電圧の用途などに応じて、配線設計の自由度を向上させる適切な基板構成が可能になる。

In the receptacle KRE2, among the terminals to which the power supply voltage is supplied, the terminals TA15 to TA24, TA27, and TA28 connected to any one of the

また、フィルタ回路が介在しない電源ラインに接続された端子TA13、TA14は、フィルタ回路が介在する電源ラインに接続された端子TA15〜TA24などよりも外側に配置されている。このような端子の配置により、例えば演出制御基板12にて電圧を安定化する対象となる電源電圧の用途などに応じて、配線設計の自由度を向上させる適切な基板構成が可能になる。加えて、端子TA13、TA14に供給された直流34Vの電源電圧VSL2を、そのまま電源電圧VSLとしてドライバ基板19に対して出力するための配線長を短縮する適切な基板構成が可能になる。

The terminals TA13 and TA14 connected to the power supply line not including the filter circuit are disposed outside the terminals TA15 to TA24 connected to the power supply line including the filter circuit. Such an arrangement of terminals enables an appropriate board configuration that improves the degree of freedom in wiring design according to, for example, the use of a power supply voltage for which the voltage is to be stabilized by the

レセプタクルKRE2において、端子TA13〜TA24、TA27、TA28は、各種の電源電圧に接続される電源電圧端子となる。これに対し、レセプタクルKRE2において、端子TA11、TA12と、端子TA29、TA30とは、いずれも接地電圧に接続される接地端子となる。そして、端子TA13〜TA24、TA27、TA28は、端子TA11、TA12と、端子TA29、TA30との間に配置されている。このような端子の配置により、ノイズの影響を受けにくい適切な基板構成が可能になる。また、電源電圧を遮蔽して、ノイズの発生を防止する適切な基板構成が可能になる。 In the receptacle KRE2, the terminals TA13 to TA24, TA27, and TA28 are power supply voltage terminals connected to various power supply voltages. On the other hand, in the receptacle KRE2, the terminals TA11 and TA12 and the terminals TA29 and TA30 are all ground terminals connected to the ground voltage. The terminals TA13 to TA24, TA27, and TA28 are disposed between the terminals TA11 and TA12 and the terminals TA29 and TA30. Such an arrangement of terminals enables an appropriate substrate configuration that is less susceptible to noise. In addition, an appropriate substrate configuration that shields the power supply voltage and prevents the generation of noise can be realized.

レセプタクルKRE2において、端子TA15〜TA24、TA27、TA28は、直流34Vの電源電圧VSL2とは異なる電源電圧に接続される第1電源電圧端子となる。その一方で、レセプタクルKRE2において、端子TA13、TA14は、直流34Vの電源電圧VSL2に接続される第2電源電圧端子となる。また、レセプタクルKRE2において、端子TA11、TA12は接地電圧に接続される第1接地端子となり、端子TA25、TA26は接地電圧に接続される第2接地端子となり、端子TA29、TA30は接地電圧に接続される第3接地端子となる。そして、レセプタクルKRE2では、第2電源電圧端子に含まれる端子TA13、TA14と、第1電源電圧端子に含まれる端子TA15〜TA24とが、第1接地端子に含まれる端子TA11、TA12と、第2接地端子に含まれる端子TA25、TA26との間に配置され、第1電源電圧端子に含まれる端子TA27、TA28が、第2接地端子に含まれる端子TA25、TA26と、第3接地端子に含まれる端子TA29、TA30との間に配置される。このような端子の配置により、ノイズの影響を受けにくい適切な基板構成が可能になる。特に、第2接地端子に含まれる端子TA25、TA26を、第2電源電圧端子に含まれる端子TA13、TA14および第1電源電圧端子に含まれる端子TA15〜TA24と、第1電源電圧端子に含まれるTA27、TA28との間に配置させることで、さらにノイズの影響を受けにくい適切な基板構成が可能になる。また、電源電圧を効率よく遮蔽して、さらにノイズの発生を防止する適切な基板構成が可能になる。加えて、直流34Vの電源電圧VSL2に接続される端子TA13、TA14は、表示制御部123のグラフィックスプロセッサといった特定のマイクロプロセッサに供給する電源電圧の生成に用いられる直流12Vの電源電圧VDD3に接続されるTA27、TA28から離れて配置されるので、特定のマイクロプロセッサがノイズの影響を受けにくい適切な基板構成が可能になる。

In the receptacle KRE2, the terminals TA15 to TA24, TA27, and TA28 are first power supply voltage terminals that are connected to a power supply voltage different from the DC power supply voltage VSL2. On the other hand, in the receptacle KRE2, the terminals TA13 and TA14 become second power supply voltage terminals connected to the power supply voltage VSL2 of DC 34V. In the receptacle KRE2, the terminals TA11 and TA12 are first ground terminals connected to the ground voltage, the terminals TA25 and TA26 are second ground terminals connected to the ground voltage, and the terminals TA29 and TA30 are connected to the ground voltage. A third ground terminal. In the receptacle KRE2, the terminals TA13 and TA14 included in the second power supply voltage terminal, the terminals TA15 to TA24 included in the first power supply voltage terminal, the terminals TA11 and TA12 included in the first ground terminal, and the second The terminals TA27 and TA28 which are disposed between the terminals TA25 and TA26 included in the ground terminal and are included in the first power supply voltage terminal are included in the terminals TA25 and TA26 included in the second ground terminal and the third ground terminal. Arranged between terminals TA29 and TA30. Such an arrangement of terminals enables an appropriate substrate configuration that is less susceptible to noise. In particular, the terminals TA25 and TA26 included in the second ground terminal are included in the terminals TA13 and TA14 included in the second power supply voltage terminal and the terminals TA15 to TA24 included in the first power supply voltage terminal and the first power supply voltage terminal. By disposing them between TA27 and TA28, an appropriate substrate configuration that is less susceptible to noise becomes possible. In addition, an appropriate substrate configuration that efficiently shields the power supply voltage and prevents the generation of noise can be realized. In addition, the terminals TA13 and TA14 connected to the DC 34V power supply voltage VSL2 are connected to the DC 12V power supply voltage VDD3 used to generate a power supply voltage to be supplied to a specific microprocessor such as a graphics processor of the

演出制御基板12では、レセプタクルKRE2の端子TA15〜TA20にて供給された電源電圧VDD2から、分岐点DB1にて電源電圧VDLが分岐される。このような分岐点DB1にて電源電圧VDLが分岐された後に、フィルタ回路131aにより電源電圧VDSを安定化する。電源電圧VDLは、例えば演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するために用いられる直流12Vの電源電圧である。電源電圧VDSは、増幅回路521に供給され、音声信号を出力するために用いられる直流12Vの電源電圧である。このように、フィルタ回路131aは、1の電源電圧VDD2を、電源電圧VDLと電源電圧VDSとに分岐した後に、電源電圧VDSを安定化する。演出制御基板12には、増幅回路521が設けられ、スピーカ8L、8Rに供給される音声信号を出力可能としてもよい。

In the

図13(A)は、電源電圧VDSを供給するための配線における配線長の関係を示している。演出制御基板12において、電源電圧VDSを増幅回路521に供給するための電源ラインLDSは、分岐点DB1からフィルタ回路131aの入力部までの配線長LL1を有する配線と、フィルタ回路131aの出力部から増幅回路521の入力部までの配線長LL2を有する配線とを、含んでいればよい。そして、配線長LL2は、配線長LL1よりも短くなるように、演出制御基板12における配線や回路の配置が調整されていればよい。このように、フィルタ回路131aから増幅回路521までの配線長LL2は、電源電圧VDSを分岐点DB1にて分岐させてからフィルタ回路131aまでの配線長LL1よりも短くなる。なお、増幅回路521やフィルタ回路131aは、演出制御基板12に設置されるものに限定されず、音声制御基板13に設置されてもよい。

FIG. 13A shows the relationship between the wiring lengths of the wirings for supplying the power supply voltage VDS. In the

図13(B)は、増幅回路521やフィルタ回路131aを音声制御基板13に設置した場合における電源電圧VDSの伝送経路を示している。電源基板92では、変圧回路501、直流電圧生成回路502などを用いて、外部電源である商用電源から直流12Vの電源電圧VDD2が生成される。直流12Vの電源電圧VDD2は、電源基板配線用のレセプタクルKRE2において、端子TA15〜TA20に供給される。演出制御基板12では、レセプタクルKRE2の端子TA15〜TA20にて供給された電源電圧VDD2から、分岐点DB1にて電源電圧VDLが分岐された後、そのまま電源電圧VDSとして演出制御基板12から出力され、音声基板配線用のレセプタクルKRE4に接続された音声制御基板配線を経由して、音声制御基板13に供給されてもよい。例えば、電源基板配線用のレセプタクルKRE2において、電源電圧VDD2の供給を受ける端子TA15〜TA20は、電源ラインLDSに接続され、電源ラインLDSが音声制御基板配線用のレセプタクルKRE4における所定端子に接続されていればよい。演出制御基板12において、直流12Vの電源電圧VDSに対応する電源ラインLDSにはフィルタ回路などの電圧を安定化する安定化回路が介在しなくてもよい。その一方で、音声制御基板13では、直流12Vの電源電圧VDSをフィルタ回路131aに入力して、電圧を安定化する。こうして安定化された電源電圧VDSを増幅回路521に供給すればよい。

FIG. 13B shows a transmission path of the power supply voltage VDS when the

音声制御基板13には、音声制御用IC522、音声データROM523などが設けられてもよい。音声制御用IC522は、演出制御基板12の演出制御用CPU120などから出力された指令(音番号データなど)に応じて、音声や効果音を生成するための信号処理を実行する。音声データROM523は、音番号データに応じた制御データを記憶している。音番号データに応じた制御データは、所定期間(例えば飾り図柄の可変表示期間)における音声や効果音の出力態様を時系列的に示すデータの集まりである。なお、音声制御基板13に設けられる各種の構成を、演出制御基板12に設けられるように構成し、音声制御基板13を備えないものであってもよい。

The

音声制御用IC522などにより生成された音声信号を増幅して、スピーカ8L、8Rなどに出力可能な増幅回路521は、電源電圧に変動が生じると、出力される音声信号に歪みが生じるといった、音質に悪影響が及ぶおそれがある。そこで、直流12Vの電源電圧VDSは、フィルタ回路131aにより安定化した後に、増幅回路521に供給される。演出制御基板12において、1の電源電圧VDD2を、特定の電気部品を駆動するための電源電圧VDLと、増幅回路521に供給するための電源電圧VDSとに分岐した後に、フィルタ回路131aを用いて安定化した電源電圧VDSを増幅回路521に供給する。このように、フィルタ回路131aを用いて安定化した電源電圧VDSを増幅回路521に供給することで、増幅回路521を安定して動作させる適切な基板構成が可能になる。

The

増幅回路521に供給するための電源電圧VDSに対応する電源ラインLDSにおいて、フィルタ回路131aから増幅回路521までの配線長LL2は、分岐点DB1にて電源電圧VDLが分岐されてからフィルタ回路131aに入力するまでの配線長LL1よりも短くなる。このように、フィルタ回路131aを用いて安定化した電源電圧VDSを増幅回路521に供給するまでの配線長を短くすることで、ノイズの影響を受けにくく、増幅回路521を安定して動作させる適切な基板構成が可能になる。

In the power supply line LDS corresponding to the power supply voltage VDS supplied to the

演出制御基板12では、レセプタクルKRE2の端子TA21〜TA24にて供給された電源電圧VCC2から、電源電圧VCLが分岐される。電源電圧VCLが分岐された後に、フィルタ回路131bにより電源電圧VCCを安定化する。電源電圧VCLは、例えば演出用モータ60に含まれる特定のモータや演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するために用いられる直流5Vの電源電圧である。電源電圧VCCは、例えば演出制御用CPU120といった、所定の電気回路を駆動するために用いられる直流5Vの直流電源である。このように、フィルタ回路131bは、1の電源電圧VCC2を、電源電圧VCLと電源電圧VDDとに分岐した後の電源電圧VDDを安定化する。

In the

演出制御基板12では、レセプタクルKRE2の端子TA27、TA28にて供給された電源電圧VDD3を、フィルタ回路131cにより安定化した後に、電源電圧VDCを供給可能に分岐させる。電源電圧VDCは、電源断の発生を監視するために用いられる直流12Vの電源電圧である。また、電源電圧VDD3は、フィルタ回路131cにより安定化した後に、降圧コンバータ回路132に入力される。降圧コンバータ回路132は、1入力2出力の直流電圧を変換する回路である。図11に示す降圧コンバータ回路132は、直流12Vの電源電圧VDD3をフィルタ回路131cにより安定化した電圧が入力されて、直流1.05Vの電源電圧と、直流3.3Vの電源電圧とに変換して出力する。降圧コンバータ回路132の出力部は、直流1.05Vの電源電圧を供給する電源ラインL10と、直流3.3Vの電源電圧を供給する電源ラインL33とに接続されている。直流1.05Vの電源電圧は、例えば表示制御部123に含まれるグラフィックスプロセッサといった、所定の電気回路を駆動するために用いられる。直流3.3Vの電源電圧は、例えばROM121や表示制御部123に含まれる画像データメモリといった、所定の電気回路を駆動するために用いられる。直流3.3Vの電源電圧は、レギュレータ回路133にも入力される。レギュレータ回路133は、例えばLDO(Low Drop-Out)レギュレータなどのシリーズレギュレータといったリニア方式の安定化電源回路であればよく、直流3.3Vの電源電圧が入力されて、直流1.5Vの電源電圧に変換して出力する。レギュレータ回路133の出力部は、直流1.5Vの電源電圧を供給する電源ラインL15に接続されている。直流1.5Vの電源電圧は、例えばRAM122といった、所定の電気回路を駆動するために用いられる。

In the

図14は、フィルタ回路131a〜131cの構成例を示している。図14(A)は、電源電圧VDSに対応するフィルタ回路131aの構成例を示している。図14(B)は、電源電圧VCCに対応するフィルタ回路131bの構成例を示している。図14(C)は、電源電圧VDCに対応するフィルタ回路131cの構成例を示している。

FIG. 14 shows a configuration example of the

図14(A)に示すフィルタ回路131aは、三端子コンデンサ85a、バイパスコンデンサC10、C11、電解コンデンサC1を用いて構成されていればよい。バイパスコンデンサC10、C11は、電解コンデンサC1と比較して、高周波のノイズを防止するノイズ対策用の電気部品であり、デカップリングコンデンサともいう。電解コンデンサC1は、バイパスコンデンサC10、C11と比較して、低周波のノイズを防止するノイズ対策用の電気部品である。三端子コンデンサ85aの入力端子(IN)は、フィルタ回路131aの入力部となり、直流12Vの電源電圧VDD2が供給される。三端子コンデンサ85aの出力端子(OUT)は、フィルタ回路131aの出力部となり、電圧が安定化された直流12Vの電源電圧VDSを供給する。三端子コンデンサ85aの接地端子(GND)は、接地(グランドラインに接続)されている。三端子コンデンサ85aの出力端子と接地端子との間には、0.1μFのバイパスコンデンサC10、47μFのバイパスコンデンサC11、1000μFの電解コンデンサC1が、接続されている。

The

図14(B)に示すフィルタ回路131bは、三端子コンデンサ85b、バイパスコンデンサC12、C13、電解コンデンサC2を用いて構成されていればよい。バイパスコンデンサC12、C13は、電解コンデンサC2と比較して、高周波のノイズを防止するノイズ対策用の電気部品である。電解コンデンサC2は、バイパスコンデンサC12、C13と比較して、低周波のノイズを防止するノイズ対策用の電気部品である。三端子コンデンサ85bの入力端子(IN)は、フィルタ回路131bの入力部となり、直流5Vの電源電圧VCC2が供給される。三端子コンデンサ85bの出力端子(OUT)は、フィルタ回路131bの出力部となり、電圧が安定化された直流5Vの電源電圧VCCを供給する。三端子コンデンサ85bの接地端子(GND)は、接地(グランドラインに接続)されている。三端子コンデンサ85bの出力端子と接地端子との間には、0.1μFのバイパスコンデンサC12、47μFのバイパスコンデンサC13、1000μFの電解コンデンサC2が、接続されている。

The

図14(C)に示すフィルタ回路131cは、三端子コンデンサ85c、バイパスコンデンサC14、電解コンデンサC3を用いて構成されていればよい。バイパスコンデンサC14は、電解コンデンサC3と比較して、高周波のノイズを防止するノイズ対策用の電気部品である。電解コンデンサC3は、バイパスコンデンサC14と比較して、低周波のノイズを防止するノイズ対策用の電気部品である。三端子コンデンサ85cの入力端子(IN)は、フィルタ回路131cの入力部となり、直流12Vの電源電圧VDD3が供給される。三端子コンデンサ85cの出力端子(OUT)は、フィルタ回路131cの出力部となり、電圧が安定化された直流12Vの電源電圧VDCを供給する。三端子コンデンサ85cの接地端子(GND)は、接地(グランドラインに接続)されている。三端子コンデンサ85cの出力端子と接地端子との間には、0.1μFのバイパスコンデンサC14、1000μFの電解コンデンサC3が、接続されている。

The

フィルタ回路131a〜131cは、各電源経路の電圧を安定化する安定化回路として機能する。例えばフィルタ回路131aは、電源ラインLDSにより供給される直流12Vの電源電圧VDSを安定化する。フィルタ回路131bは、電源ラインLCCにより供給される直流5Vの電源電圧VCCを安定化する。フィルタ回路131cは、電源ラインLDCにより供給される直流12Vの電源電圧を安定化する。演出制御基板12には、フィルタ回路131a〜131cの他にも、各種電源電圧におけるノイズの発生を防止するノイズ防止回路が設けられてもよい。

The

図15は、演出制御基板12に設けられるノイズ防止回路の構成例を示している。図15(A)は、電源電圧VDLというLED用DC12V(直流12V)に対応するノイズ防止回路135aの構成例を示している。図15(B)は、電源電圧VCLというLED/モータ用DC5V(直流5V)に対応するノイズ防止回路135bの構成例を示している。図15(C)は、電源電圧VCCというIC用DC5V(直流5V)や直流3.3Vの電源電圧というIC用DC3.3V(直流3.3V)に対応するノイズ防止回路135cの構成例を示している。

FIG. 15 shows a configuration example of a noise prevention circuit provided on the

図15(A)に示すノイズ防止回路135aは、直列接続されたコンデンサC20および抵抗R20と、直列接続されたコンデンサC21および抵抗R21と、直列接続されたコンデンサC22および抵抗R22とを用いて構成されていればよい。これらの構成は、いずれも電源電圧VDLを供給する電源ラインLDLと接地電圧を提供する接地端子(グランドライン)とに接続されていればよい。コンデンサC20、C21、C22は、いずれも0.1μFのバイパスコンデンサであればよい。抵抗R20、R21、R22は、いずれも22Ωの抵抗値を有するものであればよい。

A

図15(B)に示すノイズ防止回路135bは、直列接続されたコンデンサC23および抵抗R23と、直列接続されたコンデンサC24および抵抗R24とを用いて構成されていればよい。これらの構成は、いずれも電源電圧VCLを供給する電源ラインLCLと接地電圧を提供する接地端子(グランドライン)とに接続されていればよい。コンデンサC23、C24は、いずれも0.1μFのバイパスコンデンサであればよい。抵抗R23、R24は、いずれも22Ωの抵抗値を有するものであればよい。

The

図15(C)に示すノイズ防止回路135cは、コンデンサC25〜C28を用いて構成されていればよい。コンデンサC25は、電源電圧VCCを供給する電源ラインLCCと接地電圧を提供する接地端子(グランドライン)とに接続されていればよい。コンデンサC26、C27、C28は、いずれも直流3.3Vの電源電圧を供給する電源ラインL33と接地電圧を提供する接地端子(グランドライン)とに接続されていればよい。コンデンサC25〜C28は、いずれも0.1μFのバイパスコンデンサであればよい。

The

図15(A)に示すノイズ防止回路135aでは、コンデンサC20、C21、C22に加え、抵抗R20、R21、R22が用いられている。図15(B)に示すノイズ防止回路135bでは、コンデンサC23、C24に加え、抵抗R23、R24が用いられている。その一方で、図15(C)に示すノイズ防止回路135cでは、コンデンサC25〜C28が用いられ、抵抗は用いられていない。このように、ノイズ防止回路135a、135bでは、ノイズ防止回路135cとは異なる回路素子として、抵抗R20、R21、R22や、抵抗R23、R24が、用いられている。

In the

図15(A)に示すノイズ防止回路135aにより安定化される電源電圧VDLは、例えば演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するために用いられる。電源ラインLDLは、例えば演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するための電源電圧VDLを供給する。図15(B)に示すノイズ防止回路135bにより安定化される電源電圧VCLは、例えば演出用モータ60に含まれる特定のモータや演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するために用いられる。電源ラインLCLは、例えば演出用モータ60に含まれる特定のモータや演出用LED61に含まれる特定のLEDといった、特定の電気部品を駆動するための電源電圧VCLを供給する。図15(C)に示すノイズ防止回路135cにより安定化される電源電圧VCCと直流3.3Vの電源電圧は、例えば演出制御用CPU120やROM121あるいは表示制御部123に含まれる画像データメモリといった、特定の制御回路を含む電気回路を駆動するために用いられる。電源ラインLCCは、例えば演出制御用CPU120といった、特定の制御回路を含む電気回路を駆動するための電源電圧VCCを供給する。電源ラインL33は、例えばROM121あるいは表示制御部123の画像データメモリといった、特定の制御回路を含む電気回路を駆動するための直流3.3Vの電源電圧を供給する。このように、モータやLEDなど特定の電気部品を駆動するための電源電圧に対応するノイズ防止回路135a、135bでは、CPUやROMなど特定の電気回路を駆動するための電源電圧に対応するノイズ防止回路135cとは異なる回路素子として、抵抗R20、R21、R22や、抵抗R23、R24が、用いられている。

The power supply voltage VDL stabilized by the

演出用モータ60に含まれる特定のモータや演出用LED61に含まれる特定のLEDのような電流駆動型の回路素子を用いた負荷回路では、負荷回路の過渡現象により過大な突入電流が発生して、電気部品が破損してしまうおそれがある。そこで、ノイズ防止回路135aでは、コンデンサC20に抵抗R20を直列接続し、コンデンサC21に抵抗R21を直列接続し、コンデンサC22に抵抗R22を直列接続する。また、ノイズ防止回路135bでは、コンデンサC23に抵抗R23を直列接続し、コンデンサC24に抵抗R24を直列接続する。なお、電源電圧VDLが安定しているときには、コンデンサC20、C21、C22が充電状態となり、抵抗R20、R21、R22は非導通状態となるので、電力損失の発生を防止できる。電源電圧VCLが安定しているときには、コンデンサC23、C24が充電状態となり、抵抗R23、R24は非導通状態となるので、電力損失の発生を防止できる。その一方で、演出制御用CPU120やROM121あるいは表示制御部123の画像データメモリなどの半導体集積回路では、例えばCMOS回路といった、電圧駆動型の回路素子が用いられ、入力インピーダンスが比較的に大きくなる。そのため、回路の過渡現象による突入電流は発生しにくい。そのため、ノイズ防止回路135cでは、コンデンサC25〜C28を用いる一方で、抵抗を用いる必要はない。こうして、電源電圧を供給する対象となる回路や電気部品の特性に応じて異なる回路素子を用いたノイズ防止回路を構成することにより、基板容積の増大や製造コストの増加を防止しつつ、ノイズの発生を防止する適切な基板構成が可能になる。

In a load circuit using a current-driven circuit element such as a specific motor included in the

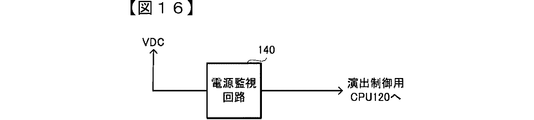

図16は、電源電圧VDCを用いる電源監視回路140を示している。演出制御基板12では、電源電圧VDCが電源断の発生を監視するために用いられる。電源監視回路140は、例えば停電監視リセットモジュールICを用いて構成され、電源断信号を出力可能な電源監視手段を実現する回路である。例えば電源監視回路140は、電源電圧VDCが所定値(例えば10V)を超えると、オフ状態(ハイレベル)の電源断信号を出力する。その一方で、電源電圧VDCが所定値以下になった期間が、予め定められた待機時間以上継続したときに、オン状態(ローレベル)の電源断信号を出力する。電源監視回路140から出力された電源断信号は、演出制御用CPU120へと伝送される。

FIG. 16 shows a power

電源断信号を出力するための監視対象となる電源電圧VDCは、直流1.05Vの電源電圧や直流3.3Vの電源電圧、直流1.5Vの電源電圧を生成するために用いられる。直流1.05Vの電源電圧は、例えば表示制御部123に含まれるグラフィックスプロセッサといった、所定の電気回路を駆動するために用いられる。直流3.3Vの電源電圧は、例えばROM121や表示制御部123に含まれる画像データメモリといった、所定の電気回路を駆動するために用いられる。直流1.5Vの電源電圧は、例えばRAM122といった、所定の電気回路を駆動するために用いられる。こうした電気回路に供給される電源電圧の生成に用いられる電源電圧VDCを監視対象とすることにより、電気回路の動作状態が不安定となる以前に、電源断信号を出力する(オン状態にする)ことができるので、各種電気回路における誤動作を防止できる。

The power supply voltage VDC to be monitored for outputting the power-off signal is used to generate a power supply voltage of DC 1.05V, a power supply voltage of DC 3.3V, and a power supply voltage of DC 1.5V. The power supply voltage of DC 1.05V is used for driving a predetermined electric circuit such as a graphics processor included in the

演出制御基板12では、レセプタクルKRE2の端子TA27、TA28にて供給された電源電圧VDD3を、フィルタ回路131cにより安定化した後に、降圧コンバータ回路132に入力する。降圧コンバータ回路132は、入力電圧を用いて、直流1.05Vの電源電圧と、直流1.05Vよりも高い直流3.3Vの電源電圧とを生成する。直流3.3Vの電源電圧は、レギュレータ回路133に入力される。レギュレータ回路133は、入力電圧を用いて、直流1.5Vの電源電圧を生成する。直流1.5Vの電源電圧は、直流1.05Vよりも高いが直流3.3Vよりも低い電源電圧となる。このように、降圧コンバータ回路132およびレギュレータ回路133を用いて、直流1.05Vの電源電圧と、直流1.05Vよりも高い直流1.5Vの電源電圧と、直流1.5Vよりも高い直流3.3Vの電源電圧とを生成することができ、降圧コンバータ回路132は、直流1.05Vの電源電圧と、直流3.3Vの電源電圧とを出力する一方で、レギュレータ回路133は、直流1.5Vの電源電圧を出力する。

In the

電源電圧VDD3を、フィルタ回路131cにより安定化した後に、分岐させた直流12Vの電源電圧VDCは、電源断の発生を監視する電源監視回路140に供給される。したがって、降圧コンバータ回路132の入力電圧は、直流12Vの電源電圧VDCと共通であり、降圧コンバータ回路132の入力電圧が電源監視回路140の監視対象になる。なお、電源電圧VDCを分岐させた後において、降圧コンバータ回路132の入力側に、所定容量(例えば47μF)のバイパスコンデンサが接続されてもよい。

After the power supply voltage VDD3 is stabilized by the

降圧コンバータ回路132およびレギュレータ回路133を用いて生成される電源電圧のうち、電圧値が最も小さい低電圧となる直流1.05Vの電源電圧は、例えば表示制御部123のグラフィックスプロセッサといった、特定のマイクロプロセッサに供給される。なお、直流1.05Vの電源電圧は、表示制御部123のグラフィックスプロセッサに供給されるものに限定されず、例えば演出制御用CPU120その他に任意のマイクロプロセッサに供給されてもよい。

Among the power supply voltages generated by using the step-down

降圧コンバータ回路132およびレギュレータ回路133を用いて生成される電源電圧のうち、電圧値が最も大きく高電圧となる直流3.3Vの電源電圧は、例えばROM121や表示制御部123の画像データメモリなどに供給される。ROM121は、直流1.5Vの電源電圧により駆動する電気部品よりも先に起動可能であればよい。

Of the power supply voltages generated by using the step-down

降圧コンバータ回路132およびレギュレータ回路133を用いて生成される電源電圧のうち、直流1.05Vよりも高く直流3.3Vよりは低い直流1.5Vの電源電圧は、例えばRAM122に供給される。RAM122は、例えばDDR(Double Data Rate)方式で記憶や読出が可能な一時記憶メモリであり、SIMM(Single In-line Memory Module)やDIMM(Dual In-line Memory Module)といった、メモリモジュールとして機能する基板を構成する。このようなRAM122を構成する基板は、演出制御基板12に着脱自在に接続可能な別基板として構成されてもよい。この場合、直流1.5Vの電源電圧は、演出制御基板12とは異なる基板に供給されることになる。

Of the power supply voltages generated using the step-down

降圧コンバータ回路132およびレギュレータ回路133に代えて、1入力3出力の降圧コンバータ回路を用いた場合には、特別な専用回路が必要になり、製造コストが増加するおそれがある。また、単一の回路における発熱量が増大して、電気回路が破損してしまうおそれがある。そこで、降圧コンバータ回路132では、フィルタ回路131cにより安定化した電源電圧VDD3(電源電圧VDCでも同様)が入力されて、直流1.05Vの電源電圧と、直流3.3Vの電源電圧とを出力する。レギュレータ回路133では、直流3.3Vの電源電圧が入力されて、直流1.5Vの電源電圧を出力する。これにより、製造コストの増加を防止するとともに、電気回路での発熱を分散する適切な基板構成が可能になる。

When a step-down converter circuit having one input and three outputs is used in place of the step-down

降圧コンバータ回路132に供給される電圧と同一または略同一の電源電圧VDCは、電源監視回路140に供給され、電源断の発生が監視される。こうして、降圧コンバータ回路132およびレギュレータ回路133による各種電源電圧の生成に用いられる電源電圧VDCを、電源監視回路140の監視対象とするので、例えば表示制御部123のグラフィックスプロセッサといった、パチンコ遊技機1における演出を実行するために重要な電気回路の動作状態が不安定となる以前に、電源断の発生を検出する適切な基板構成が可能になる。

The power supply voltage VDC that is the same or substantially the same as the voltage supplied to the step-down

降圧コンバータ回路132から出力された直流1.05Vの電源電圧は、例えば表示制御部123のグラフィックスプロセッサといった、特定のマイクロプロセッサに供給される。降圧コンバータ回路132から直流1.05Vの電源電圧を出力させることで、電源断が発生した場合に、レギュレータ回路133から出力させた構成よりも長時間が経過するまで直流1.05Vの電源電圧を維持することができる。これにより、電源断が発生した場合に、例えば表示制御部123のグラフィックスプロセッサといった、パチンコ遊技機1における演出を実行するために重要な電気回路の動作を可能な限り継続させる適切な基板構成が可能になる。

The power supply voltage of 1.05 V DC output from the step-down

降圧コンバータ回路132から出力された直流3.3Vの電源電圧は、例えばROM121に供給され、レギュレータ回路133から出力される直流1.5Vの電源電圧により駆動するRAM122などの電気部品よりも先に起動可能となる。これにより、電源投入された場合に、例えば演出制御用CPU120によりROM121の記憶データを即座に読出できる適切な基板構成が可能になる。

The DC 3.3V power supply voltage output from the step-down

レギュレータ回路133から出力された直流1.5Vの電源電圧は、例えばRAM122といった、演出制御基板12とは異なる基板として構成されたものに供給されてもよい。このように、演出制御基板12とは異なる基板に供給される直流1.5Vの電源電圧を、降圧コンバータ回路132とは異なるレギュレータ回路133から出力させることで、製造コストの増加を防止するとともに、電気回路での発熱を分散する適切な基板構成が可能になる。

The power supply voltage of 1.5 V DC output from the

(特徴部30AKに関する説明)

図17は、本実施形態の特徴部30AKに関し、主基板11における一方の基板面(表面)にて、CPU103とRAM102とを接続する配線のパターンが形成された部分の構成例を示している。主基板11では、例えばRAM102とCPU103といった、複数の電気部品を複数の信号配線により接続するために、複数の信号配線を構成する配線のパターンが形成されている。CPU103は、パチンコ遊技機1における遊技の制御に関して、所定の処理を実行可能に構成された電気部品であり、RAM102はCPU103による処理の実行に関する情報を記憶可能に構成された電気部品である。

(Explanation regarding the feature 30AK)

FIG. 17 shows a configuration example of a portion in which a wiring pattern for connecting the

複数の信号配線を構成する配線のパターンに対し、それらの周囲あるいは信号配線間における領域にて、1または複数のグランド導体が配置されている。グランド導体は、基準グランドや特性インピーダンス調整用グランドとして機能し、グランド電圧に維持される。図17に示す構成例では、複数のグランド導体として、複数の信号配線の周囲における領域にグランド導体30AK10Gおよびグランド導体30AK11Gが配置され、複数の信号配線間における領域にグランド導体30AK20Gが配置されている。このように、複数の信号配線を構成する配線のパターンが設けられていない空白領域となる空域部分には、1または複数のグランド導体が設けられていてもよい。これにより、複数の信号配線から放射される電磁波ノイズや信号配線間での電磁波ノイズによる電磁妨害を、防止あるいは抑制できる。 One or a plurality of ground conductors are arranged in the area around or between the signal wirings with respect to the wiring patterns constituting the plurality of signal wirings. The ground conductor functions as a reference ground or a characteristic impedance adjustment ground, and is maintained at the ground voltage. In the configuration example shown in FIG. 17, as a plurality of ground conductors, a ground conductor 30AK10G and a ground conductor 30AK11G are arranged in a region around a plurality of signal wires, and a ground conductor 30AK20G is arranged in a region between the plurality of signal wires. . As described above, one or a plurality of ground conductors may be provided in an airspace portion which is a blank area where a wiring pattern constituting a plurality of signal wirings is not provided. Thereby, the electromagnetic interference by the electromagnetic wave noise radiated | emitted from several signal wiring and the electromagnetic wave noise between signal wiring can be prevented or suppressed.

なお、複数の信号配線の周囲および信号配線間における双方の領域に複数のグランド導体が配置されるものに限定されず、複数の信号配線の周囲または信号配線間における一方の領域にのみグランド導体が配置されるものであってもよい。あるいは、このようなグランド導体が配置されないものであってもよい。 It should be noted that the ground conductor is not limited to one in which a plurality of ground conductors are arranged in both regions around the signal wires and between the signal wires. It may be arranged. Alternatively, such a ground conductor may not be disposed.

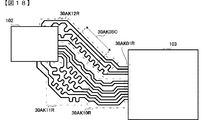

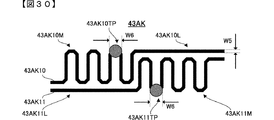

図18は、図17に示した複数の信号配線を構成する配線のパターンについて、より詳細に説明するための領域や区間を示している。図18に示す領域30AK01Rは、複数の信号配線がCPU103に接続される側の端部における領域である。図18に示す領域30AK10Rは、複数の信号配線がいずれも直線形状または略直線形状で互いに平行または略平行な第1形状となる領域であり、図18に示す領域30AK11Rと領域30AK12Rは、少なくとも一部の信号配線が直線形状および略直線形状とは異なる形状で他の信号配線と平行および略平行ではない第2形状となる領域である。図18に示す区間30AK0SCでは、複数の信号配線のうち一部の信号配線が最短または略最短の距離で接続する短距離パターンと短距離パターンに含まれない信号配線が短距離パターンよりも長い距離で接続する長距離パターンとが配置されている。

FIG. 18 shows areas and sections for explaining in more detail the wiring patterns constituting the plurality of signal wirings shown in FIG. A region 30AK01R illustrated in FIG. 18 is a region at an end portion on the side where a plurality of signal wirings are connected to the

図19は、図18に示された領域30AK01Rの拡大図である。図19に示す領域30AK01Rにおいて、複数の信号配線を構成する配線のパターンは、パターン30AK10D〜30AK13Dと、パターン30AK10CKと、パターン30AK10CSと、パターン30AK10RSと、パターン30AK10A〜30AK14Aとを含んでいる。 FIG. 19 is an enlarged view of the region 30AK01R shown in FIG. In the region 30AK01R shown in FIG. 19, the patterns of the wirings constituting the plurality of signal wirings include patterns 30AK10D to 30AK13D, pattern 30AK10CK, pattern 30AK10CS, pattern 30AK10RS, and patterns 30AK10A to 30AK14A.

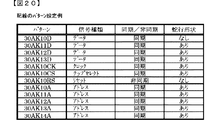

図20は、図19に示された配線のパターンに対応して、信号種類、信号同期の有無、蛇行形状の有無についての設定例を示している。図20に示す信号種類は、各配線のパターンが構成する信号配線で伝送される電気信号の内容(用途)を示している。図20に示す信号同期は、他の信号配線で伝送される電気信号に対する同期の有無を示している。図20に示す蛇行形状は、RAM102とCPU103との間を接続する各配線のパターンについて、直線形状および略直線形状とは異なる蛇行形状となる部分が設けられているか否かを示している。蛇行形状は、ミアンダ形状やジグザグ形状、あるいは折返し形状とも称され、所定区間における信号配線の延設方向に対し、信号配線が繰り返し折り曲げられることにより、例えば延設方向に直交あるいは略直交する方向に折返し往復する形状であればよい。

FIG. 20 shows an example of setting the signal type, the presence / absence of signal synchronization, and the presence / absence of a meandering shape corresponding to the wiring pattern shown in FIG. The signal types shown in FIG. 20 indicate the contents (uses) of electric signals transmitted through the signal wirings formed by the wiring patterns. The signal synchronization shown in FIG. 20 indicates the presence or absence of synchronization with an electric signal transmitted through another signal wiring. The meandering shape shown in FIG. 20 indicates whether or not each wiring pattern connecting the

図20に示す設定例において、配線のパターン30AK10D〜30AK13Dは、いずれもデータ信号を伝送するための信号配線を構成する。各信号配線で伝送されるデータ信号は、例えばクロック信号および他の信号配線で伝送されるデータ信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10CKは、クロック信号を伝送するための信号配線を構成する。クロック信号は、例えばデータ信号やアドレス信号、チップセレクト信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10CSは、チップセレクト信号を伝送するための信号配線を構成する。チップセレクト信号は、例えばクロック信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10RSは、リセット信号を伝送するための信号配線を構成する。リセット信号は、他の信号配線で伝送される信号とは同期しない非同期で伝送される。配線のパターン30AK10A〜30AK14Aは、いずれもアドレス信号を伝送するための信号配線を構成する。各信号配線で伝送されるアドレス信号は、例えばクロック信号および他の信号配線で伝送されるアドレス信号といった、他の信号配線で伝送される信号と同期して伝送される。 In the setting example shown in FIG. 20, all of the wiring patterns 30AK10D to 30AK13D constitute a signal wiring for transmitting a data signal. A data signal transmitted through each signal wiring is transmitted in synchronization with a signal transmitted through another signal wiring, such as a clock signal and a data signal transmitted through another signal wiring. The wiring pattern 30AK10CK constitutes a signal wiring for transmitting a clock signal. The clock signal is transmitted in synchronization with a signal transmitted through another signal wiring such as a data signal, an address signal, and a chip select signal. The wiring pattern 30AK10CS constitutes a signal wiring for transmitting a chip select signal. The chip select signal is transmitted in synchronization with a signal transmitted through another signal wiring, such as a clock signal. The wiring pattern 30AK10RS constitutes a signal wiring for transmitting a reset signal. The reset signal is transmitted asynchronously without being synchronized with a signal transmitted through another signal wiring. Each of the wiring patterns 30AK10A to 30AK14A constitutes a signal wiring for transmitting an address signal. An address signal transmitted through each signal wiring is transmitted in synchronization with a signal transmitted through another signal wiring, such as a clock signal and an address signal transmitted through another signal wiring.

他の信号配線で伝送される信号と同期して伝送されるデータ信号、クロック信号、チップセレクト信号、アドレス信号のうちデータ信号を伝送するための信号配線を構成する配線のパターン30AK10D〜30AK13Dには、蛇行形状がない配線のパターン30AK10Dが含まれている。配線のパターン30AK10Dが構成する信号配線で伝送されるデータ信号とは異なるデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線を構成する配線のパターンは、少なくとも一部分が直線形状および略直線形状とは異なる形状としての蛇行形状となっている。 The wiring patterns 30AK10D to 30AK13D constituting the signal wiring for transmitting the data signal among the data signal, the clock signal, the chip select signal, and the address signal transmitted in synchronization with the signal transmitted through the other signal wiring include A wiring pattern 30AK10D having no meandering shape is included. At least part of the wiring pattern constituting the signal wiring for transmitting the data signal, clock signal, chip select signal, and address signal different from the data signal transmitted by the signal wiring formed by the wiring pattern 30AK10D is linear. Further, the meandering shape is different from the substantially linear shape.

配線のパターン30AK10Dが構成するデータ信号を伝送するための信号配線は、他のデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線に比べて、RAM102とCPU103における接続端子間の距離が長くなっている。そこで、配線のパターン30AK10Dが構成する信号配線で伝送されるデータ信号とは異なるデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線を構成する配線のパターンは、少なくとも一部分が蛇行形状となることにより、各信号配線の配線長が同一または略同一となる。その一方で、配線のパターン30AK10Dには蛇行形状を設ける必要がない。

The signal wiring for transmitting the data signal formed by the wiring pattern 30AK10D is more connected between the connection terminals of the

このように、同期信号を伝送するための信号配線のうち複数の電気部品における接続端子間の距離が他の接続端子間の距離と比べて長くなる信号配線は、例えば蛇行形状となる配線部分といった、直線形状および略直線形状とは異なる形状となる配線部分を含まないように、配線のパターンが形成されていればよい。逆にいうと、直線形状または略直線形状などの形状となる一方で蛇行形状のような直線形状および略直線形状とは異なる形状を含まない配線のパターンが構成する信号配線は、蛇行形状のような直線形状および略直線形状とは異なる形状を含む配線のパターンが構成する信号配線と比較して、複数の電気部品における接続端子間の距離が長い。あるいは、同期信号を伝送するための信号配線のうち複数の電気部品における接続端子間の距離が他の接続端子間の距離と比べて長くなる信号配線は、例えば蛇行形状となる配線部分といった、他の信号配線と平行および略平行な形状とは異なる形状となる配線部分を含まないように、配線のパターンが形成されていればよい。逆にいうと、他の信号配線と平行または略平行な形状となる一方で蛇行形状のような平行および略平行な形状とは異なる形状を含まない配線のパターンが構成する信号配線は、蛇行形状のような他の信号配線と平行および略平行な形状とは異なる形状を含む配線のパターンが構成する信号配線と比較して、複数の電気部品における接続端子間の距離が長い。これにより、各信号配線の配線長を同一または略同一とし、複数の信号配線で伝送される信号の遅延時間差(スキュー)が発生することを、防止あるいは抑制できる。複数の信号配線で伝送される信号の遅延時間差を減少させることにより、複数の信号配線で伝送される信号の信頼性を向上させることができる。 Thus, the signal wiring in which the distance between the connection terminals in the plurality of electrical components among the signal wirings for transmitting the synchronization signal is longer than the distance between the other connection terminals is, for example, a wiring portion having a meandering shape. The wiring pattern may be formed so as not to include a wiring portion having a shape different from the linear shape and the substantially linear shape. In other words, the signal wiring formed by the wiring pattern which does not include a linear shape such as a meandering shape or a shape different from the substantially linear shape while having a linear shape or a substantially linear shape is like a meandering shape. The distance between the connection terminals in the plurality of electrical components is longer than the signal wiring formed by the wiring pattern including a shape different from the straight line shape and the substantially straight line shape. Alternatively, among the signal wirings for transmitting the synchronization signal, the signal wiring in which the distance between the connection terminals in the plurality of electrical components is longer than the distance between the other connection terminals is, for example, a wiring portion having a meandering shape. The wiring pattern may be formed so as not to include a wiring portion having a shape different from the shape parallel to and substantially parallel to the signal wiring. In other words, the signal wiring formed by a wiring pattern that is parallel or substantially parallel to other signal wirings but does not include a parallel or substantially parallel shape such as a meandering shape is a meandering shape. The distance between the connection terminals in the plurality of electrical components is longer than the signal wiring formed by the wiring pattern including a shape different from the parallel and substantially parallel shape to the other signal wiring. As a result, it is possible to prevent or suppress the occurrence of a delay time difference (skew) between signals transmitted through a plurality of signal wirings by making the wiring lengths of the respective signal wirings the same or substantially the same. By reducing the delay time difference between signals transmitted through a plurality of signal lines, the reliability of signals transmitted through the plurality of signal lines can be improved.

配線のパターン30AK10RSには、蛇行形状が設けられていない。配線のパターン30AK10RSは、非同期信号であるリセット信号を伝送するための信号配線を構成する。リセット信号などの非同期信号を伝送する場合には、他の信号配線で伝送される信号との遅延時間差を考慮する必要がない。そこで、リセット信号を伝送するための信号配線を構成する配線のパターン30AK10RSのように、非同期信号が伝送される信号配線を構成する配線のパターンには蛇行形状を設けない。配線のパターンに蛇行形状を設けないようにすれば、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。 The wiring pattern 30AK10RS is not provided with a meandering shape. The wiring pattern 30AK10RS constitutes a signal wiring for transmitting a reset signal that is an asynchronous signal. When an asynchronous signal such as a reset signal is transmitted, there is no need to consider a delay time difference from a signal transmitted through another signal wiring. Therefore, like the wiring pattern 30AK10RS constituting the signal wiring for transmitting the reset signal, the meandering shape is not provided in the wiring pattern constituting the signal wiring for transmitting the asynchronous signal. If the meandering shape is not provided in the wiring pattern, an increase in the area of the substrate on which the wiring pattern is arranged can be suppressed, and the size of the substrate can be reduced.