JP2017511971A - 封止層を横切るサイドバリア層を有するビアを備える集積デバイス - Google Patents

封止層を横切るサイドバリア層を有するビアを備える集積デバイス Download PDFInfo

- Publication number

- JP2017511971A JP2017511971A JP2016550191A JP2016550191A JP2017511971A JP 2017511971 A JP2017511971 A JP 2017511971A JP 2016550191 A JP2016550191 A JP 2016550191A JP 2016550191 A JP2016550191 A JP 2016550191A JP 2017511971 A JP2017511971 A JP 2017511971A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- implementations

- substrate

- integrated device

- coupled

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

- 230000004888 barrier function Effects 0.000 title claims abstract description 194

- 238000007789 sealing Methods 0.000 title claims abstract description 177

- 239000000758 substrate Substances 0.000 claims abstract description 172

- 238000005538 encapsulation Methods 0.000 claims abstract description 36

- 238000000034 method Methods 0.000 claims description 90

- 239000000945 filler Substances 0.000 claims description 58

- 238000004891 communication Methods 0.000 claims description 8

- 239000000463 material Substances 0.000 description 67

- 229910052751 metal Inorganic materials 0.000 description 58

- 239000002184 metal Substances 0.000 description 58

- 230000008569 process Effects 0.000 description 56

- 229920002120 photoresistant polymer Polymers 0.000 description 48

- 229910000679 solder Inorganic materials 0.000 description 37

- 238000004519 manufacturing process Methods 0.000 description 25

- 239000010936 titanium Substances 0.000 description 16

- 238000007747 plating Methods 0.000 description 15

- 238000001259 photo etching Methods 0.000 description 13

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 12

- 229910052802 copper Inorganic materials 0.000 description 12

- 239000010949 copper Substances 0.000 description 12

- 229910000881 Cu alloy Inorganic materials 0.000 description 10

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 239000000919 ceramic Substances 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 229920000642 polymer Polymers 0.000 description 6

- 229910016570 AlCu Inorganic materials 0.000 description 5

- 229910010165 TiCu Inorganic materials 0.000 description 5

- CPFNXHQBAHTVKB-UHFFFAOYSA-N [Ti].[Cu].[W] Chemical compound [Ti].[Cu].[W] CPFNXHQBAHTVKB-UHFFFAOYSA-N 0.000 description 5

- WPPDFTBPZNZZRP-UHFFFAOYSA-N aluminum copper Chemical compound [Al].[Cu] WPPDFTBPZNZZRP-UHFFFAOYSA-N 0.000 description 5

- IUYOGGFTLHZHEG-UHFFFAOYSA-N copper titanium Chemical compound [Ti].[Cu] IUYOGGFTLHZHEG-UHFFFAOYSA-N 0.000 description 5

- 238000001459 lithography Methods 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 230000008878 coupling Effects 0.000 description 4

- 238000010168 coupling process Methods 0.000 description 4

- 238000005859 coupling reaction Methods 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 150000003071 polychlorinated biphenyls Chemical class 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1017—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support

- H01L2225/1023—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support the support being an insulating substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1058—Bump or bump-like electrical connections, e.g. balls, pillars, posts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0655—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1532—Connection portion the connection portion being formed on the die mounting surface of the substrate

- H01L2924/1533—Connection portion the connection portion being formed on the die mounting surface of the substrate the connection portion being formed both on the die mounting surface of the substrate and outside the die mounting surface of the substrate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Micromachines (AREA)

Abstract

Description

本願は、2014年2月13日に出願された「Integrated Device Comprising Via With Side Barrier Layer Traversing Encapsulation Layer」という名称の米国仮出願第61/939523号の優先権を主張する、2014年5月9日に出願された「Integrated Device Comprising Via With Side Barrier Layer Traversing Encapsulation Layer」という名称の米国特許出願第14/274517号の優先権を主張する。これらの出願は、参照により本明細書に明確に組み込まれる。

いくつかの新規の特徴は、封止層と、封止層を横切るビア構造と、パッドとを含む集積デバイスに関する。ビア構造は、第1の側面と、第2の側面と、第3の側面とを含むビアを含む。ビア構造は、ビアの少なくとも第1の側面と第3の側面を囲むバリア層も含む。パッドは、ビア構造のバリア層に直接結合される。いくつかの実装形態では、ビア構造は充填材(たとえば、ポリマー充填材)も含む。いくつかの実装形態では、集積デバイスは、封止層の第1の表面に結合された第1の誘電体層を含む。いくつかの実装形態では、集積デバイスは、封止層の第2の表面に結合された第2の誘電体層を含む。いくつかの実装形態では、集積デバイスは、封止層の第1の表面に結合された基板を含む。いくつかの実装形態では、集積デバイスは、基板に結合された第1のダイを含み、封止層は、第1のダイを封止する。いくつかの実装形態では、基板は基板貫通ビア(TSV,through substrate via)のセットを含む。いくつかの実装形態では、ビアはシード層を含む。いくつかの実装形態では、ビアは、パッドとして動作するように構成された部分を含む。

図3は、集積デバイス(たとえば、パッケージデバイス、パッケージオンパッケージ(PoP)デバイス、インターポーザ)に実装されてもよい封止貫通ビア(TEV)のセットの一例を示す。

いくつかの実装形態では、ビア構造を含む集積デバイス(たとえば、集積パッケージ)を提供することは、いくつかのプロセスを含む。図5(図5A〜図5Cを含む)は、集積デバイスを提供するための例示的なシーケンスを示す。いくつかの実装形態では、図5A〜図5Cのシーケンスは、図3および/または図4の集積デバイス、ならびに/あるいは本開示で説明する他の集積デバイスを提供する/製造するために使用され得る。

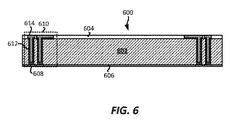

図6は、ビア構造のセット610を含む集積パッケージデバイスを示す。詳細には、図6は、ビア構造のセット610を含むインターポーザ600の一例を示す。いくつかの実装形態では、ビア構造610は、図3に示すビア構造および/または本開示において説明し図示する任意の新規のビア構造であってもよい。

いくつかの実装形態では、集積デバイスはインターポーザを含んでもよい。いくつかの実装形態では、ビア構造を含む集積デバイス(たとえば、集積パッケージ)を提供することは、いくつかのプロセスを含む。図7(図7A〜図7Cを含む)は、集積デバイスを提供するための例示的なシーケンスを示す。いくつかの実装形態では、図7A〜図7Cのシーケンスは、図3、図4、および/または図6の集積デバイス、ならびに/あるいは本開示において説明する他の集積デバイスを提供する/製造するために使用されてもよい。

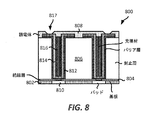

図8は、集積デバイス(たとえば、集積パッケージデバイス、パッケージオンパッケージ(PoP)デバイス、インターポーザ)に実装されてもよい封止貫通ビア(TEV)のセットの一例を示す。

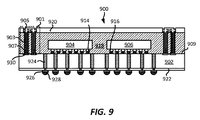

いくつかの実装形態では、ビア構造を含む集積デバイス(たとえば、集積パッケージ)を提供することは、いくつかのプロセスを含む。図10(図10A〜図10Cを含む)は、集積デバイスを提供するための例示的なシーケンスを示す。いくつかの実装形態では、図10A〜図10Cのシーケンスは、図8および/または図9の集積デバイス、ならびに/あるいは本開示で説明する他の集積デバイスを提供する/製造するために使用され得る。

図11は、ビア構造のセット1110を含む集積パッケージデバイスを示す。詳細には、図11は、ビア構造のセット1110を含むインターポーザ1100の一例を示す。いくつかの実装形態では、ビア構造1110は、図8に示すビア構造および/または本開示において説明し図示する任意の新規のビア構造であってもよい。

いくつかの実装形態では、集積デバイスはインターポーザを含んでもよい。いくつかの実装形態では、ビア構造を含む集積デバイス(たとえば、集積パッケージ)を提供することは、いくつかのプロセスを含む。図12(図12A〜図12Cを含む)は、集積デバイスを提供するための例示的なシーケンスを示す。いくつかの実装形態では、図12A〜図12Cのシーケンスは、図8、図9、および/または図11の集積デバイス、ならびに/あるいは本開示において説明する他の集積デバイスを提供する/製造するために使用されてもよい。

いくつかの実装形態では、ビア構造を含む集積デバイス(たとえば、集積パッケージ)を提供することは、いくつかのプロセスを含む。図13は、集積デバイスを提供する方法を示す。いくつかの実装形態では、図13の方法は、図3、図4、図8、および/または図9の集積デバイス、ならびに/あるいは本開示において説明する他の集積デバイスを提供する/製造するために使用されてもよい。

図14は、上述の集積デバイス、半導体デバイス、集積回路、ダイ、インターポーザ、またはパッケージのうちのいずれかと一体化される場合がある様々な電子デバイスを示す。たとえば、モバイル電話1402、ラップトップコンピュータ1404、および固定位置端末1406が、本明細書で説明する集積デバイス1400を含んでもよい。集積デバイス1400は、たとえば、本明細書で説明する集積回路、ダイ、インターポーザ、またはパッケージのうちのいずれかであってもよい。図14に示すデバイス1402、1404、1406は例にすぎない。他の電子デバイスは、限定はされないが、モバイルデバイス、ハンドヘルドパーソナル通信システム(PCS,personal communication system)ユニット、携帯情報端末などのポータブルデータユニット、GPS対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、メータ読取り機器などの固定位置データユニット、通信デバイス、スマートフォン、タブレットコンピュータ、またはデータもしくはコンピュータ命令を記憶し、もしくは取り出す任意の他のデバイス、またはそれらの任意の組合せを含む、集積デバイス1400を特徴としてもよい。

104 第2のパッケージ

105 第2の基板

106 第1の基板

107 第2のダイ

108 第1のダイ

109 第3のダイ

110 モールド

115 はんだボールの第2のセット

116 はんだボールの第1のセット

117 ワイヤボンディングの第1のセット

118 配線の第1のセット

119 ワイヤボンディングの第2のセット

126 はんだボールの第3のセット

200 集積デバイス

302 基板

304 絶縁層

306 封止層

308 誘電体層

310 第1のパッド

312 第1のバリア層

314 封止貫通ビア(TEV)

315 キャビティ

400 集積パッケージデバイス

401 ビア構造

402 基板

403 第1のバリア層

404 第1のダイ

405 封止貫通ビア(TEV)

406 第2のダイ

409 誘電体層

414 配線の第1のセット

416 配線の第2のセット

418 封止層

420 第1の誘電体層

422 第2の誘電体層

426 配線の第3のセット

428 はんだボールのセット

430 第1のパッド

502 基板

503 誘電体層

504 基板貫通ビア(TSV)のセット

505 パッドのセット

506 第1のダイ

508 第2のダイ

516 配線の第1のセット

518 配線の第2のセット

520 封止層

525 キャビティ

530 バリア層

532 シード層

534 フォトレジスト層

536 金属層

538 ビア構造

540 誘電体層

550 誘電体層

552 配線のセット

554 はんだボールのセット

560 集積デバイス

600 インターポーザ

602 封止層

604 第1の誘電体層

606 基板

608 第1のパッド

610 ビア構造のセット

612 バリア層

614 封止貫通ビア(TEV)

702 キャリア

703 誘電体層

704 基板

705 パッドのセット

720 封止層

725 キャビティ

730 バリア層

732 シード層

734 フォトレジスト層

736 金属層

738 ビア構造

740 誘電体層

760 集積デバイス

802 基板

804 絶縁層

806 封止層

808 誘電体層

810 第1のパッド

812 第1のバリア層

814 封止貫通ビア(TEV)

816 充填材

817 キャビティ

900 集積パッケージデバイス

901 ビア構造のセット

902 基板

903 第1のバリア層

904 第1のダイ

905 封止貫通ビア(TEV)

906 第2のダイ

907 充填材

909 誘電体層

914 配線の第1のセット

916 配線の第2のセット

918 封止層

920 第1の誘電体層

922 第2の誘電体層

924 基板貫通ビア(TSV)のセット

926 配線の第3のセット

928 はんだボールのセット

930 第1のパッド

1002 基板

1003 誘電体層

1004 基板貫通ビア(TSV)のセット

1005 パッドのセット

1006 第1のダイ

1008 第2のダイ

1016 配線の第1のセット

1018 配線の第2のセット

1020 封止層

1025 キャビティ

1030 バリア層

1032 シード層

1034 フォトレジスト層

1036 金属層

1037 キャビティ

1038 ビア構造

1039 充填材

1040 誘電体層

1050 誘電体層

1052 配線のセット

1054 はんだボールのセット

1060 集積デバイス

1100 インターポーザ

1102 封止層

1104 第1の誘電体層

1106 基板

1108 第1のパッド

1110 ビア構造のセット

1112 第1のバリア層

1114 封止貫通ビア(TEV)

1116 充填材

1202 キャリア

1203 誘電体層

1204 基板

1205 パッドのセット

1220 封止層

1225 キャビティ

1230 バリア層

1232 シード層

1234 フォトレジスト層

1236 金属層

1237 キャビティ

1238 ビア構造

1239 充填材

1240 誘電体層

1260 集積デバイス

1400 集積デバイス

1402 モバイル電話

1404 ラップトップコンピュータ

1406 固定位置端末

Claims (30)

- 封止層と、

前記封止層を横切るビア構造であって、

第1の側面と、第2の側面と、第3の側面とを備えるビアと、

前記ビアの少なくとも前記第1の側面と前記第3の側面を囲むバリア層とを備えるビア構造と、

前記ビア構造の前記バリア層に直接結合されたパッドとを備える集積デバイス。 - 前記封止層の第1の表面に結合された第1の誘電体層をさらに備える、請求項1に記載の集積デバイス。

- 前記封止層の第2の表面に結合された第2の誘電体層をさらに備える、請求項2に記載の集積デバイス。

- 前記封止層の第1の表面に結合された基板をさらに備える、請求項1に記載の集積デバイス。

- 前記基板に結合された第1のダイをさらに備え、前記封止層は、前記第1のダイを封止する、請求項4に記載の集積デバイス。

- 前記ビア構造は充填材をさらに備える、請求項4に記載の集積デバイス。

- 前記ビアはシード層を備える、請求項1に記載の集積デバイス。

- 前記ビアは、パッドとして動作するように構成された部分を備える、請求項1に記載の集積デバイス。

- 少なくともインターポーザ、パッケージデバイス、および/またはパッケージオンパッケージデバイスのうちの1つを備える、請求項1に記載の集積デバイス。

- 音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および/またはラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項1に記載の集積デバイス。

- 封止層と、

前記封止層を横切るビア構造であって、

第1の側面と、第2の側面と、第3の側面とを備えるビアと、

前記ビアの少なくとも前記第1の側面と前記第3の側面を囲むバリア手段とを備えるビア構造と、

前記ビア構造の前記バリア手段に直接結合されたパッドとを備える装置。 - 前記封止層の第1の表面に結合された第1の誘電体層をさらに備える、請求項11に記載の装置。

- 前記封止層の第2の表面に結合された第2の誘電体層をさらに備える、請求項12に記載の装置。

- 前記封止層の第1の表面に結合された基板をさらに備える、請求項11に記載の装置。

- 前記基板に結合された第1のダイをさらに備え、前記封止層は、前記第1のダイを封止する、請求項14に記載の装置。

- 前記ビア構造は充填材手段をさらに備える、請求項11に記載の装置。

- 前記ビアはシード層を備える、請求項11に記載の装置。

- 前記ビアは、パッドとして動作するように構成された部分を備える、請求項11に記載の装置。

- 少なくともインターポーザ、パッケージデバイス、および/またはパッケージオンパッケージデバイスのうちの1つを備える、請求項11に記載の装置。

- 音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および/またはラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項11に記載の装置。

- 集積デバイスを製作するための方法であって、

基板上にパッドを形成するステップと、

前記基板上に封止層を形成するステップと、

前記封止層内にビア構造を形成するステップとを含み、前記ビア構造を形成する前記ステップは、

前記封止層内にバリア層を形成するステップと、

前記バリア層上にビアを形成するステップとを含み、前記ビアは、第1の側面と、第2の側面と、第3の側面とを備え、前記ビアは、前記バリア層が前記ビアの少なくとも前記第1の側面と前記第3の側面を囲むように前記バリア層上に形成され、前記バリア層はパッドに直接結合される、方法。 - 前記封止層の第1の表面上に第1の誘電体層を形成するステップをさらに含む、請求項21に記載の方法。

- 前記封止層の第2の表面上に第2の誘電体層を形成するステップをさらに含む、請求項22に記載の方法。

- 前記基板の少なくとも一部を除去するステップをさらに含む、請求項21に記載の方法。

- 前記基板に第1のダイを結合するステップをさらに含み、前記封止層を形成する前記ステップは、前記第1のダイを前記封止層によって封止するステップを含む、請求項21に記載の方法。

- 前記ビア構造を形成するステップは、充填材を形成するステップをさらに含む、請求項21に記載の方法。

- 前記ビアを形成する前記ステップは、前記バリア層上にシード層を形成するステップを含む、請求項21に記載の方法。

- 前記ビアを形成する前記ステップは、ビアの一部をパッドとして形成するステップを含む、請求項21に記載の方法。

- 前記集積デバイスは、少なくともインターポーザ、パッケージデバイス、および/またはパッケージオンパッケージデバイスのうちの1つを備える、請求項21に記載の方法。

- 前記集積デバイスは、音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、モバイルデバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および/またはラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項21に記載の方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201461939523P | 2014-02-13 | 2014-02-13 | |

| US61/939,523 | 2014-02-13 | ||

| US14/274,517 US9466554B2 (en) | 2014-02-13 | 2014-05-09 | Integrated device comprising via with side barrier layer traversing encapsulation layer |

| US14/274,517 | 2014-05-09 | ||

| PCT/US2015/015421 WO2015123301A1 (en) | 2014-02-13 | 2015-02-11 | Integrated device comprising via with side barrier layer traversing encapsulation layer |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017511971A true JP2017511971A (ja) | 2017-04-27 |

| JP2017511971A5 JP2017511971A5 (ja) | 2018-02-08 |

Family

ID=53775574

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016550191A Ceased JP2017511971A (ja) | 2014-02-13 | 2015-02-11 | 封止層を横切るサイドバリア層を有するビアを備える集積デバイス |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9466554B2 (ja) |

| EP (1) | EP3105787B1 (ja) |

| JP (1) | JP2017511971A (ja) |

| CN (1) | CN105981166B (ja) |

| WO (1) | WO2015123301A1 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9343417B2 (en) * | 2013-09-18 | 2016-05-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Hollow metal pillar packaging scheme |

| US9385110B2 (en) | 2014-06-18 | 2016-07-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device and method |

| US9355963B2 (en) * | 2014-09-26 | 2016-05-31 | Qualcomm Incorporated | Semiconductor package interconnections and method of making the same |

| TWI559829B (zh) * | 2014-10-22 | 2016-11-21 | 矽品精密工業股份有限公司 | 封裝結構及其製法 |

| US10651160B2 (en) | 2017-03-20 | 2020-05-12 | Qualcomm Incorporated | Low profile integrated package |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010041630A1 (ja) * | 2008-10-10 | 2010-04-15 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US20100155920A1 (en) * | 2008-12-24 | 2010-06-24 | Samsung Electronics Co., Ltd. | Stacked semiconductor package, semiconductor package module and method of manufacturing the stacked semiconductor package |

| JP2011238674A (ja) * | 2010-05-07 | 2011-11-24 | Seiko Epson Corp | 配線基板、圧電発振器、ジャイロセンサー、配線基板の製造方法 |

| JP2012119688A (ja) * | 2010-12-02 | 2012-06-21 | Samsung Electronics Co Ltd | 積層パッケージ構造物、パッケージオンパッケージ素子、およびパッケージオンパッケージ素子製造方法 |

| JP2012129262A (ja) * | 2010-12-13 | 2012-07-05 | Sumitomo Bakelite Co Ltd | 半導体素子封止体の製造方法および半導体パッケージの製造方法 |

| US20120168944A1 (en) * | 2010-12-30 | 2012-07-05 | Stmicroelectronics Pte Ltd. | Through hole via filling using electroless plating |

| JP2013535834A (ja) * | 2010-07-23 | 2013-09-12 | テッセラ,インコーポレイテッド | 組立て後に平坦化される超小型電子素子 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6586682B2 (en) | 2000-02-23 | 2003-07-01 | Kulicke & Soffa Holdings, Inc. | Printed wiring board with controlled line impedance |

| GB0330010D0 (en) * | 2003-12-24 | 2004-01-28 | Cavendish Kinetics Ltd | Method for containing a device and a corresponding device |

| JP2005235860A (ja) * | 2004-02-17 | 2005-09-02 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| US8239162B2 (en) * | 2006-04-13 | 2012-08-07 | Tanenhaus & Associates, Inc. | Miniaturized inertial measurement unit and associated methods |

| US8021981B2 (en) | 2006-08-30 | 2011-09-20 | Micron Technology, Inc. | Redistribution layers for microfeature workpieces, and associated systems and methods |

| DE102007020266B3 (de) * | 2007-04-30 | 2008-11-13 | Advanced Micro Devices, Inc., Sunnyvale | Halbleiterstruktur mit einem elektrisch leitfähigen Strukturelement und Verfahren zu ihrer Herstellung |

| JP5596919B2 (ja) * | 2008-11-26 | 2014-09-24 | キヤノン株式会社 | 半導体装置の製造方法 |

| US7799602B2 (en) | 2008-12-10 | 2010-09-21 | Stats Chippac, Ltd. | Semiconductor device and method of forming a shielding layer over a semiconductor die after forming a build-up interconnect structure |

| JP2010157690A (ja) | 2008-12-29 | 2010-07-15 | Ibiden Co Ltd | 電子部品実装用基板及び電子部品実装用基板の製造方法 |

| US8476770B2 (en) * | 2011-07-07 | 2013-07-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Apparatus and methods for forming through vias |

| US9040346B2 (en) | 2012-05-03 | 2015-05-26 | Infineon Technologies Ag | Semiconductor package and methods of formation thereof |

| US8981559B2 (en) | 2012-06-25 | 2015-03-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Package on package devices and methods of packaging semiconductor dies |

-

2014

- 2014-05-09 US US14/274,517 patent/US9466554B2/en active Active

-

2015

- 2015-02-11 JP JP2016550191A patent/JP2017511971A/ja not_active Ceased

- 2015-02-11 WO PCT/US2015/015421 patent/WO2015123301A1/en active Application Filing

- 2015-02-11 CN CN201580008236.2A patent/CN105981166B/zh not_active Expired - Fee Related

- 2015-02-11 EP EP15706345.4A patent/EP3105787B1/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010041630A1 (ja) * | 2008-10-10 | 2010-04-15 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US20100155920A1 (en) * | 2008-12-24 | 2010-06-24 | Samsung Electronics Co., Ltd. | Stacked semiconductor package, semiconductor package module and method of manufacturing the stacked semiconductor package |

| JP2011238674A (ja) * | 2010-05-07 | 2011-11-24 | Seiko Epson Corp | 配線基板、圧電発振器、ジャイロセンサー、配線基板の製造方法 |

| JP2013535834A (ja) * | 2010-07-23 | 2013-09-12 | テッセラ,インコーポレイテッド | 組立て後に平坦化される超小型電子素子 |

| JP2012119688A (ja) * | 2010-12-02 | 2012-06-21 | Samsung Electronics Co Ltd | 積層パッケージ構造物、パッケージオンパッケージ素子、およびパッケージオンパッケージ素子製造方法 |

| JP2012129262A (ja) * | 2010-12-13 | 2012-07-05 | Sumitomo Bakelite Co Ltd | 半導体素子封止体の製造方法および半導体パッケージの製造方法 |

| US20120168944A1 (en) * | 2010-12-30 | 2012-07-05 | Stmicroelectronics Pte Ltd. | Through hole via filling using electroless plating |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150228556A1 (en) | 2015-08-13 |

| US9466554B2 (en) | 2016-10-11 |

| CN105981166B (zh) | 2019-04-16 |

| EP3105787B1 (en) | 2021-08-25 |

| WO2015123301A1 (en) | 2015-08-20 |

| EP3105787A1 (en) | 2016-12-21 |

| CN105981166A (zh) | 2016-09-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI575693B (zh) | 包括無機層中的高密度互連和有機層中的重分佈層的集成裝置 | |

| JP6309643B2 (ja) | 再分配層上に積層ダイを備える集積デバイス | |

| JP6505951B2 (ja) | 埋込みパッケージオンパッケージ(PoP)デバイスを備える集積デバイス | |

| TWI588965B (zh) | 層疊封裝元件及其製造方法 | |

| US9947642B2 (en) | Package-on-Package (PoP) device comprising a gap controller between integrated circuit (IC) packages | |

| US9153560B2 (en) | Package on package (PoP) integrated device comprising a redistribution layer | |

| US9230936B2 (en) | Integrated device comprising high density interconnects and redistribution layers | |

| US9368566B2 (en) | Package on package (PoP) integrated device comprising a capacitor in a substrate | |

| US20160343646A1 (en) | High aspect ratio interconnect for wafer level package (wlp) and integrated circuit (ic) package | |

| JP2017511971A (ja) | 封止層を横切るサイドバリア層を有するビアを備える集積デバイス | |

| US9355898B2 (en) | Package on package (PoP) integrated device comprising a plurality of solder resist layers | |

| US20180331061A1 (en) | Integrated device comprising bump on exposed redistribution interconnect | |

| JP6192859B2 (ja) | カプセル封止層の中にビアとしてワイヤを備える集積デバイス |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170619 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20170915 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20171219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180312 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180813 |

|

| A045 | Written measure of dismissal of application [lapsed due to lack of payment] |

Free format text: JAPANESE INTERMEDIATE CODE: A045 Effective date: 20181217 |