以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等(個数、数値、量、範囲等を含む)についても同様である。

以下、実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、複数の類似の部材(部位)が存在する場合には、総称の符号に記号を追加し個別または特定の部位を示す場合がある。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。

また、断面図において、各部位の大きさは実デバイスと対応するものではなく、図面を分かりやすくするため、特定の部位を相対的に大きく表示する場合がある。

(実施の形態1)

以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

[構造説明]

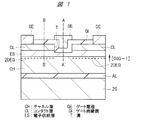

図1は、本実施の形態の半導体装置の構成を示す断面図である。図1に示す半導体装置は、窒化物半導体を用いた電界効果トランジスタ(FET;Field Effect Transistor)である。また、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)とも呼ばれる。

図1に示すように、本実施の形態の半導体装置においては、支持基板2S上に接合層ALを介して、チャネル層(電子走行層ともいう)CH、電子供給層ESおよびn型のコンタクト層CLの積層体が配置されている。この積層体は、窒化物半導体よりなる。そして、電子供給層ESは、チャネル層CHよりバンドギャップが広い窒化物半導体である。

ここでは、チャネル層CHとして、アンドープのGaN層が、電子供給層ESとして、アンドープのAlGaN層が、コンタクト層CLとして、n型のAlGaN層が用いられている。この電子供給層ESとチャネル層CHとの界面近傍のチャネル層CH側に、2次元電子ガス2DEGが生成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、チャネル層(アンドープのGaN層)CHから電子供給層(アンドープのAlGaN層)ES側へ向かう方向は、[000−1]方向となる。言い換えれば、接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

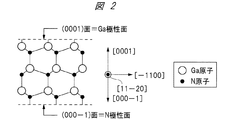

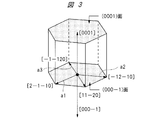

図2は、GaNの結晶構造を示す図であり、図3は、結晶における面と方位の関係を示す図である。

[000−1]方向([000−1]結晶軸方向ともいう)とは、図2および図3に示すように、c軸方向([0001]方向)の逆方向を意味する。よって、[000−1]方向は、(000−1)面に対する外向きの法線ベクトルの向きとなる。ここで、GaNの結晶構造においては、(000−1)面は、N面(窒素側の面、N極性面)となる。

また、[0001]方向([0001]結晶軸方向ともいう)とは、図2および図3に示すように、c軸方向([0001]方向)を意味する。よって、[0001]方向は、(0001)面に対する外向きの法線ベクトルの向きとなる。ここで、GaNの結晶構造においては、(0001)面は、Ga面(ガリウム側の面、Ga極性面)となる。

また、ゲート電極GEは、n型のコンタクト層(n型のAlGaN層)CLを貫通し、その底面から電子供給層(アンドープのAlGaN層)ESを露出する溝Tの内部に、ゲート絶縁膜GIを介して配置されている。このゲート電極GEの両側のn型のコンタクト層(n型のAlGaN層)CL上には、それぞれソース電極SEおよびドレイン電極DEが配置されている。

ゲート電極GE上には、層間絶縁層(図示せず)が配置される。また、上記ソース電極SEおよびドレイン電極DE上には、上記層間絶縁層中に形成されたコンタクトホール内に埋め込まれた導電性膜(プラグ、図示せず)が配置される。

[製法説明]

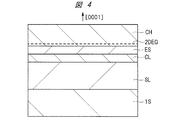

次いで、図4〜図14を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図4〜図14は、本実施の形態の半導体装置の製造工程を示す断面図である。

図4に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、有機金属気相成長(Metalorganic Chemical Vapor Deposition、MOCVDともいう)法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、n型のコンタクト層CLを形成する。例えば、MOCVD法を用いて、層厚50nm程度のn型のAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。次いで、n型のコンタクト層(n型のAlGaN層)CL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚20nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚1μm程度のアンドープのGaN層を堆積する。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CHの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にn型のAlGaNが成長し、n型のコンタクト層(n型のAlGaN層)CLが形成される。そして、n型のコンタクト層(n型のAlGaN層)CLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面近傍に、2次元電子ガス(2次元電子ガス層)2DEGが生成(形成)される。この2次元電子ガス2DEGの生成面、即ち、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面(界面)は、Ga面((0001)面)であり、この接合面(2次元電子ガス2DEGの生成面)からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(犠牲層(GaN層)SL、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CH)を形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

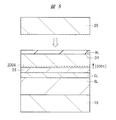

次いで、図5に示すように、チャネル層(アンドープのGaN層)CHの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、水素シルセスキオキサン(Hydrogen Silsesquioxane:HSQと略する)などの塗布系絶縁膜を用いることができる。また、支持基板2Sとしては、例えば、シリコン(Si)からなる基板を用いることができる。

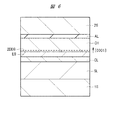

例えば、HSQの前駆体をチャネル層(アンドープのGaN層)CH上に塗布し、支持基板2Sを搭載した後、200℃程度の熱処理を施す。これにより、HSQが硬化し、図6に示すように、チャネル層(アンドープのGaN層)CHと支持基板2Sとを接合層ALを介して接着する(貼り合わせる)ことができる。接合層ALとして、HSQを用いた場合、約900℃程度までの熱負荷に耐えることができる。

次いで、図7に示すように、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、例えば、レーザーリフトオフ法を用いることができる。例えば、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの界面にレーザーを照射し、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの界面部においてアブレーションを生じさせ、隙間を形成する。次いで、この隙間から犠牲層(GaN層)SLと基板1Sとを剥離する。この結果、n型のコンタクト層(n型のAlGaN層)CL上に、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CHが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

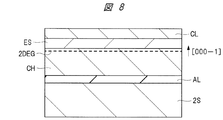

次いで、図8に示すように、上記積層構造体のn型のコンタクト層(n型のAlGaN層)CL側が上面となるように、上記積層構造体を反転させる。言い換えれば、上記積層構造体の[000−1]方向が上向きとなるように、上記積層構造体を配置する。これにより、支持基板2S上に接合層ALを介して、チャネル層(アンドープのGaN層)CH、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のAlGaN層)CLの積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

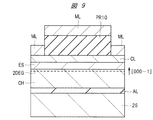

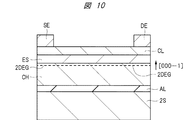

次いで、図9および図10に示すように、n型のコンタクト層(n型のAlGaN層)CL上のゲート電極GEの形成予定領域の両側にソース電極SEおよびドレイン電極DEを形成する。このソース電極SEおよびドレイン電極DEは、例えば、リフトオフ法を用いて形成することができる。例えば、図9に示すように、n型のコンタクト層(n型のAlGaN層)CL上にフォトレジスト膜PR10を形成し、露光・現像することにより、ソース電極SEおよびドレイン電極DEの形成領域上のフォトレジスト膜PR10を除去する。

次いで、フォトレジスト膜PR10上を含むn型のコンタクト層(n型のAlGaN層)CL上に、金属膜MLを形成する。これにより、ソース電極SEおよびドレイン電極DEの形成領域においては、n型のコンタクト層(n型のAlGaN層)CL上に、直接、金属膜MLが形成される。一方、その他の領域では、フォトレジスト膜PR10上に金属膜MLが形成される。

金属膜MLは、例えば、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al膜)により構成される。金属膜MLを構成する各膜は、例えば、真空蒸着法を用いて形成することができる。

次いで、フォトレジスト膜PR10を除去する。この際、フォトレジスト膜PR10上に形成されている金属膜MLもフォトレジスト膜PR10とともに除去され、n型のコンタクト層(n型のAlGaN層)CL上に直接接触するように形成されている金属膜ML(ソース電極SEおよびドレイン電極DE)だけが残存する(図10)。

次いで、支持基板2Sに対して、熱処理(アロイ処理)を施す。熱処理としては、例えば、窒素雰囲気中で、600℃、1分程度の熱処理を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。同様に、ドレイン電極DEとチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。即ち、ソース電極SEおよびドレイン電極DEが、それぞれ2次元電子ガス2DEGに対して電気的に接続された状態となる。

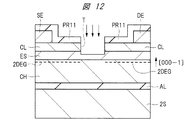

次いで、図11および図12に示すように、n型のコンタクト層(n型のAlGaN層)CLの中央部、言い換えれば、ゲート電極GEの形成予定領域の近傍のn型のコンタクト層(n型のAlGaN層)CLを除去することにより、n型のコンタクト層(n型のAlGaN層)CLを分離する。まず、図11に示すように、ソース電極SEおよびドレイン電極DE上を含むn型のコンタクト層(n型のAlGaN層)CL上にフォトレジスト膜PR11を形成し、露光・現像することにより、ゲート電極GEの形成予定領域の近傍のフォトレジスト膜PR11を除去する。

次いで、図12に示すように、フォトレジスト膜PR11をマスクとしてn型のコンタクト層(n型のAlGaN層)CLをドライエッチング法などを用いて除去する。エッチングガスとしては、塩化硼素(BCl3)系のガスを用いることができる。この工程により、n型のコンタクト層(n型のAlGaN層)CLの下層の電子供給層(アンドープのAlGaN層)ESが露出する。言い換えれば、n型のコンタクト層(n型のAlGaN層)CLを貫通し、電子供給層(アンドープのAlGaN層)ESまで到達する溝(リセスともいう)Tが形成される。この後、フォトレジスト膜PR11を除去する。

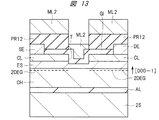

次いで、図13および図14に示すように、ゲート絶縁膜GIを形成した後、ゲート電極GEを形成する。まず、図13に示すように、ゲート絶縁膜GIを形成する。ゲート絶縁膜GIとしては、アルミナ(酸化アルミニウム、Al2O3)を用いることができる。例えば、ソース電極SE、ドレイン電極DEおよび溝Tの内部上を含むn型のコンタクト層(n型のAlGaN層)CL上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、原子層堆積(Atomic Layer Deposition:ALDと略する)法を用いて形成する。次いで、ソース電極SEおよびドレイン電極DE上のゲート絶縁膜GIを除去する。なお、このゲート絶縁膜GIの除去は、ソース電極SEおよびドレイン電極DE上にコンタクトホールを形成する際に行ってもよい。

次いで、ゲート絶縁膜GI上にゲート電極GEを形成する。ゲート電極GEは、例えば、リフトオフ法を用いて形成することができる。例えば、図13に示すように、ゲート絶縁膜GI上にフォトレジスト膜PR12を形成し、露光・現像することにより、ゲート電極GEの形成領域上のフォトレジスト膜PR12を除去する。

次いで、フォトレジスト膜PR12上を含むゲート絶縁膜GI上に、金属膜ML2を形成する。これにより、ゲート電極GEの形成領域においては、ゲート絶縁膜GI上に、直接、金属膜ML2が形成される。一方、その他の領域では、フォトレジスト膜PR12上に金属膜ML2が形成される。金属膜ML2は、例えば、ニッケル(Ni)膜と、ニッケル膜上に形成された金(Au)膜との積層膜(Ni/Au膜)により構成される。金属膜ML2を構成する各膜は、例えば、真空蒸着法を用いて形成することができる。

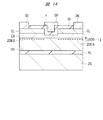

次いで、フォトレジスト膜PR12を除去する。この際、フォトレジスト膜PR12上に形成されている金属膜ML2もフォトレジスト膜PR12とともに除去され、溝Tの内部およびその近傍にのみ金属膜ML2(ゲート電極GE)が残存する(図14)。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GE、ソース電極SEおよびドレイン電極DEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

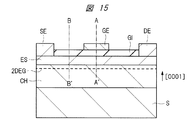

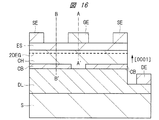

図15は、本実施の形態の比較例1の半導体装置の構成を示す断面図である。また、図16は、本実施の形態の比較例2の半導体装置の構成を示す断面図である。

図15の比較例1の半導体装置は、いわゆる横型のFETである。この半導体装置においては、基板S上に形成されたチャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとの積層体と、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介して形成されたゲート電極GEとを有する。このチャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとの界面近傍には、2次元電子ガス2DEGが形成される。また、ゲート電極GEの両側の電子供給層(アンドープのAlGaN層)ES上には、ソース電極SEおよびドレイン電極DEが形成されている。

ここで、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとの積層体は、[0001]方向のエピタキシャル成長により形成されている。言い換えれば、いわゆる、ガリウム(Ga)面成長モードにて形成されている。

このような、比較例1の構成の半導体装置は、閾値電圧(Vt)が負のノーマリオントランジスタであり、ノーマリオフ化は困難である。例えば、閾値電圧(Vt)は、−4V〜−9V程度である。さらに、比較例1の構成の半導体装置においては、ゲート絶縁膜GIを厚膜化するにしたがい、閾値電圧(Vt)が減少してしまう。即ち、比較例1の構成の半導体装置は、ノーマリオフ動作と高耐圧化を両立することがきわめて困難な構成である。

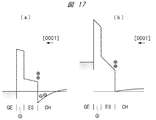

図17は、比較例1の半導体装置のゲート電極直下(A−A’部)における伝導帯エネルギープロファイルを示す図である。横軸は、ゲート電極直下(A−A’部)の位置を、縦軸は、エネルギーの大きさを示す。また、(a)は、ゲート電圧Vg=0Vの場合、(b)は、ゲート電圧Vg=閾値電圧(Vt)の場合の伝導帯エネルギープロファイルである。

電子供給層(アンドープのAlGaN層)ESはチャネル層(アンドープのGaN層)CHより格子定数が小さく、電子供給層(アンドープのAlGaN層)ESに引張応力が生じる。このため、自発性分極効果とピエゾ分極効果に基づいて電子供給層(アンドープのAlGaN層)ESに分極が発生する。[0001]方向のエピタキシャル成長により形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとがGa面配向した比較例1の構成では、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面が正電荷(+σ)になる。同様に、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面には負電荷(−σ)が発生する(図17(a))。しかしながら、この負電荷(−σ)は、ゲート絶縁膜GIとの界面準位により補償されるため電気的に中性になる。

この分極電荷の面密度σは、電子供給層ESであるAlGaN層のAl組成をx、素電荷をqとすると、次の式(1)のように近似できる。

σ/q≒6.4×1013[cm−2]×x…(1)

例えば、Al組成がx=0.2の場合、分極電荷の面密度σは、1.2×1013[cm−2]と計算される。このため、ゲート電圧Vg=0Vの熱平衡状態においてもヘテロ界面近傍に2次元電子ガス2DEGが誘起され、ノーマリオン動作となる(図17(a))。

一方、ゲート電圧Vg=閾値電圧(Vt)のオフ状態ではゲート絶縁膜GIの内部に電界が発生して、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーは、基板S側(チャネル層(アンドープのGaN層))からゲート電極GE側に向かって増加する(図17(b))。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が減少する。よって、所望の閾値電圧(Vt)を得るためには、ゲート絶縁膜GIを薄くする必要がある。このように、ノーマリオフ動作と高耐圧化を両立することが困難である。

図16の比較例2の半導体装置は、いわゆる縦型のFETである。この半導体装置においても、同様に、ノーマリオフ動作と高耐圧化を両立することが困難である。この場合、基板S上には、n型のドリフト層(GaN層)DLと、開口部を有するp型の電流ブロック層(GaN層)CBとが形成されている。この開口部は、電流狭窄部となる。p型の電流ブロック層(GaN層)CB上には、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとの積層体が形成され、電子供給層(アンドープのAlGaN層)ES上には、ゲート電極GEが形成されている。このチャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとの界面近傍には、2次元電子ガス2DEGが形成される。また、ゲート電極GEの両側の電子供給層(アンドープのAlGaN層)ES上には、ソース電極SEが形成されている。また、ドレイン電極DEは、n型のドリフト層(GaN層)DLの引き出し部上に形成されている。この比較例2の場合も、比較例1と同様に、ノーマリオフ動作と高耐圧化を両立することが困難である。

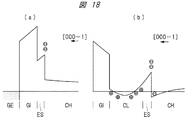

これに対し、本実施の形態の半導体装置の伝導帯エネルギープロファイルは図18に示すようになる。図18は、本実施の形態の半導体装置(図1)の伝導帯エネルギープロファイルを示す図である。横軸は、位置を、縦軸は、エネルギーの大きさを示す。また、(a)は、ゲート電極直下(A−A’部)の伝導帯エネルギープロファイルを示し、(b)は、ゲート電極とソース電極(またはドレイン電極)との間に位置する部位の直下(B−B’部)の伝導帯エネルギープロファイルを示す。

電子供給層(アンドープのAlGaN層)ESはチャネル層(アンドープのGaN層)CHより格子定数が小さく、電子供給層(アンドープのAlGaN層)ESに引張応力が生じる。このため、自発性分極効果とピエゾ分極効果に基づいて電子供給層(アンドープのAlGaN層)ESに分極が発生する。しかしながら、本実施の形態においては、結晶面を反転させたので、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。言い換えれば、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとがN面配向した本実施の形態の半導体装置においては、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面が負電荷(−σ)になる。同様に、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面には正電荷(+σ)が発生する(図18(a))。しかしながら、この正電荷(+σ)は、ゲート絶縁膜GIとの界面準位により補償されるため電気的に中性になる。

上記式(1)から、電子供給層ESであるAlGaN層のAl組成がx=0.2の場合、分極電荷の面密度σは、1.2×1013[cm−2]と計算される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a))。一方、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GIの内部に発生する電界の方向も比較例1の場合と逆になるため、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成される。ここで、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物の面密度を、例えば、5×1013cm−2と、負電荷の面密度σより大きくなるように設定する。また、チャネル層(アンドープのGaN層)CHは、電子供給層(アンドープのAlGaN層)ESよりバンドギャップが小さいため、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b))。

(変形例)

図1に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型の半導体層、n型の半導体領域ともいう、n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、チャネル層(アンドープのGaN層)CH、n型のコンタクト層(n型のGaN層)CLおよび電子供給層(アンドープのAlGaN層)ESを積層した後、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のGaN層)CLを除去することにより、溝Tを形成すればよい。

また、図1に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

なお、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとをN面配向させるためには、チャネル層(アンドープのGaN層)CH上に、[000−1]方向に、電子供給層(アンドープのAlGaN層)ESを結晶成長させる、いわゆる、N面(窒素面)での成長モードを用いることが考えられる。しかしながら、チャネル層(アンドープのGaN層)CHのN面は、エッチング速度がGa面より大きいことに起因して、鏡面成長を得るのが難しい。その結果、N面での成長モードでは、良好な結晶が得られない。

これに対し、本実施の形態においては、良好な結晶が得られるGa面モードでの結晶成長を行い、上下を反転させることで、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとがN面配向した積層体を得ることができる。特に、Ga面モードでの結晶成長を行い、レーザーリフトオフ法などを用いて、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの間を剥離することで、平坦性の高い積層体を形成することができる。

(実施の形態2)

実施の形態1においては、いわゆるリセスゲート構造のゲート電極を設けているが、本実施の形態においては、プレーナーゲート構造のゲート電極を用いる。

[構造説明]

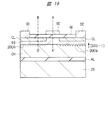

図19は、本実施の形態の半導体装置の構成を示す断面図である。図19に示す半導体装置は、窒化物半導体を用いた電界効果トランジスタである。また、高電子移動度トランジスタ(HEMT)とも呼ばれる。

図19に示すように、本実施の形態の半導体装置においては、支持基板2S上に接合層ALを介して、チャネル層(電子走行層ともいう)CH、電子供給層ESおよびn型のコンタクト層CLの積層体が配置されている。この積層体は、窒化物半導体よりなる。そして、電子供給層ESは、チャネル層CHよりバンドギャップが広い窒化物半導体である。

ここでは、チャネル層CHとして、アンドープのGaN層が、電子供給層ESとして、アンドープのAlGaN層が、コンタクト層CLとして、n型のAlGaN層が用いられている。この電子供給層ESとチャネル層CHとの界面近傍のチャネル層CH側に、2次元電子ガス2DEGが生成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そしてチャネル層(アンドープのGaN層)CHから電子供給層(アンドープのAlGaN層)ES側へ向かう方向は、[000−1]方向となる。言い換えれば、接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

また、ゲート電極GEは、n型のコンタクト層(n型のAlGaN層)CLの開口部から露出する電子供給層(アンドープのAlGaN層)ES上に、ゲート絶縁膜GIを介して配置されている。言い換えれば、ゲート電極GEの両側には、ゲート絶縁膜GIを介してn型のコンタクト層(n型のAlGaN層)CLが配置され、ゲート電極GE下には、ゲート絶縁膜GIを介して電子供給層(アンドープのAlGaN層)ESが配置されている。このゲート電極GEの両側のn型のコンタクト層(n型のAlGaN層)CL上には、それぞれソース電極SEおよびドレイン電極DEが配置されている。

ゲート電極GE上には、層間絶縁層(図示せず)が配置される。また、上記ソース電極SEおよびドレイン電極DE上には、上記層間絶縁層中に形成されたコンタクトホール内に埋め込まれた導電性膜(プラグ、図示せず)が配置される。

[製法説明]

次いで、図20〜図25を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図20〜図25は、本実施の形態の半導体装置の製造工程を示す断面図である。

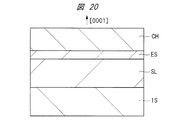

図20に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、MOCVD法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚50nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚1μm程度のアンドープのGaN層を堆積する。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CHの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(接合面)は、Ga面((0001)面)であり、この界面からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CH)を形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

次いで、図21に示すように、チャネル層(アンドープのGaN層)CHの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、HSQなどの塗布系絶縁膜を用いることができる。また、支持基板2Sとしては、例えば、シリコン(Si)からなる基板を用いることができる。

例えば、HSQの前駆体をチャネル層(アンドープのGaN層)CH上に塗布し、支持基板2Sを搭載した後、200℃程度の熱処理を施す。これにより、HSQが硬化し、図6に示すように、チャネル層(アンドープのGaN層)CHと支持基板2Sとを接合層ALを介して接着することができる。接合層ALとして、HSQを用いた場合、約900℃程度までの熱負荷に耐えることができる。

次いで、犠牲層(GaN層)SLと電子供給層(アンドープのAlGaN層)ESとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、実施の形態1と同様に、例えば、レーザーリフトオフ法を用いることができる。これにより、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CHが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

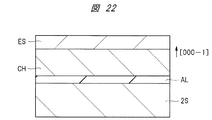

次いで、図22に示すように、上記積層構造体の電子供給層(アンドープのAlGaN層)ES側が上面となるように、上記積層構造体を反転させる。これにより、支持基板2S上に接合層ALを介して、チャネル層(アンドープのGaN層)CHおよび電子供給層(アンドープのAlGaN層)ESの積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

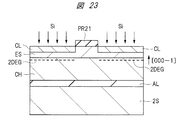

次いで、図23に示すように、イオン注入法によりn型のコンタクト層(n型のAlGaN層)CLを形成する。まず、図23に示すように、電子供給層(アンドープのAlGaN層)ES上にフォトレジスト膜PR21を形成し、露光・現像することにより、ゲート電極GEの形成予定領域以外のフォトレジスト膜PR21を除去する。次いで、フォトレジスト膜PR21をマスクとして、電子供給層(アンドープのAlGaN層)ESの上層部に、n型の不純物をイオン注入する。これにより、ゲート電極GEの形成予定領域の両側の電子供給層(アンドープのAlGaN層)ESの上層部に、n型のコンタクト層(n型のAlGaN層)CLが形成される。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。また、n型のコンタクト層(n型のAlGaN層)CLの厚さは、例えば30nm程度である。この後、フォトレジスト膜PR21を除去する。次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、n型のコンタクト層(n型のAlGaN層)CL中のn型の不純物(ここでは、Si)を活性化する。この熱処理により、n型のコンタクト層(n型のAlGaN層)CL中の電子濃度は、例えば、2×1019/cm3程度となる。

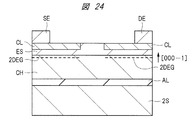

次いで、図24に示すように、n型のコンタクト層(n型のAlGaN層)CL上のゲート電極GEの形成予定領域の両側にソース電極SEおよびドレイン電極DEを形成する。このソース電極SEおよびドレイン電極DEは、実施の形態1と同様に、例えば、リフトオフ法を用いて形成することができる。次いで、実施の形態1と同様に、支持基板2Sに対して、熱処理(アロイ処理)を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。同様に、ドレイン電極DEとチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。即ち、ソース電極SEおよびドレイン電極DEが、それぞれ2次元電子ガス2DEGに対して電気的に接続された状態となる。

次いで、図25に示すように、ゲート絶縁膜GIを形成した後、ゲート電極GEを形成する。まず、実施の形態1と同様に、ゲート絶縁膜GIを形成する。例えば、ソース電極SE、ドレイン電極DE、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のAlGaN層)CL上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、原子層堆積法を用いて形成する。次いで、ソース電極SEおよびドレイン電極DE上のゲート絶縁膜GIを除去する。なお、このゲート絶縁膜GIの除去は、ソース電極SEおよびドレイン電極DE上にコンタクトホールを形成する際に行ってもよい。

次いで、ゲート絶縁膜GI上にゲート電極GEを形成する。ゲート電極GEは、実施の形態1と同様に、例えば、リフトオフ法を用いて形成することができる。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GE、ソース電極SEおよびドレイン電極DEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、実施の形態1で詳細に説明したように、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

即ち、本実施の形態の半導体装置の伝導帯エネルギープロファイルは、実施の形態1の場合(図18)と同様である。よって、実施の形態1において詳細に説明したように、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a)参照)。また、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b)参照)。

また、本実施の形態においては、溝Tの形成工程を必要としないため、閾値電圧(Vt)の調整が実施の形態1の場合より容易となる。

(変形例)

図19に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、図23に示すイオン注入法の際に、チャネル層(アンドープのGaN層)CHの上層部に、n型の不純物をイオン注入することにより、ゲート電極GEの形成予定領域の両側のチャネル層(アンドープのGaN層)CHの上層部に、n型のコンタクト層(n型のAlGaN層)CLを形成してもよい。

また、図19に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

(実施の形態3)

実施の形態1および2においては、いわゆる横型のFETを例に説明したが、実施の形態3〜6においては、いわゆる縦型のFETについて説明する。以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

[構造説明]

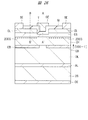

図26は、本実施の形態の半導体装置の構成を示す断面図である。図26に示す半導体装置は、窒化物半導体を用いた電界効果トランジスタである。また、高電子移動度トランジスタ(HEMT)とも呼ばれる。

図26に示すように、本実施の形態の半導体装置においては、支持基板2S上に接合層ALを介して、n型のドリフト層DL、電流ブロック層CB、チャネル層(電子走行層ともいう)CH、電子供給層ESおよびn型のコンタクト層CLの積層体が配置されている。この積層体は、窒化物半導体よりなる。そして、電子供給層ESは、チャネル層CHよりバンドギャップが広い窒化物半導体である。電流ブロック層CBは、ゲート電極GEと対応する位置に開口部(離間部)を有する。この電流ブロック層CBの開口部は、電流狭窄部となる。

ここでは、n型のドリフト層DLとして、n型のGaN層が、電流ブロック層CBとして、p型のGaN層が用いられている。そして、チャネル層CHとして、アンドープのGaN層が、電子供給層ESとして、アンドープのAlGaN層が、コンタクト層CLとして、n型のAlGaN層が用いられている。この電子供給層ESとチャネル層CHとの界面近傍のチャネル層CH側に、2次元電子ガス2DEGが生成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、チャネル層(アンドープのGaN層)CHから電子供給層(アンドープのAlGaN層)ES側へ向かう方向は、[000−1]方向となる。言い換えれば、接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

また、ゲート電極GEは、n型のコンタクト層(n型のAlGaN層)CLを貫通し、その底面から電子供給層(アンドープのAlGaN層)ESを露出する溝Tの内部に、ゲート絶縁膜GIを介して配置されている。このゲート電極GEの両側のn型のコンタクト層(n型のAlGaN層)CL上には、ソース電極SEが配置されている。また、ドレイン電極DEは、支持基板2Sの裏面側に配置されている。

このような構成の半導体装置は、縦型のFETと呼ばれ、キャリアが、チャネル層(アンドープのGaN層)CHから開口部(電流狭窄部)を介してn型のドリフト層(n型のGaN層)DLへと、支持基板2Sと垂直な方向に走行する。2次元電子ガス2DEGのキャリア濃度をゲート電圧で変調することによりFET動作が行われる。

ゲート電極GE上には、層間絶縁層(図示せず)が配置される。また、上記ソース電極SE上には、上記層間絶縁層中に形成されたコンタクトホール内に埋め込まれた導電性膜(プラグ、図示せず)が配置される。

[製法説明]

次いで、図27〜図32を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図27〜図32は、本実施の形態の半導体装置の製造工程を示す断面図である。

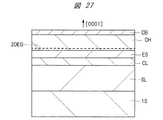

図27に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、MOCVD法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、n型のコンタクト層CLを形成する。例えば、MOCVD法を用いて、層厚50nm程度のn型のAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。次いで、n型のコンタクト層(n型のAlGaN層)CL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚20nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚0.1μm程度のアンドープのGaN層を堆積する。次いで、チャネル層CH(アンドープのGaN層)上に、p型の電流ブロック層(p型不純物層、p型の半導体領域ともいう)CBを形成する。例えば、MOCVD法を用いて、層厚0.5μm程度のp型のGaN層を堆積する。p型の不純物としては、例えばMg(マグネシウム)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびp型の電流ブロック層(p型のGaN層)CBの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にn型のAlGaNが成長し、n型のコンタクト層(n型のAlGaN層)CLが形成される。そして、n型のコンタクト層(n型のAlGaN層)CLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。そして、チャネル層(アンドープのGaN層)CHのGa面((0001)面)上に、[0001]方向にp型のGaNが成長し、電流ブロック層(p型のGaN層)CBが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面近傍に、2次元電子ガス(2次元電子ガス層)2DEGが生成(形成)される。この2次元電子ガス2DEGの生成面、即ち、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面(界面)は、Ga面((0001)面)であり、この接合面(2次元電子ガス2DEGの生成面)からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびp型の電流ブロック層(p型のGaN層)CB)を形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、電流ブロック層(p型のGaN層)CB中のp型の不純物(ここでは、Mg)を活性化する。この熱処理により、電流ブロック層(p型のGaN層)CB中の正孔濃度は、例えば、2×1018/cm3程度となる。

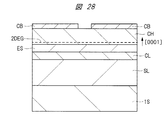

次いで、図28に示すように、電流ブロック層(p型のGaN層)CBの中央部、言い換えれば、ゲート電極GEの形成予定領域の近傍の電流ブロック層(p型のGaN層)CBを除去することにより、電流ブロック層(p型のGaN層)CBに開口部を形成する。例えば、電流ブロック層(p型のGaN層)CB上に、ゲート電極GEの形成予定領域を覆うフォトレジスト膜(図示せず)を形成し、電流ブロック層(p型のGaN層)CBをドライエッチング法などを用いて除去する。エッチングガスとしては、塩化硼素(BCl3)系のガスを用いることができる。この工程により、電流ブロック層(p型のGaN層)CBに開口部が形成され、その底面からチャネル層(アンドープのGaN層)CHが露出する。この後、上記フォトレジスト膜(図示せず)を除去する。

次いで、図29に示すように、チャネル層(アンドープのGaN層)CHの露出部を含む電流ブロック層(p型のGaN層)CB上に、n型のドリフト層(n型のGaN層)DLを形成する。例えば、上記開口部内を含む電流ブロック層(p型のGaN層)CB上に、層厚10μm程度のn型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、5×1016/cm3程度である。このように、開口部内を含む電流ブロック層(p型のGaN層)CB上へのエピタキシャル成長は、埋め込み再成長と呼ばれる。

なお、電流ブロック層CBとして、p型のGaN層とその上部のAlN層(窒化アルミニウム層、層厚0.01μm程度)との積層膜を用いてもよい。この場合、この積層膜に開口部を形成し、開口部内を含む電流ブロック層(積層膜)CB上に、n型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる(埋め込み再成長)。この際、開口部内においては、チャネル層(アンドープのGaN層)CHの露出部からn型のドリフト層(n型のGaN層)DLがエピタキシャル成長し、他の部分においては、AlN層上にn型のドリフト層(n型のGaN層)DLがエピタキシャル成長する。AlN層上においては、アンドープのGaN層上と比較し、n型のGaN層の成長速度が小さい。よって、開口部内において優先的に成膜がなされる。また、開口部がn型のGaN層で埋め尽くされた後は、開口部の両側において横方向に成長が進む。これにより、埋め込み再成長の際、n型のドリフト層(n型のGaN層)DLの表面の平坦性を向上させることができる。上記開口部に埋め込まれたn型のドリフト層(n型のGaN層)DLは、電流狭窄部(アパーチャー)となる。

次いで、図30に示すように、n型のドリフト層(n型のGaN層)DLの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、Au(金)と錫(Sn)との合金である半田層を用いることができる。また、半田層の上下に金属膜(メタライズ)を設けてもよい。例えば、n型のドリフト層(n型のGaN層)DLの(0001)面上に、金属膜として、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を形成し、この上部に、半田層を形成する。また、支持基板2S上に金属膜として、チタン(Ti)膜と、チタン膜上に形成された白金(Pt)膜と、白金膜上に形成された金(Au)膜との積層膜(Ti/Pt/Au)を形成する。支持基板2Sとしては、シリコン(Si)からなる基板を用いることができる。

次いで、接合層ALである半田層と、支持基板2Sの金属膜とを対向させ、n型のドリフト層(n型のGaN層)DLと支持基板2Sとを半田層(接合層AL)を介して融着する。

次いで、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、実施の形態1の場合と同様に、レーザーリフトオフ法を用いることができる。

これにより、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CH、電流ブロック層(p型のGaN層)CB、n型のドリフト層(n型のGaN層)DLが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

次いで、図31に示すように、上記積層構造体のn型のコンタクト層(n型のAlGaN層)CL側が上面となるように、上記積層構造体を反転させる。これにより、支持基板2S上に接合層ALを介して上記積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

次いで、図32に示すように、n型のコンタクト層(n型のAlGaN層)CL上に、ソース電極SEを形成する。このソース電極SEは、実施の形態1の場合と同様に、リフトオフ法を用いて形成することができる。例えば、ソース電極SEの形成領域に開口部を有するフォトレジスト膜(図示せず)を形成する。次いで、このフォトレジスト膜上を含むn型のコンタクト層(n型のAlGaN層)CL上に、金属膜を形成し、フォトレジスト膜上の金属膜をフォトレジスト膜とともに除去する。これにより、n型のコンタクト層(n型のAlGaN層)CL上に、ソース電極SEを形成することができる。

次いで、支持基板2Sに対して、熱処理(アロイ処理)を施す。熱処理としては、例えば、窒素雰囲気中で、600℃、1分程度の熱処理を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。

次いで、実施の形態1と同様にして、溝Tを形成した後、ゲート絶縁膜GIを形成し、さらに、ゲート電極GEを形成する。即ち、n型のコンタクト層(n型のAlGaN層)CLをドライエッチング法などを用いて除去し、n型のコンタクト層(n型のAlGaN層)CLを貫通し、電子供給層(アンドープのAlGaN層)ESを露出する溝Tを形成する。そして、ソース電極SE上を含む電子供給層(アンドープのAlGaN層)ES上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、ALD法を用いて形成する。次いで、ソース電極SE上のゲート絶縁膜GIを除去する。次いで、溝Tの内部のゲート絶縁膜GI上にゲート電極GEをリフトオフ法などを用いて形成する。

次いで、支持基板2Sの裏面側が上面となるように支持基板2Sを反転し、支持基板2S上にドレイン電極DEを形成する(図32)。例えば、支持基板2S上に、金属膜を形成することにより、ドレイン電極DEを形成する。金属膜としては、例えば、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を用いることができる。この膜は、例えば、真空蒸着法を用いて形成することができる。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GEおよびソース電極SEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、実施の形態1で詳細に説明したように、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

即ち、本実施の形態の半導体装置の伝導帯エネルギープロファイルは、実施の形態1の場合(図18)と同様である。よって、実施の形態1において詳細に説明したように、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a)参照)。また、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b)参照)。

また、本実施の形態においては、電流ブロック層(p型のGaN層)CBに開口部(電流狭窄部)を設けたので、効率良くキャリアをドレイン側に導くことができる。また、本実施の形態によれば、電流ブロック層(p型のGaN層)CBや、その開口部(電流狭窄部)も容易に形成することができる。

(変形例)

図26に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、チャネル層(アンドープのGaN層)CH、n型のコンタクト層(n型のGaN層)CLおよび電子供給層(アンドープのAlGaN層)ESを積層した後、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のGaN層)CLを除去することにより、溝Tを形成すればよい。

また、図26に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

(実施の形態4)

以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

[構造説明]

図33は、本実施の形態の半導体装置の構成を示す断面図である。図33に示す半導体装置は、窒化物半導体を用いた電界効果トランジスタである。また、高電子移動度トランジスタ(HEMT)とも呼ばれる。

図33に示すように、本実施の形態の半導体装置においては、支持基板2S上に接合層ALを介して、n型のドリフト層DL、電流ブロック層CB、チャネル層(電子走行層ともいう)CH、電子供給層ESおよびn型のコンタクト層CLの積層体が配置されている。この積層体は、窒化物半導体よりなる。そして、電子供給層ESは、チャネル層CHよりバンドギャップが広い窒化物半導体である。

電流ブロック層CBは、ゲート電極GEと対応する位置に開口部を有する。この電流ブロック層CBの開口部は、電流狭窄部となる。

ここでは、n型のドリフト層DLとして、n型のGaN層が、電流ブロック層CBとして、p型のGaN層が用いられている。そして、チャネル層CHとして、アンドープのGaN層が、電子供給層ESとして、アンドープのAlGaN層が、コンタクト層CLとして、n型のAlGaN層が用いられている。この電子供給層ESとチャネル層CHとの界面近傍のチャネル層CH側に、2次元電子ガス2DEGが生成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、チャネル層(アンドープのGaN層)CHから電子供給層(アンドープのAlGaN層)ES側へ向かう方向は、[000−1]方向となる。言い換えれば、接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

また、ゲート電極GEは、n型のコンタクト層(n型のAlGaN層)CLの開口部から露出する電子供給層(アンドープのAlGaN層)ES上に、ゲート絶縁膜GIを介して配置されている。言い換えれば、ゲート電極GEの両側には、ゲート絶縁膜GIを介してn型のコンタクト層(n型のAlGaN層)CLが配置され、ゲート電極GE下には、ゲート絶縁膜GIを介して電子供給層(アンドープのAlGaN層)ESが配置されている。このゲート電極GEの両側のn型のコンタクト層(n型のAlGaN層)CL上には、ソース電極SEが配置されている。また、ドレイン電極DEは、支持基板2Sの裏面側に配置されている。

このような構成の半導体装置は、縦型のFETと呼ばれ、キャリアが、チャネル層(アンドープのGaN層)CHから開口部(電流狭窄部)を介してn型のドリフト層(n型のGaN層)DLへと、支持基板2Sと垂直な方向に走行する。2次元電子ガス2DEGのキャリア濃度をゲート電圧で変調することによりFET動作が行われる。

ゲート電極GE上には、層間絶縁層(図示せず)が配置される。また、上記ソース電極SE上には、上記層間絶縁層中に形成されたコンタクトホール内に埋め込まれた導電性膜(プラグ、図示せず)が配置される。

[製法説明]

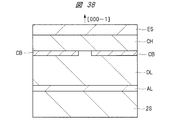

次いで、図34〜図40を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図34〜図40は、本実施の形態の半導体装置の製造工程を示す断面図である。

図34に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、MOCVD法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚20nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚0.1μm程度のアンドープのGaN層を堆積する。次いで、チャネル層CH(アンドープのGaN層)上に、p型の電流ブロック層CBを形成する。例えば、MOCVD法を用いて、層厚0.5μm程度のp型のGaN層を堆積する。p型の不純物としては、例えばMg(マグネシウム)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびp型の電流ブロック層(p型のGaN層)CBの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。そして、チャネル層(アンドープのGaN層)CHのGa面((0001)面)上に、[0001]方向にp型のGaNが成長し、電流ブロック層(p型のGaN層)CBが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(接合面)は、Ga面((0001)面)であり、この界面(接合面)からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびp型の電流ブロック層(p型のGaN層)CB)を形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、電流ブロック層(p型のGaN層)CB中のp型の不純物(ここでは、Mg)を活性化する。この熱処理により、電流ブロック層(p型のGaN層)CB中の正孔濃度は、例えば、2×1018/cm3程度となる。

次いで、図35に示すように、電流ブロック層(p型のGaN層)CBの中央部、言い換えれば、ゲート電極GEの形成予定領域の近傍の電流ブロック層(p型のGaN層)CBを除去することにより、電流ブロック層(p型のGaN層)CBに開口部を形成する。例えば、電流ブロック層(p型のGaN層)CB上に、ゲート電極GEの形成予定領域を覆うフォトレジスト膜(図示せず)を形成し、電流ブロック層(p型のGaN層)CBをドライエッチング法などを用いて除去する。エッチングガスとしては、塩化硼素(BCl3)系のガスを用いることができる。この工程により、電流ブロック層(p型のGaN層)CBに開口部が形成され、その底面からチャネル層(アンドープのGaN層)CHが露出する。この後、上記フォトレジスト膜(図示せず)を除去する。

次いで、図36に示すように、チャネル層(アンドープのGaN層)CHの露出部を含む電流ブロック層(p型のGaN層)CB上に、n型のドリフト層(n型のGaN層)DLを形成する。例えば、上記開口部内を含む電流ブロック層(p型のGaN層)CB上に、層厚10μm程度のn型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、5×1016/cm3程度である。このように、開口部内を含む電流ブロック層(p型のGaN層)CB上へのエピタキシャル成長は、埋め込み再成長と呼ばれる。

なお、電流ブロック層CBとして、p型のGaN層とその上部のAlN層(窒化アルミニウム層、層厚0.01μm程度)との積層膜を用いてもよい。この場合、この積層膜に開口部を形成し、開口部内を含む電流ブロック層(積層膜)CB上に、n型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる(埋め込み再成長)。この際、開口部内においては、チャネル層(アンドープのGaN層)CHの露出部からn型のドリフト層(n型のGaN層)DLがエピタキシャル成長し、他の部分においては、AlN層上にn型のドリフト層(n型のGaN層)DLがエピタキシャル成長する。AlN層上においては、アンドープのGaN層上と比較し、n型のGaN層の成長速度が小さい。よって、開口部内において優先的に成膜がなされる。また、開口部がn型のGaN層で埋め尽くされた後は、開口部の両側において横方向に成長が進む。これにより、埋め込み再成長の際、n型のドリフト層(n型のGaN層)DLの表面の平坦性を向上させることができる。上記開口部に埋め込まれたn型のドリフト層(n型のGaN層)DLは、電流狭窄部となる。

次いで、図37に示すように、n型のドリフト層(n型のGaN層)DLの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、Ag(銀)ペーストを用いることができる。また、Ag(銀)ペーストの上下に金属膜(メタライズ)を設けてもよい。例えば、n型のドリフト層(n型のGaN層)DLの(0001)面上に、金属膜として、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜の積層膜(Ti/Al)を形成し、この上部に、Ag(銀)ペーストを形成する。また、支持基板2S上に金属膜として、チタン(Ti)膜と、チタン膜上に形成された白金(Pt)膜と、白金膜上に形成された金(Au)膜との積層膜(Ti/Pt/Au)を形成する。支持基板2Sとしては、シリコン(Si)からなる基板を用いることができる。

次いで、接合層ALであるAg(銀)ペーストと、支持基板2Sの金属膜とを対向させ、n型のドリフト層(n型のGaN層)DLと支持基板2SとをAg(銀)ペースト(接合層AL)を介して融着する。

次いで、犠牲層(GaN層)SLと電子供給層(アンドープのAlGaN層)ESとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、実施の形態1の場合と同様に、レーザーリフトオフ法を用いることができる。

これにより、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CH、電流ブロック層(p型のGaN層)CB、n型のドリフト層(n型のGaN層)DLが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

次いで、図38に示すように、上記積層構造体の電子供給層(アンドープのAlGaN層)ES側が上面となるように、上記積層構造体を反転させる。これにより、支持基板2S上に接合層ALを介して上記積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

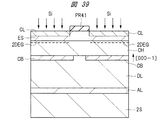

次いで、図39に示すように、イオン注入法によりn型のコンタクト層(n型のAlGaN層)CLを形成する。まず、電子供給層(アンドープのAlGaN層)ES上のゲート電極GEの形成予定領域にフォトレジスト膜PR41を形成する。次いで、フォトレジスト膜PR41をマスクとして、電子供給層(アンドープのAlGaN層)ESの上層部に、n型の不純物をイオン注入する。これにより、ゲート電極GEの形成予定領域の両側の電子供給層(アンドープのAlGaN層)ESの上層部に、n型のコンタクト層(n型のAlGaN層)CLが形成される。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。また、n型のコンタクト層(n型のAlGaN層)CLの厚さは、例えば30nm程度である。この後、フォトレジスト膜PR41を除去する。次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、n型のコンタクト層(n型のAlGaN層)CL中のn型の不純物(ここでは、Si)を活性化する。この熱処理により、n型のコンタクト層(n型のAlGaN層)CL中の電子濃度は、例えば、2×1019/cm3程度となる。

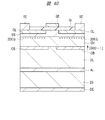

次いで、図40に示すように、n型のコンタクト層(n型のAlGaN層)CL上のゲート電極GEの形成予定領域の両側にソース電極SEを形成する。このソース電極SEは、実施の形態1の場合と同様に、リフトオフ法を用いて形成することができる。例えば、ソース電極SEの形成領域に開口部を有するフォトレジスト膜(図示せず)を形成する。次いで、このフォトレジスト膜上を含むn型のコンタクト層(n型のAlGaN層)CL上に、金属膜を形成し、フォトレジスト膜上の金属膜をフォトレジスト膜とともに除去する。これにより、n型のコンタクト層(n型のAlGaN層)CL上に、ソース電極SEを形成することができる。

次いで、支持基板2Sに対して、熱処理(アロイ処理)を施す。熱処理としては、例えば、窒素雰囲気中で、600℃、1分程度の熱処理を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。

次いで、実施の形態2と同様にして、ゲート絶縁膜GIを形成し、さらに、ゲート電極GEを形成する。即ち、ソース電極SE上を含む電子供給層(アンドープのAlGaN層)ES上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、ALD法を用いて形成する。次いで、ソース電極SE上のゲート絶縁膜GIを除去する。次いで、ゲート絶縁膜GI上にゲート電極GEをリフトオフ法などを用いて形成する。

次いで、支持基板2Sの裏面側が上面となるように支持基板2Sを反転し、支持基板2S上にドレイン電極DEを形成する(図40)。例えば、支持基板2S上に、金属膜を形成することにより、ドレイン電極DEを形成する。金属膜としては、例えば、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を用いることができる。この膜は、例えば、真空蒸着法を用いて形成することができる。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GEおよびソース電極SEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、実施の形態1で詳細に説明したように、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

即ち、本実施の形態の半導体装置の伝導帯エネルギープロファイルは、実施の形態1の場合(図18)と同様である。よって、実施の形態1において詳細に説明したように、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a)参照)。また、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b)参照)。

また、本実施の形態においては、電流ブロック層(p型のGaN層)CBに開口部(電流狭窄部)を設けたので、効率良くキャリアをドレイン側に導くことができる。また、本実施の形態によれば、電流ブロック層(p型のGaN層)CBや、その開口部(電流狭窄部)も容易に形成することができる。

(変形例)

図33に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、チャネル層(アンドープのGaN層)CHおよび電子供給層(アンドープのAlGaN層)ESの積層体のうち、チャネル層(アンドープのGaN層)CHの上層部にn型の不純物をイオン注入し、n型のコンタクト層(n型のGaN層)CLを形成してもよい。

また、図33に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

(実施の形態5)

本実施の形態においては、実施の形態3の電流ブロック層(p型のGaN層)CBを、イオン注入法で形成する。以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

[構造説明]

本実施の形態の半導体装置の構成は実施の形態3(図26)と同様の構成であるため、その詳細な説明を省略する。

[製法説明]

次いで、図41〜図45を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図41〜図45は、本実施の形態の半導体装置の製造工程を示す断面図である。

図41に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、MOCVD法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、n型のコンタクト層CLを形成する。例えば、MOCVD法を用いて、層厚50nm程度のn型のAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。次いで、n型のコンタクト層(n型のAlGaN層)CL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚20nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚0.1μm程度のアンドープのGaN層を堆積する。次いで、チャネル層CH(アンドープのGaN層)上に、n型のドリフト層(n型のGaN層)DLを形成する。例えば、チャネル層CH(アンドープのGaN層)上に、層厚10μm程度のn型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、5×1016/cm3程度である。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ESおよびチャネル層(アンドープのGaN層)CHの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にn型のAlGaNが成長し、n型のコンタクト層(n型のAlGaN層)CLが形成される。そして、n型のコンタクト層(n型のAlGaN層)CLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。そして、チャネル層(アンドープのGaN層)CHのGa面((0001)面)上に、[0001]方向にn型のGaNが成長し、n型のドリフト層(n型のGaN層)DLが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面近傍に、2次元電子ガス(2次元電子ガス層)2DEGが生成(形成)される。この2次元電子ガス2DEGの生成面、即ち、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面(界面)は、Ga面((0001)面)であり、この接合面(2次元電子ガス2DEGの生成面)からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびn型のドリフト層(n型のGaN層)DL)を形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

次いで、図42に示すように、イオン注入法によりp型の電流ブロック層(p型のGaN層)CBを形成する。まず、n型のドリフト層(n型のGaN層)DL上のゲート電極GEの形成予定領域にフォトレジスト膜PR51を形成する。次いで、フォトレジスト膜PR51をマスクとして、n型のドリフト層(n型のGaN層)DLの底部に、p型の不純物をイオン注入する。これにより、ゲート電極GEの形成予定領域の両側のn型のドリフト層(n型のGaN層)DLの底部、即ち、n型のドリフト層(n型のGaN層)DLとチャネル層(アンドープのGaN層)CHとの境界部近傍に、p型の電流ブロック層(p型のGaN層)CBが形成される。p型の不純物としては、例えばMg(マグネシウム)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。また、p型の電流ブロック層(p型のGaN層)CBの厚さは、例えば0.5μm程度である。この後、フォトレジスト膜PR51を除去する。次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、p型の電流ブロック層(p型のGaN層)CB中のp型の不純物(ここでは、Mg)を活性化する。この熱処理により、n型のコンタクト層(n型のAlGaN層)CL中の正孔濃度は、例えば、2×1018/cm3程度となる。

なお、p型の電流ブロック層(p型のGaN層)CBの形成に際して、比較例2(図16)のp型の電流ブロック層(p型のGaN層)CBをイオン注入法で形成する場合には、電子供給層ES側から、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(2次元電子ガス2DEG)を介して不純物イオンを注入する必要がある。このため、これらの層において不純物イオンの注入による損傷が生じ、上記界面(2次元電子ガス2DEG)でのキャリアの移動度やキャリア濃度が低下する恐れがある。

これに対し、本実施の形態によれば、n型のドリフト層(n型のGaN層)DLから不純物イオンを注入することができるため、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(2次元電子ガス2DEG)において不純物イオンの注入による損傷が生じ難い。よって、上記界面(2次元電子ガス2DEG)でのキャリアの移動度やキャリア濃度を向上させることができる。

次いで、図43に示すように、n型のドリフト層(n型のGaN層)DLの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、Au(金)と錫(Sn)との合金である半田層を用いることができる。また、半田層の上下に金属膜(メタライズ)を設けてもよい。例えば、n型のドリフト層(n型のGaN層)DLの(0001)面上に、金属膜として、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を形成し、この上部に、半田層を形成する。また、支持基板2S上に金属膜として、チタン(Ti)膜と、チタン膜上に形成された白金(Pt)膜と、白金膜上に形成された金(Au)膜との積層膜(Ti/Pt/Au)を形成する。支持基板2Sとしては、シリコン(Si)からなる基板を用いることができる。

次いで、接合層ALである半田層と、支持基板2Sの金属膜とを対向させ、n型のドリフト層(n型のGaN層)DLと支持基板2Sとを半田層(接合層AL)を介して融着する。

次いで、犠牲層(GaN層)SLとn型のコンタクト層(n型のAlGaN層)CLとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、実施の形態1の場合と同様に、レーザーリフトオフ法を用いることができる。

これにより、n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CH、電流ブロック層(p型のGaN層)CB、n型のドリフト層(n型のGaN層)DLが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

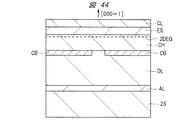

次いで、図44に示すように、上記積層構造体のn型のコンタクト層(n型のAlGaN層)CL側が上面となるように、上記積層構造体を反転させる。これにより、支持基板2S上に接合層ALを介して上記積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面(2次元電子ガス2DEGの生成面)から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

次いで、図45に示すように、n型のコンタクト層(n型のAlGaN層)CL上に、ソース電極SEを形成する。このソース電極SEは、実施の形態1の場合と同様に、リフトオフ法を用いて形成することができる。例えば、ソース電極SEの形成領域に開口部を有するフォトレジスト膜(図示せず)を形成する。次いで、このフォトレジスト膜上を含むn型のコンタクト層(n型のAlGaN層)CL上に、金属膜を形成し、フォトレジスト膜上の金属膜をフォトレジスト膜とともに除去する。これにより、n型のコンタクト層(n型のAlGaN層)CL上に、ソース電極SEを形成することができる。

次いで、支持基板2Sに対して、熱処理(アロイ処理)を施す。熱処理としては、例えば、窒素雰囲気中で、600℃、1分程度の熱処理を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。

次いで、実施の形態1と同様にして、溝Tを形成した後、ゲート絶縁膜GIを形成し、さらに、ゲート電極GEを形成する。即ち、n型のコンタクト層(n型のAlGaN層)CLをドライエッチング法などを用いて除去し、n型のコンタクト層(n型のAlGaN層)CLを貫通し、電子供給層(アンドープのAlGaN層)ESを露出する溝Tを形成する。そして、ソース電極SE上を含む電子供給層(アンドープのAlGaN層)ES上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、ALD法を用いて形成する。次いで、ソース電極SE上のゲート絶縁膜GIを除去する。次いで、溝Tの内部のゲート絶縁膜GI上にゲート電極GEをリフトオフ法などを用いて形成する。

次いで、支持基板2Sの裏面側が上面となるように支持基板2Sを反転し、支持基板2S上にドレイン電極DEを形成する。例えば、支持基板2S上に、金属膜を形成することにより、ドレイン電極DEを形成する。金属膜としては、例えば、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を用いることができる。この膜は、例えば、真空蒸着法を用いて形成することができる。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GEおよびソース電極SEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、実施の形態1で詳細に説明したように、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

即ち、本実施の形態の半導体装置の伝導帯エネルギープロファイルは、実施の形態1の場合(図18)と同様である。よって、実施の形態1において詳細に説明したように、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a)参照)。また、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b)参照)。

また、本実施の形態においては、電流ブロック層(p型のGaN層)CBに開口部(電流狭窄部)を設けたので、効率良くキャリアをドレイン側に導くことができる。また、本実施の形態によれば、電流ブロック層(p型のGaN層)CBや、その開口部(電流狭窄部)も容易に形成することができる。

(変形例)

図45に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、チャネル層(アンドープのGaN層)CH、n型のコンタクト層(n型のGaN層)CLおよび電子供給層(アンドープのAlGaN層)ESを積層した後、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のGaN層)CLを除去することにより、溝Tを形成すればよい。

また、図45に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

(実施の形態6)

本実施の形態においては、実施の形態4の電流ブロック層(p型のGaN層)CBを、イオン注入法で形成する。以下、図面を参照しながら本実施の形態の半導体装置について詳細に説明する。

[構造説明]

本実施の形態の半導体装置の構成は実施の形態4(図33)と同様の構成であるため、その詳細な説明を省略する。

[製法説明]

次いで、図46〜図50を参照しながら、本実施の形態の半導体装置の製造方法を説明するとともに、当該半導体装置の構成をより明確にする。図46〜図50は、本実施の形態の半導体装置の製造工程を示す断面図である。

図46に示すように、基板(成長用基板ともいう)1Sとして、例えば窒化ガリウム(GaN)からなる基板1Sを準備する。

次いで、基板1S上に核生成層(図示せず)を介して犠牲層SLを形成する。この犠牲層SLは、例えば、GaN層よりなる。例えば、窒化ガリウム(GaN)からなる基板1S上に、MOCVD法を用いて、層厚1μm程度の犠牲層(GaN層)SLを堆積する。

次いで、犠牲層(GaN層)SL上に、電子供給層ESを形成する。例えば、MOCVD法を用いて、層厚50nm程度のアンドープのAlGaN層を堆積する。AlGaN層は、Al0.2Ga0.8Nで示す組成比を有する。次いで、電子供給層(アンドープのAlGaN層)ES上にチャネル層CHを形成する。例えば、MOCVD法を用いて、層厚0.1μm程度のアンドープのGaN層を堆積する。次いで、チャネル層CH(アンドープのGaN層)上に、n型のドリフト層(n型のGaN層)DLを形成する。例えば、チャネル層CH(アンドープのGaN層)上に、層厚10μm程度のn型のドリフト層(n型のGaN層)DLをMOCVD法を用いて成長させる。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、5×1016/cm3程度である。

このようなMOCVD法を用いて形成された成長膜をエピタキシャル層(エピタキシャル膜)という。上記犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびn型のドリフト層(n型のGaN層)DLの積層体は、[0001]結晶軸方向に平行なGa面での成長モードにて形成される。言い換えれば、[0001]結晶軸方向に平行なGa面上に、それぞれの層が順次成長する。

具体的には、窒化ガリウム(GaN)からなる基板1SのGa面((0001)面)上に、[0001]方向にGaNが成長し、犠牲層(GaN層)SLが形成される。そして、犠牲層(GaN層)SLのGa面((0001)面)上に、[0001]方向にアンドープのAlGaNが成長し、電子供給層(アンドープのAlGaN層)ESが形成される。そして、電子供給層(アンドープのAlGaN層)ESのGa面((0001)面)上に、[0001]方向にアンドープのGaNが成長し、チャネル層(アンドープのGaN層)CHが形成される。そして、チャネル層(アンドープのGaN層)CHのGa面((0001)面)上に、[0001]方向にn型のGaNが成長し、n型のドリフト層(n型のGaN層)DLが形成される。

この電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(接合面)は、Ga面((0001)面)であり、この界面(接合面)からチャネル層(アンドープのGaN層)CH側への方向は、[0001]方向となる。

このように、[0001]結晶軸方向に平行なGa面での成長モードで、上記積層体の各層(犠牲層(GaN層)SL、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CHおよびn型のドリフト層(n型のGaN層)DLを形成することにより、凹凸の少ないより平坦なエピタキシャル層よりなる積層体を得ることができる。

ここで、AlGaNとGaNとは、格子定数が異なるが、AlGaNのトータル膜厚を臨界膜厚以下に設定することにより、転位の発生の少ない良好な結晶品質の積層体を得ることができる。

基板1Sとしては、窒化ガリウム(GaN)からなる基板以外の基板を用いてもよい。窒化ガリウム(GaN)からなる基板を用いることにより、転位発生の少ない良好な結晶品質の積層体を成長させることができる。上記転位などの結晶欠陥は、リーク電流の原因となる。このため、結晶欠陥を抑制することにより、リーク電流を低減することができ、トランジスタのオフ耐圧を向上させることができる。

なお、基板1S上の核生成層(図示せず)としては、窒化ガリウム(GaN)層と窒化アルミニウム(AlN)層との積層膜(AlN/GaN膜)を、繰り返し積層した超格子層を用いることができる。

次いで、図47に示すように、イオン注入法によりp型の電流ブロック層(p型のGaN層)CBを形成する。まず、n型のドリフト層(n型のGaN層)DL上のゲート電極GEの形成予定領域にフォトレジスト膜PR61を形成する。次いで、フォトレジスト膜PR61をマスクとして、n型のドリフト層(n型のGaN層)DLの底部に、p型の不純物をイオン注入する。これにより、ゲート電極GEの形成予定領域の両側のn型のドリフト層(n型のGaN層)DLの底部、即ち、n型のドリフト層(n型のGaN層)DLとチャネル層(アンドープのGaN層)CHとの境界部近傍に、p型の電流ブロック層(p型のGaN層)CBが形成される。p型の不純物としては、例えばMg(マグネシウム)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。また、p型の電流ブロック層(p型のGaN層)CBの厚さは、例えば0.5μm程度である。この後、フォトレジスト膜PR61を除去する。次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、p型の電流ブロック層(p型のGaN層)CB中のp型の不純物(ここでは、Mg)を活性化する。この熱処理により、p型の電流ブロック層(p型のGaN層)CB中の正孔濃度は、例えば、2×1018/cm3程度となる。

なお、p型の電流ブロック層(p型のGaN層)CBの形成に際して、比較例2(図16)のp型の電流ブロック層(p型のGaN層)CBをイオン注入法で形成する場合には、電子供給層ES側から、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(2次元電子ガス2DEG)を介して不純物イオンを注入する必要がある。このため、これらの層において不純物イオンの注入による損傷が生じ、上記界面(2次元電子ガス2DEG)でのキャリアの移動度やキャリア濃度が低下する恐れがある。

これに対し、本実施の形態によれば、n型のドリフト層(n型のGaN層)DLから不純物イオンを注入することができるため、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面(2次元電子ガス(2DEG))において不純物イオンの注入による損傷が生じ難い。よって、上記界面(2次元電子ガス(2DEG))でのキャリアの移動度やキャリア濃度を向上させることができる。

次いで、図48に示すように、n型のドリフト層(n型のGaN層)DLの(0001)面上に、接合層ALを形成し、支持基板2Sを搭載する。接合層ALとしては、例えば、Ag(銀)ペーストを用いることができる。また、Ag(銀)ペーストの上下に金属膜(メタライズ)を設けてもよい。例えば、n型のドリフト層(n型のGaN層)DLの(0001)面上に、金属膜として、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜の積層膜(Ti/Al)を形成し、この上部に、Ag(銀)ペーストを形成する。また、支持基板2S上に金属膜として、チタン(Ti)膜と、チタン膜上に形成された白金(Pt)膜と、白金膜上に形成された金(Au)膜との積層膜(Ti/Pt/Au)を形成する。支持基板2Sとしては、シリコン(Si)からなる基板を用いることができる。

次いで、接合層ALであるAg(銀)ペーストと、支持基板2Sの金属膜とを対向させ、n型のドリフト層(n型のGaN層)DLと支持基板2SとをAg(銀)ペースト(接合層AL)を介して融着する。

次いで、犠牲層(GaN層)SLと電子供給層(アンドープのAlGaN層)ESとの界面から犠牲層(GaN層)SLおよび基板1Sを剥離する。剥離方法としては、実施の形態1の場合と同様に、レーザーリフトオフ法を用いることができる。

これにより、電子供給層(アンドープのAlGaN層)ES、チャネル層(アンドープのGaN層)CH、電流ブロック層(p型のGaN層)CB、n型のドリフト層(n型のGaN層)DLが積層され、さらに、この上部に、接合層ALおよび支持基板2Sが積層された積層構造体が形成される。

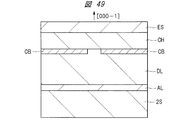

次いで、図49に示すように、上記積層構造体の電子供給層(アンドープのAlGaN層)ES側が上面となるように、上記積層構造体を反転させる。これにより、支持基板2S上に接合層ALを介して上記積層体が配置される。前述したとおり、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの接合面は、Ga面((0001)面)である。そして、この接合面から電子供給層(アンドープのAlGaN層)ES側への方向は、[000−1]方向となる。

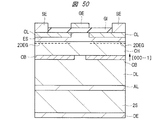

次いで、図50に示すように、イオン注入法によりn型のコンタクト層(n型のAlGaN層)CLを形成する。まず、電子供給層(アンドープのAlGaN層)ESのゲート電極GEの形成予定領域上にフォトレジスト膜(図示せず)を形成する。次いで、このフォトレジスト膜をマスクとして、電子供給層(アンドープのAlGaN層)ESの上層部に、n型の不純物をイオン注入する。これにより、ゲート電極GEの形成予定領域の両側の電子供給層(アンドープのAlGaN層)ESの上層部に、n型のコンタクト層(n型のAlGaN層)CLが形成される。n型の不純物としては、例えばSi(シリコン)が用いられ、その濃度(不純物濃度)は、例えば、1×1019/cm3程度である。また、n型のコンタクト層(n型のAlGaN層)CLの厚さは、例えば30nm程度である。この後、フォトレジスト膜を除去する。次いで、例えば、窒素雰囲気中で、熱処理(アニール)を行い、n型のコンタクト層(n型のAlGaN層)CL中のn型の不純物(ここでは、Si)を活性化する。この熱処理により、n型のコンタクト層(n型のAlGaN層)CL中の電子濃度は、例えば、2×1019/cm3程度となる。

次いで、n型のコンタクト層(n型のAlGaN層)CL上のゲート電極GEの形成予定領域の両側にソース電極SEを形成する。このソース電極SEは、実施の形態1等と同様に、例えば、リフトオフ法を用いて形成することができる。次いで、実施の形態1と同様に、支持基板2Sに対して、熱処理(アロイ処理)を施す。この熱処理により、ソース電極SEと、2次元電子ガス2DEGが形成されているチャネル層(アンドープのGaN層)CHとのオーミック接触を図ることができる。即ち、ソース電極SEが、それぞれ2次元電子ガス2DEGに対して電気的に接続された状態となる。

次いで、ゲート絶縁膜GIを形成した後、ゲート電極GEを形成する。まず、実施の形態2と同様に、ゲート絶縁膜GIを形成する。例えば、ソース電極SE、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のAlGaN層)CL上に、ゲート絶縁膜GIとして、例えば、アルミナ膜を、原子層堆積法を用いて形成する。次いで、ソース電極SE上のゲート絶縁膜GIを除去する。なお、このゲート絶縁膜GIの除去は、ソース電極SE上にコンタクトホールを形成する際に行ってもよい。

次いで、ゲート絶縁膜GI上にゲート電極GEを形成する。ゲート電極GEは、実施の形態2と同様に、例えば、リフトオフ法を用いて形成することができる。

次いで、支持基板2Sの裏面側が上面となるように支持基板2Sを反転し、支持基板2S上にドレイン電極DEを形成する。例えば、支持基板2S上に、金属膜を形成することにより、ドレイン電極DEを形成する。金属膜としては、例えば、チタン(Ti)膜と、チタン膜上に形成されたアルミニウム(Al)膜との積層膜(Ti/Al)を用いることができる。この膜は、例えば、真空蒸着法を用いて形成することができる。

以上の工程により、本実施の形態の半導体装置が略完成する。なお、上記工程においては、ゲート電極GEおよびソース電極SEを、リフトオフ法を用いて形成したが、これらの電極を金属膜のパターニングにより形成してもよい。

このように、本実施の形態の半導体装置においては、[000−1]方向に、チャネル層(アンドープのGaN層)CHと電子供給層(アンドープのAlGaN層)ESとを順に積層した構成としたので、実施の形態1で詳細に説明したように、(1)ノーマリオフ動作と(2)高耐圧化の両立が容易となる。

即ち、本実施の形態の半導体装置の伝導帯エネルギープロファイルは、実施の形態1の場合(図18)と同様である。よって、実施の形態1において詳細に説明したように、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの界面に負電荷(−σ)が生成される。このため、ゲート電圧Vg=0Vの熱平衡状態においては、ゲート電極直下(A−A’部)の2次元電子ガス(チャネル)2DEGが空乏化して、ノーマリオフ動作が可能となる(図18(a)参照)。また、ゲート電圧Vg=閾値電圧(Vt)のオフ状態においては、ゲート絶縁膜GI中の伝導帯のポテンシャルエネルギーが、基板2S側(チャネル層(アンドープのGaN層)CH)からゲート電極GE側に向かって減少する。この電界強度(σ/ε:εはゲート絶縁膜の誘電率)はゲート絶縁膜GIの厚さに依存しないため、ゲート絶縁膜GIを厚くするにしたがって閾値電圧(Vt)が増加することとなる。このように、本実施の形態の半導体装置においては、ノーマリオフ動作と高耐圧化の両立が容易になる。

さらに、ゲート電極直下を除く領域(B−B’部)においては、n型のコンタクト層(n型のAlGaN層)CL中のn型不純物がイオン化し、正電荷が形成され、電子供給層(アンドープのAlGaN層)ESとチャネル層(アンドープのGaN層)CHとの境界に、2次元電子ガス2DEGが生成されてオン抵抗が低減される(図18(b)参照)。

また、本実施の形態においては、溝Tの形成工程を必要としないため、閾値電圧(Vt)の調整が実施の形態1等の場合より容易となる。

また、本実施の形態においては、電流ブロック層(p型のGaN層)CBに開口部(電流狭窄部)を設けたので、効率良くキャリアをドレイン側に導くことができる。また、本実施の形態によれば、電流ブロック層(p型のGaN層)CBや、その開口部(電流狭窄部)も容易に形成することができる。

また、本実施の形態においては、実施の形態4等で説明した埋め込み再成長を用いる必要がなく、より簡易な工程で半導体装置を製造することができる。

(変形例)

図50に示す形態においては、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。

例えば、チャネル層(アンドープのGaN層)CHおよび電子供給層(アンドープのAlGaN層)ESの積層体のうち、チャネル層(アンドープのGaN層)CHの上層部にn型の不純物をイオン注入し、n型のコンタクト層(n型のGaN層)CLを形成してもよい。

また、図50に示す形態においては、電子供給層(アンドープのAlGaN層)ES上にゲート絶縁膜GIを介してゲート電極GEを配置した、いわゆる、MIS型(金属−絶縁膜−半導体型)のゲート電極構成を例示したが、電子供給層(アンドープのAlGaN層)ES上に直接ゲート電極GEを配置した、いわゆる、ショットキー型のゲート電極構成を採用してもよい。

(共通変形例の説明)

本欄においては、上記実施の形態1〜6に共通するその他の変形例について説明する。

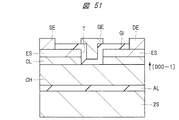

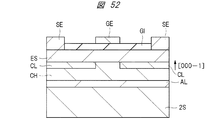

前述したように、上記実施の形態1〜6において、AlGaN層(n型のコンタクト層(n型のAlGaN層)CL、電子供給層(アンドープのAlGaN層)ES)の一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けたが、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。言い換えれば、電子供給層(アンドープのAlGaN層)ESの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けても、チャネル層(アンドープのGaN層)CHの一部にn型不純物層(n型のコンタクト層(n型のAlGaN層)CL)を設けてもよい。図51は、チャネル層の一部にn型不純物層を設けた横型の半導体装置の構成例を示す断面図である。図52は、チャネル層の一部にn型不純物層を設けた縦型の半導体装置の構成例を示す断面図である。なお、上記実施の形態1〜6と共通する部位には同一の符号を付し、その繰り返しの説明を省略する。

例えば、図51に示すように、チャネル層(アンドープのGaN層)CH、n型のコンタクト層(n型のGaN層)CLおよび電子供給層(アンドープのAlGaN層)ESを積層した後、電子供給層(アンドープのAlGaN層)ESおよびn型のコンタクト層(n型のGaN層)CLを除去することにより、溝Tを形成すればよい。

また、図52に示すように、チャネル層(アンドープのGaN層)CHおよび電子供給層(アンドープのAlGaN層)ESの積層体のうち、チャネル層(アンドープのGaN層)CHの上層部にn型の不純物をイオン注入し、n型のコンタクト層(n型のGaN層)CLを形成してもよい。

このように、n型のコンタクト層CLは、電子供給層ESの一部としてその中に形成してもよく、また、チャネル層CHの一部としてその中に形成してもよい。

上記実施の形態1〜6においては、支持基板2Sとして、シリコン(Si)からなる基板を用いたが、この他、炭化シリコン(SiC)からなる基板、サファイア基板またはシリコン(Si)からなる基板などを用いることができる。

また、上記実施の形態1〜6においては、核生成層として、AlN/GaN膜を繰り返し積層した超格子層を用いたが、AlN膜、AlGaN膜やGaN膜などの単層膜を用いてもよい。

また、上記実施の形態1〜6においては、チャネル層CHとして、GaN(GaN層)を用いたが、AlGaN、AlInN、AlGaInN、InGaN、窒化インジウム(InN)などのIII族窒化物半導体を用いてもよい。

また、上記実施の形態1〜6においては、電子供給層ESとして、AlGaN(AlGaN層)を用いたが、チャネル層CHよりバンドギャップが広い(バンドギャップが大きい)他のIII族窒化物半導体を用いてもよい。例えば、AlN、GaN、AlGaInN、InGaNなどを電子供給層として用いることができる。

また、上記実施の形態1〜6においては、電子供給層ESとして、アンドープのIII族窒化物半導体を用いたが、n型のIII族窒化物半導体を用いてもよい。n型の不純物としては、例えばSi(シリコン)を用いることができる。また、アンドープのIII族窒化物半導体とn型のIII族窒化物半導体との積層膜や、アンドープのIII族窒化物半導体とn型のIII族窒化物半導体とアンドープのIII族窒化物半導体との積層膜を、電子供給層として用いてもよい。

また、上記実施の形態1〜6においては、コンタクト層CLとして、AlGaN(AlGaN層)を用いたが、AlN、GaN、AlGaInN、InGaN、InNなどの他のIII族窒化物半導体を用いてもよい。

また、上記実施の形態1〜6においては、電流ブロック層CBとして、GaN(GaN層)を用いたが、AlGaN、AlN、AlGaInN、InGaN、InNなどの他のIII族窒化物半導体を用いてもよい。

また、上記実施の形態3〜6においては、p型の不純物として、Mgを用いたが、この他、亜鉛(Zn)、水素(H)などの他の不純物を用いてもよい。

また、上記実施の形態1〜6においては、ソース電極SEやドレイン電極DEの材料として、Ti/Al膜を用いたが、この他、Ti/Al/Ni/Au膜、Ti/Al/Mo/Au膜、Ti/Al/Nb/Au膜などの他の金属膜を用いてもよい。Moは、モリブデン、Nbは、ニオビウムである。

また、上記実施の形態1〜6においては、ゲート電極GEの材料として、Ni/Au膜を用いたが、この他、Ni/Pd/Au膜、Ni/Pt/Au膜、Ti/Au膜、Ti/Pd/Au膜などの他の金属膜を用いてもよい。Pdは、パラディウム、Ptは、白金である。

また、上記実施の形態1〜6においては、ゲート絶縁膜GIとして、アルミナを用いたが、この他、窒化シリコン(Si3N4)、酸化シリコン(SiO2)などの他の絶縁体を用いてもよい。

また、上記実施の形態1〜6においては、接合層ALとして、HSQや半田などを用いたが、SOG(Spin-on-glass)、SOD(Spin-on-Dielectrics)、ポリイミドなどの塗布系絶縁膜を用いてもよい。また、Sn−Pb、Sn−Sb、Bi−Sn、Sn−Cu、Sn−Inなどの半田、Niペースト、Auペースト、Pdペースト、カーボンペーストなどよりなる導電性接着剤を用いても良い。また、酸化インジウム(In2O3)、酸化錫(SnO2)、酸化亜鉛(ZnO)などの導電性酸化物を用いても良い。Pbは鉛、Sbはアンチモン、Biはビスマス、Cuは銅、Inはインジウムである。

また、上記実施の形態1〜6において説明した断面図には、素子分離を記載していないが、素子(FET)間には、必要に応じて素子分離が設けられる。この素子分離は、例えば、III族窒化物半導体中にNやB(ホウ素)などのイオン注入することにより形成することができる。このイオン注入により、注入領域が高抵抗化し、素子分離として機能する。また、素子形成領域の外周をエッチングする(メサエッチングする)ことにより素子間を分離してもよい。

また、上記実施の形態において示した具体的材料の組成式(例えば、AlGaNなど)において、各元素の組成比は発明の要旨を逸脱しない範囲で適宜設定可能である。

このように、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。