JP2017096998A - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP2017096998A JP2017096998A JP2015225470A JP2015225470A JP2017096998A JP 2017096998 A JP2017096998 A JP 2017096998A JP 2015225470 A JP2015225470 A JP 2015225470A JP 2015225470 A JP2015225470 A JP 2015225470A JP 2017096998 A JP2017096998 A JP 2017096998A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- display device

- region

- connection terminals

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000000758 substrate Substances 0.000 claims abstract description 71

- 239000003990 capacitor Substances 0.000 claims description 29

- 238000004519 manufacturing process Methods 0.000 claims description 27

- 238000002788 crimping Methods 0.000 claims description 17

- 238000000034 method Methods 0.000 claims description 14

- 238000003825 pressing Methods 0.000 claims 3

- 239000010410 layer Substances 0.000 description 65

- 239000010408 film Substances 0.000 description 22

- 239000000463 material Substances 0.000 description 10

- 238000000059 patterning Methods 0.000 description 10

- 239000011347 resin Substances 0.000 description 10

- 229920005989 resin Polymers 0.000 description 10

- 239000004642 Polyimide Substances 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- 239000002184 metal Substances 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 229920001721 polyimide Polymers 0.000 description 8

- 230000037303 wrinkles Effects 0.000 description 8

- 238000003860 storage Methods 0.000 description 7

- 239000011241 protective layer Substances 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 239000011324 bead Substances 0.000 description 5

- 229910003437 indium oxide Inorganic materials 0.000 description 5

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 230000007797 corrosion Effects 0.000 description 4

- 238000005260 corrosion Methods 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- -1 for example Polymers 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

Images

Abstract

Description

[概略構成]

本実施形態に係る表示装置100の概略構成を、図1を参照して説明する。図1は、本実施形態に係る表示装置100の概略構成を示す斜視図である。本実施形態に係る表示装置100は、第1基板102と、第2基板104と、複数の画素108と、シール材110と、半導体装置112と、端子領域114と、接続端子116とを有している。

次いで、本実施形態に係る表示装置100の回路構成について、図2を参照して説明する。図2は、本実施形態に係る表示装置100の回路構成を示す図である。

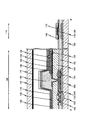

図3を参照し、本実施形態に係る表示装置100の構成について更に詳細に説明する。図3は、本実施形態に係る表示装置100が有する画素108及び接続端子116の構成を示す断面図であり、図1におけるA−A´の断面を示している。

図4〜図10を参照し、本実施形態に係る表示装置100の製造方法について詳細に説明する。図4〜図10は、本実施形態に係る表示装置100の製造方法を説明する断面図であり、図1におけるA−A´において第1基板102(アレイ基板とも呼ぶ。)側の断面を示している。

図11を参照し、第1実施形態に係る表示装置100の変形例について説明する。図11は、本変形例に係る表示装置150が有する接続端子116の構成を示す断面図である。尚、本変形例に係る表示装置150が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

図12を参照し、本実施形態に係る表示装置200の構成について詳細に説明する。図12は、本実施形態に係る表示装置200が有する端子領域114の構成を示す断面図である。尚、本実施形態に係る表示装置200が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

図13を参照し、本実施形態に係る表示装置300の構成について詳細に説明する。図13は、本実施形態に係る表示装置300が有する端子領域114の構成を示す断面図である。尚、本実施形態に係る表示装置300が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

図14を参照し、本実施形態に係る表示装置400の構成について詳細に説明する。図14は、本実施形態に係る表示装置400が有する端子領域114の構成を示す断面図である尚、本実施形態に係る表示装置400が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

図15を参照し、本実施形態に係る表示装置500の構成について詳細に説明する。図15は、本実施形態に係る表示装置500が有する端子領域114の構成を示す断面図である。尚、本実施形態に係る表示装置500が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

図16を参照し、本実施形態に係る表示装置600の構成について詳細に説明する。図16は、本実施形態に係る表示装置600が有する端子領域114の構成を示す断面図である。尚、本実施形態に係る表示装置600が有する画素108の構成については、第1実施形態に係る表示装置100と同様であるため、図示は省略した。

Claims (18)

- 可撓性を有し、各々がトランジスタ及び容量を含む複数の画素が配列された表示領域及び端子領域を有する基板と、

前記端子領域において、複数の接続端子を担う第1電極と、

前記表示領域において、前記複数の画素毎に設けられた容量の一端の電極を担い、前記端子領域において、前記複数の接続端子の各々の上に配置され、前記複数の接続端子の各々と導通する第2電極と、

前記複数の接続端子と前記第2電極とが重畳する領域において、前記第2電極を介して前記複数の接続端子に電気的に接続された外部回路とを備えた表示装置。 - 前記第1電極は、前記表示領域において、複数の前記トランジスタに接続される映像信号線を担うことを特徴とする請求項1に記載の表示装置。

- 前記第2電極は、前記端子領域において、表面に凹凸形状を有し、

前記外部回路と前記複数の接続端子は、異方性導電膜を介して接続されることを特徴とする請求項1に記載の表示装置。 - 前記表示領域において、複数の前記トランジスタ上に配置された平坦化層を担い、前記端子領域において、前記接続端子と前記第2電極との間に配置された絶縁層を更に備えた請求項1に記載の表示装置。

- 前記絶縁層は、前記端子領域において、表面に凹凸形状を有し、

前記外部回路と前記複数の接続端子は、異方性導電膜を介して接続されることを特徴とする請求項4に記載の表示装置。 - 前記表示領域において、前記複数の画素毎に設けられた画素電極を担い、前記端子領域において、前記第2電極の上に配置された第3電極を更に備えた請求項1に記載の表示装置。

- 前記第3電極は、表面に凹凸形状を有し、

前記外部回路と前記複数の接続端子は、異方性導電膜を介して接続されることを特徴とする請求項6に記載の表示装置。 - 前記複数の接続端子の下に、アイランド状に配置された第4電極を更に備えた請求項1に記載の表示装置。

- 前記第4電極は、前記表示領域において、複数の前記トランジスタに接続されるゲート線を担うことを特徴とする請求項8に記載の表示装置。

- 可撓性を有し、各々がトランジスタ及び容量を含む複数の画素が配置される表示領域及び端子領域を有する基板に、

前記端子領域において、複数の接続端子を担う第1電極を形成し、

前記表示領域において、前記複数の画素毎に設けられる容量の一端の電極を担い、前記端子領域において、前記複数の接続端子の各々の上に配置され、前記複数の接続端子の各々と導通する第2電極を形成し、

前記複数の接続端子に外部回路を圧着して電気的に接続することを含む表示装置の製造方法。 - 前記第1電極を形成することは、前記表示領域において、複数の前記トランジスタに接続される映像信号線を同時に形成することである請求項10に記載の表示装置の製造方法。

- 前記第2電極の前記端子領域における表面に凹凸パターンを形成し、

前記外部回路を圧着することは、異方性導電膜を介して圧着することを特徴とする請求項10に記載の表示装置の製造方法。 - 前記接続端子を形成した後、前記第2電極を形成する前に、

前記表示領域において、複数の前記トランジスタ上に配置される平坦化層を担い、前記端子領域において、前記接続端子の上に配置される絶縁層を形成することを更に含む請求項10に記載の表示装置の製造方法。 - 前記絶縁層の前記端子領域における表面に凹凸パターンを形成し、

前記外部回路を圧着することは、異方性導電膜を介して圧着することを特徴とする請求項13に記載の表示装置の製造方法。 - 前記第2電極を形成した後に、前記外部回路を圧着する前に、

前記表示領域において、前記複数の画素毎に設けられる画素電極を担い、前記端子領域において、前記第2電極の上に第3電極を形成することを更に含む請求項10に記載の表示装置の製造方法。 - 前記第3電極の前記端子領域における表面に凹凸パターンを形成し、

前記外部回路を圧着することは、異方性導電膜を介して圧着することを特徴とする請求項15に記載の表示装置の製造方法。 - 前記複数の接続端子を形成する前に、

前記端子領域に、アイランド状に配置された第4電極を形成することを更に含む請求項10に記載の表示装置の製造方法。 - 前記第4電極を形成することは、前記表示領域において、複数の前記トランジスタに接続されるゲート線を同時に形成することである請求項17に記載の表示装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015225470A JP2017096998A (ja) | 2015-11-18 | 2015-11-18 | 表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015225470A JP2017096998A (ja) | 2015-11-18 | 2015-11-18 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017096998A true JP2017096998A (ja) | 2017-06-01 |

| JP2017096998A5 JP2017096998A5 (ja) | 2017-08-17 |

Family

ID=58804774

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015225470A Withdrawn JP2017096998A (ja) | 2015-11-18 | 2015-11-18 | 表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2017096998A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019064592A1 (ja) * | 2017-09-29 | 2019-04-04 | シャープ株式会社 | 表示デバイス、表示デバイスの製造方法、表示デバイスの製造装置 |

| JP2019095694A (ja) * | 2017-11-27 | 2019-06-20 | 株式会社ジャパンディスプレイ | 表示装置 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006222437A (ja) * | 2006-03-03 | 2006-08-24 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2008242249A (ja) * | 2007-03-28 | 2008-10-09 | Kyodo Printing Co Ltd | フレキシブルディスプレイ |

| JP2012068657A (ja) * | 2004-11-30 | 2012-04-05 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2012137728A (ja) * | 2010-12-10 | 2012-07-19 | Asahi Glass Co Ltd | 赤外光透過フィルタ及びこれを用いた撮像装置 |

| WO2013099135A1 (ja) * | 2011-12-28 | 2013-07-04 | パナソニック株式会社 | フレキシブル表示装置 |

| JP2013235275A (ja) * | 2009-09-04 | 2013-11-21 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| JP2014186139A (ja) * | 2013-03-22 | 2014-10-02 | Japan Display Inc | 有機エレクトロルミネッセンス表示装置 |

| US20140291624A1 (en) * | 2013-03-27 | 2014-10-02 | Samsung Display Co., Ltd. | Organic light emitting device display and manufacturing method thereof |

| JP2015072362A (ja) * | 2013-10-03 | 2015-04-16 | 株式会社ジャパンディスプレイ | 表示装置及びその製造方法 |

| JP2015103467A (ja) * | 2013-11-27 | 2015-06-04 | 株式会社ジャパンディスプレイ | 有機el表示装置及びその製造方法 |

-

2015

- 2015-11-18 JP JP2015225470A patent/JP2017096998A/ja not_active Withdrawn

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012068657A (ja) * | 2004-11-30 | 2012-04-05 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2006222437A (ja) * | 2006-03-03 | 2006-08-24 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JP2008242249A (ja) * | 2007-03-28 | 2008-10-09 | Kyodo Printing Co Ltd | フレキシブルディスプレイ |

| JP2013235275A (ja) * | 2009-09-04 | 2013-11-21 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| JP2012137728A (ja) * | 2010-12-10 | 2012-07-19 | Asahi Glass Co Ltd | 赤外光透過フィルタ及びこれを用いた撮像装置 |

| WO2013099135A1 (ja) * | 2011-12-28 | 2013-07-04 | パナソニック株式会社 | フレキシブル表示装置 |

| JP2014186139A (ja) * | 2013-03-22 | 2014-10-02 | Japan Display Inc | 有機エレクトロルミネッセンス表示装置 |

| US20140291624A1 (en) * | 2013-03-27 | 2014-10-02 | Samsung Display Co., Ltd. | Organic light emitting device display and manufacturing method thereof |

| JP2015072362A (ja) * | 2013-10-03 | 2015-04-16 | 株式会社ジャパンディスプレイ | 表示装置及びその製造方法 |

| JP2015103467A (ja) * | 2013-11-27 | 2015-06-04 | 株式会社ジャパンディスプレイ | 有機el表示装置及びその製造方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019064592A1 (ja) * | 2017-09-29 | 2019-04-04 | シャープ株式会社 | 表示デバイス、表示デバイスの製造方法、表示デバイスの製造装置 |

| CN111133496A (zh) * | 2017-09-29 | 2020-05-08 | 夏普株式会社 | 显示设备、显示设备的制造方法、显示设备的制造装置 |

| US10777633B2 (en) | 2017-09-29 | 2020-09-15 | Sharp Kabushiki Kaisha | Display device, display device manufacturing method, and display device manufacturing apparatus |

| JP2019095694A (ja) * | 2017-11-27 | 2019-06-20 | 株式会社ジャパンディスプレイ | 表示装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6756508B2 (ja) | 表示装置 | |

| US9147724B2 (en) | Large area organic light emitting diode display | |

| JP6707118B2 (ja) | 表示装置 | |

| US9525012B2 (en) | Curved display device | |

| JP6211873B2 (ja) | 有機el表示装置及び有機el表示装置の製造方法 | |

| JP6391917B2 (ja) | 発光素子表示装置及びその製造方法 | |

| US9825109B2 (en) | Display device | |

| JP6709274B2 (ja) | 表示装置 | |

| JP2016031499A (ja) | 表示装置 | |

| KR20160058360A (ko) | 협 베젤 구조를 갖는 대면적 유기발광 다이오드 표시장치 | |

| JP6719948B2 (ja) | 表示装置 | |

| JP2019095507A (ja) | 表示装置 | |

| JP2016206393A (ja) | 表示装置及びその製造方法 | |

| JP2017138354A (ja) | 表示装置、および表示装置の作製方法 | |

| JP2017147044A (ja) | 表示装置、および表示装置の作製方法 | |

| US10446637B2 (en) | Display device and method of manufacturing a display device | |

| JP6223070B2 (ja) | 有機el表示装置及び有機el表示装置の製造方法 | |

| JP2011090925A (ja) | 電気光学装置の製造方法 | |

| US8076843B2 (en) | Organic electroluminescence display device | |

| KR102043852B1 (ko) | 유기전계발광 표시장치 | |

| JP2010080344A (ja) | 表示装置 | |

| JP2019020509A (ja) | 表示装置および表示装置の製造方法 | |

| JP2017096998A (ja) | 表示装置 | |

| JP2019003040A (ja) | 表示装置 | |

| JP2012059641A (ja) | 発光パネル及びその製造方法、発光装置、並びに、電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170707 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170707 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180605 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20180903 |