JP2015508233A - 裏面照射型センサを作製するための方法 - Google Patents

裏面照射型センサを作製するための方法 Download PDFInfo

- Publication number

- JP2015508233A JP2015508233A JP2014556595A JP2014556595A JP2015508233A JP 2015508233 A JP2015508233 A JP 2015508233A JP 2014556595 A JP2014556595 A JP 2014556595A JP 2014556595 A JP2014556595 A JP 2014556595A JP 2015508233 A JP2015508233 A JP 2015508233A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor

- flake

- thickness

- doped region

- donor body

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 61

- 239000004065 semiconductor Substances 0.000 claims abstract description 107

- 238000004519 manufacturing process Methods 0.000 claims abstract description 35

- 239000010409 thin film Substances 0.000 claims abstract description 17

- 150000002500 ions Chemical class 0.000 claims description 18

- 239000000758 substrate Substances 0.000 claims description 15

- 238000012545 processing Methods 0.000 claims description 12

- 238000003776 cleavage reaction Methods 0.000 claims description 11

- 238000001465 metallisation Methods 0.000 claims description 10

- 230000007017 scission Effects 0.000 claims description 10

- 238000002513 implantation Methods 0.000 claims description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 5

- 230000000295 complement effect Effects 0.000 claims description 2

- 238000000151 deposition Methods 0.000 claims description 2

- 229910044991 metal oxide Inorganic materials 0.000 claims description 2

- 150000004706 metal oxides Chemical class 0.000 claims description 2

- 230000008878 coupling Effects 0.000 claims 4

- 238000010168 coupling process Methods 0.000 claims 4

- 238000005859 coupling reaction Methods 0.000 claims 4

- 230000008569 process Effects 0.000 abstract description 11

- 235000012431 wafers Nutrition 0.000 description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 12

- 239000002019 doping agent Substances 0.000 description 12

- 229910052710 silicon Inorganic materials 0.000 description 12

- 239000010703 silicon Substances 0.000 description 12

- 239000000463 material Substances 0.000 description 9

- 239000011521 glass Substances 0.000 description 7

- 238000005530 etching Methods 0.000 description 5

- 239000007789 gas Substances 0.000 description 5

- 238000000227 grinding Methods 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- 239000005388 borosilicate glass Substances 0.000 description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- 239000005360 phosphosilicate glass Substances 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000004299 exfoliation Methods 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- -1 BBr 3 Chemical compound 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 2

- RLOWWWKZYUNIDI-UHFFFAOYSA-N phosphinic chloride Chemical compound ClP=O RLOWWWKZYUNIDI-UHFFFAOYSA-N 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000003750 conditioning effect Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- HVMJUDPAXRRVQO-UHFFFAOYSA-N copper indium Chemical compound [Cu].[In] HVMJUDPAXRRVQO-UHFFFAOYSA-N 0.000 description 1

- KUNSUQLRTQLHQQ-UHFFFAOYSA-N copper tin Chemical compound [Cu].[Sn] KUNSUQLRTQLHQQ-UHFFFAOYSA-N 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000280 densification Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- ALKZAGKDWUSJED-UHFFFAOYSA-N dinuclear copper ion Chemical compound [Cu].[Cu] ALKZAGKDWUSJED-UHFFFAOYSA-N 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical class [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- RHZWSUVWRRXEJF-UHFFFAOYSA-N indium tin Chemical compound [In].[Sn] RHZWSUVWRRXEJF-UHFFFAOYSA-N 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14632—Wafer-level processed structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14687—Wafer level processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/08—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors

- H01L31/10—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof in which radiation controls flow of current through the device, e.g. photoresistors characterised by potential barriers, e.g. phototransistors

- H01L31/101—Devices sensitive to infrared, visible or ultraviolet radiation

- H01L31/102—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier

- H01L31/103—Devices sensitive to infrared, visible or ultraviolet radiation characterised by only one potential barrier the potential barrier being of the PN homojunction type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1892—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof methods involving the use of temporary, removable substrates

- H01L31/1896—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof methods involving the use of temporary, removable substrates for thin-film semiconductors

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Electromagnetism (AREA)

- Manufacturing & Machinery (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

Description

この出願は、2012年3月21日に出願され、「裏面照射型センサを作製するための方法(Method for Fabricating Backside-Illuminated Sensors)」という名称を有する米国特許出願番号第13/425,877号への優先権を主張する。米国特許出願番号第13/425,877号は、2012年2月8日に出願され、「裏面照射型センサを作製するための方法(Method for Fabricating Backside-Illuminated Sensors)」という名称を有する米国仮出願番号第61/596,694号への優先権を主張する。これらは両方ともここで、すべての目的のために参照により援用される。この出願はまた、2012年3月21日に出願され、「スーパーストレート・レシーバ要素を有する薄片を含むバックコンタクト型光起電力セル(Back-Contact Photovoltaic Cell Comprising A Thin Lamina Having A Superstrate Receiver Element)」という名称を有する米国特許出願番号第13/425,870号に関係付けられており、すべての目的のために参照により援用される。

イメージセンサは、光を受け取り、受け取られた光の量に基づいてエネルギーを電気信号に変換する。イメージセンサは一般に、シリコン光感応層と、電気信号を処理するための集積チップのような電気回路網とを含む。分解能を向上するようチップ上のピクセル密度を増加させることが望ましい。しかしながら、ピクセル密度が増加すると、クロストークおよび回路の配線の高密度化のような問題が生じる。

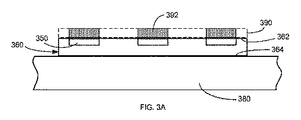

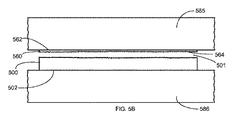

裏面照射型センサを作製するための方法は、第1の導電性を有する薄膜半導体薄片を提供するステップと、薄片内および薄片の表面に第2の導電性を有するドープ領域を形成するステップとを含む。ドープ領域への電気的接続部が形成される。仮キャリアが、半導体の裏面に接触され、その後、取り除かれる。裏面照射型センサが半導体薄片から作製され、作製中に、提供された半導体薄片の厚さが実質的に変化しないままである。

裏面照射型センサは、完成したセンサデバイスについての所望の厚さと実質的に同等の厚さを有する薄片を使用して作製される。いくつかの実施形態では、薄片は、ドープ領域が薄片の表面内および表面に形成される自立薄片として提供され得る。他の実施形態では、ドープ領域は、半導体ドナー体の第1の面に形成され、薄片が当該ドナー体から劈開され、ドープ領域が薄片の表面内および表面に存在する。本願明細書において開示される方法は、スループットの改善および製造コストの減少を可能にする。

Claims (22)

- 裏面照射型センサを作製する方法であって、

表面、裏面、および前記表面と前記裏面との間の厚さを有する薄膜半導体薄片を提供するステップを備え、前記半導体薄片は第1の導電性を有しており、前記方法はさらに、

前記薄片の前記表面において前記半導体薄片内にドープ領域を形成するステップを備え、前記ドープ領域は第2の導電性を有しており、前記方法はさらに、

前記半導体薄片の前記裏面に仮キャリアを接触させるステップと、

前記半導体薄片の表側に前記ドープ領域への電気的接続部を形成するステップと、

前記裏面から前記仮キャリアを取り除くステップと、

前記半導体薄片から裏面照射型センサを作製するステップとを備え、前記半導体薄片の厚さは、前記裏面照射型センサの作製中に実質的に変化しないままである、方法。 - 第1の面を有する半導体ドナー体を提供するステップをさらに備え、前記半導体ドナー体は前記第1の導電性を有しており、前記方法はさらに、

劈開面を規定するように前記半導体ドナー体の前記第1の面にイオンを注入するステップと、

前記劈開面において前記半導体ドナー体を劈開するステップとを備え、前記劈開面は前記半導体薄片の前記裏面を形成し、前記半導体ドナー体の前記第1の面は前記半導体薄片の前記表面を形成する、請求項1に記載の方法。 - 前記イオンを注入するステップ、前記半導体ドナー体を劈開するステップ、および前記ドープ領域を形成するステップのみが摂氏約450度を上回る処理温度を有する、請求項2に記載の方法。

- 前記ドープ領域を形成するステップが、前記イオンを注入するステップに先立って行われる、請求項2に記載の方法。

- 前記イオンを注入するステップは注入エネルギーを含み、

前記注入エネルギーは前記劈開面の深さを決定し、前記深さは、前記半導体ドナー体の前記第1の面から測定され、

前記深さは、前記半導体薄片の厚さと実質的に同等になるように選ばれる、請求項2に記載の方法。 - 前記電気的接続部を形成するステップは、

前記半導体薄片の表側に金属化層を施すステップと、

前記金属化層に集積回路を結合するステップとを含む、請求項1に記載の方法。 - 前記集積回路は相補型金属酸化膜半導体(CMOS)である、請求項6に記載の方法。

- 前記半導体薄片の裏面にカラーフィルタを結合するステップをさらに備える、請求項1に記載の方法。

- 前記薄膜半導体薄片の厚さは約25ミクロン未満である、請求項1に記載の方法。

- 前記薄膜半導体薄片の厚さは、約1ミクロンから約50ミクロンの間である、請求項1に記載の方法。

- 前記半導体薄片の厚さは、前記裏面照射型センサの作製中に、その当初に提供された厚さの20%の偏差内にあるままである、請求項1に記載の方法。

- 裏面照射型センサを作製する方法であって、

第1の面および第1の導電性を有する半導体ドナー体を提供するステップと、

前記第1の面において前記半導体ドナー体内にドープ領域を形成するステップとを備え、前記ドープ領域は第2の導電性を有しており、前記方法はさらに、

劈開面を規定するように前記半導体ドナー体の第1の面にイオンを注入するステップと、

前記劈開面において前記半導体ドナー体から半導体薄片を劈開するステップとを備え、前記劈開面は前記半導体薄片の裏面を形成し、前記半導体ドナー体の第1の面は前記半導体薄片の表面であり、前記表面は前記ドープ領域を含んでおり、前記方法はさらに、

前記半導体薄片の裏面に仮キャリアを接触させるステップと、

前記半導体薄片の表側上に前記ドープ領域への電気的接続部を形成するステップと、

前記裏面から前記仮キャリアを取り除くステップと、

前記半導体薄片から裏面照射型センサを作製するステップとを備え、前記半導体薄片の前記表側と前記裏面との間の厚さは、前記裏面照射型センサの作製中に実質的に変化しないままである、方法。 - 前記電気的接続部を形成するステップは、

前記半導体薄片の表側に金属化層を施すステップと、

前記金属化層に集積回路を結合するステップとを含む、請求項12に記載の方法。 - 前記半導体薄片の裏面にカラーフィルタを結合するステップをさらに含む、請求項12に記載の方法。

- 前記ドープ領域を形成するステップが、前記イオンを注入するステップに先立って行われる、請求項12に記載の方法。

- 前記薄膜半導体薄片の厚さは、約1ミクロンから約50ミクロンの間である、請求項12に記載の方法。

- 前記半導体薄片の厚さは、前記裏面照射型センサの作製中に、その当初に提供された厚さの20%の偏差内にあるままである、請求項12に記載の方法。

- 前記イオンを注入するステップは注入エネルギーを含み、前記注入エネルギーは前記劈開面の深さを決定し、前記深さは、前記半導体ドナー体の第1の面から測定される、請求項12に記載の方法。

- 劈開された前記半導体薄片の厚さは、作製された前記裏面照射型センサにおける半導体基板の所望の最終厚さと実質的に同等である、請求項12に記載の方法。

- 前記ドープ領域を形成するステップ、前記イオンを注入するステップ、および前記半導体ドナー体を劈開するステップのみが摂氏約450度を上回る処理温度を有する、請求項12に記載の方法。

- 前記薄片から裏面照射型センサを作製するステップは、前記薄片の裏面をパッシベートする層を堆積することを含む、請求項12に記載の方法。

- 前記パッシベートする層は、水素化アモルファスシリコンを含む、請求項21に記載の方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201261596694P | 2012-02-08 | 2012-02-08 | |

| US61/596,694 | 2012-02-08 | ||

| US13/425,877 | 2012-03-21 | ||

| US13/425,877 US8871608B2 (en) | 2012-02-08 | 2012-03-21 | Method for fabricating backside-illuminated sensors |

| PCT/US2013/024684 WO2013119513A1 (en) | 2012-02-08 | 2013-02-05 | Method for fabricating backside-illuminated sensors |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015508233A true JP2015508233A (ja) | 2015-03-16 |

| JP2015508233A5 JP2015508233A5 (ja) | 2016-03-10 |

Family

ID=48903240

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014556595A Pending JP2015508233A (ja) | 2012-02-08 | 2013-02-05 | 裏面照射型センサを作製するための方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8871608B2 (ja) |

| EP (1) | EP2812920A4 (ja) |

| JP (1) | JP2015508233A (ja) |

| KR (1) | KR20140135184A (ja) |

| WO (1) | WO2013119513A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020136645A (ja) * | 2019-02-26 | 2020-08-31 | 浜松ホトニクス株式会社 | 光検出装置の製造方法、及び光検出装置 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR3009428B1 (fr) * | 2013-08-05 | 2015-08-07 | Commissariat Energie Atomique | Procede de fabrication d'une structure semi-conductrice avec collage temporaire via des couches metalliques |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009206356A (ja) * | 2008-02-28 | 2009-09-10 | Toshiba Corp | 固体撮像装置およびその製造方法 |

| JP2010219439A (ja) * | 2009-03-18 | 2010-09-30 | Panasonic Corp | 固体撮像装置及びその製造方法 |

| JP2011522421A (ja) * | 2008-05-28 | 2011-07-28 | サーノフ コーポレーション | 極薄シリコン・オン・インシュレータ基板を使用した背面照射型撮像装置 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4162505A (en) | 1978-04-24 | 1979-07-24 | Rca Corporation | Inverted amorphous silicon solar cell utilizing cermet layers |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| US6146979A (en) | 1997-05-12 | 2000-11-14 | Silicon Genesis Corporation | Pressurized microbubble thin film separation process using a reusable substrate |

| JP4450126B2 (ja) | 2000-01-21 | 2010-04-14 | 日新電機株式会社 | シリコン系結晶薄膜の形成方法 |

| JP4220819B2 (ja) * | 2003-03-27 | 2009-02-04 | 浜松ホトニクス株式会社 | 放射線検出器 |

| US7339110B1 (en) | 2003-04-10 | 2008-03-04 | Sunpower Corporation | Solar cell and method of manufacture |

| US7425460B2 (en) | 2004-09-17 | 2008-09-16 | California Institute Of Technology | Method for implementation of back-illuminated CMOS or CCD imagers |

| US7468485B1 (en) | 2005-08-11 | 2008-12-23 | Sunpower Corporation | Back side contact solar cell with doped polysilicon regions |

| US7820475B2 (en) | 2005-12-21 | 2010-10-26 | Sunpower Corporation | Back side contact solar cell structures and fabrication processes |

| US20070169808A1 (en) | 2006-01-26 | 2007-07-26 | Kherani Nazir P | Solar cell |

| US20070277874A1 (en) | 2006-05-31 | 2007-12-06 | David Francis Dawson-Elli | Thin film photovoltaic structure |

| US7928317B2 (en) | 2006-06-05 | 2011-04-19 | Translucent, Inc. | Thin film solar cell |

| US20080070340A1 (en) | 2006-09-14 | 2008-03-20 | Nicholas Francis Borrelli | Image sensor using thin-film SOI |

| US7781715B2 (en) * | 2006-09-20 | 2010-08-24 | Fujifilm Corporation | Backside illuminated imaging device, semiconductor substrate, imaging apparatus and method for manufacturing backside illuminated imaging device |

| US20080092944A1 (en) | 2006-10-16 | 2008-04-24 | Leonid Rubin | Semiconductor structure and process for forming ohmic connections to a semiconductor structure |

| JP5166745B2 (ja) | 2007-03-07 | 2013-03-21 | 信越化学工業株式会社 | 単結晶シリコン太陽電池の製造方法 |

| US8481845B2 (en) | 2008-02-05 | 2013-07-09 | Gtat Corporation | Method to form a photovoltaic cell comprising a thin lamina |

| US8338209B2 (en) | 2008-08-10 | 2012-12-25 | Twin Creeks Technologies, Inc. | Photovoltaic cell comprising a thin lamina having a rear junction and method of making |

| JP4799594B2 (ja) * | 2008-08-19 | 2011-10-26 | 株式会社東芝 | 固体撮像装置およびその製造方法 |

| US20100139755A1 (en) | 2008-12-09 | 2010-06-10 | Twin Creeks Technologies, Inc. | Front connected photovoltaic assembly and associated methods |

| US7964431B2 (en) | 2009-03-19 | 2011-06-21 | Twin Creeks Technologies, Inc. | Method to make electrical contact to a bonded face of a photovoltaic cell |

| JP5482025B2 (ja) * | 2009-08-28 | 2014-04-23 | ソニー株式会社 | 固体撮像装置とその製造方法、及び電子機器 |

-

2012

- 2012-03-21 US US13/425,877 patent/US8871608B2/en not_active Expired - Fee Related

-

2013

- 2013-02-05 KR KR1020147025054A patent/KR20140135184A/ko not_active Application Discontinuation

- 2013-02-05 WO PCT/US2013/024684 patent/WO2013119513A1/en active Application Filing

- 2013-02-05 EP EP13746571.2A patent/EP2812920A4/en not_active Withdrawn

- 2013-02-05 JP JP2014556595A patent/JP2015508233A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009206356A (ja) * | 2008-02-28 | 2009-09-10 | Toshiba Corp | 固体撮像装置およびその製造方法 |

| JP2011522421A (ja) * | 2008-05-28 | 2011-07-28 | サーノフ コーポレーション | 極薄シリコン・オン・インシュレータ基板を使用した背面照射型撮像装置 |

| JP2010219439A (ja) * | 2009-03-18 | 2010-09-30 | Panasonic Corp | 固体撮像装置及びその製造方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020136645A (ja) * | 2019-02-26 | 2020-08-31 | 浜松ホトニクス株式会社 | 光検出装置の製造方法、及び光検出装置 |

| WO2020175483A1 (ja) * | 2019-02-26 | 2020-09-03 | 浜松ホトニクス株式会社 | 光検出装置の製造方法、及び光検出装置 |

| JP7364343B2 (ja) | 2019-02-26 | 2023-10-18 | 浜松ホトニクス株式会社 | 光検出装置の製造方法、及び光検出装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8871608B2 (en) | 2014-10-28 |

| KR20140135184A (ko) | 2014-11-25 |

| WO2013119513A1 (en) | 2013-08-15 |

| US20130203205A1 (en) | 2013-08-08 |

| EP2812920A4 (en) | 2015-10-07 |

| EP2812920A1 (en) | 2014-12-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI601303B (zh) | 薄矽太陽能電池的金屬箔輔助製造 | |

| US7897434B2 (en) | Methods of fabricating solar cell chips | |

| US20110073175A1 (en) | Photovoltaic cell comprising a thin lamina having emitter formed at light-facing and back surfaces | |

| JP2010503991A (ja) | 薄膜soiを用いるイメージセンサ | |

| JP5414298B2 (ja) | 太陽電池の製造方法 | |

| JP2017504950A (ja) | イオン注入を使用した太陽電池エミッタ領域製造 | |

| JP2006516830A (ja) | 改良された光起電電池及びその製造 | |

| US8518724B2 (en) | Method to form a device by constructing a support element on a thin semiconductor lamina | |

| US8101451B1 (en) | Method to form a device including an annealed lamina and having amorphous silicon on opposing faces | |

| TWI538244B (zh) | Method for manufacturing solar cells | |

| TWI656655B (zh) | Solar cell manufacturing method and solar cell obtained by the manufacturing method | |

| TW201532298A (zh) | 使用自對準植入體及覆蓋體之太陽能電池射極區之製備 | |

| JP6207414B2 (ja) | 光起電力素子およびその製造方法 | |

| KR101160116B1 (ko) | 후면 접합 태양전지의 제조방법 | |

| US8921686B2 (en) | Back-contact photovoltaic cell comprising a thin lamina having a superstrate receiver element | |

| US8871608B2 (en) | Method for fabricating backside-illuminated sensors | |

| KR101161807B1 (ko) | 플라즈마 도핑과 확산을 이용한 후면접합 태양전지의 제조방법 및 그 태양전지 | |

| KR100995654B1 (ko) | 태양전지 및 그 제조방법 | |

| CN108022938A (zh) | 一种半导体器件的制造方法 | |

| KR101113486B1 (ko) | 후면접합 태양전지의 제조방법 | |

| KR20110007517A (ko) | 후면접합 구조의 태양전지 | |

| TW201340301A (zh) | 用於製造背側發光感測器之方法 | |

| CN217158212U (zh) | 一种基于锗p-i-n光电二极管的图像传感器 | |

| CN114597226B (zh) | 一种基于锗p-i-n光电二极管的图像传感器的制造方法 | |

| CN217158211U (zh) | 一种基于锗p-i-n光电二极管的图像传感器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160122 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160122 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161220 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170725 |