JP2015011663A - マルチコアプロセッサ、画像形成装置およびプログラム - Google Patents

マルチコアプロセッサ、画像形成装置およびプログラム Download PDFInfo

- Publication number

- JP2015011663A JP2015011663A JP2013138937A JP2013138937A JP2015011663A JP 2015011663 A JP2015011663 A JP 2015011663A JP 2013138937 A JP2013138937 A JP 2013138937A JP 2013138937 A JP2013138937 A JP 2013138937A JP 2015011663 A JP2015011663 A JP 2015011663A

- Authority

- JP

- Japan

- Prior art keywords

- processor

- core

- processing

- processor core

- image forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 claims description 53

- 230000008569 process Effects 0.000 claims description 46

- 230000015572 biosynthetic process Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 18

- 230000004048 modification Effects 0.000 description 14

- 238000012986 modification Methods 0.000 description 14

- 230000006870 function Effects 0.000 description 13

- 230000007704 transition Effects 0.000 description 4

- 238000004891 communication Methods 0.000 description 3

- 230000000052 comparative effect Effects 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

Images

Landscapes

- Facsimiles In General (AREA)

- Accessory Devices And Overall Control Thereof (AREA)

Abstract

Description

請求項2に係る発明によれば、装置にインストールされているソフトウェアの複雑度が高いほど第1のプロセッサコアによる処理に切り替わる確立が高くなるように閾値が決定された場合に比べて、第1のプロセッサコアによる処理と第2のプロセッサコアによる処理とを切り替える処理の発生が抑制される。

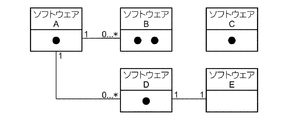

請求項3に係る発明によれば、装置にインストールされているソフトウェアの数に応じて閾値が決定される。

請求項4に係る発明によれば、装置にインストールされている複数のソフトウェアが互いに関連する度合いに応じて閾値が決定される。

請求項5に係る発明によれば、装置に組み込まれている電子機器の構成に応じて閾値が決定されない場合に比べて、第1のプロセッサコアによる処理と第2のプロセッサコアによる処理とを切り替える処理の発生が抑制される。

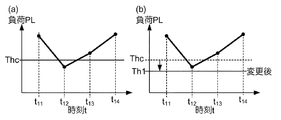

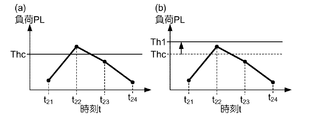

請求項6に係る発明によれば、負荷の大きさが閾値以上になると第1のプロセッサコアによる処理に切り替え、かつ負荷の大きさが閾値を下回ると第2のプロセッサコアによる処理に切り替えた場合に比べて、マルチコアプロセッサの処理効率を向上させることができる。

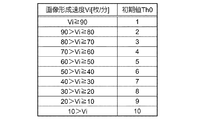

請求項8に係る発明によれば、画像形成部が画像を形成する速度が速いほど第1のプロセッサコアによる処理に切り替わる確率が高くなるように閾値が決定された場合に比べて、第1のプロセッサコアによる処理と第2のプロセッサコアによる処理とを切り替える処理の発生が抑制される。

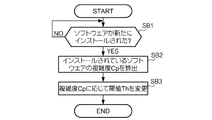

プロセッサ101が閾値Thを変更する処理は、画像形成装置1の電源が投入されたことを契機として行われる場合に限らない。閾値Thを変更する処理は、例えば、新たなソフトウェアが画像形成装置1にインストールされた場合に行われてもよい。

ステップSA1において特定される画像形成装置1のハードウェア構成は、画像形成速度Viに限らない。例えば、画像形成装置1に決められた処理を実行させるために画像形成装置1に組み込まれている電子機器の構成が、画像形成装置1のハードウェア構成として特定されてもよい。具体例としては、画像形成装置1の機能を拡張するためのいわゆる拡張ボード(例えば、パラレルインタフェースボード、無線LAN(Local Area Network)ボード、イーサネット(登録商標)ボード、画像データ変換ボードなど)が画像形成装置1のハードウェア構成として特定されてもよい。この場合、ステップSA2において、画像形成装置1に拡張ボードが組み込まれている場合には、プロセッサコア101Bに切り替わる確立が高くなるように初期値Th0が決定されてもよい。また、画像形成装置1に組み込まれた拡張ボードの数が多いほど、プロセッサコア101Bに切り替わる確立が高くなるように初期値Th0が決定されてもよい。別の具体例として、画像形成装置1の原稿読み取り部に対して原稿を送る原稿送り装置が画像形成装置1のハードウェア構成として特定されてもよい。この場合、ステップSA2において、画像形成装置1が原稿送り装置を備えている場合には、プロセッサコア101Bに切り替わる確立が高くなるように初期値Th0が決定されてもよい。

プロセッサ101が閾値Thを決定する処理は、図3に示した処理に限定されない。例えば、プロセッサ101は、過去(図3に示した処理が開始される前)にプリント機能が実行されたファイルのサイズ、当該ファイルに含まれているイラストまたは図表などのオブジェクトの数、および当該ファイルの圧縮形式などに基づいてプロセッサ101に将来与えられる処理の負荷の大きさを予測し、予測された負荷の大きさが大きいほどプロセッサコア101Bに切り替わる確立が高くなるように閾値Thを変更してもよい。

関連度Lsが算出される方法は、実施形態に記載された方法に限らない。例えば、あるソフトウェアに基づいて複数のサービスが起動される場合には、起動されているサービスの数に応じて関連度Lsが算出されてもよい。この場合、プロセッサ101は、ステップSA3の処理の前に、画像形成装置1にインストールされているソフトウェアの各々について、起動されているサービスの数を特定する。

複雑度Cpは、画像形成装置1にインストールされているソフトウェアの数に応じて算出されてもよい。この場合、プロセッサ101は、インストールされているソフトウェアの数が多いほど複雑度Cpが高くなるように、複雑度Cpを算出する。さらに別の例で、複雑度Cpは、関連度Lfおよび関連度Lsのいずれか一方に応じて算出されてもよい。この場合、関連度データには、関連度Lfおよび関連度Lsのいずれか一方が示されていてもよい。

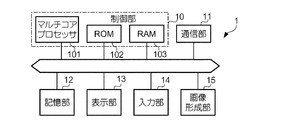

画像形成装置1およびプロセッサ101のハードウェア構成は、図1および図2に示した構成に限らない。図3に示した各ステップの処理が実行されれば、画像形成装置1またはプロセッサ101はどのようなハードウェア構成であってもよい。例えば、プロセッサ101は、デュアルコアプロセッサに限らない。プロセッサ101は、3つ以上のプロセッサコアを有するマルチコアプロセッサ(例えば、トリプルコアプロセッサ、またはクアッドコアプロセッサなど)であってもよい。また、プロセッサ101の機能的構成は、図2に示した構成に限らない。例えば、決定手段1011は、プロセッサコア101Aおよびプロセッサコア101Bのいずれか一方が有していてもよい。この場合、閾値Thを決定する処理は、決定手段1011を有するプロセッサ101により行われる。

実施形態において、プロセッサ101によって実行されるプログラムは、磁気記録媒体(磁気テープ、磁気ディスク(HDD、FD(Flexible Disk))など)、光記録媒体(光ディスク(CD(Compact Disk)、DVD(Digital Versatile Disk))など)、光磁気記録媒体、半導体メモリ(フラッシュROMなど)などのコンピュータが読み取り可能な記録媒体に記憶した状態で提供されてもよい。また、このプログラムは、インターネットなどのネットワーク経由でダウンロードされてもよい。

実施形態に示した閾値Thおよび範囲はあくまで一例であり、閾値Thはいかなる値または範囲で用いられてもよい。

Claims (9)

- マルチコアプロセッサであって、

第1のプロセッサコアと、

前記第1のプロセッサコアよりも消費電力および処理能力が高い第2のプロセッサコアと、

当該マルチコアプロセッサを含む装置のハードウェア構成またはソフトウェア構成に応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とが切り替わる負荷の大きさの閾値を決定する決定手段と、

与えられた処理の負荷の大きさと前記閾値とに応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とを切り替える切替手段と

を有するマルチコアプロセッサ。 - 前記決定手段は、前記装置にインストールされているソフトウェアの複雑度が高いほど前記第2のプロセッサコアによる処理に切り替わる確率が高くなるように、前記閾値を決定する

ことを特徴とする請求項1に記載のマルチコアプロセッサ。 - 前記複雑度は、前記装置にインストールされているソフトウェアの数に応じて決まる

ことを特徴とする請求項2に記載のマルチコアプロセッサ。 - 前記複雑度は、複数の前記ソフトウェアが互いに関連する度合いに応じて決まる

ことを特徴とする請求項2または3に記載のマルチコアプロセッサ。 - 前記決定手段は、前記装置に決められた処理を実行させるために前記装置に組み込まれている電子機器の構成に応じて前記閾値を決定する

ことを特徴とする請求項1ないし4のいずれか1項に記載のマルチコアプロセッサ。 - 前記切替手段は、

与えられた処理の負荷の大きさが閾値以上になると、前記第1のプロセッサコアによる処理を前記第2のプロセッサコアによる処理に切り替え、

与えられた処理の負荷の大きさが閾値を下回ると、前記第2のプロセッサコアによる処理を前記第1のプロセッサコアによる処理に切り替える

ことを特徴とする請求項1ないし5のいずれか1項に記載のマルチコアプロセッサ。 - 画像を処理するマルチコアプロセッサと、

前記マルチコアプロセッサにより処理された画像を記録媒体に形成する画像形成部と

を有し、

前記マルチコアプロセッサは、

第1のプロセッサコアと、

前記第1のプロセッサコアよりも消費電力および処理能力が高い第2のプロセッサコアと、

自機のハードウェア構成またはソフトウェア構成に応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とが切り替わる負荷の大きさの閾値を決定する決定手段と、

与えられた処理の負荷の大きさと前記閾値とに応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とを切り替える切替手段と

を有する画像形成装置。 - 前記決定手段は、前記画像形成部が画像を形成する速度が速いほど前記第2のプロセッサコアによる処理に切り替わる確率が高くなるように、前記閾値を決定する

ことを特徴とする請求項7に記載の画像形成装置。 - 第1のプロセッサコアと、前記第1のプロセッサコアよりも消費電力および処理能力が高い第2のプロセッサコアとを有するマルチコアプロセッサに、

当該マルチコアプロセッサを含む装置のハードウェア構成またはソフトウェア構成に応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とが切り替わる負荷の大きさの閾値を決定するステップと、

与えられた処理の負荷の大きさと前記閾値とに応じて、前記第1のプロセッサコアによる処理と前記第2のプロセッサコアによる処理とを切り替えるステップと

を実行させるためのプログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013138937A JP6056683B2 (ja) | 2013-07-02 | 2013-07-02 | マルチコアプロセッサ、画像形成装置およびプログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013138937A JP6056683B2 (ja) | 2013-07-02 | 2013-07-02 | マルチコアプロセッサ、画像形成装置およびプログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015011663A true JP2015011663A (ja) | 2015-01-19 |

| JP6056683B2 JP6056683B2 (ja) | 2017-01-11 |

Family

ID=52304729

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013138937A Expired - Fee Related JP6056683B2 (ja) | 2013-07-02 | 2013-07-02 | マルチコアプロセッサ、画像形成装置およびプログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6056683B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101797845B1 (ko) * | 2016-02-16 | 2017-11-14 | 가천대학교 산학협력단 | 멀티코어 컴퓨팅 시스템에서 병렬 비디오 처리 장치 및 방법 |

| KR20180035087A (ko) * | 2016-09-28 | 2018-04-05 | 가천대학교 산학협력단 | 멀티코어 시스템을 이용한 병렬 비디오 처리 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04215168A (ja) * | 1990-12-13 | 1992-08-05 | Nec Corp | コンピュータシステム |

| JP2006178698A (ja) * | 2004-12-22 | 2006-07-06 | Hitachi Ltd | 負荷状態監視装置および負荷状態監視方法 |

-

2013

- 2013-07-02 JP JP2013138937A patent/JP6056683B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04215168A (ja) * | 1990-12-13 | 1992-08-05 | Nec Corp | コンピュータシステム |

| JP2006178698A (ja) * | 2004-12-22 | 2006-07-06 | Hitachi Ltd | 負荷状態監視装置および負荷状態監視方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101797845B1 (ko) * | 2016-02-16 | 2017-11-14 | 가천대학교 산학협력단 | 멀티코어 컴퓨팅 시스템에서 병렬 비디오 처리 장치 및 방법 |

| US10701378B2 (en) | 2016-02-16 | 2020-06-30 | Gachon University Of Industry—Academic Cooperation Foundation | Parallel video processing apparatus using multicore system and method thereof |

| KR20180035087A (ko) * | 2016-09-28 | 2018-04-05 | 가천대학교 산학협력단 | 멀티코어 시스템을 이용한 병렬 비디오 처리 |

| KR101925681B1 (ko) * | 2016-09-28 | 2018-12-05 | 가천대학교 산학협력단 | 멀티코어 시스템을 이용한 병렬 비디오 처리 |

| US10534650B2 (en) | 2016-09-28 | 2020-01-14 | Gachon University Of Industry-Academic Cooperation Foundation | Parallel video processing using multicore system |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6056683B2 (ja) | 2017-01-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6056683B2 (ja) | マルチコアプロセッサ、画像形成装置およびプログラム | |

| US10726179B1 (en) | Circuit design supporting method and storage medium | |

| JP2009026199A (ja) | クロック周波数制御方法及びコンピュータプログラム | |

| JP2012234458A (ja) | 画像処理装置、画像処理装置の制御方法及びプログラム | |

| JP6056433B2 (ja) | 画像処理装置 | |

| JP6119498B2 (ja) | マルチコアプロセッサ、画像形成装置およびプログラム | |

| JP2011193302A (ja) | マーカ配置装置、マーカ検出装置、及びプログラム | |

| US10356256B2 (en) | Communication apparatus, control method for communication apparatus, and storage medium for changing a version of an encryption communication protocol used for communication | |

| JP7505337B2 (ja) | 情報処理装置 | |

| WO2019150662A1 (ja) | 処理装置、処理方法及びプログラム | |

| US20110063674A1 (en) | Information processing apparatus and computer-readable medium including computer program | |

| JP2013043294A (ja) | 印刷装置、印刷方法、コンピュータプログラムおよび記録媒体 | |

| US20240388669A1 (en) | Management apparatus, control method for management apparatus, and storage medium | |

| JP2010103733A (ja) | 色変換テーブル生成装置、色変換テーブル、画像処理装置 | |

| JP7604834B2 (ja) | 画像形成装置、管理システム、画像形成装置の管理方法、及びプログラム | |

| JP2020188421A (ja) | 情報処理装置、情報処理システム、プログラム、及び情報処理方法 | |

| CN112101464B (zh) | 基于深度学习的影像样本数据的获取方法和装置 | |

| JP7660475B2 (ja) | 表示装置、画像処理装置、及び表示方法 | |

| JP7524604B2 (ja) | 情報処理装置、システム、方法、およびプログラム | |

| JP6169026B2 (ja) | 電子機器および表示制御プログラム | |

| JP2012175490A (ja) | 画像形成装置 | |

| JP2011048590A (ja) | 画像形成装置 | |

| JP2009134413A (ja) | 画像処理システム及び画像処理プログラム | |

| JP7156088B2 (ja) | 通信機器、ログ転送方法及び通信システム | |

| JP6569242B2 (ja) | 画像処理装置、画像処理システム及び画像処理プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161012 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161108 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161121 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6056683 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |