JP2014123701A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2014123701A JP2014123701A JP2013073507A JP2013073507A JP2014123701A JP 2014123701 A JP2014123701 A JP 2014123701A JP 2013073507 A JP2013073507 A JP 2013073507A JP 2013073507 A JP2013073507 A JP 2013073507A JP 2014123701 A JP2014123701 A JP 2014123701A

- Authority

- JP

- Japan

- Prior art keywords

- inner lead

- circuit board

- semiconductor device

- heat dissipation

- frame tab

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/45124—Aluminium (Al) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45147—Copper (Cu) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48095—Kinked

- H01L2224/48096—Kinked the kinked part being in proximity to the bonding area on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

- H01L2224/48139—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate with an intermediate bond, e.g. continuous wire daisy chain

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48472—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area also being a wedge bond, i.e. wedge-to-wedge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/4901—Structure

- H01L2224/4903—Connectors having different sizes, e.g. different diameters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

Landscapes

- Lead Frames For Integrated Circuits (AREA)

- Wire Bonding (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

【課題】装置の小型化を図りつつインナーリードにワイヤボンディングを良好に行うことができる構成の半導体装置を提供することを課題とする。

【解決手段】半導体装置は、インナーリード26iを放熱回路基板20上に有する。インナーリード26iは、ワイヤボンディングされるワイヤW1の被接続部となるインナーリードポスト26p1、26p2を有している。インナーリードポスト26p1、26p2は、矩形状であって長手方向が放熱回路基板20の長手方向に沿っている。

【選択図】図1

【解決手段】半導体装置は、インナーリード26iを放熱回路基板20上に有する。インナーリード26iは、ワイヤボンディングされるワイヤW1の被接続部となるインナーリードポスト26p1、26p2を有している。インナーリードポスト26p1、26p2は、矩形状であって長手方向が放熱回路基板20の長手方向に沿っている。

【選択図】図1

Description

本発明は、ワイヤボンディングを行った半導体装置に関する。

近年、市場における電子機器の小型化要求はますます高まっている。その反面、相対的に発熱が多い半導体素子(発熱素子)を有する発熱回路を電源装置に組み込むことも要望されている(例えば、特許文献1参照)。

ところで、電子機器に搭載されている半導体素子などの電子部品には、アウターリードに連続しているインナーリードに、ワイヤをワイヤボンディングで接続していることが多い。この接続を行う際、通常、アウターリードの例えば両端部を押さえることで、ワイヤボンディング時にインナーリードの移動を抑止している。

しかし、ワイヤボンディング時にアウターリードを充分に押さえることができず、この結果、インナーリードの移動を充分に抑止できないという不具合が発生することがあった。電子機器の小型化に伴ってアウターリードの幅を小さくすると、この問題は更に顕著となる。

本発明は上記課題に鑑みてなされたものであり、装置の小型化を図りつつインナーリードにワイヤボンディングを良好に行うことができる構成の半導体装置を提供することを課題とする。

上記課題を解決するために、本発明に係る半導体装置は、インナーリードを放熱回路基板上に有する半導体装置であって、前記インナーリードは、ボンディングワイヤの被接続部となるインナーリードポストを有しており、前記インナーリードポストは、矩形状であって長手方向が前記放熱回路基板の長手方向に沿っていることを特徴とする。

本発明によれば、装置の小型化を図りつつインナーリードにワイヤボンディングを良好に行うことができる構成の半導体装置が実現される。

以下、添付図面を参照して、本発明の実施の形態について説明する。以下の説明では、すでに説明したものと同一または類似の構成要素には同一または類似の符号を付し、その詳細な説明を適宜省略している。

また、図面は模式的なものであり、寸法比などは現実のものとは異なることに留意すべきである。従って、具体的な寸法比などは以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

また、以下に示す実施の形態は、この発明の技術的思想を具体化するための例示であって、この発明の実施の形態は、構成部品の材質、形状、構造、配置等を下記のものに特定するものではない。この発明の実施の形態は、要旨を逸脱しない範囲内で種々変更して実施できる。

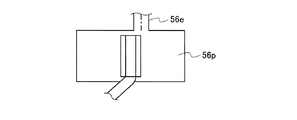

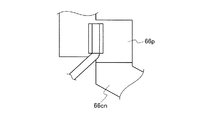

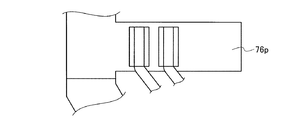

図1(a)および(b)は、それぞれ、本発明の一実施形態の半導体装置で、内部構造を説明する平面図および側面図である。図2〜図4は、何れも、本発明の一実施形態の半導体装置の変形例を示す部分拡大平面図である。

図1に示すように、半導体装置10は、放熱性の回路基板である放熱回路基板20と、放熱回路基板20に搭載された第1の発熱素子22、第2の発熱素子24、リードフレーム26および感温素子(例えばサーミスタ)28と、を備えている。

第1の発熱素子22と第2の発熱素子24は、封止樹脂34の短手方向の略中央部に配置されている。また第1の発熱素子22は第2の発熱素子24よりも相対的に発熱が多い。

半導体装置10は、放熱回路基板20の裏面が露出するように、これらを封止する封止樹脂34を備えている。

放熱回路基板(放熱板)20は、金属ベース回路基板やセラミックベース回路基板であることが多い。また、放熱回路基板20上の銅パターン部分(図示せず)と、第2の発熱素子24を搭載したリードフレーム26の裏面とが、導電性接着剤(例えばはんだ)を介して接着され、放熱回路基板20の裏面は、封止樹脂(封止体)34から露出している。

(フレームタブ)

リードフレーム26は複数のフレームタブを有している。すなわち、リードフレーム26は、第1の発熱素子22を搭載する第1フレームタブ40と、第1の発熱素子22および第2の発熱素子24を搭載する第2フレームタブ42と、第2の発熱素子24を搭載する第3フレームタブ43とを有する。そして第2フレームタブ42には、第1の発熱素子22と第2の発熱素子24との間のフレームタブ部分42mに、フレームタブ部分42mを貫通する透孔46が形成されている。また、隣り合う第2の発熱素子24同士の間にも透孔46が形成されている。

リードフレーム26は複数のフレームタブを有している。すなわち、リードフレーム26は、第1の発熱素子22を搭載する第1フレームタブ40と、第1の発熱素子22および第2の発熱素子24を搭載する第2フレームタブ42と、第2の発熱素子24を搭載する第3フレームタブ43とを有する。そして第2フレームタブ42には、第1の発熱素子22と第2の発熱素子24との間のフレームタブ部分42mに、フレームタブ部分42mを貫通する透孔46が形成されている。また、隣り合う第2の発熱素子24同士の間にも透孔46が形成されている。

本実施形態では、リードフレーム26は銅製であり、均一な厚さの平条フレームである。従ってフレームタブ(第1フレームタブ40、第2フレームタブ42、および、第3フレームタブ43)は銅からなる。フレームタブが導電性接着剤(例えばはんだ)で付けられる放熱回路基板20上の銅パターン部分(図示せず)のサイズは、フレームタブと接する部分に比べ、同じか或いはやや小さくされている。

また、第1フレームタブ40における第1の発熱素子22の1つあたりの面積は、第2フレームタブ42における第2の発熱素子24の1つあたりの面積に比べて大きい。具体的には、第1フレームタブ40の熱抵抗が、第2フレームタブ42の熱抵抗よりも小さくなるように、第1フレームタブ40の第1の発熱素子1つあたりの面積を、第2フレームタブ42の第2の発熱素子1つあたりの面積に比べて例えば1.5倍以上大きくすることにより、第1の発熱素子22からの熱を効率良く放熱できる構造になっている。なお、第1の発熱素子22の熱抵抗は1.7W/℃、第2の発熱素子24の熱抵抗は3W/℃である。

(インナーリード)

リードフレーム26を構成するインナーリード26iはアウターリード26eに連続している。インナーリード26iのうち、第2フレームタブ42に接続するインナーリード以外では、インナーリードポスト26p1、26p2のいずれかを有する。インナーリードポスト26p1、26p2は平面視矩形状であり、その長手方向が、放熱回路基板20の長手方向に沿うように配置されている。インナーリードポスト26p1の長手方向略中央部には、第2の発熱素子24と電気接続するためのワイヤ(ボンディングワイヤ)W1が接続されている。そして、インナーリードポスト26p2の長手方向略中央部には、第1の発熱素子22と電気接続するためのワイヤ(ボンディングワイヤ)W2、W3が接続されている。なお、ワイヤの材質には例えばアルミニウムまたはアルミニウム合金、あるいは金または金合金、あるいは銅または銅合金を用いる。

リードフレーム26を構成するインナーリード26iはアウターリード26eに連続している。インナーリード26iのうち、第2フレームタブ42に接続するインナーリード以外では、インナーリードポスト26p1、26p2のいずれかを有する。インナーリードポスト26p1、26p2は平面視矩形状であり、その長手方向が、放熱回路基板20の長手方向に沿うように配置されている。インナーリードポスト26p1の長手方向略中央部には、第2の発熱素子24と電気接続するためのワイヤ(ボンディングワイヤ)W1が接続されている。そして、インナーリードポスト26p2の長手方向略中央部には、第1の発熱素子22と電気接続するためのワイヤ(ボンディングワイヤ)W2、W3が接続されている。なお、ワイヤの材質には例えばアルミニウムまたはアルミニウム合金、あるいは金または金合金、あるいは銅または銅合金を用いる。

また、本実施形態では、第2フレームタブ42には1つの第1の発熱素子22と複数(図1では3つ)の第2の発熱素子24とが配置されており、第3フレームタブ43には1つの第2の発熱素子24が配置されている。このため、第2フレームタブ42に供給する電力は第3フレームタブに供給する電力に比べて大きい。本実施形態ではこれを考慮して、アウターリード26eと第2フレームタブ42とに接続するインナーリード本体26mの横幅が、インナーリードポスト26p1と第3フレームタブ43とに接続するインナーリード接続部26cnに比べて幅広にされている。

また、本実施形態では、図1から判るように、第3フレームタブ43に接続するインナーリード接続部26cnと、第2の発熱素子24に接続されるワイヤW1とは、平面視で互い違いに交差している。

(封止樹脂)

本実施形態では、封止樹脂34は、放熱回路基板20と対向する側の長手方向、すなわち放熱回路基板20に接する側が放熱回路基板20に対して確実に凸形状となるように(すなわち封止樹脂34の表面側が凹形状となるように)、封止樹脂34の線膨張率、封止樹脂34の厚み、放熱回路基板20の厚みなどが考慮されている。

本実施形態では、封止樹脂34は、放熱回路基板20と対向する側の長手方向、すなわち放熱回路基板20に接する側が放熱回路基板20に対して確実に凸形状となるように(すなわち封止樹脂34の表面側が凹形状となるように)、封止樹脂34の線膨張率、封止樹脂34の厚み、放熱回路基板20の厚みなどが考慮されている。

また、封止樹脂34の裏面に切欠部34dを形成することで沿面距離を確保しており、これにより、電気絶縁性が向上している。

また、封止樹脂34の長手方向両端部には、ビス止めのネジが入り込む切欠部34sが形成されている。そして、平面視の投影面上で、ビス止めのネジの頭部Hが、第1の発熱素子22、更にはリードフレーム26に重ならないように、切欠部34s、リードフレーム26などの寸法、位置が決められている。

(アウターリード)

また、本実施形態では、インナーリード26iに連続するアウターリード26eは、放熱回路基板20の外周から内側で曲げて、放熱回路基板20の裏面から離す必要があり、放熱回路基板20とは高さを異ならせている。

また、本実施形態では、インナーリード26iに連続するアウターリード26eは、放熱回路基板20の外周から内側で曲げて、放熱回路基板20の裏面から離す必要があり、放熱回路基板20とは高さを異ならせている。

本実施形態では、アウターリード26eは放熱回路基板20に繋がる部位がデプレスされていることで、このようにアウターリード26eの端部(樹脂封止体側面から導出されたアウターリードの端面)と放熱回路基板20との高さが異なっている。

また、本実施形態では、デプレスの位置は、放熱回路基板20を中央にして、左右同じであるが、異なっていてもよい。

なお、デプレスの形態としては、例えば図1(b)に示すように、高さ方向に対して側面視で直線状に傾斜する直線傾斜部26es、26etを形成してもよく、デプレスの形態は特に限定しない。

(感温素子)

感温素子28は半導体素子を有するものであり、過熱保護用に放熱回路基板20上に載置され、検知能力が向上している。すなわち、図1に示すように、感温素子28は、放熱回路基板20に形成されている電極21k、21jに接続され、放熱回路基板20上に直接に載置されているので、フレームタブを介して感温素子を配置した場合に比べ、放熱回路基板20の温度を高い検出精度で検出をすることができる構成になっている。

感温素子28は半導体素子を有するものであり、過熱保護用に放熱回路基板20上に載置され、検知能力が向上している。すなわち、図1に示すように、感温素子28は、放熱回路基板20に形成されている電極21k、21jに接続され、放熱回路基板20上に直接に載置されているので、フレームタブを介して感温素子を配置した場合に比べ、放熱回路基板20の温度を高い検出精度で検出をすることができる構成になっている。

また感温素子28は、発熱素子と同様に封止樹脂34の短手方向の略中央部に配置され、また隣り合う第3フレームタブ43同士の間隔と同一の間隔で、第2の発熱素子24の横並びに配置されている。

また、感温素子28は、長矩形の外形を有し、感温素子28の長手方向が半導体装置10の長手方向と垂直になるよう配置しており、歪による特性変動を防止している。

また、本実施形態では、感温素子28に接続される放熱回路基板20の電極面積(一方の電極21jおよび他方の電極21kの合計の面積)が、感温素子28の平面視面積よりも広い。

(作用、効果)

以下、本実施形態の作用、効果について説明する。

以下、本実施形態の作用、効果について説明する。

本実施形態では、感温素子28が放熱回路基板20上に直接に載置されている。従って、支持板などの介在物を経由して感温素子を配置した従来例に比べ、放熱回路基板20の温度を高い検出精度で温度検出をすることができ、充分な過熱対策保護を図ることができる。

また、本実施形態では、感温素子28に接続される放熱回路基板20の電極面積(一方の電極21jおよび他方の電極21kの合計の面積)が、感温素子28の平面視面積は、従来に比べて遥かに広い。従って、放熱回路基板20の熱が感温素子28に伝わる速度は、従来に比べて遥かに速く、放熱回路基板20の温度をより迅速に正確に検出することができる。

また感温素子28は、発熱素子と同様に封止樹脂34の短手方向の略中央部に配置されている。そして、感温素子28は、隣り合う第3フレームタブ43の間隔と同一の間隔で第2の発熱素子24の横並びの位置に配置されており、このように感温素子28が第2の発熱素子24に隣接することで、更に検出精度を向上させることができる構成になっている。

また、感温素子28は、長矩形の外形を有し、感温素子28の長手方向が半導体装置10の長手方向と垂直になるよう配置しており、歪による特性変動を防止している。すなわち、温度変化などにより封止樹脂34に反りが生じた場合、仮に感温素子28の長手方向が半導体装置10の長手方向と平行であると、感温素子28に生じる反りが最大となるが、本実施形態では、封止樹脂34の反りによって感温素子28に生じる反りが最小となるように感温素子28の向きが設定されている。

また、インナーリードポスト26p1と第2の発熱素子24が載置される第3フレームタブ43とに連続するインナーリード接続部26cnと、インナーリードポスト26p1と第2の発熱素子24とに接続するワイヤ(ボンディングワイヤ)W1とは、平面視で交差した、いわゆるクロス配線となっており、しかも、互い違いにクロスしている。これにより、接続に必要な領域を狭くすることができ、半導体装置10の小型化に大きく役立っている。また、小型化のために、アウターリードのピッチが狭い場合でも、接続に必要な領域を狭くすることができ、狭ピッチに対応することが可能である。

また、インナーリード接続部26cnの幅を広くすることにより、放熱性の向上が期待できる。

また、インナーリード接続部26cnの厚さを厚くして放熱性の向上が期待できる。

また、インナーリード接続部26cnの幅を広くしたり、あるいは厚さを厚くしたりすることでインナーリード接続部26cnの機械的強度が向上し、変形を防止する効果が期待できる。

また、インナーリード26iに形成されたインナーリードポスト26p1、26p2は、平面視矩形状であって、その長手方向が、放熱回路基板20の長手方向と平行方向となるように配置されている。インナーリードポスト26p1には第2の発熱素子24と電気接続するためのワイヤ(ボンディング)W1が接続されている。従って、ワイヤボンディングする際にインナーリードポスト26p1の両端部を押さえて確実にワイヤボンディングすることができる。しかも、半導体装置10の小型化を図るために第1の発熱素子22を密集させた配置にしても、上記のクロス配線の領域を確保することができ、半導体装置10の小型化を充分に図り易い。インナーリードポスト26p2についても同様である。

また、ワイヤの材質は、通電のために電気抵抗の低い金属が好ましく、例えばアルミニウムまたはアルミニウム合金、あるいは金または金合金、あるいは銅または銅合金が好ましい。

また、ワイヤの太さについては、大電流を流すワイヤは電気抵抗を小さくするために相対的に太く、それ以外のワイヤは細くしてもよい。

また、リボンワイヤあるいは、ストラップリードを用いることによって、高い通電性と放熱性の向上を期待することができる。

また、リードフレーム26は複数のフレームタブ(第1フレームタブ40および第2フレームタブ42)を有しており、第1フレームタブ40における第1の発熱素子22の1つあたりの面積は、第2フレームタブ42における第2の発熱素子24の1つあたりの面積に比べて大きい。従って、第1フレームタブ40では第2フレームタブ42よりも放熱し易いので、第1の発熱素子22で発生した熱を放熱し易い。

また、第2フレームタブ42には、1つの第1の発熱素子22と複数の第2の発熱素子24とが配置されており、第2フレームタブ42に供給する電力は他のフレームタブに比べて相対的に大きい。アウターリード26eと第2フレームタブ42とに接続するインナーリード本体26mの横幅を幅広にすることで伝熱効果を高め放熱性を向上させることができる。

また、第2フレームタブ42の透孔46は、第2フレームタブ42の横方向の熱伝導を妨げることにより、発熱素子間の熱の影響を防止することには有効であるが、第2フレームタブ42の中央付近に熱がこもり易くなることを防ぐため、幅広なインナーリード本体26mを第2フレームタブ42の略中央に接続することにより、第2フレームタブ42の放熱性を向上させることができる。

また、第1の発熱素子22と第2の発熱素子24との間のフレームタブ部分42mに、フレームタブ部分42mを貫通する透孔46が形成されている。

透孔46により、フレームタブ部分42mを通過する横方向の伝熱を防止でき、第1の発熱素子22で発生した熱が、第2の発熱素子24に伝わることを防止できる。

また、透孔46内には第2フレームタブ40を放熱回路基板に接着する際に、樹脂を主剤とした導電性接着剤が入り込んでもよい。この場合、はんだが入り込んだ場合よりも熱の遮断性効果が高くなる。

また、封止樹脂34にて封止した際に封止樹脂34が入り込んでも熱の遮断性効果が高くなる。この際、透孔46内にボイド等の空気が入り込んでも熱の遮断性効果が高くなる。

なお、導電性接着剤として、はんだを入り込ませてもよい。この場合、熱の遮断性は劣るが、接着時にはんだ中のボイドが透孔46内に抜けるため、はんだの厚みを均一化しやすいという効果が得られる。

また透孔46の形状、大きさは本実施形態に限定するものでは無く、第2フレームタブの強度が維持される大きさであればよい。

例えば、透孔46の幅は、フレームタブ部分42mの幅と略等しい幅まで可能である。

また、フレームタブの厚みが均一な平条フレームとしたが、フレームタブが厚い異形条フレームとすることで熱容量が増加し、放熱効果を向上させることができる。

フレームタブが導電性接着剤(例えばはんだ)で付けられる放熱回路基板20上の銅パターン部分(図示せず)のサイズは、フレームタブと接する部分に比べ、同じか或いはやや小さくされており、これにより、導電性接着剤(例えばはんだ)のはみ出しが抑えられている。

なお、リードフレーム26の表面にはめっき(例えばニッケルめっき)を施してもよい。

放熱回路基板20は、放熱性を重視する場合は金属ベース回路基板とし、そうでない場合は、安価なセラミックベース回路基板することができる。

また、放熱回路基板20は、放熱回路基板20上の銅パターン部分に、第2の発熱素子24を搭載したリードフレーム26の裏面を導電性接着剤(例えばはんだ)を介して接着しており、発熱素子からの熱を封止樹脂34から露出した放熱回路基板20の裏面から放熱する効果が期待できる。

また、銅パターン部分のサイズは、フレームタブと接する部分に比べ、同じか或いはやや小さくされており、これにより、導電性接着剤のはみ出しが抑えられている。

また、封止樹脂34は、放熱回路基板20と対向する側の長手方向、すなわち放熱回路基板20に接する側が放熱回路基板20に対して確実に凸形状となっている。これにより、外部の放熱フィンにビス止めすることで、放熱回路基板20の中央部が封止樹脂34から浮き上がることを確実に防止し、密着性を向上させることができる。このことは、封止樹脂34が薄厚であるときに特に顕著な効果を奏する。

また、封止樹脂34の裏面に切欠部34dを形成することで沿面距離を確保しており、これにより、電気絶縁性が向上している。

なお、インナーリードポスト26p1、26p2とアウターリード26eやインナーリード接続部26cnとの接続形態や、インナーリードポスト26p1、26p2の寸法などは特に限定するものではない。例えば、図1に示したアウターリード26eよりも幅細のアウターリード56e(図2参照)が接続されたインナーリードポスト56pであってもよいし、図1に示したインナーリード接続部26cnに比べ、平面視で逆方向(紙面左下方向)に延び出すインナーリード接続部66cn(図3参照)が接続されたインナーリードポスト66pであってもよい。また、図1に示したインナーリードポスト26p2に比べ、平面視での縦横比が更に大きいインナーリードポスト76p(図4参照)であってもよい。

また、本実施形態では、感温素子28の長手方向が半導体装置10の長手方向と垂直になるよう配置された例で説明したが、厳密に垂直ではなくて、例えば垂直方向に対して±5°程度に傾いていても、封止樹脂34の反りによって感温素子28に生じる反りを小さくすることができる。

また、本実施形態では、インナーリードポスト26p1、26p2の長手方向が、放熱回路基板20の長手方向と平行方向となるように配置された例で説明したが、厳密に平行ではなくて、例えば平行方向に対して±5°程度に傾いていても、ワイヤボンディングする際にインナーリードポスト26p1の両端部を押さえて確実にワイヤボンディングすることができ、また、第1の発熱素子22を密集させた配置にしても、上記のクロス配線の領域を確保して半導体装置10の小型化を充分に図ることができる。

感温素子28は、温度検知精度に応じた電子部品や抵抗で構成することもできる。

第1の発熱素子22と第2の発熱素子24は、従来のシリコン(Si)半導体素子に比べて高温状態での動作が可能であり、スイッチング速度が速く、低損失である化合物半導体、例えばシリコンカーバイド(SiC)やガリウムナイトライド(GaN)等の化合物半導体で構成することもできる。

以上のように、本発明に係る半導体装置は、インナーリードは、ボンディングワイヤの被接続部となるインナーリードポストを有しており、インナーリードポストは、矩形状であって長手方向が放熱回路基板の長手方向に沿っているので、装置の小型化を図りつつインナーリードにワイヤボンディングを良好に行うことができる構成の半導体装置として用いるのに好適である。

10 半導体装置

20 放熱回路基板

22 発熱素子

24 発熱素子

26 リードフレーム

26cn インナーリード接続部

26m インナーリード本体

26p1 インナーリードポスト

26p2 インナーリードポスト

40 第1フレームタブ(単数素子搭載フレームタブ)

42 第2フレームタブ(複数素子搭載フレームタブ)

43 第3フレームタブ(単数素子搭載フレームタブ)

W1 ワイヤ(ボンディングワイヤ)

W2 ワイヤ(ボンディングワイヤ)

W3 ワイヤ(ボンディングワイヤ)

20 放熱回路基板

22 発熱素子

24 発熱素子

26 リードフレーム

26cn インナーリード接続部

26m インナーリード本体

26p1 インナーリードポスト

26p2 インナーリードポスト

40 第1フレームタブ(単数素子搭載フレームタブ)

42 第2フレームタブ(複数素子搭載フレームタブ)

43 第3フレームタブ(単数素子搭載フレームタブ)

W1 ワイヤ(ボンディングワイヤ)

W2 ワイヤ(ボンディングワイヤ)

W3 ワイヤ(ボンディングワイヤ)

Claims (4)

- インナーリードを放熱回路基板上に有する半導体装置であって、

前記インナーリードは、ボンディングワイヤの被接続部となるインナーリードポストを有しており、

前記インナーリードポストは、矩形状であって長手方向が前記放熱回路基板の長手方向に沿っていることを特徴とする半導体装置。 - 前記インナーリードポストの長手方向略中央部にボンディングワイヤが接続されていることを特徴とする請求項1記載の半導体装置。

- 前記インナーリードを有するリードフレームは、発熱素子が載置されるフレームタブを備えており、

前記インナーリードポストと前記フレームタブとに連続するインナーリード接続部と、前記インナーリードポストと前記フレームタブ上に載置された前記発熱素子とに接続するボンディングワイヤとは、平面視で交差していることを特徴とする請求項1または2記載の半導体装置。 - 前記フレームタブとして、1つの発熱素子が載置された単数素子搭載フレームタブと、複数の発熱素子が載置された複数素子搭載フレームタブとが設けられ、

前記複数素子搭載フレームタブに接続する前記インナーリード接続部またはインナーリード本体は、前記単数素子搭載フレームタブに接続する前記インナーリード接続部に比べて幅広であることを特徴とする請求項3記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013073507A JP2014123701A (ja) | 2012-11-20 | 2013-03-29 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012254552 | 2012-11-20 | ||

| JP2012254552 | 2012-11-20 | ||

| JP2013073507A JP2014123701A (ja) | 2012-11-20 | 2013-03-29 | 半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2014123701A true JP2014123701A (ja) | 2014-07-03 |

Family

ID=51403948

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013073507A Pending JP2014123701A (ja) | 2012-11-20 | 2013-03-29 | 半導体装置 |

| JP2013073495A Pending JP2014123700A (ja) | 2012-11-20 | 2013-03-29 | 半導体装置 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013073495A Pending JP2014123700A (ja) | 2012-11-20 | 2013-03-29 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (2) | JP2014123701A (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12489047B2 (en) | 2020-06-08 | 2025-12-02 | Rohm Co., Ltd. | Semiconductor device |

| CN114035643A (zh) * | 2022-01-10 | 2022-02-11 | 上海奥简微电子科技有限公司 | 温控保护电路 |

-

2013

- 2013-03-29 JP JP2013073507A patent/JP2014123701A/ja active Pending

- 2013-03-29 JP JP2013073495A patent/JP2014123700A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014123700A (ja) | 2014-07-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7755179B2 (en) | Semiconductor package structure having enhanced thermal dissipation characteristics | |

| JP6164364B2 (ja) | 半導体装置 | |

| JP7150461B2 (ja) | 半導体装置 | |

| KR101477378B1 (ko) | 하우징 및 이를 구비하는 전력 모듈 | |

| JP6448418B2 (ja) | 電力用半導体装置 | |

| JP7238353B2 (ja) | 半導体モジュールおよびそれを用いた半導体装置 | |

| JP7121188B2 (ja) | 素子用基板、発光素子モジュールおよび発光装置 | |

| CN112514066B (zh) | 半导体装置 | |

| WO2014034411A1 (ja) | 電力用半導体装置 | |

| JP2015115471A (ja) | 電力用半導体装置 | |

| JP7379886B2 (ja) | 半導体装置 | |

| JP6048238B2 (ja) | 電子装置 | |

| US20130147027A1 (en) | Semiconductor package | |

| JP4702279B2 (ja) | 半導体装置およびその製造方法 | |

| JP5429413B2 (ja) | 半導体装置 | |

| JP4046623B2 (ja) | パワー半導体モジュールおよびその固定方法 | |

| JP2014123701A (ja) | 半導体装置 | |

| JP6540587B2 (ja) | パワーモジュール | |

| JP5177174B2 (ja) | 半導体装置 | |

| JP2013113638A (ja) | 半導体装置 | |

| JP2008091432A (ja) | 電子部品 | |

| JP2015149363A (ja) | 半導体モジュール | |

| JP2014103270A (ja) | 半導体モジュール | |

| JP6060053B2 (ja) | パワー半導体装置 | |

| KR101897304B1 (ko) | 파워 모듈 |