JP2013242575A - Liquid crystal display device - Google Patents

Liquid crystal display device Download PDFInfo

- Publication number

- JP2013242575A JP2013242575A JP2013131297A JP2013131297A JP2013242575A JP 2013242575 A JP2013242575 A JP 2013242575A JP 2013131297 A JP2013131297 A JP 2013131297A JP 2013131297 A JP2013131297 A JP 2013131297A JP 2013242575 A JP2013242575 A JP 2013242575A

- Authority

- JP

- Japan

- Prior art keywords

- backlight

- image

- layer

- conductive layer

- display panel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 618

- 239000004065 semiconductor Substances 0.000 claims description 423

- 230000015572 biosynthetic process Effects 0.000 claims description 14

- 238000000034 method Methods 0.000 description 668

- 239000010408 film Substances 0.000 description 645

- 239000000758 substrate Substances 0.000 description 634

- 239000010410 layer Substances 0.000 description 583

- 230000002829 reductive effect Effects 0.000 description 325

- 238000006243 chemical reaction Methods 0.000 description 314

- 230000033001 locomotion Effects 0.000 description 247

- 238000004519 manufacturing process Methods 0.000 description 166

- 230000006870 function Effects 0.000 description 118

- 239000003990 capacitor Substances 0.000 description 113

- 239000012535 impurity Substances 0.000 description 108

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 107

- 229910052814 silicon oxide Inorganic materials 0.000 description 101

- 230000004044 response Effects 0.000 description 96

- 239000000463 material Substances 0.000 description 93

- 229910052710 silicon Inorganic materials 0.000 description 83

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 74

- 239000010703 silicon Substances 0.000 description 74

- 238000012545 processing Methods 0.000 description 73

- 230000008859 change Effects 0.000 description 67

- 230000008901 benefit Effects 0.000 description 66

- 230000015654 memory Effects 0.000 description 65

- 239000002585 base Substances 0.000 description 61

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 60

- 238000009832 plasma treatment Methods 0.000 description 59

- 229910052581 Si3N4 Inorganic materials 0.000 description 52

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 52

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 42

- 230000005684 electric field Effects 0.000 description 42

- 239000011159 matrix material Substances 0.000 description 42

- 238000002834 transmittance Methods 0.000 description 42

- 230000000694 effects Effects 0.000 description 38

- 229910052782 aluminium Inorganic materials 0.000 description 35

- 239000002356 single layer Substances 0.000 description 35

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 33

- 239000007789 gas Substances 0.000 description 33

- 230000006872 improvement Effects 0.000 description 33

- 239000010936 titanium Substances 0.000 description 33

- 229910052760 oxygen Inorganic materials 0.000 description 32

- 239000001301 oxygen Substances 0.000 description 32

- 206010047571 Visual impairment Diseases 0.000 description 31

- 230000008569 process Effects 0.000 description 30

- 239000000956 alloy Substances 0.000 description 29

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 29

- 239000013078 crystal Substances 0.000 description 28

- 150000002500 ions Chemical class 0.000 description 28

- 230000002093 peripheral effect Effects 0.000 description 27

- 125000006850 spacer group Chemical group 0.000 description 27

- 238000004544 sputter deposition Methods 0.000 description 27

- 229910052719 titanium Inorganic materials 0.000 description 27

- 239000011521 glass Substances 0.000 description 25

- 229910052757 nitrogen Inorganic materials 0.000 description 25

- 238000010586 diagram Methods 0.000 description 24

- 238000007667 floating Methods 0.000 description 24

- 229910052750 molybdenum Inorganic materials 0.000 description 24

- 230000004888 barrier function Effects 0.000 description 23

- 229910052721 tungsten Inorganic materials 0.000 description 23

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 22

- 239000001257 hydrogen Substances 0.000 description 22

- 229910052739 hydrogen Inorganic materials 0.000 description 22

- 229910052799 carbon Inorganic materials 0.000 description 21

- 238000005259 measurement Methods 0.000 description 21

- 229910045601 alloy Inorganic materials 0.000 description 20

- 239000010949 copper Substances 0.000 description 20

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 20

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 19

- 238000005530 etching Methods 0.000 description 19

- 238000010438 heat treatment Methods 0.000 description 19

- 229910052751 metal Inorganic materials 0.000 description 19

- 239000002184 metal Substances 0.000 description 19

- 238000005121 nitriding Methods 0.000 description 17

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 17

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 16

- 230000003647 oxidation Effects 0.000 description 16

- 238000007254 oxidation reaction Methods 0.000 description 16

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 15

- 239000012298 atmosphere Substances 0.000 description 15

- 229910052802 copper Inorganic materials 0.000 description 15

- 230000006866 deterioration Effects 0.000 description 15

- 238000000206 photolithography Methods 0.000 description 15

- 125000001424 substituent group Chemical group 0.000 description 15

- 229910052715 tantalum Inorganic materials 0.000 description 15

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 14

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 14

- 229910052786 argon Inorganic materials 0.000 description 14

- 238000005229 chemical vapour deposition Methods 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 14

- -1 electrophoresis Substances 0.000 description 14

- 229910052734 helium Inorganic materials 0.000 description 14

- 239000011733 molybdenum Substances 0.000 description 14

- 230000001590 oxidative effect Effects 0.000 description 14

- 229910052698 phosphorus Inorganic materials 0.000 description 14

- 239000011574 phosphorus Substances 0.000 description 14

- 239000010937 tungsten Substances 0.000 description 14

- 229910021417 amorphous silicon Inorganic materials 0.000 description 13

- 230000005540 biological transmission Effects 0.000 description 13

- 239000011651 chromium Substances 0.000 description 13

- 238000012937 correction Methods 0.000 description 13

- 238000009826 distribution Methods 0.000 description 13

- 229910052743 krypton Inorganic materials 0.000 description 13

- 230000003287 optical effect Effects 0.000 description 13

- 229920005989 resin Polymers 0.000 description 13

- 239000011347 resin Substances 0.000 description 13

- 230000002123 temporal effect Effects 0.000 description 13

- 239000010409 thin film Substances 0.000 description 13

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 12

- 150000001875 compounds Chemical class 0.000 description 12

- 238000006073 displacement reaction Methods 0.000 description 12

- 239000000126 substance Substances 0.000 description 12

- 229910052804 chromium Inorganic materials 0.000 description 11

- 239000003086 colorant Substances 0.000 description 11

- 239000010931 gold Substances 0.000 description 11

- 229910052697 platinum Inorganic materials 0.000 description 11

- 238000007639 printing Methods 0.000 description 11

- 230000009467 reduction Effects 0.000 description 11

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 11

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 10

- 229910052796 boron Inorganic materials 0.000 description 10

- 230000007547 defect Effects 0.000 description 10

- 125000001153 fluoro group Chemical group F* 0.000 description 10

- 229910052754 neon Inorganic materials 0.000 description 10

- 125000000962 organic group Chemical group 0.000 description 10

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 10

- 229910052709 silver Inorganic materials 0.000 description 10

- 238000003860 storage Methods 0.000 description 10

- 238000000576 coating method Methods 0.000 description 9

- 238000001514 detection method Methods 0.000 description 9

- 239000012212 insulator Substances 0.000 description 9

- 229910052759 nickel Inorganic materials 0.000 description 9

- 150000004767 nitrides Chemical class 0.000 description 9

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 9

- 229910052724 xenon Inorganic materials 0.000 description 9

- 229910052779 Neodymium Inorganic materials 0.000 description 8

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 8

- 238000002425 crystallisation Methods 0.000 description 8

- 229910052737 gold Inorganic materials 0.000 description 8

- 238000012966 insertion method Methods 0.000 description 8

- 230000007246 mechanism Effects 0.000 description 8

- 229920003023 plastic Polymers 0.000 description 8

- 239000004033 plastic Substances 0.000 description 8

- 238000002310 reflectometry Methods 0.000 description 8

- 229910052725 zinc Inorganic materials 0.000 description 8

- 239000011701 zinc Substances 0.000 description 8

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 7

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 7

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 7

- 229910052785 arsenic Inorganic materials 0.000 description 7

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 7

- 125000004429 atom Chemical group 0.000 description 7

- 230000000295 complement effect Effects 0.000 description 7

- 229910052733 gallium Inorganic materials 0.000 description 7

- 229910052732 germanium Inorganic materials 0.000 description 7

- 239000010955 niobium Substances 0.000 description 7

- 206010040844 Skin exfoliation Diseases 0.000 description 6

- 238000001312 dry etching Methods 0.000 description 6

- 238000001962 electrophoresis Methods 0.000 description 6

- 230000001747 exhibiting effect Effects 0.000 description 6

- 150000002431 hydrogen Chemical class 0.000 description 6

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 6

- 239000011368 organic material Substances 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 239000010453 quartz Substances 0.000 description 6

- 229910021332 silicide Inorganic materials 0.000 description 6

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 6

- 239000010935 stainless steel Substances 0.000 description 6

- 229910001220 stainless steel Inorganic materials 0.000 description 6

- 230000001360 synchronised effect Effects 0.000 description 6

- 229920001665 Poly-4-vinylphenol Polymers 0.000 description 5

- 239000004952 Polyamide Substances 0.000 description 5

- 239000004642 Polyimide Substances 0.000 description 5

- 125000000217 alkyl group Chemical group 0.000 description 5

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 5

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 5

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 5

- 239000002041 carbon nanotube Substances 0.000 description 5

- 229910021393 carbon nanotube Inorganic materials 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 5

- 238000001816 cooling Methods 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 239000010432 diamond Substances 0.000 description 5

- 229910003460 diamond Inorganic materials 0.000 description 5

- 239000000975 dye Substances 0.000 description 5

- 239000004744 fabric Substances 0.000 description 5

- 239000011572 manganese Substances 0.000 description 5

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 5

- 229920002647 polyamide Polymers 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 238000000926 separation method Methods 0.000 description 5

- 239000010944 silver (metal) Substances 0.000 description 5

- 229910000838 Al alloy Inorganic materials 0.000 description 4

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 4

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 4

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- 239000012790 adhesive layer Substances 0.000 description 4

- 229910052783 alkali metal Inorganic materials 0.000 description 4

- 150000001340 alkali metals Chemical class 0.000 description 4

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 4

- 150000001342 alkaline earth metals Chemical class 0.000 description 4

- 239000005407 aluminoborosilicate glass Substances 0.000 description 4

- 229910052788 barium Inorganic materials 0.000 description 4

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 4

- 239000005388 borosilicate glass Substances 0.000 description 4

- 239000000872 buffer Substances 0.000 description 4

- 238000007906 compression Methods 0.000 description 4

- 230000006835 compression Effects 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 230000003111 delayed effect Effects 0.000 description 4

- 239000000835 fiber Substances 0.000 description 4

- 239000012467 final product Substances 0.000 description 4

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical group [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 4

- 229910052736 halogen Inorganic materials 0.000 description 4

- 230000012447 hatching Effects 0.000 description 4

- 230000005660 hydrophilic surface Effects 0.000 description 4

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 4

- 239000002245 particle Substances 0.000 description 4

- 238000005498 polishing Methods 0.000 description 4

- 229920000728 polyester Polymers 0.000 description 4

- 229920000139 polyethylene terephthalate Polymers 0.000 description 4

- 239000005020 polyethylene terephthalate Substances 0.000 description 4

- 230000001681 protective effect Effects 0.000 description 4

- 230000008439 repair process Effects 0.000 description 4

- 230000002441 reversible effect Effects 0.000 description 4

- 239000010980 sapphire Substances 0.000 description 4

- 229910052594 sapphire Inorganic materials 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 210000003491 skin Anatomy 0.000 description 4

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 4

- 239000012780 transparent material Substances 0.000 description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 4

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 3

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 3

- 229910000583 Nd alloy Inorganic materials 0.000 description 3

- HEQWUWZWGPCGCD-UHFFFAOYSA-N cadmium(2+) oxygen(2-) tin(4+) Chemical compound [O--].[O--].[O--].[Cd++].[Sn+4] HEQWUWZWGPCGCD-UHFFFAOYSA-N 0.000 description 3

- 230000006837 decompression Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 239000003779 heat-resistant material Substances 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 238000005286 illumination Methods 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000010884 ion-beam technique Methods 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 229910052748 manganese Inorganic materials 0.000 description 3

- 229910052758 niobium Inorganic materials 0.000 description 3

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- 150000001282 organosilanes Chemical class 0.000 description 3

- 239000012071 phase Substances 0.000 description 3

- PFNQVRZLDWYSCW-UHFFFAOYSA-N (fluoren-9-ylideneamino) n-naphthalen-1-ylcarbamate Chemical compound C12=CC=CC=C2C2=CC=CC=C2C1=NOC(=O)NC1=CC=CC2=CC=CC=C12 PFNQVRZLDWYSCW-UHFFFAOYSA-N 0.000 description 2

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- KZMAWJRXKGLWGS-UHFFFAOYSA-N 2-chloro-n-[4-(4-methoxyphenyl)-1,3-thiazol-2-yl]-n-(3-methoxypropyl)acetamide Chemical compound S1C(N(C(=O)CCl)CCCOC)=NC(C=2C=CC(OC)=CC=2)=C1 KZMAWJRXKGLWGS-UHFFFAOYSA-N 0.000 description 2

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 2

- QTBSBXVTEAMEQO-UHFFFAOYSA-M Acetate Chemical compound CC([O-])=O QTBSBXVTEAMEQO-UHFFFAOYSA-M 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 244000025254 Cannabis sativa Species 0.000 description 2

- 235000012766 Cannabis sativa ssp. sativa var. sativa Nutrition 0.000 description 2

- 235000012765 Cannabis sativa ssp. sativa var. spontanea Nutrition 0.000 description 2

- 229920000298 Cellophane Polymers 0.000 description 2

- 229920000742 Cotton Polymers 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- 239000005264 High molar mass liquid crystal Substances 0.000 description 2

- 239000004976 Lyotropic liquid crystal Substances 0.000 description 2

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 2

- 241001465754 Metazoa Species 0.000 description 2

- 239000004988 Nematic liquid crystal Substances 0.000 description 2

- 239000004677 Nylon Substances 0.000 description 2

- 229910003849 O-Si Inorganic materials 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- 229910003872 O—Si Inorganic materials 0.000 description 2

- 239000004698 Polyethylene Substances 0.000 description 2

- 229920000297 Rayon Polymers 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 229910002808 Si–O–Si Inorganic materials 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 230000001133 acceleration Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 239000005354 aluminosilicate glass Substances 0.000 description 2

- UBSJOWMHLJZVDJ-UHFFFAOYSA-N aluminum neodymium Chemical compound [Al].[Nd] UBSJOWMHLJZVDJ-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 235000009120 camo Nutrition 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 210000004027 cell Anatomy 0.000 description 2

- 235000005607 chanvre indien Nutrition 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 238000003776 cleavage reaction Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 210000004207 dermis Anatomy 0.000 description 2

- 229920001971 elastomer Polymers 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 2

- 239000012530 fluid Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 239000011888 foil Substances 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 230000004313 glare Effects 0.000 description 2

- 238000000227 grinding Methods 0.000 description 2

- 239000011487 hemp Substances 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 2

- 229910052740 iodine Inorganic materials 0.000 description 2

- 239000011630 iodine Substances 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000010985 leather Substances 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 239000003094 microcapsule Substances 0.000 description 2

- 239000013081 microcrystal Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 229960001730 nitrous oxide Drugs 0.000 description 2

- 235000013842 nitrous oxide Nutrition 0.000 description 2

- 229920001778 nylon Polymers 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 206010033675 panniculitis Diseases 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 239000002861 polymer material Substances 0.000 description 2

- 229920002635 polyurethane Polymers 0.000 description 2

- 239000004814 polyurethane Substances 0.000 description 2

- 239000000843 powder Substances 0.000 description 2

- 239000000047 product Substances 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 239000002964 rayon Substances 0.000 description 2

- 230000007017 scission Effects 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 239000004575 stone Substances 0.000 description 2

- 230000035882 stress Effects 0.000 description 2

- 210000004304 subcutaneous tissue Anatomy 0.000 description 2

- 229920002994 synthetic fiber Polymers 0.000 description 2

- 239000012209 synthetic fiber Substances 0.000 description 2

- 229920003002 synthetic resin Polymers 0.000 description 2

- 239000000057 synthetic resin Substances 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000002023 wood Substances 0.000 description 2

- 101150034533 ATIC gene Proteins 0.000 description 1

- 101100269850 Caenorhabditis elegans mask-1 gene Proteins 0.000 description 1

- 239000004985 Discotic Liquid Crystal Substance Substances 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- 125000002066 L-histidyl group Chemical group [H]N1C([H])=NC(C([H])([H])[C@](C(=O)[*])([H])N([H])[H])=C1[H] 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910019015 Mg-Ag Inorganic materials 0.000 description 1

- 240000008790 Musa x paradisiaca Species 0.000 description 1

- 235000018290 Musa x paradisiaca Nutrition 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004695 Polyether sulfone Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 206010037660 Pyrexia Diseases 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910020751 SixGe1-x Inorganic materials 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 229910001362 Ta alloys Inorganic materials 0.000 description 1

- 206010057040 Temperature intolerance Diseases 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 238000000149 argon plasma sintering Methods 0.000 description 1

- 238000001505 atmospheric-pressure chemical vapour deposition Methods 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000008033 biological extinction Effects 0.000 description 1

- 230000004397 blinking Effects 0.000 description 1

- 239000011449 brick Substances 0.000 description 1

- NNBFNNNWANBMTI-UHFFFAOYSA-M brilliant green Chemical compound OS([O-])(=O)=O.C1=CC(N(CC)CC)=CC=C1C(C=1C=CC=CC=1)=C1C=CC(=[N+](CC)CC)C=C1 NNBFNNNWANBMTI-UHFFFAOYSA-M 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000011575 calcium Substances 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 208000037265 diseases, disorders, signs and symptoms Diseases 0.000 description 1

- 208000035475 disorder Diseases 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000004070 electrodeposition Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 230000012010 growth Effects 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 230000008543 heat sensitivity Effects 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- 238000000097 high energy electron diffraction Methods 0.000 description 1

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 150000002497 iodine compounds Chemical class 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 238000005184 irreversible process Methods 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000003698 laser cutting Methods 0.000 description 1

- 230000031700 light absorption Effects 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- DTSBBUTWIOVIBV-UHFFFAOYSA-N molybdenum niobium Chemical compound [Nb].[Mo] DTSBBUTWIOVIBV-UHFFFAOYSA-N 0.000 description 1

- GALOTNBSUVEISR-UHFFFAOYSA-N molybdenum;silicon Chemical compound [Mo]#[Si] GALOTNBSUVEISR-UHFFFAOYSA-N 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 239000005416 organic matter Substances 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 229920006393 polyether sulfone Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 229910021426 porous silicon Inorganic materials 0.000 description 1

- 238000001556 precipitation Methods 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 230000001953 sensory effect Effects 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 241000894007 species Species 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

Abstract

Description

本発明は、装置およびその駆動方法に関する。具体的には、半導体装置およびその駆動方

法に関する。さらに具体的には、液晶表示装置およびその駆動方法、特に、コントラスト

を向上した液晶表示装置およびその駆動方法、さらに、動画の品質を向上させる方法に関

する。

The present invention relates to an apparatus and a driving method thereof. Specifically, the present invention relates to a semiconductor device and a driving method thereof. More specifically, the present invention relates to a liquid crystal display device and a driving method thereof, and more particularly to a liquid crystal display device having improved contrast and a driving method thereof, and a method of improving the quality of moving images.

近年、薄型の表示装置に対する関心が高まっている。CRTディスプレイに代わり、液晶

ディスプレイ、プラズマディスプレイ、プロジェクションディスプレイなどが開発され、

普及してきた。さらに、フィールドエミッションディスプレイ、無機エレクトロルミネセ

ンスディスプレイ、有機エレクトロルミネセンスディスプレイ、電子ペーパーなどが、次

世代の表示装置として開発が進められている。

In recent years, interest in thin display devices has increased. Instead of CRT displays, liquid crystal displays, plasma displays, projection displays, etc. have been developed.

It has become popular. Furthermore, field emission displays, inorganic electroluminescent displays, organic electroluminescent displays, electronic paper, and the like are being developed as next-generation display devices.

上述したような表示装置に備えられた表示部には、画像を構成する最小単位である画素が

並置される。そして、それぞれの画素が、画像データにしたがった輝度で発光することで

、表示部に画像が形成される。

In the display unit provided in the display device as described above, pixels that are the minimum unit constituting an image are juxtaposed. Then, each pixel emits light with luminance according to the image data, so that an image is formed on the display unit.

このような表示装置を用いて動画を表示させるときは、複数の画像を、1秒間に数十回、

素早く表示させることで行う。この、複数の画像を表示する周期(または、画像データが

表示装置に入力される周期)のことを、1フレーム期間と呼ぶ。

When displaying a moving image using such a display device, a plurality of images are displayed several tens of times per second,

This is done by displaying it quickly. This period for displaying a plurality of images (or the period for inputting image data to the display device) is called one frame period.

ここで、表示装置の駆動方法は、画素の輝度が、1フレーム期間内に、どのような時間的

分布を持っているかという観点で分類できる。アクティブマトリクス型の表示装置に主に

用いられるホールド型の駆動方法は、1フレーム期間内で、画素の輝度は一定である。一

方、CRT等に用いられるインパルス型の駆動方法は、1フレーム期間内に一度強く発光

した後、画素の輝度は直ちに減衰して発光しなくなる。インパルス型の駆動方法では、1

フレーム期間の大半は非発光状態である。

Here, the driving method of the display device can be classified from the viewpoint of what temporal distribution the pixel luminance has within one frame period. In a hold-type driving method mainly used for an active matrix display device, the luminance of a pixel is constant within one frame period. On the other hand, in the impulse-type driving method used for CRT or the like, after intense light emission once in one frame period, the luminance of the pixel is immediately attenuated and no light is emitted. In the impulse type driving method, 1

Most of the frame period is a non-light emitting state.

ホールド型の表示装置は、動画を表示したとき、画像の一部分が動いている場合では動い

ているものが尾を引いたように見えたり、画像全体で動いている場合では全体がぼやけて

見えたりする問題(動画ボケ:Motion Blur)を持つことが明らかになってき

ている。これは、人間の目は動いている物体の動きを予測して物体が動く先に視線を動か

しているのに対して、ホールド型の表示装置に表示される画像は1フレーム期間の間は止

まり続けているという不一致から起こっているといわれている。インパルス型の表示装置

では、画像は一瞬表示されてから直ちに消えるので、このような見え方と表示の不一致は

起こらず、動画ボケの問題は起こらない。

When a moving image is displayed, a hold-type display device may appear to have a trailing edge when it is moving part of the image, or it may appear blurry when it is moving as a whole image. It has become clear that it has a problem (moving motion blur). This is because the human eye predicts the movement of the moving object and moves the line of sight ahead of the moving object, whereas the image displayed on the hold-type display device stops for one frame period. It is said that it is caused by the disagreement of continuing. In the impulse-type display device, an image is displayed for a moment and then disappears immediately. Therefore, such inconsistency between the appearance and the display does not occur, and the problem of moving image blur does not occur.

ホールド型の表示装置における動画ボケの問題を解決する方法としては、主に、次の2つ

の方法が提案されている(特許文献1)。1つ目は、1フレーム期間内に、本来の画像を

表示する期間と、黒画像を表示する期間とを設けることである。こうすることで、表示を

擬似的にインパルス型に近づけることができ、目の残像を抑えることができるため、動画

の品質を向上することができる(特許文献2、3)。2つ目は、1フレーム期間の長さを

短くする(フレーム周波数を大きくする)ことである。こうすることで、画像の動きが目

の動きに追従できるようになり、画像の動きがなめらかになるため、動画の品質を向上す

ることができる(特許文献4)。さらに、1つ目の方法の改良技術として、黒画像の代わ

りに、元の画像より暗い画像を表示することでも動画の品質を向上することができること

が公開されている(特許文献5、6、非特許文献1、2、3)。さらに、条件に応じて駆

動方法を変える方法も公開されている(特許文献7、8)。

As a method of solving the problem of moving image blur in the hold type display device, the following two methods are mainly proposed (Patent Document 1). The first is to provide a period for displaying an original image and a period for displaying a black image within one frame period. By doing so, the display can be approximated to an impulse type and the afterimage of the eyes can be suppressed, so that the quality of the moving image can be improved (

さらに、表示装置が表示できる画像の品質を表す指標のひとつとして、コントラスト比が

ある。コントラスト比とは、表示装置が発することのできる輝度の明暗比(最大輝度と最

小輝度の比)のことである。コントラスト比が大きい表示装置ほど、明るさのダイナミッ

クレンジが大きく、メリハリのきいた、くっきりとした画像を表示することができる。バ

ックライトを用いた表示装置におけるコントラスト比を向上する方法としては、特許文献

9、非特許文献4などに開示されている。

Further, as one of the indexes representing the quality of an image that can be displayed by the display device, there is a contrast ratio. The contrast ratio is the brightness contrast ratio (the ratio between the maximum brightness and the minimum brightness) that the display device can emit. A display device with a higher contrast ratio has a larger dynamic range of brightness and can display a sharp and clear image. Methods for improving the contrast ratio in a display device using a backlight are disclosed in

このように、ホールド型の表示装置における動画ボケの問題を解決する方法として、様々

なものが検討されているが、その効果はまだ不十分であり、インパルス型と同等な動画の

品質を持つには至っていない。さらに、黒画像を表示する表示を擬似的にインパルス型に

近づける方法では、ちらつき(フリッカ)が増大する。また、黒画像の表示することによ

って画像の輝度が小さくなってしまい、黒画像を挿入しない場合と同等の輝度を得るため

には消費電力が増大してしまうという問題もある。フレーム周波数を大きくする方法では

、データ処理が複雑になるため、高速に処理できる駆動回路が必要になり、製造コストの

増加や、データ処理に伴う発熱や消費電力の増大が問題となる。

As described above, various methods for solving the problem of moving image blur in the hold type display device have been studied. However, the effect is still insufficient, and the moving image quality is equivalent to that of the impulse type. Has not reached. Further, flickering is increased in the method of artificially bringing the display for displaying a black image closer to the impulse type. Also, there is a problem that the luminance of the image is reduced by displaying the black image, and the power consumption is increased in order to obtain the same luminance as when the black image is not inserted. Since the method of increasing the frame frequency complicates data processing, a driving circuit capable of high-speed processing is required, and there are problems of increased manufacturing costs, heat generation and power consumption accompanying data processing.

さらに、バックライトを用いた表示装置におけるコントラスト比を向上する方法として、

様々なものが検討されているが、動画の品質も同様に向上するための方法の検討はなされ

ていない。

Furthermore, as a method for improving the contrast ratio in a display device using a backlight,

Although various things are examined, the method for improving the quality of a moving image is also not examined.

本発明は、このような問題を鑑みてなされたものであり、主なものとしては、静止画およ

び動画の品質(画質)が向上された表示装置およびその駆動方法を提供することである。

より詳細には、動画ボケの問題がない表示装置およびその駆動方法を提供すること、コン

トラスト比の向上した表示装置およびその駆動方法を提供すること、フリッカのない表示

装置およびその駆動方法を提供すること、視野角が向上された表示装置およびその駆動方

法を提供すること、応答速度が向上された表示装置およびその駆動方法を提供すること、

等を課題とする。さらに、消費電力が低減された表示装置およびその駆動方法を提供する

こと、製造コストが低減された表示装置およびその駆動方法を提供すること、等を課題と

する。

The present invention has been made in view of such a problem, and a main object is to provide a display device with improved quality (image quality) of still images and moving images and a driving method thereof.

More specifically, a display device free from the problem of moving image blur and a driving method thereof, a display device with improved contrast ratio and a driving method thereof, and a display device free from flicker and a driving method thereof are provided. Providing a display device with improved viewing angle and driving method thereof, providing a display device with improved response speed and driving method thereof,

And so on. It is another object of the present invention to provide a display device with reduced power consumption and a driving method thereof, to provide a display device with reduced manufacturing cost, and a driving method thereof.

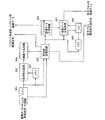

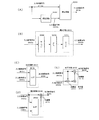

本発明の一は、バックライトと、表示パネルを有する液晶表示装置であって、バックライ

トは、明るさを個別に制御できる複数の単位領域に分割され、表示パネルは、複数の領域

の数よりも多い数の画素を有し、表示パネルに表示される画像は、液晶表示装置に入力さ

れる画像データの動きの変化量を検出することで推定された中間状態の画像データにした

がって表示される画像を含み、バックライトは、表示パネルに表示される画像にしたがっ

てそれぞれの領域の明るさが制御される期間を有し、且つ、表示パネルに表示される画像

の表示周期と同じ周期で発光状態が制御されることを特徴とする液晶表示装置である。

One aspect of the present invention is a liquid crystal display device having a backlight and a display panel, and the backlight is divided into a plurality of unit regions whose brightness can be individually controlled, and the display panel is based on the number of the plurality of regions. An image that has a large number of pixels and is displayed on the display panel is displayed according to the intermediate state image data estimated by detecting the amount of change in the movement of the image data input to the liquid crystal display device. Including the image, the backlight has a period in which the brightness of each area is controlled according to the image displayed on the display panel, and the light emission state is the same cycle as the display cycle of the image displayed on the display panel Is a liquid crystal display device.

本発明の一は、バックライトと、表示パネルを有する液晶表示装置であって、バックライ

トは、明るさを個別に制御できる複数の単位領域に分割され、表示パネルは、単位領域の

数よりも多い数の画素を有し、表示パネルに表示される画像は、表示領域全域において同

じ表示状態を与える画像を含み、バックライトは、表示パネルに表示される画像にしたが

ってそれぞれの単位領域の明るさが制御される期間を有し、且つ、表示パネルに表示され

る画像の表示周期よりも長い周期で発光状態が制御されることを特徴とする液晶表示装置

である。

One aspect of the present invention is a liquid crystal display device having a backlight and a display panel, and the backlight is divided into a plurality of unit regions whose brightness can be individually controlled, and the display panel is more than the number of unit regions. The image that has a large number of pixels and is displayed on the display panel includes an image that gives the same display state in the entire display area, and the backlight has the brightness of each unit area according to the image displayed on the display panel. The liquid crystal display device is characterized in that the light emission state is controlled in a period longer than the display period of an image displayed on the display panel.

本発明の一は、バックライトと、表示パネルを有する液晶表示装置であって、バックライ

トは、明るさを個別に制御できる複数の単位領域に分割され、表示パネルは、単位領域の

数よりも多い数の画素を有し、表示パネルに表示される画像は、液晶表示装置に入力され

る画像データの周期と同じ周期で表示状態が制御され、バックライトは、表示パネルに表

示される画像にしたがってそれぞれの単位領域の明るさが制御される期間を有し、且つ、

発光領域全域において同じ発光状態を与える画像を含み、バックライトは、表示パネルに

表示される画像の表示周期よりも短い周期で発光状態が制御されることを特徴とする液晶

表示装置である。

One aspect of the present invention is a liquid crystal display device having a backlight and a display panel, and the backlight is divided into a plurality of unit regions whose brightness can be individually controlled, and the display panel is more than the number of unit regions. The display state of an image that has a large number of pixels and is displayed on the display panel is controlled in the same cycle as the cycle of image data input to the liquid crystal display device, and the backlight is an image displayed on the display panel. Therefore, it has a period in which the brightness of each unit area is controlled, and

The liquid crystal display device is characterized in that the light emission state is controlled in a cycle shorter than the display cycle of the image displayed on the display panel, including an image giving the same light emission state in the entire light emitting region.

本発明の一は、バックライトと、表示パネルを有する液晶表示装置であって、バックライ

トは、明るさを個別に制御できる複数の単位領域に分割され、表示パネルは、単位領域の

数よりも多い数の画素を有し、表示パネルに表示される画像は、表示領域全域において同

じ表示状態を与える画像を含み、バックライトは、表示パネルに表示される画像にしたが

ってそれぞれの単位領域の明るさが制御される期間を有し、バックライトに表示される画

像は、発光領域全域において同じ発光状態を与える画像を含み、且つ、表示パネルに表示

される画像の表示周期と同じ周期で発光状態が制御されることを特徴とする液晶表示装置

である。

One aspect of the present invention is a liquid crystal display device having a backlight and a display panel, and the backlight is divided into a plurality of unit regions whose brightness can be individually controlled, and the display panel is more than the number of unit regions. The image that has a large number of pixels and is displayed on the display panel includes an image that gives the same display state in the entire display area, and the backlight has the brightness of each unit area according to the image displayed on the display panel. The image displayed on the backlight includes an image that gives the same light emission state in the entire light emission region, and the light emission state is in the same cycle as the display cycle of the image displayed on the display panel. A liquid crystal display device that is controlled.

本発明の一は、バックライトと、表示パネルを有する液晶表示装置であって、バックライ

トは、明るさを個別に制御できる複数の単位領域に分割され、表示パネルは、単位領域の

数よりも多い数の画素を有し、バックライトは、明るさを制御できる段階の数が3段階以

上であり、表示パネルは、明るさを制御できる段階の数がn段階(nは2以上の整数)で

あり、液晶表示装置全体として表示できる明るさの段階の数がn段階よりも多いことを特

徴とする液晶表示装置である。

One aspect of the present invention is a liquid crystal display device having a backlight and a display panel, and the backlight is divided into a plurality of unit regions whose brightness can be individually controlled, and the display panel is more than the number of unit regions. It has a large number of pixels, the backlight has three or more stages in which the brightness can be controlled, and the display panel has n stages in which the brightness can be controlled (n is an integer of 2 or more). The liquid crystal display device is characterized in that the number of brightness steps that can be displayed as a whole liquid crystal display device is greater than n steps.

本発明において、バックライトは、明るさを制御できる段階の数が3段階以上であり、表

示パネルは、明るさを制御できる段階の数がn段階(nは2以上の整数)であり、表示装

置全体として表示できる明るさの段階の数がn段階よりも多い構成であってもよい。

In the present invention, the backlight has three or more stages in which the brightness can be controlled, and the display panel has n stages (n is an integer of 2 or more) in which the brightness can be controlled. The number of the brightness | luminance steps which can be displayed as the whole apparatus may be larger than n steps.

本発明において、液晶表示装置に入力される画像データが与える画像の明るさの平均値に

したがって、バックライトの明るさが制御される構成であってもよい。

In the present invention, the backlight brightness may be controlled in accordance with the average value of the image brightness given by the image data input to the liquid crystal display device.

本発明において、表示パネルに入力される電圧のうち、オーバードライブ電圧が含まれて

もよい。

In the present invention, an overdrive voltage may be included among the voltages input to the display panel.

本発明において、表示パネルに入力される電圧のうち、極性が周期的に切り替わる電圧が

含まれてもよい。

In the present invention, a voltage whose polarity is periodically switched among voltages input to the display panel may be included.

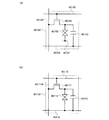

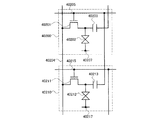

なお、スイッチは、様々な形態のものを用いることができる。例としては、電気的スイッ

チや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、

特定のものに限定されない。例えば、スイッチとして、トランジスタ(例えば、バイポー

ラトランジスタ、MOSトランジスタなど)、ダイオード(例えば、PNダイオード、P

INダイオード、ショットキーダイオード、MIM(Metal Insulator

Metal)ダイオード、MIS(Metal Insulator Semicond

uctor)ダイオード、ダイオード接続のトランジスタなど)、サイリスタなどを用い

ることが出来る。または、これらを組み合わせた論理回路をスイッチとして用いることが

出来る。

Note that various types of switches can be used. Examples include electrical switches and mechanical switches. In other words, anything that can control the current flow,

It is not limited to a specific thing. For example, as a switch, a transistor (for example, bipolar transistor, MOS transistor, etc.), a diode (for example, PN diode, P, etc.)

IN diode, Schottky diode, MIM (Metal Insulator)

Metal diode, MIS (Metal Insulator Semiconductor)

uctor) diodes, diode-connected transistors, etc.), thyristors, etc. can be used. Alternatively, a logic circuit combining these can be used as a switch.

機械的なスイッチの例としては、デジタルマイクロミラーデバイス(DMD)のように、

MEMS(マイクロ・エレクトロ・メカニカル・システム)技術を用いたスイッチがある

。そのスイッチは、機械的に動かすことが出来る電極を有し、その電極が動くことによっ

て、接続と非接続とを制御して動作する。

An example of a mechanical switch is a digital micromirror device (DMD),

There is a switch using MEMS (micro electro mechanical system) technology. The switch has an electrode that can be moved mechanically, and operates by controlling connection and disconnection by moving the electrode.

スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとし

て動作するため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流

を抑えたい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オ

フ電流が少ないトランジスタとしては、LDD領域を有するトランジスタやマルチゲート

構造を有するトランジスタ等がある。または、スイッチとして動作させるトランジスタの

ソース端子の電位が、低電位側電源(Vss、GND、0Vなど)の電位に近い状態で動

作する場合はNチャネル型トランジスタを用いることが望ましい。反対に、ソース端子の

電位が、高電位側電源(Vddなど)の電位に近い状態で動作する場合はPチャネル型ト

ランジスタを用いることが望ましい。なぜなら、Nチャネル型トランジスタではソース端

子が低電位側電源の電位に近い状態で動作するとき、Pチャネル型トランジスタではソー

ス端子が高電位側電源の電位に近い状態で動作するとき、ゲートとソースの間の電圧の絶

対値を大きくできるため、スイッチとして、より正確な動作をさせやすいからである。ソ

ースフォロワ動作をしてしまうことが少ないため、出力電圧の大きさが小さくなってしま

うことが少ないからである。

In the case where a transistor is used as a switch, the transistor operates as a mere switch, and thus the polarity (conductivity type) of the transistor is not particularly limited. However, when it is desired to suppress off-state current, it is desirable to use a transistor having a polarity with smaller off-state current. As a transistor with low off-state current, a transistor having an LDD region, a transistor having a multi-gate structure, and the like can be given. Alternatively, an N-channel transistor is preferably used in the case where the transistor operates as a switch when the potential of the source terminal of the transistor is close to the potential of the low potential power supply (Vss, GND, 0 V, or the like). On the other hand, it is desirable to use a P-channel transistor when operating in a state where the potential of the source terminal is close to the potential of the high potential side power supply (Vdd or the like). This is because an N-channel transistor operates when the source terminal is close to the potential of the low-potential side power supply, and a P-channel transistor operates when the source terminal is close to the potential of the high-potential side power supply. This is because the absolute value of the voltage between them can be increased, so that the switch can be operated more accurately. This is because the source follower operation is rare and the output voltage is less likely to decrease.

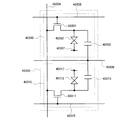

なお、Nチャネル型トランジスタとPチャネル型トランジスタの両方を用いて、CMO

S型のスイッチをスイッチとして用いてもよい。CMOS型のスイッチにすると、Pチャ

ネル型トランジスタまたはNチャネル型トランジスタのどちらか一方のトランジスタが導

通すれば電流が流れるため、スイッチとして機能しやすくなる。例えば、スイッチへの入

力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。さ

らに、スイッチをオンまたはオフさせるための信号の電圧振幅値を小さくすることが出来

るので、消費電力を小さくすることも出来る。

Note that CMO using both N-channel and P-channel transistors

An S-type switch may be used as the switch. When a CMOS switch is used, a current flows when one of the P-channel transistor and the N-channel transistor is turned on, so that the switch can easily function as a switch. For example, the voltage can be appropriately output regardless of whether the voltage of the input signal to the switch is high or low. Further, since the voltage amplitude value of the signal for turning on or off the switch can be reduced, the power consumption can be reduced.

なお、スイッチとしてトランジスタを用いる場合、スイッチは、入力端子(ソース端子

またはドレイン端子の一方)と、出力端子(ソース端子またはドレイン端子の他方)と、

導通を制御する端子(ゲート端子)とを有している。一方、スイッチとしてダイオードを

用いる場合、スイッチは、導通を制御する端子を有していない場合がある。そのため、ト

ランジスタよりもダイオードをスイッチとして用いた方が、端子を制御するための配線を

少なくすることが出来る。

Note that when a transistor is used as the switch, the switch includes an input terminal (one of a source terminal or a drain terminal), an output terminal (the other of the source terminal or the drain terminal),

And a terminal for controlling conduction (gate terminal). On the other hand, when a diode is used as the switch, the switch may not have a terminal for controlling conduction. Therefore, the use of a diode as a switch rather than a transistor can reduce the wiring for controlling the terminal.

なお、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接

続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続さ

れている場合とを含むものとする。ここで、A、Bは、対象物(例えば、装置、素子、回

路、配線、電極、端子、導電膜、層、など)であるとする。したがって、所定の接続関係

、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続

関係以外のものも含むものとする。

In addition, when it is explicitly described that A and B are connected, A and B are electrically connected, and A and B are functionally connected. , A and B are directly connected. Here, A and B are objects (for example, devices, elements, circuits, wirings, electrodes, terminals, conductive films, layers, etc.). Therefore, it is not limited to a predetermined connection relationship, for example, the connection relationship shown in the figure or text, and includes things other than the connection relation shown in the figure or text.

例えば、AとBとが電気的に接続されている場合として、AとBとの電気的な接続を可

能とする素子(例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダ

イオードなど)が、AとBとの間に1個以上配置されていてもよい。あるいは、AとBと

が機能的に接続されている場合として、AとBとの機能的な接続を可能とする回路(例え

ば、論理回路(インバータ、NAND回路、NOR回路など)、信号変換回路(DA変換

回路、AD変換回路、ガンマ補正回路など)、電位レベル変換回路(電源回路(昇圧回路

、降圧回路など)、信号の電位レベルを変えるレベルシフタ回路など)、電圧源、電流源

、切り替え回路、増幅回路(信号振幅または電流量などを大きく出来る回路、オペアンプ

、差動増幅回路、ソースフォロワ回路、バッファ回路など)、信号生成回路、記憶回路、

制御回路など)が、AとBとの間に1個以上配置されていてもよい。あるいは、AとBと

が直接接続されている場合として、AとBとの間に他の素子や他の回路を挟まずに、Aと

Bとが直接接続されていてもよい。

For example, when A and B are electrically connected, an element (for example, a switch, a transistor, a capacitor, an inductor, a resistance element, a diode, or the like) that enables electrical connection between A and B is provided. 1 or more may be arranged between A and B. Alternatively, when A and B are functionally connected, a circuit (for example, a logic circuit (an inverter, a NAND circuit, a NOR circuit, etc.), a signal conversion circuit that enables functional connection between A and B (DA conversion circuit, AD conversion circuit, gamma correction circuit, etc.), potential level conversion circuit (power supply circuit (boost circuit, step-down circuit, etc.), level shifter circuit that changes signal potential level), voltage source, current source, switching circuit , Amplifier circuits (circuits that can increase signal amplitude or current amount, operational amplifiers, differential amplifier circuits, source follower circuits, buffer circuits, etc.), signal generation circuits, memory circuits,

One or more control circuits and the like may be arranged between A and B. Alternatively, when A and B are directly connected, A and B may be directly connected without sandwiching other elements or other circuits between A and B.

なお、AとBとが直接接続されている、と明示的に記載する場合は、AとBとが直接接

続されている場合(つまり、AとBとの間に他の素子や他の回路を間に介さずに接続され

ている場合)と、AとBとが電気的に接続されている場合(つまり、AとBとの間に別の

素子や別の回路を挟んで接続されている場合)とを含むものとする。

Note that in the case where it is explicitly described that A and B are directly connected, when A and B are directly connected (that is, another element or other circuit between A and B). ) And A and B are electrically connected (that is, A and B are connected with another element or another circuit sandwiched between them). ).

なお、AとBとが電気的に接続されている、と明示的に記載する場合は、AとBとが電

気的に接続されている場合(つまり、AとBとの間に別の素子や別の回路を挟んで接続さ

れている場合)と、AとBとが機能的に接続されている場合(つまり、AとBとの間に別

の回路を挟んで機能的に接続されている場合)と、AとBとが直接接続されている場合(

つまり、AとBとの間に別の素子や別の回路を挟まずに接続されている場合)とを含むも

のとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続さ

れている、とのみ明示的に記載されている場合と同じであるとする。

Note that in the case where it is explicitly described that A and B are electrically connected, another element is connected between A and B (that is, between A and B). Or when A and B are functionally connected (that is, they are functionally connected with another circuit between A and B). And A and B are directly connected (

That is, it is assumed that A and B are connected without interposing another element or another circuit). That is, when it is explicitly described that it is electrically connected, it is the same as when it is explicitly only described that it is connected.

子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディ

スプレイ(PDP)、デジタルマイクロミラーデバイス(DMD)、圧電セラミックディ

スプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、

反射率、透過率などが変化する表示媒体を用いることができる。なお、EL素子を用いた

表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールド

エミッションディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Sur

face−conduction Electron−emitter Disply)

など、液晶素子を用いた表示装置としては液晶ディスプレイ(透過型液晶ディスプレイ、

半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型

液晶ディスプレイ)、電子インクや電気泳動素子を用いた表示装置としては電子ペーパー

がある。

Child, electronic ink, electrophoretic element, grating light valve (GLV), plasma display (PDP), digital micromirror device (DMD), piezoelectric ceramic display, carbon nanotube, etc.

A display medium whose reflectance, transmittance, and the like change can be used. An EL display is used as a display device using an EL element, and a field emission display (FED) or a SED type flat display (SED: Sur) is used as a display device using an electron-emitting device.

face-conduction electron-emitter display)

As a display device using a liquid crystal element, a liquid crystal display (a transmissive liquid crystal display,

There are electronic papers as display devices using a semi-transmissive liquid crystal display, a reflective liquid crystal display, a direct-view liquid crystal display, and a projection liquid crystal display) and electronic ink or electrophoretic elements.

なお、EL素子とは、陽極と、陰極と、陽極と陰極との間に挟まれたEL層とを有する

素子である。なお、EL層としては、1重項励起子からの発光(蛍光)を利用するもの、

3重項励起子からの発光(燐光)を利用するもの、1重項励起子からの発光(蛍光)を利

用するものと3重項励起子からの発光(燐光)を利用するものとを含むもの、有機物によ

って形成されたもの、無機物によって形成されたもの、有機物によって形成されたものと

無機物によって形成されたものとを含むもの、高分子の材料、低分子の材料、高分子の材

料と低分子の材料とを含むものなどを用いることができる。ただし、これに限定されず、

EL素子として様々なものを用いることができる。

Note that an EL element is an element having an anode, a cathode, and an EL layer sandwiched between the anode and the cathode. Note that the EL layer uses light emission (fluorescence) from singlet excitons,

Includes those that use light emission (phosphorescence) from triplet excitons, those that use light emission (fluorescence) from singlet excitons, and those that use light emission (phosphorescence) from triplet excitons , One formed by organic matter, one formed by inorganic matter, one containing organic and one formed by inorganic matter, polymer material, low molecular material, polymer material and low A material containing a molecular material can be used. However, it is not limited to this,

Various EL elements can be used.

なお、電子放出素子とは、先鋭な陰極に高電界を集中して電子を引き出す素子である。例

えば、電子放出素子として、スピント型、カーボンナノチューブ(CNT)型、金属―絶

縁体―金属を積層したMIM(Metal−Insulator−Metal)型、金属

―絶縁体―半導体を積層したMIS(Metal−Insulator−Semicon

ductor)型、MOS型、シリコン型、薄膜ダイオード型、ダイヤモンド型、表面伝

導エミッタSCD型、オード型、ダイヤモンド型、表面伝導エミッタSCD型、金属―絶

縁体―半導体−金属型等の薄膜型、HEED型、EL型、ポーラスシリコン型、表面伝導

(SED)型などを用いることができる。ただし、これに限定されず、電子放出素子とし

て様々なものを用いることができる。

The electron-emitting device is an element that draws electrons by concentrating a high electric field on a sharp cathode. For example, as an electron-emitting device, a Spindt type, a carbon nanotube (CNT) type, a metal-insulator-metal laminated MIM (Metal-Insulator-Metal) type, and a metal-insulator-semiconductor laminated MIS (Metal-Insulator). -Semicon

(ductor) type, MOS type, silicon type, thin film diode type, diamond type, surface conduction emitter SCD type, ode type, diamond type, surface conduction emitter SCD type, metal-insulator-semiconductor-metal thin film type, HEED, etc. A type, an EL type, a porous silicon type, a surface conduction (SED) type, or the like can be used. However, the present invention is not limited to this, and various types of electron-emitting devices can be used.

なお、液晶素子とは、液晶の光学的変調作用によって光の透過または非透過を制御する素

子であり、一対の電極、及び液晶により構成される。なお、液晶の光学的変調作用は、液

晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御

される。なお、液晶素子としては、ネマチック液晶、コレステリック液晶、スメクチック

液晶、ディスコチック液晶、サーモトロピック液晶、ライオトロピック液晶、リオトロピ

ック液晶、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高

分子液晶、プラズマアドレス液晶(PDLC)、バナナ型液晶、TN(Twisted

Nematic)モード、STN(Super Twisted Nematic)モー

ド、IPS(In−Plane−Switching)モード、FFS(Fringe

Field Switching)モード、MVA(Multi−domain Ver

tical Alignment)モード、PVA(Patterned Vertic

al Alignment)、ASV(Advanced Super View)モー

ド、ASM(Axially Symmetric aligned Micro−ce

ll)モード、OCB(Optical Compensated Birefring

ence)モード、ECB(Electrically Controlled Bir

efringence)モード、FLC(Ferroelectric Liquid

Crystal)モード、AFLC(AntiFerroelectric Liqui

d Crystal)モード、PDLC(Polymer Dispersed Liq

uid Crystal)モード、ゲストホストモードなどを用いることができる。ただ

し、これに限定されず、液晶素子として様々なものを用いることができる。

Note that a liquid crystal element is an element that controls transmission or non-transmission of light by an optical modulation action of liquid crystal, and includes a pair of electrodes and liquid crystal. Note that the optical modulation action of the liquid crystal is controlled by an electric field applied to the liquid crystal (including a horizontal electric field, a vertical electric field, or an oblique electric field). Liquid crystal elements include nematic liquid crystal, cholesteric liquid crystal, smectic liquid crystal, discotic liquid crystal, thermotropic liquid crystal, lyotropic liquid crystal, lyotropic liquid crystal, low molecular liquid crystal, polymer liquid crystal, ferroelectric liquid crystal, antiferroelectric liquid crystal, main chain. Type liquid crystal, side chain type polymer liquid crystal, plasma addressed liquid crystal (PDLC), banana type liquid crystal, TN (Twisted)

Nematic) mode, STN (Super Twisted Nematic) mode, IPS (In-Plane-Switching) mode, FFS (Fringe)

Field Switching mode, MVA (Multi-domain Ver.)

tick alignment mode, PVA (Patterned Vertic)

al Alignment), ASV (Advanced Super View) mode, ASM (Axial Symmetrical Aligned Micro-ce)

ll) mode, OCB (Optical Compensated Birefring)

ence) mode, ECB (Electrically Controlled Bird)

efficiency mode, FLC (Ferroelectric Liquid)

Crystal) mode, AFLC (Antiferroelectric Liquid)

d Crystal) mode, PDLC (Polymer Dispersed Liq)

uid Crystal) mode, guest host mode, etc. can be used. However, the present invention is not limited to this, and various liquid crystal elements can be used.

なお、電子ペーパーとしては、光学異方性と染料分子配向のような分子により表示される

もの、電気泳動、粒子移動、粒子回転、相変化のような粒子により表示されるもの、フィ

ルムの一端が移動することにより表示されるもの、分子の発色/相変化により表示される

もの、分子の光吸収により表示されるもの、電子とホールが結合して時発光により表示さ

れるものなどのことをいう。例えば、電子ペーパーとして、マイクロカプセル型電気泳動

、水平移動型電気泳動、垂直移動型電気泳動、球状ツイストボール、磁気ツイストボール

、円柱ツイストボール方式、帯電トナー、電子粉流体、磁気泳動型、磁気感熱式、エレク

トロウェッテイング、光散乱(透明白濁)、コレステリック液晶/光導電層、コレステリ

ック液晶、双安定性ネマチック液晶、強誘電性液晶、2色性色素・液晶分散型、可動フィ

ルム、ロイコ染料発消色、フォトクロミック、エレクトロクロミック、エレクトロデポジ

ション、フレキシブル有機ELなどを用いることができる。ただし、これに限定されず、

電子ペーパーとして様々なものを用いることができる。ここで、マイクロカプセル型電気

泳動を用いることによって、電気泳動方式の欠点である泳動粒子の凝集、沈殿を解決する

ことができる。電子粉流体は、高速応答性、高反射率、広視野角、低消費電力、メモリー

性などのメリットを有する。

Electronic paper includes those displayed by molecules such as optical anisotropy and dye molecule orientation, those displayed by particles such as electrophoresis, particle movement, particle rotation, and phase change. It is displayed by moving, displayed by color development / phase change of molecules, displayed by light absorption of molecules, displayed by light emission when electrons and holes are combined, etc. . For example, as electronic paper, microcapsule type electrophoresis, horizontal movement type electrophoresis, vertical movement type electrophoresis, spherical twist ball, magnetic twist ball, cylindrical twist ball method, charged toner, electronic powder fluid, magnetophoretic type, magnetic heat sensitivity Formula, electrowetting, light scattering (transparent white turbidity), cholesteric liquid crystal / photoconductive layer, cholesteric liquid crystal, bistable nematic liquid crystal, ferroelectric liquid crystal, dichroic dye / liquid crystal dispersion type, movable film, leuco dye extinction Color, photochromic, electrochromic, electrodeposition, flexible organic EL, etc. can be used. However, it is not limited to this,

Various electronic papers can be used. Here, by using microcapsule electrophoresis, aggregation and precipitation of electrophoretic particles, which is a drawback of the electrophoresis system, can be solved. The electronic powder fluid has advantages such as high-speed response, high reflectivity, wide viewing angle, low power consumption, and memory properties.

なお、プラズマディスプレイは、電極を表面に形成した基板と、電極及び微小な溝を表面

に形成し且つ溝内に蛍光体層を形成した基板とを狭い間隔で対向させて、希ガスを封入し

た構造を有する。なお、電極間に電圧をかけることによって紫外線を発生させ、蛍光体を

光らせることで、表示を行うことができる。なお、プラズマディスプレイとしては、DC

型PDP、AC型PDPでもよい。ここで、プラズマディスプレイパネルとしては、AS

W(Address While Sustain)駆動、サブフレームをリセット期間

、アドレス期間、維持期間に分割するADS(Address Display Sep

arated)駆動、CLEAR(Low Energy Address and R

eduction of False Contour Sequence)駆動、AL

IS(Alternate Lighting of Surfaces)方式、TER

ES(Techbology of Reciprocal Susfainer)駆動

などを用いることができる。ただし、これに限定されず、プラズマディスプレイとして様

々なものを用いることができる。

Note that the plasma display encloses a rare gas with a substrate having an electrode formed on the surface and a substrate having an electrode and a minute groove formed on the surface and a phosphor layer formed in the groove facing each other at a narrow interval. It has a structure. In addition, a display can be performed by generating an ultraviolet-ray by applying a voltage between electrodes and making fluorescent substance light. As a plasma display, DC

It may be a type PDP or an AC type PDP. Here, as a plasma display panel, AS

W (Address While Sustain) drive, ADS (Address Display Sep) that divides subframe into reset period, address period, and sustain period

driven), CLEAR (Low Energy Address and R)

instruction of false control sequence) drive, AL

IS (Alternate Lightning of Surfaces) method, TER

An ES (Technology of Reciprocal Susfainer) drive or the like can be used. However, the present invention is not limited to this, and various types of plasma displays can be used.

なお、光源を必要とする表示装置、例えば、液晶ディスプレイ(透過型液晶ディスプレイ

、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射

型液晶ディスプレイ)、グレーティングライトバルブ(GLV)を用いた表示装置、デジ

タルマイクロミラーデバイス(DMD)を用いた表示装置などの光源としては、エレクト

ロルミネッセンス、冷陰極管、熱陰極管、LED、レーザー光源、水銀ランプなどを用い

ることができる。ただし、これに限定されず、光源して様々なものを用いることができる

。

Note that a display device that requires a light source, such as a liquid crystal display (transmission type liquid crystal display, transflective type liquid crystal display, reflection type liquid crystal display, direct view type liquid crystal display, projection type liquid crystal display), or a grating light valve (GLV) is used. As a light source for a display device using a conventional display device or a digital micromirror device (DMD), electroluminescence, a cold cathode tube, a hot cathode tube, an LED, a laser light source, a mercury lamp, or the like can be used. However, the present invention is not limited to this, and various light sources can be used.

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定され

ない。例えば、ゲート電極が2個以上のマルチゲート構造を用いてもよい。マルチゲート

構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続

された構成となる。マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上

による信頼性の向上を図ることができる。あるいは、マルチゲート構造により、飽和領域

で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があま

り変化せず、電圧・電流特性の傾きがフラットな特性にすることができる。電圧・電流特

性の傾きがフラットである特性を利用すると、理想的な電流源回路や、非常に高い抵抗値

をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路やカレントミラ

ー回路を実現することが出来る。別の例として、チャネルの上下にゲート電極が配置され

ている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることによ

り、チャネル領域が増えるため、電流値の増加、又は空乏層ができやすくなることによる

S値の低減を図ることができる。チャネルの上下にゲート電極が配置されると、複数のト

ランジスタが並列に接続されたような構成となる。

Note that the structure of the transistor can take a variety of forms. It is not limited to a specific configuration. For example, a multi-gate structure having two or more gate electrodes may be used. When the multi-gate structure is employed, the channel regions are connected in series, so that a plurality of transistors are connected in series. With the multi-gate structure, the off-state current can be reduced and the reliability can be improved by improving the withstand voltage of the transistor. Or, when operating in the saturation region, the drain-source current does not change much even when the drain-source voltage changes, and the slope of the voltage / current characteristic is flat due to the multi-gate structure. it can. By using the characteristic that the slope of the voltage / current characteristic is flat, an ideal current source circuit and an active load having a very high resistance value can be realized. As a result, a differential circuit or a current mirror circuit with good characteristics can be realized. As another example, a structure in which gate electrodes are arranged above and below a channel may be used. With the structure in which the gate electrodes are arranged above and below the channel, the channel region increases, so that the current value can be increased or the S value can be reduced because a depletion layer can be easily formed. When gate electrodes are provided above and below a channel, a structure in which a plurality of transistors are connected in parallel is obtained.

あるいは、チャネル領域の上にゲート電極が配置されている構造でもよいし、チャネル

領域の下にゲート電極が配置されている構造でもよい。あるいは、正スタガ構造または逆

スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、チャネル領

域が並列に接続されていてもよいし、チャネル領域が直列に接続されていてもよい。ある

いは、チャネル領域(もしくはその一部)にソース電極やドレイン電極が重なっていても

よい。チャネル領域(もしくはその一部)にソース電極やドレイン電極が重なる構造にす

ることにより、チャネル領域の一部に電荷がたまって、動作が不安定になることを防ぐこ

とができる。あるいは、LDD領域を設けても良い。LDD領域を設けることにより、オ

フ電流の低減、又はトランジスタの耐圧向上による信頼性の向上を図ることができる。あ

るいは、LDD領域を設けることにより、飽和領域で動作する時に、ドレイン・ソース間

電圧が変化しても、ドレイン・ソース間電流があまり変化せず、電圧・電流特性の傾きが

フラットな特性にすることができる。

Alternatively, a structure in which a gate electrode is disposed over a channel region may be employed, or a structure in which a gate electrode is disposed under a channel region may be employed. Alternatively, a normal stagger structure or an inverted stagger structure may be used, the channel region may be divided into a plurality of regions, the channel regions may be connected in parallel, or the channel regions may be connected in series. Good. Alternatively, a source electrode or a drain electrode may overlap with the channel region (or a part thereof). With the structure in which the source electrode or the drain electrode overlaps with the channel region (or part thereof), it is possible to prevent electric charges from being accumulated in part of the channel region and unstable operation. Alternatively, an LDD region may be provided. By providing the LDD region, the off-state current can be reduced or the reliability can be improved by improving the withstand voltage of the transistor. Alternatively, by providing an LDD region, when operating in the saturation region, even if the drain-source voltage changes, the drain-source current does not change so much and the slope of the voltage-current characteristic is flat. be able to.

なお、トランジスタは、様々なタイプを用いることができ、様々な基板を用いて形成さ

せることができる。したがって、所定の機能を実現させるために必要な回路の全てが、同

一の基板に形成されていてもよい。例えば、所定の機能を実現させるために必要な回路の

全てが、ガラス基板、プラスチック基板、単結晶基板、またはSOI基板を用いて形成さ

れていてもよく、さまざまな基板を用いてに形成されていてもよい。所定の機能を実現さ

せるために必要な回路の全てが同じ基板を用いて形成されていることにより、部品点数の

削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図るこ

とができる。あるいは、所定の機能を実現させるために必要な回路の一部が、ある基板に

形成されており、所定の機能を実現させるために必要な回路の別の一部が、別の基板に形

成されていてもよい。つまり、所定の機能を実現させるために必要な回路の全てが同じ基

板を用いて形成されていなくてもよい。例えば、所定の機能を実現させるために必要な回

路の一部は、ガラス基板上にトランジスタを用いて形成され、所定の機能を実現させるた

めに必要な回路の別の一部は、単結晶基板に形成され、単結晶基板を用いて形成されたト

ランジスタで構成されたICチップをCOG(Chip On Glass)でガラス基

板に接続して、ガラス基板上にそのICチップを配置してもよい。あるいは、そのICチ

ップをTAB(Tape Automated Bonding)やプリント基板を用い

てガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されているこ

とにより、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による

信頼性の向上を図ることができる。あるいは、駆動電圧が高い部分及び駆動周波数が高い

部分の回路は、消費電力が大きくなってしまうので、そのような部分の回路は同じ基板に

形成せず、そのかわりに、例えば、単結晶基板にその部分の回路を形成して、その回路で

構成されたICチップを用いるようにすれば、消費電力の増加を防ぐことができる。