JP2013125890A - Photoelectric conversion element and manufacturing method of the same - Google Patents

Photoelectric conversion element and manufacturing method of the same Download PDFInfo

- Publication number

- JP2013125890A JP2013125890A JP2011274354A JP2011274354A JP2013125890A JP 2013125890 A JP2013125890 A JP 2013125890A JP 2011274354 A JP2011274354 A JP 2011274354A JP 2011274354 A JP2011274354 A JP 2011274354A JP 2013125890 A JP2013125890 A JP 2013125890A

- Authority

- JP

- Japan

- Prior art keywords

- type

- type amorphous

- film

- photoelectric conversion

- conversion element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

Abstract

Description

この発明は、光電変換素子およびその製造方法に関するものである。 The present invention relates to a photoelectric conversion element and a manufacturing method thereof.

バックコンタクト型太陽電池は、従来、受光面側にあったpn接合および電極を裏面側に形成することで、受光面側の電極による影を無くし、太陽光をより吸収させることで、高効率を得る太陽電池である。 The back contact solar cell has a high efficiency by forming a pn junction and an electrode on the light receiving surface side on the back surface, thereby eliminating shadows from the electrode on the light receiving surface side and absorbing more sunlight. Solar cell to get.

そして、この種の太陽電池においては、pn接合としてヘテロ接合を用いる太陽電池も提案されている(特許文献1)。この太陽電池は、半導体基板の裏面にi型アモルファスシリコン(a−Si)およびn型a−Siを順次積層し、その積層したi型a−Siおよびn型a−Siの一部分を除去し、その除去した一部分にi型a−Siおよびp型a−Siを順次積層した構造からなる。 And in this kind of solar cell, the solar cell which uses a heterojunction as a pn junction is also proposed (patent document 1). In this solar cell, i-type amorphous silicon (a-Si) and n-type a-Si are sequentially laminated on the back surface of the semiconductor substrate, and a part of the laminated i-type a-Si and n-type a-Si is removed. The removed part has a structure in which i-type a-Si and p-type a-Si are sequentially laminated.

また、受光面側の構造に関しては、ヘテロ接合を用いないバックコンタクト型の太陽電池において用いられているFSF拡散層、シリコンナイトライド(SiN)および二酸化シリコン(SiO2)のようなパッシベーション膜に加えて、アモルファスシリコン膜によってパッシベーションする方法が提案されている(非特許文献1)。 In addition, regarding the structure on the light receiving surface side, in addition to a passivation film such as an FSF diffusion layer, silicon nitride (SiN), and silicon dioxide (SiO 2 ) used in a back contact solar cell that does not use a heterojunction. Thus, a method of passivation with an amorphous silicon film has been proposed (Non-Patent Document 1).

しかし、従来の太陽電池のように、単結晶シリコン基板の光入射側の表面をアモルファスシリコン膜によってパッシベーションした場合、単結晶シリコン基板に対するパッシベーションの効果が低いという問題がある。 However, when the surface on the light incident side of a single crystal silicon substrate is passivated with an amorphous silicon film as in a conventional solar cell, there is a problem that the effect of passivation on the single crystal silicon substrate is low.

そこで、この発明の実施の形態によれば、半導体基板に対するパッシベーションの効果を向上可能な光電変換素子を提供する。 Therefore, according to the embodiment of the present invention, a photoelectric conversion element capable of improving the effect of passivation to a semiconductor substrate is provided.

また、この発明の実施の形態によれば、半導体基板に対するパッシベーションの効果を向上可能な光電変換素子の製造方法を提供する。 Moreover, according to the embodiment of the present invention, there is provided a method for manufacturing a photoelectric conversion element capable of improving the effect of passivation to a semiconductor substrate.

この発明の実施の形態によれば、光電変換素子は、半導体基板と、酸化膜と、第1から第3の非晶質膜とを備える。半導体基板は、第1の導電型を有する単結晶シリコンからなる。酸化膜は、半導体基板の光入射側の表面に接して設けられる。第1の非晶質膜は、酸化膜に接して設けられ、第1の導電型を有する。第2の非晶質膜は、半導体基板の光入射側の表面と反対側に設けられ、第1の導電型と反対の第2の導電型を有する。第3の非晶質膜は、半導体基板の面内方向において第2の非晶質膜に隣接して半導体基板の光入射側の表面と反対側に設けられ、第1の導電型を有する。 According to the embodiment of the present invention, the photoelectric conversion element includes a semiconductor substrate, an oxide film, and first to third amorphous films. The semiconductor substrate is made of single crystal silicon having the first conductivity type. The oxide film is provided in contact with the surface on the light incident side of the semiconductor substrate. The first amorphous film is provided in contact with the oxide film and has the first conductivity type. The second amorphous film is provided on the opposite side of the light incident side surface of the semiconductor substrate and has a second conductivity type opposite to the first conductivity type. The third amorphous film is provided adjacent to the second amorphous film in the in-plane direction of the semiconductor substrate, on the opposite side of the light incident surface of the semiconductor substrate, and has the first conductivity type.

また、この発明の実施の形態によれば、光電変換素子の製造方法は、第1の導電型を有する単結晶シリコンからなる半導体基板の光入射側の表面に接して酸化膜を形成する第1の工程と、第1の工程の後、酸化膜に接して第1の導電型を有する第1の非晶質膜を堆積する第2の工程と、第1の工程の後、半導体基板の光入射側の表面と反対側に第1の導電型と反対の第2の導電型を有する第2の非晶質膜を堆積する第3の工程と、半導体基板の面内方向において第2の非晶質膜に隣接して半導体基板の光入射側の表面と反対側に第1の導電型を有する第3の非晶質膜を堆積する第4の工程とを備える。 According to the embodiment of the present invention, in the method for manufacturing a photoelectric conversion element, the oxide film is formed in contact with the light incident surface of the semiconductor substrate made of single crystal silicon having the first conductivity type. After the first step, after the first step, the second step of depositing the first amorphous film having the first conductivity type in contact with the oxide film, and after the first step, the light of the semiconductor substrate A third step of depositing a second amorphous film having a second conductivity type opposite to the first conductivity type on the side opposite to the surface on the incident side; and a second step in the in-plane direction of the semiconductor substrate. And a fourth step of depositing a third amorphous film having the first conductivity type on the opposite side of the light incident side surface of the semiconductor substrate adjacent to the crystalline film.

この発明の実施の形態による光電変換素子においては、半導体基板の光入射側の表面に接して酸化膜が設けられ、第1の非晶質膜が酸化膜に接して設けられる。その結果、半導体基板の光入射側の表面付近に存在するキャリア(電子および正孔)は、酸化膜による半導体基板のパッシベーション効果と、第1の非晶質膜によるFSF効果(表面電界効果)とによって再結合が抑制される。 In the photoelectric conversion element according to the embodiment of the present invention, the oxide film is provided in contact with the light incident side surface of the semiconductor substrate, and the first amorphous film is provided in contact with the oxide film. As a result, carriers (electrons and holes) existing near the surface on the light incident side of the semiconductor substrate cause the passivation effect of the semiconductor substrate by the oxide film and the FSF effect (surface field effect) by the first amorphous film. Suppresses recombination.

従って、半導体基板に対するパッシベーションの効果を向上できる。 Therefore, the effect of passivation on the semiconductor substrate can be improved.

また、この発明の実施の形態による光電変換素子の製造方法においては、酸化膜が半導体基板の光入射側の表面に接して設けられ、第1の非晶質膜が酸化膜に接して設けられる。その結果、半導体基板の光入射側の表面付近に存在するキャリア(電子および正孔)は、上述したように、再結合が抑制される。 In the method of manufacturing a photoelectric conversion element according to the embodiment of the present invention, the oxide film is provided in contact with the light incident side surface of the semiconductor substrate, and the first amorphous film is provided in contact with the oxide film. . As a result, recombination of the carriers (electrons and holes) existing near the light incident surface of the semiconductor substrate is suppressed as described above.

従って、半導体基板に対するパッシベーションの効果を向上できる。 Therefore, the effect of passivation on the semiconductor substrate can be improved.

更に、この発明の実施の形態による光電変換素子の製造方法においては、最初に、酸化膜が半導体基板の光入射側の表面に接して設けられ、その後、第1から第3の非晶質膜が形成される。 Furthermore, in the method for manufacturing a photoelectric conversion element according to the embodiment of the present invention, first, an oxide film is provided in contact with the light incident side surface of the semiconductor substrate, and then the first to third amorphous films are formed. Is formed.

従って、光電変換素子の製造プロセスにおいて、半導体基板の光入射側の表面を保護できる。 Therefore, the surface on the light incident side of the semiconductor substrate can be protected in the manufacturing process of the photoelectric conversion element.

本発明の実施の形態について図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰返さない。 Embodiments of the present invention will be described in detail with reference to the drawings. In the drawings, the same or corresponding parts are denoted by the same reference numerals and description thereof will not be repeated.

この明細書において、「非晶質相」とは、シリコン(Si)原子等がランダムに配列された状態を言う。また、アモルファスシリコンを「a−Si」と表記するが、この表記は、実際には、水素(H)原子が含まれていることを意味する。アモルファスシリコンカーバイド(a−SiC)、アモルファスシリコンオキサイド(a−SiO)、アモルファスシリコンナイトライド(a−SiN)、アモルファスシリコンカーボンナイトライド(a−SiCN)、アモルファスシリコンゲルマニウム(a−SiGe)およびアモルファスゲルマニウム(a−Ge)についても、同様に、H原子が含まれていることを意味する。 In this specification, the “amorphous phase” refers to a state in which silicon (Si) atoms and the like are randomly arranged. Moreover, although amorphous silicon is described as “a-Si”, this notation actually means that hydrogen (H) atoms are included. Amorphous silicon carbide (a-SiC), amorphous silicon oxide (a-SiO), amorphous silicon nitride (a-SiN), amorphous silicon carbon nitride (a-SiCN), amorphous silicon germanium (a-SiGe) and amorphous germanium Similarly, (a-Ge) means that an H atom is contained.

[実施の形態1]

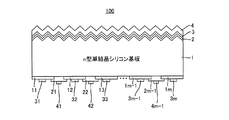

図1は、この発明の実施の形態1による光電変換素子の構成を示す断面図である。図1を参照して、この発明の実施の形態1による光電変換素子100は、n型単結晶シリコン基板1と、酸化膜2と、n型非晶質膜3,21〜2m−1(mは2以上の整数)と、反射防止膜4と、p型非晶質膜11〜1mと、電極31〜3m,41〜4m−1とを備える。

[Embodiment 1]

1 is a cross-sectional view showing a configuration of a photoelectric conversion element according to

n型単結晶シリコン基板1は、例えば、(100)の面方位および0.1〜1.0Ω・cmの比抵抗を有する。また、n型単結晶シリコン基板1は、例えば、100〜300μmの厚みを有し、好ましくは、100〜200μmの厚みを有する。そして、n型単結晶シリコン基板1は、光入射側の表面がテクスチャ化されている。

The n-type single

酸化膜2は、二酸化シリコン(SiO2)からなり、n型単結晶シリコン基板1の光入射側の表面に接して設けられる。そして、酸化膜2は、例えば、数nmの膜厚を有する。

The

n型非晶質膜3は、非晶質相からなり、例えば、n型a−Siからなる。また、n型非晶質膜3は、例えば、10nm〜数十nmの膜厚を有する。更に、n型非晶質層3のリン(P)濃度は、1×1018cm−3〜1×1020cm−3である。そして、n型非晶質膜3は、酸化膜2に接して形成される。

The n-type

反射防止膜4は、例えば、シリコンナイトライド(Si3N4)からなり、膜厚は、例えば、100nmである。そして、反射防止膜4は、n型非晶質膜3に接して設けられる。

The

p型非晶質膜11〜1mの各々は、非晶質相からなり、n型単結晶シリコン基板1の光入射側と反対側の表面に接して設けられる。そして、p型非晶質膜11〜1mの各々は、例えば、p型a−Siからなり、膜厚は、例えば、10nmである。また、p型非晶質膜11〜1mは、n型単結晶シリコン基板1の面内方向において所望の間隔で配置される。更に、p型非晶質膜11〜1mの各々におけるボロン(B)濃度は、例えば、5×1019cm−3である。

Each of p-type

n型非晶質膜21〜2m−1の各々は、非晶質相からなる。n型非晶質膜21は、p型非晶質膜11,12およびn型単結晶シリコン基板1に接して配置され、n型非晶質膜22は、p型非晶質膜12,13およびn型単結晶シリコン基板1に接して配置され、以下、同様にして、n型非晶質膜2m−1は、p型非晶質膜1m−1,1mおよびn型単結晶シリコン基板1に接して配置される。

Each of the n-type

そして、n型非晶質膜21〜2m−1の各々は、例えば、n型a−Siからなり、膜厚は、例えば、10nmである。また、n型非晶質膜21〜2m−1の各々におけるP濃度は、例えば、5×1019cm−3である。

Each of the n-type

電極31〜3mは、それぞれ、p型非晶質膜11〜1mに接して設けられる。電極41〜4m−1は、それぞれ、n型非晶質膜21〜2m−1に接して設けられる。そして、電極31〜3m,41〜4m−1の各々は、例えば、銀(Ag)からなる。

The

p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1は、図1の紙面に垂直な方向において同じ長さを有する。そして、p型非晶質膜11〜1mの全体の面積がn型単結晶シリコン基板1の面積に占める割合である面積占有率は、60〜93%であり、n型非晶質膜21〜2m−1の全体の面積がn型単結晶シリコン基板1の面積に占める割合である面積占有率は、5〜20%である。

The p-type amorphous films 11-1m and the n-type amorphous films 21-2m-1 have the same length in the direction perpendicular to the paper surface of FIG. The area occupation ratio, which is the ratio of the entire area of the p-type

このように、p型非晶質膜11〜1mの面積占有率をn型非晶質膜21〜2m−1の面積占有率よりも大きくするのは、n型単結晶シリコン基板1中で光励起された電子および正孔がpn接合(p型非晶質膜11〜1m/n型単結晶シリコン基板1)によって分離され易くし、光励起された電子および正孔の発電への寄与率を高くするためである。

As described above, the area occupancy of the p-type

図2〜図4は、それぞれ、図1に示す光電変換素子100の製造方法を示す第1〜第3の工程図である。

2-4 is a 1st-3rd process drawing which respectively shows the manufacturing method of the

光電変換素子100の製造方法について説明する。光電変換素子100は、プラズマ装置を主に用いてプラズマCVD法によって製造される。

A method for manufacturing the

プラズマ装置は、仕込室と、反応室CB1〜CB3と、取出室と、整合器と、RF電源とを備える。仕込室、反応室CB1〜CB3および取出室は、直列に配置されている。そして、仕込室と反応室CB1との間、反応室CB1と反応室CB2との間、反応室CB2と反応室CB3との間、および反応室CB3と取出室との間は、仕切バルブで仕切られている。また、仕込室から反応室CB1、反応室CB2、反応室CB3および取出室へ単結晶シリコン基板を順次搬送する搬送機構がプラズマ装置に備えられている。 The plasma apparatus includes a preparation chamber, reaction chambers CB1 to CB3, an extraction chamber, a matching unit, and an RF power source. The charging chamber, the reaction chambers CB1 to CB3, and the take-out chamber are arranged in series. A partition valve is used to partition between the charging chamber and the reaction chamber CB1, between the reaction chamber CB1 and the reaction chamber CB2, between the reaction chamber CB2 and the reaction chamber CB3, and between the reaction chamber CB3 and the take-out chamber. It has been. Further, the plasma apparatus is provided with a transport mechanism for sequentially transporting the single crystal silicon substrate from the preparation chamber to the reaction chamber CB1, the reaction chamber CB2, the reaction chamber CB3, and the take-out chamber.

仕込室は、加熱機構と排気機構とを備える。加熱機構は、単結晶シリコン基板を所定の温度に昇温する。排気機構は、仕込室内のガスを排気し、仕込室の到達圧力を、例えば、1×10−5Pa以下に設定する。 The charging chamber includes a heating mechanism and an exhaust mechanism. The heating mechanism raises the temperature of the single crystal silicon substrate to a predetermined temperature. The exhaust mechanism exhausts the gas in the preparation chamber, and sets the ultimate pressure in the preparation chamber to, for example, 1 × 10 −5 Pa or less.

反応室CB1〜CB3の各々は、平行平板電極と、加熱機構と、排気機構とを備える。加熱機構は、単結晶シリコン基板を所定の温度に昇温する。排気機構は、反応室CB1〜CB3内のガスを排気し、反応室CB1〜CB3の到達圧力を、例えば、1×10−5Pa以下に設定する。平行平板電極は、整合器を介してRF電源に接続される。なお、反応室CB1は、p型a−Siを堆積するための反応室であり、反応室CB2は、n型a−Siを堆積するための反応室であり、反応室CB3は、i型a−Siを堆積するための反応室である。 Each of the reaction chambers CB1 to CB3 includes a parallel plate electrode, a heating mechanism, and an exhaust mechanism. The heating mechanism raises the temperature of the single crystal silicon substrate to a predetermined temperature. The exhaust mechanism exhausts the gases in the reaction chambers CB1 to CB3, and sets the ultimate pressure in the reaction chambers CB1 to CB3 to, for example, 1 × 10 −5 Pa or less. The parallel plate electrodes are connected to an RF power source through a matching unit. The reaction chamber CB1 is a reaction chamber for depositing p-type a-Si, the reaction chamber CB2 is a reaction chamber for depositing n-type a-Si, and the reaction chamber CB3 is an i-type a A reaction chamber for depositing Si.

取出室は、排気機構を備える。排気機構は、取出室内のガスを排気し、取出室の到達圧力を、例えば、1×10−5Pa以下に設定する。 The take-out chamber includes an exhaust mechanism. The exhaust mechanism exhausts the gas in the extraction chamber and sets the ultimate pressure in the extraction chamber to, for example, 1 × 10 −5 Pa or less.

仕込室、反応室CB1〜CB3および取出室の各排気機構は、ターボ分子ポンプ、メカニカルブースタポンプおよびロータリーポンプからなる。ターボ分子ポンプ、メカニカルブースタポンプおよびロータリーポンプは、ターボ分子ポンプが仕込室、反応室CB1〜CB3および取出室に最も近くなるように、それぞれ、仕込室、反応室CB1〜CB3および取出室に直列的に連結されている。そして、各排気機構は、ターボ分子ポンプ、メカニカルブースタポンプおよびロータリーポンプによって、それぞれ、仕込室、反応室CB1〜CB3および取出室内のガスを排気し、またはメカニカルブースタポンプおよびロータリーポンプによって、それぞれ、仕込室、反応室CB1〜CB3および取出室内のガスを排気する。 Each exhaust mechanism of the charging chamber, the reaction chambers CB1 to CB3, and the take-out chamber includes a turbo molecular pump, a mechanical booster pump, and a rotary pump. The turbo molecular pump, the mechanical booster pump and the rotary pump are serially connected to the charging chamber, the reaction chambers CB1 to CB3 and the extraction chamber, respectively, so that the turbo molecular pump is closest to the charging chamber, the reaction chambers CB1 to CB3 and the extraction chamber. It is connected to. Each exhaust mechanism exhausts the gas in the charging chamber, reaction chambers CB1 to CB3, and the extraction chamber with a turbo molecular pump, a mechanical booster pump, and a rotary pump, respectively, or is charged with a mechanical booster pump and a rotary pump, respectively. The gases in the chamber, reaction chambers CB1 to CB3 and the extraction chamber are exhausted.

RF電源は、例えば、13.56MHzのRF電力を整合器を介して反応室CB1〜CB3の平行平板電極に印加する。 The RF power source applies, for example, RF power of 13.56 MHz to the parallel plate electrodes of the reaction chambers CB1 to CB3 via the matching unit.

光電変換素子100の製造が開始されると、n型単結晶シリコン基板1をエタノール等で超音波洗浄して脱脂し(図2の工程(a)参照)、n型単結晶シリコン基板1の表面をアルカリを用いて化学的に異方性エッチングし、n型単結晶シリコン基板1の表面をテクスチャ化する(図2の工程(b)参照)。

When the manufacture of the

その後、n型単結晶シリコン基板1をフッ酸中に浸漬してn型単結晶シリコン基板1の表面に形成された自然酸化膜を除去するとともに、n型単結晶シリコン基板1の表面を水素で終端する。

Thereafter, the n-type single

n型単結晶シリコン基板1の洗浄が終了すると、n型単結晶シリコン基板1を酸化炉に入れ、1000℃の温度で酸素雰囲気中でn型単結晶シリコン基板1を熱酸化する。この場合、酸化時間は、例えば、数分である。そして、n型単結晶シリコン基板1の片側の表面および端面に形成されたSiO2をフッ酸によって除去し、n型単結晶シリコン基板1のテクスチャ化された表面にSiO2からなる酸化膜2を形成する(図2の工程(c)参照)。

When the cleaning of the n-type single

そして、n型単結晶シリコン基板1/酸化膜2をプラズマ装置の仕込室の基板ホルダー上に配置する。

Then, the n-type single

その後、仕込室の排気機構は、1×10−5Pa以下に仕込室内のガスを排気し、仕込室の加熱機構は、n型単結晶シリコン基板1/酸化膜2の温度を200℃に設定するように基板ホルダーを加熱する。また、反応室CB1〜CB3の加熱機構も、n型単結晶シリコン基板1/酸化膜2の温度を200℃に設定するように基板ホルダーを加熱する。

After that, the evacuation mechanism in the preparation chamber exhausts the gas in the preparation chamber to 1 × 10 −5 Pa or less, and the heating mechanism in the preparation chamber sets the temperature of the n-type single

n型単結晶シリコン基板1/酸化膜2の温度が200℃に達すると、仕込室と反応室CB1との間の仕切バルブが開けられ、n型単結晶シリコン基板1/酸化膜2は、仕込室から反応室CB1へ搬送される。

When the temperature of the n-type single

p型非晶質膜11〜1mおよびn型非晶質膜3,21〜2m−1を形成するときの材料ガスの流量を表1に示す。

Table 1 shows the flow rate of the material gas when forming the p-type

n型単結晶シリコン基板1/酸化膜2が反応室CB1へ搬送されると、2sccmのシラン(SiH4)ガスと、42sccmの水素(H2)ガスと、水素希釈された12sccmのジボラン(B2H6)ガスとを反応室CB1に流し、反応室CB1の圧力を13.3Pa〜665Paの範囲に設定する。そして、RF電源は、16〜80mW/cm2の範囲のRFパワーを整合器を介して平行平板電極に印加する。これによって、反応室CB1内でプラズマが発生し、p型a−Siからなるp型非晶質膜20がn型単結晶シリコン基板1の裏面(=酸化膜2が形成された面と反対側の表面)に堆積される(図2の工程(d)参照)。なお、水素希釈されたB2H6ガスの濃度は、0.1%である。

When the n-type single

p型非晶質膜20の膜厚が10nmになると、反応室CB1の平行平板電極へのRFパワーの印加を停止するとともに、SiH4ガス、H2ガスおよびB2H6ガスの反応室CB1への供給を停止し、排気機構によって1×10−5Pa以下に反応室CB1を真空引きする。そして、仕切バルブを開け、p型非晶質膜20/n型単結晶シリコン基板1/酸化膜2を反応室CB1から取出室へ搬送し、p型非晶質膜20/n型単結晶シリコン基板1/酸化膜2を室温まで冷却した後、取り出す。

When the thickness of the p-type

そして、取り出したp型非晶質膜20/n型単結晶シリコン基板1/酸化膜2のp型非晶質膜20の全面にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン30を形成する(図2の工程(e)参照)。

Then, a resist is applied to the entire surface of the p-type

その後、レジストパターン30をマスクとしてp型非晶質膜20をドライエッチングまたはウェットエッチングによってエッチングし、p型非晶質膜11〜1mを形成する(図3の工程(f)参照)。

Thereafter, the p-type

p型非晶質膜11〜1mを形成すると、p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2のp型非晶質膜11〜1m側をフッ酸で洗浄し、p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2をプラズマ装置の仕込室の基板ホルダー上に配置する。

When the p-type

そして、仕込室の排気機構は、1×10−5Pa以下に仕込室内のガスを排気し、仕込室の加熱機構は、p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2の温度を200℃に設定するように基板ホルダーを加熱する。

And the exhaust mechanism of the preparation chamber exhausts the gas in the preparation chamber to 1 × 10 −5 Pa or less, and the heating mechanism of the preparation chamber is the p-type

p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2の温度が200℃に達すると、p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2を仕込室から反応室CB2へ搬送する。

When the temperature of the p-type

p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2が反応室CB2へ搬送されると、20sccmのSiH4ガスと、150sccmのH2ガスと、水素希釈された50sccmのフォスフィン(PH3)ガスとを反応室CB2に流し(表1参照)、反応室CB2の圧力を13.3Pa〜665Paの範囲に設定する。そして、RF電源は、16〜80mW/cm2の範囲のRFパワーを整合器を介して平行平板電極に印加する。これによって、反応室CB2内でプラズマが発生し、n型a−Siからなるn型非晶質膜40がp型非晶質膜11〜1mおよびn型単結晶シリコン基板1の表面に堆積される(図3の工程(g)参照)。なお、水素希釈されたPH3ガスの濃度は、0.2%である。

When the p-type

n型非晶質膜40の膜厚が10nmになると、反応室CB2の平行平板電極へのRFパワーの印加を停止するとともに、SiH4ガス、H2ガスおよびPH3ガスの反応室CB2への供給を停止し、排気機構によって1×10−5Pa以下に反応室CB2を真空引きする。そして、仕切バルブを開け、n型非晶質膜40/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2を反応室CB2から取出室へ搬送する。そして、n型非晶質膜40/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2を室温まで冷却し、取出室から取出す。

When the thickness of the n-type

その後、n型非晶質膜40/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2のn型非晶質膜40上にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン50を形成する(図3の工程(h)参照)。

Thereafter, a resist is applied on the n-type

その後、レジストパターン50をマスクとしてn型非晶質膜40をドライエッチングまたはウェットエッチングによってエッチングし、n型非晶質膜21〜2m−1を形成する(図3の工程(i)参照)。

Thereafter, the n-type

そして、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2をフッ酸で洗浄し、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2をプラズマ装置の仕込室の基板ホルダー上に配置する。なお、酸化膜2は、フッ酸によってエッチングされるが、フッ酸の濃度を薄くすることによって酸化膜2をエッチングすることなしに酸化膜2を洗浄できる。

Then, the n-type amorphous films 21-2m-1 / p-type amorphous films 11-1m / n-type single

その後、仕込室の排気機構は、1×10−5Pa以下に仕込室内のガスを排気し、仕込室の加熱機構は、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2の温度を200℃に設定するように基板ホルダーを加熱する。

Then, the exhaust mechanism of the preparation chamber exhausts the gas in the preparation chamber to 1 × 10 −5 Pa or less, and the heating mechanism of the preparation chamber is the n-type amorphous film 21-2m−1 / p-type amorphous film. The substrate holder is heated so that the temperature of the 11-1 m / n type single

n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2の温度が200℃に達すると、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2を仕込室から反応室CB2へ搬送する。

When the temperature of n-type amorphous film 21-2m-1 / p-type amorphous film 11-1m / n-type single

n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2が反応室CB2へ搬送されると、20sccmのSiH4ガスと、150sccmのH2ガスと、水素希釈された50sccmのPH3ガスとを反応室CB2に流し(表1参照)、反応室CB2の圧力を13.3Pa〜665Paの範囲に設定する。そして、RF電源は、16〜80mW/cm2の範囲のRFパワーを整合器を介して平行平板電極に印加する。これによって、反応室CB2内でプラズマが発生し、n型a−Siからなるn型非晶質膜3が酸化膜2上に堆積される(図4の工程(j)参照)。

When n-type amorphous film 21-2m-1 / p-type amorphous film 11-1m / n-type single

n型非晶質膜3の膜厚が10nm〜数十nmになると、反応室CB2の平行平板電極へのRFパワーの印加を停止するとともに、SiH4ガス、H2ガスおよびPH3ガスの反応室CB2への供給を停止し、排気機構によって1×10−5Pa以下に反応室CB2を真空引きする。そして、仕切バルブを開け、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2/n型非晶質膜3を反応室CB2から取出室へ搬送する。そして、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2/n型非晶質膜3を室温まで冷却し、取出室から取出す。

When the thickness of the n-type

その後、n型非晶質膜21〜2m−1/p型非晶質膜11〜1m/n型単結晶シリコン基板1/酸化膜2/n型非晶質膜3のn型非晶質膜3上にSi3N4からなる反射防止膜4をスパッタリングによって形成する(図4の工程(k)参照)。

Thereafter, n-type amorphous film 21-2m-1 / p-type amorphous film 11-1m / n-type single

引き続いて、n型非晶質膜21〜2m−1およびp型非晶質膜11〜1m側にAgを蒸着し、その蒸着したAgをフォトリソグラフィおよびエッチングによってパターンニングし、電極31〜3m,41〜4m−1を形成する。これによって、光電変換素子100が完成する(図4の工程(l)参照)。

Subsequently, Ag is vapor-deposited on the n-type

光電変換素子100の製造方法においては、図2の工程(c)において、化学堆積法(CVD:Chemical Vapour Deposition)によって酸化膜2を形成してもよく、酸化液を用いた酸化によって酸化膜2を形成してもよく、室温で水中に浸漬する、または沸騰水中に浸漬する水中酸化法によって酸化膜2を形成してもよく、自然酸化法によって酸化膜2を形成してもよい。自然酸化法によって酸化膜2を形成する場合、即ち、酸化膜2が自然酸化膜からなる場合、n型単結晶シリコン基板1の一方の表面をテクスチャ化した後、そのテクスチャ化した表面を除いてn型単結晶シリコン基板1をフッ酸で洗浄し、その後、工程(d)〜工程(l)を順次実行する。

In the manufacturing method of the

また、光電変換素子100の製造方法においては、酸化膜2を形成した後、n型非晶質膜3,21〜2m−1、p型非晶質膜11〜1m、反射防止膜4および電極31〜3m,41〜4m−1を形成する順序は、上述した工程(a)〜工程(l)において説明した順序に限らず、任意の順序であってもよい。

Moreover, in the manufacturing method of the

光電変換素子100において、太陽光が反射防止膜4側から光電変換素子100に照射されると、n型単結晶シリコン基板1中で電子および正孔が光励起される。

In the

光励起された電子および正孔は、酸化膜2側へ拡散しても、酸化膜2によるn型単結晶シリコン基板1のパッシベーション効果およびn型非晶質膜3によるFSF効果(表面電界効果)によって再結合し難くなり、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散し易くなる。

Even though the photoexcited electrons and holes diffuse to the

より具体的には、n型単結晶シリコン基板1のテクスチャ化された表面に酸化膜2(=SiO2)が接しているので、n型単結晶シリコン基板1と酸化膜2(=SiO2)との界面における界面準位密度は、1010cm−2〜1011cm−2と非常に低い。その結果、キャリア(電子および正孔)は、n型単結晶シリコン基板1のテクスチャ化された表面において殆ど再結合しない。また、酸化膜2の膜厚は、上述したように数nmであるので、キャリア(電子および正孔)は、n型非晶質膜3によるFSF効果によってn型単結晶シリコン基板1と酸化膜2との界面へ到達し難くなり、再結合が更に抑制される。特に、少数キャリアである正孔の再結合が抑制される。即ち、n型非晶質膜3を構成するn型a−Siの光学バンドギャップ(=約1.7eV)および活性化エネルギー(=約0.2eV〜0.3eV)とn型単結晶シリコン基板1の光学バンドギャップ(=1.1eV)および活性化エネルギー(=0.1eV〜0.2eV)とを考慮すると、n型a−Siの価電子帯の端は、n型単結晶シリコン基板1の価電子帯の端よりも、0.4eV〜0.6eVだけ高エネルギー側に存在するので、n型非晶質膜3は、n型単結晶シリコン基板1の表面近傍において表面電界を発生する。その結果、n型単結晶シリコン基板1の表面近傍へ拡散した正孔は、n型非晶質膜3による表面電界によってn型単結晶シリコン基板1と酸化膜2との界面へ到達し難くなる。従って、少数キャリアである正孔の再結合がFSF効果によって抑制される。

More specifically, since the oxide film 2 (= SiO 2 ) is in contact with the textured surface of the n-type single

このように、キャリア(電子および正孔)は、酸化膜2およびn型非晶質膜3によってn型単結晶シリコン基板1の表面における再結合が抑制され、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散し易くなる。

Thus, carriers (electrons and holes) are suppressed from recombination on the surface of the n-type single

そして、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散した電子および正孔は、p型非晶質膜11〜1m/n型単結晶シリコン基板1(=pn接合)による内部電界によって分離され、正孔は、p型非晶質膜11〜1mを介して電極31〜3mへ到達し、電子は、n型非晶質膜21〜2m−1を介して電極41〜4m−1へ到達する。

Then, the electrons and holes diffused toward the p-type

電極41〜4m−1へ到達した電子は、電極31〜3mと電極41〜4m−1との間に接続された負荷を介して電極31〜3mへ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子100は、n型単結晶シリコン基板1中で光励起された電子および正孔をn型単結晶シリコン基板1の裏面(=酸化膜2が形成されたn型単結晶シリコン基板1の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

In this manner, the

そして、光電変換素子100は、光入射側に、酸化膜2およびn型非晶質膜3を備えるので、上述したように、n型単結晶シリコン基板1の光入射側の表面においてキャリアの再結合が抑制され、n型単結晶シリコン基板1に対するパッシベーション効果を向上できる。

Further, since the

また、光電変換素子100の製造方法において説明したように、酸化膜2を形成した後に、p型非晶質膜11〜1m、n型非晶質膜3,21〜2m−1、反射防止膜4および電極31〜3m,41〜4m−1を形成するので(図2の工程(d)〜図4の工程(k)参照)、光電変換素子100の製造プロセスにおいて、n型単結晶シリコン基板1の受光面側の表面を保護できる。

In addition, as described in the method for manufacturing the

図5は、実施の形態1による他の光電変換素子の構成を示す断面図である。実施の形態1による光電変換素子は、図5に示す光電変換素子100Aであってもよい。

FIG. 5 is a cross-sectional view showing the configuration of another photoelectric conversion element according to the first embodiment. The photoelectric conversion element according to

図5を参照して、光電変換素子100Aは、図1に示す光電変換素子100にi型非晶質膜51〜5mを追加したものであり、その他は、光電変換素子100と同じである。

Referring to FIG. 5, the

i型非晶質膜51〜5mは、非晶質相からなり、それぞれ、n型単結晶シリコン基板1およびp型非晶質膜11〜1mに接し、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの間に配置される。そして、i型非晶質膜51〜5mの各々は、例えば、i型a−Siからなり、膜厚は、例えば、10nmである。また、i型非晶質膜51〜5mは、n型単結晶シリコン基板1の面内方向(図5の紙面における左右方向)において、それぞれ、p型非晶質膜11〜1mと同じ幅を有する。更に、i型非晶質膜51〜5mは、図5の紙面に垂直な方向において、それぞれ、p型非晶質膜11〜1mと同じ長さを有する。

The i-type

光電変換素子100Aにおいては、n型非晶質膜21〜2m−1の各々の膜厚は、p型非晶質膜11〜1mの膜厚とi型非晶質膜61〜6mの膜厚との合計膜厚からなる。

In the

また、光電変換素子100Aにおいては、i型非晶質膜51の端面は、n型非晶質膜21に接し、i型非晶質膜52の端面は、n型非晶質膜21,22に接し、i型非晶質膜53の端面は、n型非晶質膜22,23に接し、以下、同様にして、i型非晶質膜5m−1の端面は、n型非晶質膜2m−2,2m−1に接し、i型非晶質膜5mの端面は、n型非晶質膜2m−1に接する。

In the

光電変換素子100Aは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図2の工程(d)において、i型非晶質膜51〜5m用のi型非晶質膜がプラズマCVD法によってn型単結晶シリコン基板1上に堆積され、その後、p型非晶質膜11〜1m用のp型非晶質膜20がプラズマCVD法によってi型非晶質膜51〜5m用のi型非晶質膜上に堆積される。そして、i型非晶質膜51〜5m用のi型非晶質膜を堆積するときのガス流量は、表1に示すとおりである。また、i型非晶質膜51〜5m用のi型非晶質膜を堆積するときの圧力およびRFパワーは、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1を形成するときの圧力およびRFパワーと同じである。

100 A of photoelectric conversion elements are manufactured by the process (a)-process (l) shown in FIGS. In this case, in step (d) of FIG. 2, an i-type amorphous film for the i-type

光電変換素子100Aにおける発電機構は、光電変換素子100の発電機構と概ね同じであり、光電変換素子100において説明したように、電子および正孔は、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散し易くなる。そして、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散した電子および正孔は、p型非晶質膜11〜1m/i型非晶質膜51〜5m/n型単結晶シリコン基板1(=pin接合)による内部電界によって分離され、正孔は、i型非晶質膜51〜5mおよびp型非晶質膜11〜1mを介して電極31〜3mへ到達し、電子は、n型非晶質膜21〜2m−1を介して電極41〜4m−1へ到達する。

The power generation mechanism in the

電極41〜4m−1へ到達した電子は、電極31〜3mと電極41〜4m−1との間に接続された負荷を介して電極31〜3mへ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子100Aは、n型単結晶シリコン基板1中で光励起された電子および正孔をn型単結晶シリコン基板1の裏面(=酸化膜2が形成されたn型単結晶シリコン基板1の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子100Aは、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜2と、酸化膜2に接して設けられたn型非晶質膜3とを備えるので、光電変換素子100において説明したように、n型単結晶シリコン基板1に対するパッシベーション効果を向上できる。

The

また、光電変換素子100Aにおいては、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの間にi型非晶質膜51〜5mが存在するので、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの界面における正孔の再結合が抑制される。その結果、短絡光電流が増加し、光電変換素子100Aの変換効率を向上できる。

In the

光電変換素子100Aについてのその他の説明は、光電変換素子100についての説明と同じである。

The other description of the

図6は、実施の形態1による更に他の光電変換素子の構成を示す断面図である。実施の形態1による光電変換素子は、図6に示す光電変換素子100Bであってもよい。

FIG. 6 is a cross-sectional view showing a configuration of still another photoelectric conversion element according to

図6を参照して、光電変換素子100Bは、図1に示す光電変換素子100にi型非晶質膜61〜6m−1を追加したものであり、その他は、光電変換素子100と同じである。

Referring to FIG. 6,

i型非晶質膜61〜6m−1は、非晶質相からなり、それぞれ、n型単結晶シリコン基板1およびn型非晶質膜21〜2m−1に接し、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との間に配置される。そして、i型非晶質膜61〜6m−1の各々は、例えば、i型a−Siからなり、膜厚は、例えば、10nmである。また、i型非晶質膜61〜6m−1は、図6の紙面に垂直な方向において、それぞれ、n型非晶質膜21〜2m−1と同じ長さを有する。

The i-type

光電変換素子100Bにおいては、p型非晶質膜11〜1mの各々の膜厚は、n型非晶質膜21〜2m−1の膜厚とi型非晶質膜61〜6m−1の膜厚との合計膜厚からなる。

In the

また、光電変換素子100Bにおいては、p型非晶質膜11の端面は、i型非晶質膜61およびn型非晶質膜21に接し、p型非晶質膜12の端面は、i型非晶質膜61およびn型非晶質膜21とi型非晶質膜62およびn型非晶質膜22とに接し、p型非晶質膜13の端面は、i型非晶質膜62およびn型非晶質膜22とi型非晶質膜63およびn型非晶質膜23とに接し、以下、同様にして、p型非晶質膜1m−1の端面は、i型非晶質膜6m−2およびn型非晶質膜2m−2とi型非晶質膜6m−1およびn型非晶質膜2m−1とに接し、p型非晶質膜1mの端面は、i型非晶質膜6m−1およびn型非晶質膜2m−1に接する。

In the

光電変換素子100Bは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図3の工程(i)において、i型非晶質膜61〜6m−1用のi型非晶質膜がプラズマCVD法によってn型単結晶シリコン基板1およびp型非晶質膜11〜1m上に堆積され、その後、n型非晶質膜60がプラズマCVD法によってi型非晶質膜61〜6m−1用のi型非晶質膜上に堆積される。そして、i型非晶質膜61〜6m−1用のi型非晶質膜を堆積するときのガス流量は、表1に示すi型非晶質膜51〜5mのガス流量と同じである。

The

光電変換素子100Bにおける発電機構は、光電変換素子100の発電機構と概ね同じであり、光電変換素子100において説明したように、電子および正孔は、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散し易くなる。そして、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散した電子および正孔は、p型非晶質膜11〜1m/n型単結晶シリコン基板1(=pn接合)による内部電界によって分離され、正孔は、p型非晶質膜11〜1mを介して電極31〜3mへ到達し、電子は、i型非晶質膜61〜6m−1およびn型非晶質膜21〜2m−1を介して電極41〜4m−1へ到達する。

The power generation mechanism in the

電極41〜4m−1へ到達した電子は、電極31〜3mと電極41〜4m−1との間に接続された負荷を介して電極31〜3mへ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子100Bは、n型単結晶シリコン基板1中で光励起された電子および正孔をn型単結晶シリコン基板1の裏面(=酸化膜2が形成されたn型単結晶シリコン基板1の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子100Bは、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜2と、酸化膜2に接して設けられたn型非晶質膜3とを備えるので、光電変換素子100において説明したように、n型単結晶シリコン基板1に対するパッシベーション効果を向上できる。

The

また、光電変換素子100Bにおいては、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との間にi型非晶質膜61〜6m−1が存在するので、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との界面における電子の再結合が抑制される。その結果、短絡光電流が増加し、光電変換素子100Bの変換効率を向上できる。

In the

光電変換素子100Bについてのその他の説明は、光電変換素子100についての説明と同じである。

The other description of the

図7は、実施の形態1による更に他の光電変換素子の構成を示す断面図である。実施の形態1による光電変換素子は、図7に示す光電変換素子100Cであってもよい。

FIG. 7 is a cross-sectional view showing a configuration of still another photoelectric conversion element according to the first embodiment. The photoelectric conversion element according to

図7を参照して、光電変換素子100Cは、図1に示す光電変換素子100にi型非晶質膜51〜5m,61〜6m−1を追加したものであり、その他は、光電変換素子100と同じである。

Referring to FIG. 7, a

i型非晶質膜51〜5m,61〜6m−1については、上述したとおりである。

The i-type

光電変換素子100Cにおいては、i型非晶質膜61の端面は、i型非晶質膜51,52に接し、i型非晶質膜62の端面は、i型非晶質膜52,53に接し、以下、同様にして、i型非晶質膜6m−1の端面は、i型非晶質膜5m−1,5mに接する。また、n型非晶質膜21の端面は、p型非晶質膜11,12に接し、n型非晶質膜22の端面は、p型非晶質膜12,13に接し、以下、同様にして、n型非晶質膜2m−1の端面は、p型非晶質膜1m−1,1mに接する。

In the

光電変換素子100Cは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図2の工程(d)において、i型非晶質膜51〜5m用のi型非晶質膜がプラズマCVD法によってn型単結晶シリコン基板1上に堆積され、その後、p型非晶質膜11〜1m用のp型非晶質膜20がプラズマCVD法によってi型非晶質膜51〜5m用のi型非晶質膜上に堆積される。また、図3の工程(i)において、i型非晶質膜61〜6m−1用のi型非晶質膜がプラズマCVD法によってn型単結晶シリコン基板1およびp型非晶質膜11〜1m上に堆積され、その後、n型非晶質膜21〜2m−1用のn型非晶質膜60がプラズマCVD法によってi型非晶質膜61〜6m−1用のi型非晶質膜上に堆積される。そして、i型非晶質膜51〜5m用のi型非晶質膜およびi型非晶質膜61〜6m−1用のi型非晶質膜を堆積するときのガス流量は、同じであり、表1に示すとおりである。

The

光電変換素子100Cにおける発電機構は、光電変換素子100の発電機構と概ね同じであり、光電変換素子100において説明したように、電子および正孔は、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散し易くなる。そして、p型非晶質膜11〜1mおよびn型非晶質膜21〜2m−1側へ拡散した電子および正孔は、p型非晶質膜11〜1m/i型非晶質膜51〜5m/n型単結晶シリコン基板1(=pin接合)による内部電界によって分離され、正孔は、i型非晶質膜51〜5mおよびp型非晶質膜11〜1mを介して電極31〜3mへ到達し、電子は、i型非晶質膜61〜6m−1およびn型非晶質膜21〜2m−1を介して電極41〜4m−1へ到達する。

The power generation mechanism in the

電極41〜4m−1へ到達した電子は、電極31〜3mと電極41〜4m−1との間に接続された負荷を介して電極31〜3mへ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子100Cは、n型単結晶シリコン基板1中で光励起された電子および正孔をn型単結晶シリコン基板1の裏面(=酸化膜2が形成されたn型単結晶シリコン基板1の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子100Cは、n型単結晶シリコン基板1の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜2と、酸化膜2に接して設けられたn型非晶質膜3とを備えるので、光電変換素子100において説明したように、n型単結晶シリコン基板1に対するパッシベーション効果を向上できる。

The

また、光電変換素子100Cにおいては、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの間にi型非晶質膜51〜5mが存在するので、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの界面における正孔の再結合が抑制される。更に、光電変換素子100Cにおいては、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との間にi型非晶質膜61〜6m−1が存在するので、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との界面における電子の再結合が抑制される。

In the

その結果、短絡光電流が増加し、光電変換素子100Cの変換効率を向上できる。

As a result, the short-circuit photocurrent increases and the conversion efficiency of the

光電変換素子100Cについてのその他の説明は、光電変換素子100についての説明と同じである。

The other description of the

光電変換素子100,100A,100B,100Cにおいては、n型単結晶シリコン基板1の光入射側の表面(=酸化膜2が形成された表面)がテクスチャ構造になっていなくてもよい。この場合、図2の工程(b)が省略される。

In the

また、光電変換素子100,100A,100B,100Cにおいては、p型非晶質膜11〜1mは、p型a−Siからなると説明したが、実施の形態1においては、これに限らず、p型非晶質膜11〜1mは、p型a−SiC、p型a−SiO、p型a−SiN、p型a−SiCN、p型a−SiGeおよびp型a−Geのいずれかからなっていてもよい。

In the

更に、光電変換素子100,100A,100B,100Cにおいては、n型非晶質膜3,21〜2m−1は、n型a−Siからなると説明したが、実施の形態1においては、これに限らず、n型非晶質膜21〜2m−1は、n型a−SiC、n型a−SiO、n型a−SiN、n型a−SiCN、n型a−SiGeおよびn型a−Geのいずれかからなっていてもよい。

Furthermore, in the

更に、光電変換素子100A,100Cにおいては、i型非晶質膜51〜5mは、i型a−Siからなると説明したが、実施の形態1においては、これに限らず、i型非晶質膜51〜5mは、i型a−SiC、i型a−SiO、i型a−SiN、i型a−SiCNおよびi型a−SiGeのいずれかからなっていてもよい。

Further, in the

更に、光電変換素子100B,100Cにおいては、i型非晶質膜61〜6m−1は、i型a−Siからなると説明したが、実施の形態1においては、これに限らず、i型非晶質膜61〜6m−1は、i型a−SiC、i型a−SiO、i型a−SiN、i型a−SiCNおよびi型a−SiGeのいずれかからなっていてもよい。

Further, in the

即ち、光電変換素子100,100A,100B,100Cにおいては、p型非晶質膜11〜1mおよびn型非晶質膜3,21〜2m−1は、それぞれ、表2に示す材料のいずれかからなっていてもよく、光電変換素子100A,100B,100Cにおいては、i型非晶質膜51〜5mおよび/またはi型非晶質膜61〜6m−1は、それぞれ、表2に示す材料のいずれかからなっていてもよい。

That is, in the

この場合、p型a−SiCは、SiH4ガス、メタン(CH4)ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。p型a−SiOは、SiH4ガス、酸素(O2)ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。p型a−SiNは、SiH4ガス、アンモニア(NH3)ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。p型a−SiCNは、SiH4ガス、CH4ガス、NH3ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。p型a−SiGeは、SiH4ガス、ゲルマン(GeH4)ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。p型a−Geは、GeH4ガス、B2H6ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。 In this case, the p-type a-SiC is formed by the above-described plasma CVD method using SiH 4 gas, methane (CH 4 ) gas, B 2 H 6 gas, and H 2 gas as material gases. The p-type a-SiO is formed by the above-described plasma CVD method using SiH 4 gas, oxygen (O 2 ) gas, B 2 H 6 gas and H 2 gas as material gases. The p-type a-SiN is formed by the above-described plasma CVD method using SiH 4 gas, ammonia (NH 3 ) gas, B 2 H 6 gas and H 2 gas as material gases. The p-type a-SiCN is formed by the above-described plasma CVD method using SiH 4 gas, CH 4 gas, NH 3 gas, B 2 H 6 gas and H 2 gas as material gases. The p-type a-SiGe is formed by the above-described plasma CVD method using SiH 4 gas, germane (GeH 4 ) gas, B 2 H 6 gas and H 2 gas as material gases. The p-type a-Ge is formed by the above-described plasma CVD method using GeH 4 gas, B 2 H 6 gas, and H 2 gas as material gases.

また、n型a−SiCは、SiH4ガス、CH4ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。n型a−SiOは、SiH4ガス、O2ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。n型a−SiNは、SiH4ガス、NH3ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。n型a−SiCNは、SiH4ガス、CH4ガス、NH3ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。n型a−SiGeは、SiH4ガス、GeH4ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。n型a−Geは、GeH4ガス、PH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。 The n-type a-SiC is formed by the above-described plasma CVD method using SiH 4 gas, CH 4 gas, PH 3 gas, and H 2 gas as material gases. The n-type a-SiO is formed by the above-described plasma CVD method using SiH 4 gas, O 2 gas, PH 3 gas, and H 2 gas as material gases. The n-type a-SiN is formed by the above-described plasma CVD method using SiH 4 gas, NH 3 gas, PH 3 gas, and H 2 gas as material gases. The n-type a-SiCN is formed by the above-described plasma CVD method using SiH 4 gas, CH 4 gas, NH 3 gas, PH 3 gas, and H 2 gas as material gases. The n-type a-SiGe is formed by the above-described plasma CVD method using SiH 4 gas, GeH 4 gas, PH 3 gas, and H 2 gas as material gases. The n-type a-Ge is formed by the above-described plasma CVD method using GeH 4 gas, PH 3 gas, and H 2 gas as material gases.

更に、i型a−SiCは、SiH4ガス、CH4ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。i型a−SiOは、SiH4ガス、O2ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。i型a−SiNは、SiH4ガス、NH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。i型a−SiCNは、SiH4ガス、CH4ガス、NH3ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。i型a−SiGeは、SiH4ガス、GeH4ガスおよびH2ガスを材料ガスとして、上述したプラズマCVD法によって形成される。 Furthermore, i-type a-SiC is formed by the above-described plasma CVD method using SiH 4 gas, CH 4 gas, and H 2 gas as material gases. i-type a-SiO is formed by the above-described plasma CVD method using SiH 4 gas, O 2 gas, and H 2 gas as material gases. i-type a-SiN is formed by the above-described plasma CVD method using SiH 4 gas, NH 3 gas, and H 2 gas as material gases. The i-type a-SiCN is formed by the above-described plasma CVD method using SiH 4 gas, CH 4 gas, NH 3 gas, and H 2 gas as material gases. i-type a-SiGe is formed by the above-described plasma CVD method using SiH 4 gas, GeH 4 gas, and H 2 gas as material gases.

なお、i型非晶質膜51〜5m,61〜6m−1としては、i型a−Geも想定されるが、i型a−Geは、n型単結晶シリコン基板1よりも光学バンドギャップが小さいので、i型a−Geをi型非晶質膜51〜5m,61〜6m−1として用いた場合、開放電圧Vocの向上が困難である。光電変換素子100,100A,100B,100Cにおいては、i型非晶質膜51〜5m,61〜6m−1の光学バンドギャップが開放電圧Vocを支配的に決定するからである。

Note that i-type a-Ge is also assumed as the i-type

そこで、実施の形態1においては、n型単結晶シリコン基板1の光学バンドギャップよりも大きいi型a−SiC,i型a−SiO,i型a−SiN,i型a−SiCN,i型a−Si,i型a−SiGeをi型非晶質膜51〜5m,61〜6m−1として用いることにした。

Therefore, in the first embodiment, i-type a-SiC, i-type a-SiO, i-type a-SiN, i-type a-SiCN, and i-type a that are larger than the optical band gap of the n-type single

上述したように、実施の形態1による光電変換素子は、n型単結晶シリコン基板1の裏面にヘテロ接合を形成したバックコンタクト型の光電変換素子であり、n型単結晶シリコン基板1の光入射側の表面に酸化膜2およびn型非晶質膜3を順次積層した構造からなる。従って、n型単結晶シリコン基板1の光入射側の表面におけるキャリア(特に、正孔)の再結合を酸化膜2による界面準位の低下と、n型非晶質膜3によるFSF効果とによって抑制し、n型単結晶シリコン基板1に対するパッシベーション効果を向上できる。

As described above, the photoelectric conversion element according to the first embodiment is a back-contact type photoelectric conversion element in which a heterojunction is formed on the back surface of the n-type single

[実施の形態2]

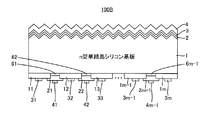

図8は、実施の形態2による光電変換素子の構成を示す断面図である。図8を参照して、実施の形態2による光電変換素子200は、p型単結晶シリコン基板101と、酸化膜102と、p型非晶質膜103,121〜12m−1と、反射防止膜104と、n型非晶質膜111〜11mと、電極131〜13m,141〜14m−1とを備える。

[Embodiment 2]

FIG. 8 is a cross-sectional view showing the configuration of the photoelectric conversion element according to the second embodiment. Referring to FIG. 8, the

p型単結晶シリコン基板101は、例えば、(100)の面方位および0.1〜1.0Ω・cmの比抵抗を有する。また、p型単結晶シリコン基板101は、例えば、100〜300μmの厚みを有し、好ましくは、100〜200μmの厚みを有する。更に、p型単結晶シリコン基板101は、光入射側の表面がテクスチャ化されている。

The p-type single

酸化膜102は、例えば、SiO2からなり、p型単結晶シリコン基板101の光入射側の表面に接して設けられる。そして、酸化膜102は、例えば、数nmの膜厚を有する。

The

p型非晶質膜103は、非晶質相からなり、例えば、p型a−Siからなる。また、p型非晶質膜103は、例えば、10nm〜数十nmの膜厚を有する。更に、p型非晶質層103のB濃度は、1×1018cm−3〜1×1020cm−3である。そして、p型非晶質膜103は、酸化膜102に接して形成される。

The p-type

反射防止膜104は、例えば、Si3N4からなり、膜厚は、例えば、100nmである。そして、反射防止膜104は、p型非晶質膜103に接して設けられる。

The

n型非晶質膜111〜11mの各々は、非晶質相からなり、p型単結晶シリコン基板101の光入射側と反対側の表面に接して設けられる。そして、n型非晶質膜111〜11mの各々は、例えば、n型a−Siからなり、膜厚は、例えば、10nmである。また、n型非晶質膜111〜11mは、p型単結晶シリコン基板101の面内方向において所望の間隔で配置される。更に、n型非晶質膜111〜11mの各々におけるP濃度は、例えば、5×1019cm−3である。

Each of n-type

p型非晶質膜121〜12m−1の各々は、非晶質相からなる。p型非晶質膜121は、n型非晶質膜111,112およびp型単結晶シリコン基板101に接して配置され、p型非晶質膜122は、n型非晶質膜112,113およびp型単結晶シリコン基板101に接して配置され、以下、同様にして、p型非晶質膜12m−1は、n型非晶質膜11m−1,11mおよびp型単結晶シリコン基板101に接して配置される。

Each of the p-type

そして、p型非晶質膜121〜12m−1の各々は、例えば、p型a−Siからなり、膜厚は、例えば、10nmである。また、p型非晶質膜121〜12m−1の各々におけるB濃度は、例えば、5×1019cm−3である。

Each of the p-type

電極131〜13mは、それぞれ、n型非晶質膜111〜11mに接して設けられる。電極141〜14m−1は、それぞれ、p型非晶質膜121〜12m−1に接して設けられる。そして、電極131〜13m,141〜14m−1の各々は、例えば、Agからなる。

The

n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1は、図8の紙面に垂直な方向において同じ長さを有する。そして、n型非晶質膜111〜11mの全体の面積がp型単結晶シリコン基板101の面積に占める割合である面積占有率は、60〜93%であり、p型非晶質膜121〜12m−1の全体の面積がp型単結晶シリコン基板101の面積に占める割合である面積占有率は、5〜20%である。

The n-type

このように、n型非晶質膜111〜11mの面積占有率をp型非晶質膜121〜12m−1の面積占有率よりも大きくするのは、p型単結晶シリコン基板101中で光励起された電子および正孔がpn接合(n型非晶質膜111〜11m/p型単結晶シリコン基板101)によって分離され易くし、光励起された電子および正孔の発電への寄与率を高くするためである。

As described above, the area occupation ratio of the n-type

光電変換素子200は、図2から図4に示す工程(a)〜工程(l)に従って製造される。この場合、n型単結晶シリコン基板1、酸化膜2、n型非晶質膜3、反射防止膜4、p型非晶質膜11〜1m、n型非晶質膜21〜2m−1および電極31〜3m,41〜4m−1をそれぞれp型単結晶シリコン基板101、酸化膜102、p型非晶質膜103、反射防止膜104、n型非晶質膜111〜11m、p型非晶質膜121〜12m−1および電極131〜13m,141〜14m−1に読み替えればよい。そして、酸化膜102は、酸化膜2と同じ方法によって形成され、p型非晶質膜103,121〜12m−1は、表1に示すp型非晶質膜11〜1mと同じ材料ガスおよびp型非晶質膜11〜1mの条件と同じ条件を用いてプラズマCVD法によって形成される。n型非晶質膜111〜11mは、表1に示すn型非晶質膜21〜2m−1と同じ材料ガスおよびn型非晶質膜21〜2m−1の条件と同じ条件を用いてプラズマCVD法によって形成される。また、反射防止膜104は、反射防止膜4と同じ方法によって形成される。

The

光電変換素子200において、太陽光が反射防止膜104側から光電変換素子200に照射されると、p型単結晶シリコン基板101中で電子および正孔が光励起される。

In the

光励起された電子および正孔は、酸化膜102側へ拡散しても、酸化膜102によるp型単結晶シリコン基板101のパッシベーション効果およびp型非晶質膜103によるFSF効果(表面電界効果)によって再結合し難くなり、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散し易くなる。

Even if the photoexcited electrons and holes diffuse to the

より具体的には、p型単結晶シリコン基板101のテクスチャ化された表面に酸化膜102(=SiO2)が接しているので、p型単結晶シリコン基板101と酸化膜102(=SiO2)との界面における界面準位密度は、1010cm−2〜1011cm−2と非常に低い。その結果、キャリア(電子および正孔)は、p型単結晶シリコン基板101のテクスチャ化された表面において殆ど再結合しない。また、酸化膜102の膜厚は、上述したように数nmであるので、キャリア(電子および正孔)は、p型非晶質膜103によるFSF効果によってp型単結晶シリコン基板101と酸化膜102との界面へ到達し難くなり、再結合が更に抑制される。特に、少数キャリアである電子の再結合が抑制される。即ち、p型非晶質膜103を構成するp型a−Siの光学バンドギャップ(=約1.7eV)および活性化エネルギー(=約0.3eV〜0.4eV)とp型単結晶シリコン基板101の光学バンドギャップ(=1.1eV)および活性化エネルギー(=0.2eV〜0.3eV)とを考慮すると、p型a−Siの伝導帯の端は、p型単結晶シリコン基板101の伝導帯の端よりも、0.4eV〜0.6eVだけ高エネルギー側に存在するので、p型非晶質膜103は、p型単結晶シリコン基板101の表面近傍において表面電界を発生する。その結果、p型単結晶シリコン基板101の表面近傍へ拡散した電子は、p型非晶質膜103による表面電界によってp型単結晶シリコン基板101と酸化膜102との界面へ到達し難くなる。従って、少数キャリアである電子の再結合がFSF効果によって抑制される。

More specifically, since the oxide film 102 (= SiO 2 ) is in contact with the textured surface of the p-type single

このように、キャリア(電子および正孔)は、酸化膜102およびp型非晶質膜103によってp型単結晶シリコン基板101の表面における再結合が抑制され、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散し易くなる。

Thus, carriers (electrons and holes) are suppressed from recombination on the surface of the p-type single

そして、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散した電子および正孔は、n型非晶質膜111〜11m/p型単結晶シリコン基板101(=pn接合)による内部電界によって分離され、電子は、n型非晶質膜111〜11mを介して電極131〜13mへ到達し、正孔は、p型非晶質膜121〜12m−1を介して電極141〜14m−1へ到達する。

Then, the electrons and holes diffused toward the n-type

電極131〜13mへ到達した電子は、電極131〜13mと電極141〜14m−1との間に接続された負荷を介して電極141〜14m−1へ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子200は、p型単結晶シリコン基板101中で光励起された電子および正孔をp型単結晶シリコン基板101の裏面(=酸化膜102が形成されたp型単結晶シリコン基板101の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

In this way, the

そして、光電変換素子200は、光入射側に、酸化膜102およびp型非晶質膜103を備えるので、上述したように、p型単結晶シリコン基板101に対するパッシベーション効果を向上できる。

Since the

また、光電変換素子100において説明したように、光電変換素子200の製造工程において、p型単結晶シリコン基板101の受光面側の表面を保護できる。

Further, as described in the

図9は、実施の形態2による他の光電変換素子の構成を示す断面図である。実施の形態2による光電変換素子は、図9に示す光電変換素子200Aであってもよい。

FIG. 9 is a cross-sectional view showing a configuration of another photoelectric conversion element according to the second embodiment. The photoelectric conversion element according to

図9を参照して、光電変換素子200Aは、図8に示す光電変換素子200にi型非晶質膜151〜15mを追加したものであり、その他は、光電変換素子200と同じである。

Referring to FIG. 9, a

i型非晶質膜151〜15mは、非晶質相からなり、それぞれ、p型単結晶シリコン基板101およびn型非晶質膜111〜11mに接し、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの間に配置される。そして、i型非晶質膜151〜15mの各々は、例えば、i型a−Siからなり、膜厚は、例えば、10nmである。また、i型非晶質膜151〜15mは、p型単結晶シリコン基板101の面内方向(図9の紙面における左右方向)において、それぞれ、n型非晶質膜111〜11mと同じ幅を有する。更に、i型非晶質膜151〜15mは、図9の紙面に垂直な方向において、それぞれ、n型非晶質膜111〜11mと同じ長さを有する。

The i-type

光電変換素子200Aにおいては、p型非晶質膜121〜12m−1の各々の膜厚は、n型非晶質膜111〜11mの膜厚とi型非晶質膜151〜15mの膜厚との合計膜厚からなる。

In the

また、光電変換素子200Aにおいては、i型非晶質膜151の端面は、p型非晶質膜121に接し、i型非晶質膜152の端面は、p型非晶質膜121,122に接し、i型非晶質膜153の端面は、p型非晶質膜122,123に接し、以下、同様にして、i型非晶質膜15m−1の端面は、p型非晶質膜12m−2,12m−1に接し、i型非晶質膜15mの端面は、p型非晶質膜12m−1に接する。

In the

光電変換素子200Aは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図2の工程(d)において、i型非晶質膜151〜15m用のi型非晶質膜がプラズマCVD法によってp型単結晶シリコン基板101上に堆積され、その後、n型非晶質膜111〜11m用のn型非晶質膜がプラズマCVD法によってi型非晶質膜151〜15m用のi型非晶質膜上に堆積される。そして、i型非晶質膜151〜15m用のi型非晶質膜を堆積するときのガス流量は、表1に示すi型非晶質膜51〜5mのガス流量と同じであり、n型非晶質膜111〜11m用のn型非晶質膜を堆積するときのガス流量は、表1に示すn型非晶質膜21〜2m−1のガス流量と同じである。

200 A of photoelectric conversion elements are manufactured by the process (a)-process (l) shown in FIGS. In this case, in the step (d) of FIG. 2, an i-type amorphous film for the i-type

光電変換素子200Aにおける発電機構は、光電変換素子200の発電機構と概ね同じであり、光電変換素子200において説明したように、電子および正孔は、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散し易くなる。そして、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散した電子および正孔は、n型非晶質膜111〜11m/i型非晶質膜151〜15m/p型単結晶シリコン基板101(=pin接合)による内部電界によって分離され、電子は、i型非晶質膜151〜15mおよびn型非晶質膜111〜11mを介して電極131〜13mへ到達し、正孔は、p型非晶質膜121〜12m−1を介して電極141〜14m−1へ到達する。

The power generation mechanism in the

電極131〜13mへ到達した電子は、電極131〜13mと電極141〜14m−1との間に接続された負荷を介して電極141〜14m−1へ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子200Aは、p型単結晶シリコン基板101中で光励起された電子および正孔をp型単結晶シリコン基板101の裏面(=酸化膜102が形成されたp型単結晶シリコン基板101の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子200Aは、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜102と、酸化膜102に接して設けられたp型非晶質膜103とを備えるので、光電変換素子200において説明したように、p型単結晶シリコン基板101に対するパッシベーション効果を向上できる。

The

また、光電変換素子200Aにおいては、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの間にi型非晶質膜151〜15mが存在するので、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの界面における電子の再結合が抑制される。その結果、短絡光電流が増加し、光電変換素子200Aの変換効率を向上できる。

In the

光電変換素子200Aについてのその他の説明は、光電変換素子200についての説明と同じである。

The other description of the

図10は、実施の形態2による更に他の光電変換素子の構成を示す断面図である。実施の形態2による光電変換素子は、図10に示す光電変換素子200Bであってもよい。

FIG. 10 is a cross-sectional view illustrating a configuration of still another photoelectric conversion element according to the second embodiment. The photoelectric conversion element according to

図10を参照して、光電変換素子200Bは、図8に示す光電変換素子200にi型非晶質膜161〜16m−1を追加したものであり、その他は、光電変換素子200と同じである。

Referring to FIG. 10,

i型非晶質膜161〜16m−1は、非晶質相からなり、それぞれ、p型単結晶シリコン基板101およびp型非晶質膜121〜12m−1に接し、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との間に配置される。そして、i型非晶質膜161〜16m−1の各々は、例えば、i型a−Siからなり、膜厚は、例えば、10nmである。また、i型非晶質膜161〜16m−1は、図10の紙面に垂直な方向において、それぞれ、p型非晶質膜121〜12m−1と同じ長さを有する。

The i-type

光電変換素子200Bにおいては、n型非晶質膜111〜11mの各々の膜厚は、p型非晶質膜121〜12m−1の膜厚とi型非晶質膜161〜16m−1の膜厚との合計膜厚からなる。

In the

また、光電変換素子200Bにおいては、n型非晶質膜111の端面は、i型非晶質膜161およびp型非晶質膜121に接し、n型非晶質膜112の端面は、i型非晶質膜161およびp型非晶質膜121とi型非晶質膜162およびp型非晶質膜122とに接し、n型非晶質膜113の端面は、i型非晶質膜162およびp型非晶質膜122とi型非晶質膜163およびp型非晶質膜123とに接し、以下、同様にして、n型非晶質膜11m−1の端面は、i型非晶質膜16m−2およびp型非晶質膜12m−2とi型非晶質膜16m−1およびp型非晶質膜12m−1とに接し、n型非晶質膜11mの端面は、i型非晶質膜16m−1およびp型非晶質膜12m−1に接する。

In the

光電変換素子200Bは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図3の工程(i)において、i型非晶質膜161〜16m−1用のi型非晶質膜がプラズマCVD法によってp型単結晶シリコン基板101およびn型非晶質膜111〜11m上に堆積され、その後、p型非晶質膜121〜12m−1用のp型非晶質膜がプラズマCVD法によってi型非晶質膜161〜16m−1用のi型非晶質膜上に堆積される。そして、i型非晶質膜161〜16m−1用のi型非晶質膜を堆積するときのガス流量は、表1に示すi型非晶質膜51〜5mのガス流量と同じであり、p型非晶質膜121〜12m−1用のp型非晶質膜を堆積するときのガス流量は、表1に示すp型非晶質膜11〜1mのガス流量と同じである。

The

光電変換素子200Bにおける発電機構は、光電変換素子200の発電機構と概ね同じであり、光電変換素子200において説明したように、電子および正孔は、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散し易くなる。そして、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散した電子および正孔は、n型非晶質膜111〜11m/p型単結晶シリコン基板101(=pn接合)による内部電界によって分離され、電子は、n型非晶質膜111〜11mを介して電極131〜13mへ到達し、正孔は、i型非晶質膜161〜16m−1およびp型非晶質膜121〜12m−1を介して電極141〜14m−1へ到達する。

The power generation mechanism in the

電極131〜13m−1へ到達した電子は、電極131〜13m−1と電極141〜14m−1との間に接続された負荷を介して電極141〜14m−1へ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子200Bは、p型単結晶シリコン基板101中で光励起された電子および正孔をp型単結晶シリコン基板101の裏面(=酸化膜102が形成されたp型単結晶シリコン基板101の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子200Bは、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜102と、酸化膜102に接して設けられたp型非晶質膜103とを備えるので、光電変換素子200において説明したように、p型単結晶シリコン基板101に対するパッシベーション効果を向上できる。

The

また、光電変換素子200Bにおいては、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との間にi型非晶質膜161〜16m−1が存在するので、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との界面における正孔の再結合が抑制される。その結果、短絡光電流が増加し、光電変換素子200Bの変換効率を向上できる。

In the

光電変換素子200Bについてのその他の説明は、光電変換素子200についての説明と同じである。

The other description of the

図11は、実施の形態2による更に他の光電変換素子の構成を示す断面図である。実施の形態2による光電変換素子は、図11に示す光電変換素子200Cであってもよい。

FIG. 11 is a cross-sectional view illustrating a configuration of still another photoelectric conversion element according to the second embodiment. The photoelectric conversion element according to

図11を参照して、光電変換素子200Cは、図8に示す光電変換素子200にi型非晶質膜151〜15m,161〜16m−1を追加したものであり、その他は、光電変換素子200と同じである。

Referring to FIG. 11, a

i型非晶質膜151〜15m,161〜16m−1については、上述したとおりである。

The i-type

光電変換素子200Cにおいては、i型非晶質膜161の端面は、i型非晶質膜151,152に接し、i型非晶質膜162の端面は、i型非晶質膜152,153に接し、以下、同様にして、i型非晶質膜16m−1の端面は、i型非晶質膜15m−1,15mに接する。また、p型非晶質膜121の端面は、n型非晶質膜111,112に接し、p型非晶質膜122の端面は、n型非晶質膜112,113に接し、以下、同様にして、p型非晶質膜12m−1の端面は、n型非晶質膜11m−1,11mに接する。

In the

光電変換素子200Cは、図2〜図4に示す工程(a)〜工程(l)によって製造される。この場合、図2の工程(d)において、i型非晶質膜151〜15m用のi型非晶質膜がプラズマCVD法によってp型単結晶シリコン基板101上に堆積され、その後、n型非晶質膜111〜11m用のn型非晶質膜がプラズマCVD法によってi型非晶質膜151〜15m用のi型非晶質膜上に堆積される。また、図3の工程(i)において、i型非晶質膜161〜16m−1用のi型非晶質膜がプラズマCVD法によってp型単結晶シリコン基板101およびn型非晶質膜111〜11m上に堆積され、その後、p型非晶質膜121〜12m−1用のp型非晶質膜がプラズマCVD法によってi型非晶質膜161〜16m−1用のi型非晶質膜上に堆積される。そして、i型非晶質膜151〜15m用のi型非晶質膜と、i型非晶質膜161〜16m−1用のi型非晶質膜とを堆積するときのガス流量は、表1に示すi型非晶質膜51〜5mを堆積するときのガス流量と同じであり、n型非晶質膜111〜11m用のn型非晶質膜を堆積するときのガス流量は、表1に示すn型非晶質膜21〜2m−1を堆積するときのガス流量と同じであり、p型非晶質膜121〜12m−1用のp型非晶質膜を堆積するときのガス流量は、表1に示すp型非晶質膜11〜1mを堆積するときのガス流量と同じである。

The

光電変換素子200Cにおける発電機構は、光電変換素子200の発電機構と概ね同じであり、光電変換素子200において説明したように、電子および正孔は、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)における再結合が抑制され、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散し易くなる。そして、n型非晶質膜111〜11mおよびp型非晶質膜121〜12m−1側へ拡散した電子および正孔は、n型非晶質膜111〜11m/i型非晶質膜151〜15m/p型単結晶シリコン基板101(=pin接合)による内部電界によって分離され、電子は、i型非晶質膜151〜15mおよびn型非晶質膜111〜11mを介して電極131〜13mへ到達し、正孔は、i型非晶質膜161〜16m−1およびp型非晶質膜121〜12m−1を介して電極141〜14m−1へ到達する。

The power generation mechanism in the

電極131〜13mへ到達した電子は、電極131〜13mと電極141〜14m−1との間に接続された負荷を介して電極141〜14m−1へ到達し、正孔と再結合する。

The electrons that have reached the

このように、光電変換素子200Cは、p型単結晶シリコン基板101中で光励起された電子および正孔をp型単結晶シリコン基板101の裏面(=酸化膜102が形成されたp型単結晶シリコン基板101の表面と反対側の面)から取り出すバックコンタクト型の光電変換素子である。

As described above, the

そして、光電変換素子200Cは、p型単結晶シリコン基板101の光入射側の表面(テクスチャ化された表面)に接して設けられた酸化膜102と、酸化膜102に接して設けられたp型非晶質膜103とを備えるので、光電変換素子200において説明したように、p型単結晶シリコン基板101に対するパッシベーション効果を向上できる。

The

また、光電変換素子200Cにおいては、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの間にi型非晶質膜151〜15mが存在するので、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの界面における電子の再結合が抑制される。更に、光電変換素子200Cにおいては、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との間にi型非晶質膜161〜16m−1が存在するので、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との界面における正孔の再結合が抑制される。

In the

その結果、短絡光電流が増加し、光電変換素子200Cの変換効率を向上できる。

As a result, the short-circuit photocurrent increases and the conversion efficiency of the

光電変換素子200Cについてのその他の説明は、光電変換素子200についての説明と同じである。

The other description of the

光電変換素子200,200A,200B,200Cにおいては、p型単結晶シリコン基板101の光入射側の表面(=酸化膜102が形成された表面)がテクスチャ構造になっていなくてもよい。この場合、図2の工程(b)が省略される。

In the

また、光電変換素子200,200A,200B,200Cにおいては、n型非晶質膜111〜11m−1は、n型a−Siからなると説明したが、実施の形態2においては、これに限らず、n型非晶質膜111〜11m−1は、n型a−SiC、n型a−SiO、n型a−SiN、n型a−SiCN、n型a−SiGeおよびn型a−Geのいずれかからなっていてもよい。

In the

更に、光電変換素子200,200A,200B,200Cにおいては、p型非晶質膜103,121〜12mは、p型a−Siからなると説明したが、実施の形態2においては、これに限らず、p型非晶質膜103,121〜12mは、p型a−SiC、p型a−SiO、p型a−SiN、p型a−SiCN、p型a−SiGeおよびp型a−Geのいずれかからなっていてもよい。

Further, in the

更に、光電変換素子200A,200Cにおいては、i型非晶質膜151〜15mは、i型a−Siからなると説明したが、実施の形態2においては、これに限らず、i型非晶質膜151〜15mは、i型a−SiC、i型a−SiO、i型a−SiN、i型a−SiCN、およびi型a−SiGeのいずれかからなっていてもよい。

Further, in the

更に、光電変換素子200B,200Cにおいては、i型非晶質膜161〜16m−1は、i型a−Siからなると説明したが、実施の形態2においては、これに限らず、i型非晶質膜161〜16m−1は、i型a−SiC、i型a−SiO、i型a−SiN、i型a−SiCN、およびi型a−SiGeのいずれかからなっていてもよい。

Further, in the

即ち、光電変換素子200,200A,200B,200Cにおいては、n型非晶質膜111〜11mおよびp型非晶質膜103,121〜12m−1は、それぞれ、表2に示すn型非晶質膜21〜2m−1およびp型非晶質膜11〜1mを構成する材料のいずれかからなっていてもよく、光電変換素子200A,200B,200Cにおいては、i型非晶質膜151〜15mおよび/またはi型非晶質膜161〜16m−1は、それぞれ、表2に示すi型非晶質膜51〜5m,61〜6m−1を構成する材料のいずれかからなっていてもよい。

That is, in the

そして、n型a−SiC、n型a−SiO、n型a−SiN、n型a−SiCN、n型a−SiGe、n型a−Ge、p型a−SiC、p型a−SiO、p型a−SiN、p型a−SiCN、p型a−SiGe、p型a−Ge、i型a−SiC、i型a−SiO、i型a−SiN、i型a−SiCN、およびi型a−SiGeは、上述した材料ガスを用いてプラズマCVD法によって形成される。 N-type a-SiC, n-type a-SiO, n-type a-SiN, n-type a-SiCN, n-type a-SiGe, n-type a-Ge, p-type a-SiC, p-type a-SiO, p-type a-SiN, p-type a-SiCN, p-type a-SiGe, p-type a-Ge, i-type a-SiC, i-type a-SiO, i-type a-SiN, i-type a-SiCN, and i The type a-SiGe is formed by the plasma CVD method using the material gas described above.

なお、i型非晶質膜151〜15m,161〜16m−1用の材料としてi型a−Geが除外されるのは、上述したi型非晶質膜51〜5m,61〜6m−1用の材料としてi型a−Geが除外される理由と同じである。

Note that i-type a-Ge is excluded as a material for the i-type

このように、実施の形態2による光電変換素子は、p型単結晶シリコン基板101の裏面にヘテロ接合を形成したバックコンタクト型の光電変換素子であり、p型単結晶シリコン基板101の光入射側の表面に酸化膜102およびp型非晶質膜103を順次積層した構造からなる。従って、p型単結晶シリコン基板101の光入射側の表面におけるキャリア(特に、電子)の再結合を酸化膜102による界面準位の低下と、p型非晶質膜103によるFSF効果とによって抑制し、p型単結晶シリコン基板101に対するパッシベーション効果を向上できる。

As described above, the photoelectric conversion element according to

上述したように、実施の形態1においては、n型単結晶シリコン基板1の光入射側の表面に酸化膜2とn型非晶質膜3とを備える光電変換素子100,100A,100B,100Cについて説明した。また、実施の形態2においては、p型単結晶シリコン基板101の光入射側の表面に酸化膜102とn型非晶質膜103とを備える光電変換素子200,200A,200B,200Cについて説明した。

As described above, in the first embodiment, the

従って、この発明の実施の形態による光電変換素子は、第1の導電型を有する単結晶シリコン基板と、半導体基板の光入射側の表面に接して設けられた酸化膜と、酸化膜に接して設けられ、第1の導電型を有する第1の非晶質膜と、半導体基板の光入射側の表面と反対側に設けられ、第1の導電型と反対の第2の導電型を有する第2の非晶質膜と、半導体基板の面内方向において第2の非晶質膜に隣接して半導体基板の光入射側の表面と反対側に設けられ、第1の導電型を有する第3の非晶質膜とを備えていればよい。 Therefore, the photoelectric conversion element according to the embodiment of the present invention includes a single crystal silicon substrate having the first conductivity type, an oxide film provided in contact with the light incident side surface of the semiconductor substrate, and in contact with the oxide film. A first amorphous film having a first conductivity type and a second conductivity type opposite to the first conductivity type provided on the opposite side of the light incident side surface of the semiconductor substrate. The second amorphous film is provided adjacent to the second amorphous film in the in-plane direction of the semiconductor substrate on the side opposite to the light incident surface of the semiconductor substrate, and has a first conductivity type. And an amorphous film.

また、実施の形態1においては、n型単結晶シリコン基板1とp型非晶質膜11〜1mとの間に配置されたi型非晶質膜51〜5mを備える光電変換素子100A、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との間に配置されたi型非晶質膜61〜6m−1を備える光電変換素子100B、およびn型単結晶シリコン基板1とp型非晶質膜11〜1mとの間に配置されたi型非晶質膜51〜5mと、n型単結晶シリコン基板1とn型非晶質膜21〜2m−1との間に配置されたi型非晶質膜61〜6m−1とを備える光電変換素子100Cについて説明した。

In the first embodiment, the

更に、実施の形態2においては、p型単結晶シリコン基板101とn型非晶質膜111〜11mとの間に配置されたi型非晶質膜151〜15mを備える光電変換素子200A、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との間に配置されたi型非晶質膜161〜16m−1を備える光電変換素子200B、およびp型単結晶シリコン基板101とn型非晶質膜111〜11mとの間に配置されたi型非晶質膜151〜15mと、p型単結晶シリコン基板101とp型非晶質膜121〜12m−1との間に配置されたi型非晶質膜161〜16m−1とを備える光電変換素子200Cについて説明した。

Further, in the second embodiment, the

従って、この発明の実施の形態による光電変換素子は、第1の導電型を有する単結晶シリコン基板と、半導体基板の光入射側の表面に接して設けられた酸化膜と、酸化膜に接して設けられ、第1の導電型を有する第1の非晶質膜と、半導体基板の光入射側の表面と反対側に設けられ、第1の導電型と反対の第2の導電型を有する第2の非晶質膜と、半導体基板の面内方向において第2の非晶質膜に隣接して半導体基板の光入射側の表面と反対側に設けられ、第1の導電型を有する第3の非晶質膜と、単結晶シリコン基板と第2および第3の非晶質膜の少なくとも一方との間に設けられ、i型の導電型を有する非晶質膜とを備えていればよい。そして、単結晶シリコン基板と第2および第3の非晶質膜の両方との間にi型の導電型を有する非晶質膜が設けられる場合、i型の導電型を有する非晶質膜は、単結晶シリコン基板と第2の非晶質膜との間に設けられ、i型の導電型を有する第4の非晶質膜と、単結晶シリコン基板と第3の非晶質膜との間に設けられ、i型の導電型を有する第5の非晶質膜とからなる。 Therefore, the photoelectric conversion element according to the embodiment of the present invention includes a single crystal silicon substrate having the first conductivity type, an oxide film provided in contact with the light incident side surface of the semiconductor substrate, and in contact with the oxide film. A first amorphous film having a first conductivity type and a second conductivity type opposite to the first conductivity type provided on the opposite side of the light incident side surface of the semiconductor substrate. The second amorphous film is provided adjacent to the second amorphous film in the in-plane direction of the semiconductor substrate on the side opposite to the light incident surface of the semiconductor substrate, and has a first conductivity type. And an amorphous film having an i-type conductivity type provided between the single crystal silicon substrate and at least one of the second and third amorphous films. . When an amorphous film having i-type conductivity is provided between the single crystal silicon substrate and both the second and third amorphous films, the amorphous film having i-type conductivity is provided. Is provided between the single crystal silicon substrate and the second amorphous film, and has a fourth amorphous film having i-type conductivity, a single crystal silicon substrate, and a third amorphous film. And a fifth amorphous film having i-type conductivity.

更に、この発明の実施の形態による光電変換素子の製造方法は、単結晶シリコン基板の光入射側の表面に接して酸化膜2(または酸化膜102)を形成する工程と、酸化膜2(または酸化膜102)を形成する工程の後にp型非晶質膜11〜1m、n型非晶質膜3,21〜2m−1、反射防止膜4および電極31〜3m,41〜4m−1(またはn型非晶質膜111〜11m、p型非晶質膜103,121〜12m−1、反射防止膜104および電極131〜13m,141〜14m−1)を形成する工程とを備えていればよい。

Furthermore, the method for manufacturing the photoelectric conversion element according to the embodiment of the present invention includes a step of forming the oxide film 2 (or oxide film 102) in contact with the light incident side surface of the single crystal silicon substrate, and the oxide film 2 (or After the step of forming the oxide film 102), the p-type amorphous film 11-1m, the n-type

従って、この発明の実施の形態による光電変換素子の製造方法は、第1の導電型を有する単結晶シリコンからなる半導体基板の光入射側の表面に接して酸化膜を形成する第1の工程と、第1の工程の後、酸化膜に接して第1の導電型を有する第1の非晶質膜を堆積する第2の工程と、第1の工程の後、半導体基板の光入射側の表面と反対側に第1の導電型と反対の第2の導電型を有する第2の非晶質膜を堆積する第3の工程と、半導体基板の面内方向において第2の非晶質膜に隣接して半導体基板の光入射側の表面と反対側に第1の導電型を有する第3の非晶質膜を堆積する第4の工程とを備えていればよい。 Therefore, the method for manufacturing the photoelectric conversion element according to the embodiment of the present invention includes the first step of forming an oxide film in contact with the light incident side surface of the semiconductor substrate made of single crystal silicon having the first conductivity type. After the first step, a second step of depositing a first amorphous film having the first conductivity type in contact with the oxide film, and after the first step, on the light incident side of the semiconductor substrate A third step of depositing a second amorphous film having a second conductivity type opposite to the first conductivity type on the side opposite to the surface; and a second amorphous film in an in-plane direction of the semiconductor substrate And a fourth step of depositing a third amorphous film having the first conductivity type on the opposite side of the light incident surface of the semiconductor substrate.

なお、実施の形態1においては、第1の導電型は、n型であり、第2の導電型は、p型である。また、実施の形態2においては、第1の導電型は、p型であり、第2の導電型は、n型である。 In the first embodiment, the first conductivity type is n-type, and the second conductivity type is p-type. In the second embodiment, the first conductivity type is p-type, and the second conductivity type is n-type.

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。 The embodiment disclosed this time should be considered as illustrative in all points and not restrictive. The scope of the present invention is shown not by the above description of the embodiments but by the scope of claims for patent, and is intended to include meanings equivalent to the scope of claims for patent and all modifications within the scope.

この発明は、光電変換素子およびその製造方法に適用される。 The present invention is applied to a photoelectric conversion element and a manufacturing method thereof.

1 n型単結晶シリコン基板、2,102 酸化膜、11〜1m,20,121〜12m−1 p型非晶質膜、21〜2m−1,40,111〜11m n型非晶質膜、30,50 レジストパターン、31〜3m,41〜4m−1,131〜13m,141〜14m−1 電極、100,100A,100B,100C,200,200A,200B,200C,200C 光電変換素子、51〜5m,61〜6m−1,151〜15m,161〜16m−1 i型非晶質膜、101 p型単結晶シリコン基板。 1 n-type single crystal silicon substrate, 2,102 oxide film, 11-1m, 20, 121-12m-1 p-type amorphous film, 21-2m-1, 40, 111-11m n-type amorphous film, 30, 50 resist pattern, 31-3m, 41-4m-1, 131-13m, 141-14m-1 electrode, 100, 100A, 100B, 100C, 200, 200A, 200B, 200C, 200C photoelectric conversion element, 51- 5m, 61-6m-1, 151-15m, 161-16m-1 i-type amorphous film, 101 p-type single crystal silicon substrate.

Claims (13)

前記半導体基板の光入射側の表面に接して設けられた酸化膜と、

前記酸化膜に接して設けられ、前記第1の導電型を有する第1の非晶質膜と、

前記半導体基板の光入射側の表面と反対側に設けられ、前記第1の導電型と反対の第2の導電型を有する第2の非晶質膜と、

前記半導体基板の面内方向において前記第2の非晶質膜に隣接して前記半導体基板の光入射側の表面と反対側に設けられ、前記第1の導電型を有する第3の非晶質膜とを備える光電変換素子。 A semiconductor substrate made of single crystal silicon having a first conductivity type;

An oxide film provided in contact with the light incident surface of the semiconductor substrate;

A first amorphous film provided in contact with the oxide film and having the first conductivity type;

A second amorphous film provided on the opposite side of the light incident surface of the semiconductor substrate and having a second conductivity type opposite to the first conductivity type;

A third amorphous material having the first conductivity type, which is provided adjacent to the second amorphous film in the in-plane direction of the semiconductor substrate, on the opposite side of the light incident surface of the semiconductor substrate. A photoelectric conversion element comprising a film.

前記半導体基板と前記第3の非晶質層との間に設けられ、i型の導電型を有する第5の非晶質膜とを更に備える、請求項1に記載の光電変換素子。 A fourth amorphous film provided between the semiconductor substrate and the second amorphous layer and having i-type conductivity;

The photoelectric conversion element according to claim 1, further comprising a fifth amorphous film that is provided between the semiconductor substrate and the third amorphous layer and has an i-type conductivity type.

前記第1の非晶質膜は、n型非晶質膜からなり、

前記第2の非晶質膜は、p型非晶質膜からなり、

前記第3の非晶質膜は、n型非晶質膜からなる、請求項1から請求項7のいずれか1項に記載の光電変換素子。 The semiconductor substrate is made of n-type single crystal silicon,

The first amorphous film is an n-type amorphous film,

The second amorphous film is a p-type amorphous film,

The photoelectric conversion element according to claim 1, wherein the third amorphous film is an n-type amorphous film.

前記第2の非晶質膜は、p型アモルファスシリコンカーバイド、p型アモルファスシリコンナイトライド、p型アモルファスシリコンカーボンナイトライド、p型アモルファスシリコンオキサイド、p型アモルファスシリコン、p型アモルファスシリコンゲルマニウムおよびp型アモルファスゲルマニウムのいずれかからなり、

前記第3の非晶質膜は、n型アモルファスシリコンカーバイド、n型アモルファスシリコンナイトライド、n型アモルファスシリコンカーボンナイトライド、n型アモルファスシリコンオキサイド、n型アモルファスシリコン、n型アモルファスシリコンゲルマニウムおよびn型アモルファスゲルマニウムのいずれかからなる、請求項8に記載の光電変換素子。 The first amorphous film includes n-type amorphous silicon carbide, n-type amorphous silicon nitride, n-type amorphous silicon carbon nitride, n-type amorphous silicon oxide, n-type amorphous silicon, n-type amorphous silicon germanium, and n-type. Made of either amorphous germanium,

The second amorphous film includes p-type amorphous silicon carbide, p-type amorphous silicon nitride, p-type amorphous silicon carbon nitride, p-type amorphous silicon oxide, p-type amorphous silicon, p-type amorphous silicon germanium, and p-type. Made of either amorphous germanium,

The third amorphous film includes n-type amorphous silicon carbide, n-type amorphous silicon nitride, n-type amorphous silicon carbon nitride, n-type amorphous silicon oxide, n-type amorphous silicon, n-type amorphous silicon germanium, and n-type. The photoelectric conversion element according to claim 8, comprising any one of amorphous germanium.

前記第1の非晶質膜は、p型非晶質膜からなり、

前記第2の非晶質膜は、n型非晶質膜からなり、

前記第3の非晶質膜は、p型非晶質膜からなる、請求項1から請求項7のいずれか1項に記載の光電変換素子。 The semiconductor substrate is made of p-type single crystal silicon,

The first amorphous film is a p-type amorphous film,

The second amorphous film is an n-type amorphous film,

The photoelectric conversion element according to any one of claims 1 to 7, wherein the third amorphous film is a p-type amorphous film.

前記第2の非晶質膜は、n型アモルファスシリコンカーバイド、n型アモルファスシリコンナイトライド、n型アモルファスシリコンカーボンナイトライド、n型アモルファスシリコンオキサイド、n型アモルファスシリコン、n型アモルファスシリコンゲルマニウムおよびn型アモルファスゲルマニウムのいずれかからなり、

前記第3の非晶質膜は、p型アモルファスシリコンカーバイド、p型アモルファスシリコンナイトライド、p型アモルファスシリコンカーボンナイトライド、p型アモルファスシリコンオキサイド、p型アモルファスシリコン、p型アモルファスシリコンゲルマニウムおよびp型アモルファスゲルマニウムのいずれかからなる、請求項10に記載の光電変換素子。 The first amorphous film includes p-type amorphous silicon carbide, p-type amorphous silicon nitride, p-type amorphous silicon carbon nitride, p-type amorphous silicon oxide, p-type amorphous silicon, p-type amorphous silicon germanium, and p-type. Made of either amorphous germanium,

The second amorphous film includes n-type amorphous silicon carbide, n-type amorphous silicon nitride, n-type amorphous silicon carbon nitride, n-type amorphous silicon oxide, n-type amorphous silicon, n-type amorphous silicon germanium, and n-type. Made of either amorphous germanium,

The third amorphous film includes p-type amorphous silicon carbide, p-type amorphous silicon nitride, p-type amorphous silicon carbon nitride, p-type amorphous silicon oxide, p-type amorphous silicon, p-type amorphous silicon germanium, and p-type. The photoelectric conversion element according to claim 10, comprising any of amorphous germanium.

前記第1の工程の後、前記酸化膜に接して前記第1の導電型を有する第1の非晶質膜を堆積する第2の工程と、

前記第1の工程の後、前記半導体基板の光入射側の表面と反対側に前記第1の導電型と反対の第2の導電型を有する第2の非晶質膜を堆積する第3の工程と、

前記半導体基板の面内方向において前記第2の非晶質膜に隣接して前記半導体基板の光入射側の表面と反対側に前記第1の導電型を有する第3の非晶質膜を堆積する第4の工程とを備える光電変換素子の製造方法。 A first step of forming an oxide film in contact with the light incident surface of a semiconductor substrate made of single crystal silicon having a first conductivity type;

A second step of depositing a first amorphous film having the first conductivity type in contact with the oxide film after the first step;

After the first step, a third amorphous film having a second conductivity type opposite to the first conductivity type is deposited on the opposite side of the light incident side surface of the semiconductor substrate. Process,

A third amorphous film having the first conductivity type is deposited on the opposite side of the light incident side surface of the semiconductor substrate adjacent to the second amorphous film in the in-plane direction of the semiconductor substrate. A manufacturing method of a photoelectric conversion element provided with the 4th process to do.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011274354A JP2013125890A (en) | 2011-12-15 | 2011-12-15 | Photoelectric conversion element and manufacturing method of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011274354A JP2013125890A (en) | 2011-12-15 | 2011-12-15 | Photoelectric conversion element and manufacturing method of the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013125890A true JP2013125890A (en) | 2013-06-24 |

| JP2013125890A5 JP2013125890A5 (en) | 2015-08-06 |

Family

ID=48776962

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011274354A Pending JP2013125890A (en) | 2011-12-15 | 2011-12-15 | Photoelectric conversion element and manufacturing method of the same |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2013125890A (en) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5734512B2 (en) * | 2012-05-14 | 2015-06-17 | 三菱電機株式会社 | Photoelectric conversion device, manufacturing method thereof, and photoelectric conversion module |

| WO2018061769A1 (en) * | 2016-09-27 | 2018-04-05 | パナソニックIpマネジメント株式会社 | Solar cell and method for producing solar cell |

| JP2021516873A (en) * | 2018-11-27 | 2021-07-08 | チンアオ ソーラー カンパニー リミテッド | Crystalline silicon solar cells and their manufacturing methods, photovoltaic modules |

| US11961930B2 (en) | 2018-11-27 | 2024-04-16 | Jingao Solar Co., Ltd. | Crystalline silicon solar cell and preparation method therefor, and photovoltaic assembly |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008021993A (en) * | 2006-06-30 | 2008-01-31 | General Electric Co <Ge> | Photovoltaic device including all-back-contact configuration, and related method |

| JP2009535845A (en) * | 2006-05-04 | 2009-10-01 | サンパワー コーポレイション | Solar cell with doped semiconductor heterojunction electrode |

| JP2010504636A (en) * | 2006-09-26 | 2010-02-12 | コミサリア、ア、レネルジ、アトミク | Back heterojunction solar cell manufacturing method |

| JP2010183080A (en) * | 2009-02-04 | 2010-08-19 | Lg Electronics Inc | Solar cell and method for manufacturing the same |

| JP2013102159A (en) * | 2011-11-07 | 2013-05-23 | Samsung Sdi Co Ltd | Photoelectric conversion element and method for manufacturing the same |

-

2011

- 2011-12-15 JP JP2011274354A patent/JP2013125890A/en active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009535845A (en) * | 2006-05-04 | 2009-10-01 | サンパワー コーポレイション | Solar cell with doped semiconductor heterojunction electrode |

| JP2008021993A (en) * | 2006-06-30 | 2008-01-31 | General Electric Co <Ge> | Photovoltaic device including all-back-contact configuration, and related method |

| JP2010504636A (en) * | 2006-09-26 | 2010-02-12 | コミサリア、ア、レネルジ、アトミク | Back heterojunction solar cell manufacturing method |

| JP2010183080A (en) * | 2009-02-04 | 2010-08-19 | Lg Electronics Inc | Solar cell and method for manufacturing the same |

| JP2013102159A (en) * | 2011-11-07 | 2013-05-23 | Samsung Sdi Co Ltd | Photoelectric conversion element and method for manufacturing the same |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5734512B2 (en) * | 2012-05-14 | 2015-06-17 | 三菱電機株式会社 | Photoelectric conversion device, manufacturing method thereof, and photoelectric conversion module |

| JPWO2013172056A1 (en) * | 2012-05-14 | 2016-01-12 | 三菱電機株式会社 | Photoelectric conversion device, manufacturing method thereof, and photoelectric conversion module |

| WO2018061769A1 (en) * | 2016-09-27 | 2018-04-05 | パナソニックIpマネジメント株式会社 | Solar cell and method for producing solar cell |

| JPWO2018061769A1 (en) * | 2016-09-27 | 2019-07-04 | パナソニックIpマネジメント株式会社 | Solar cell and method of manufacturing solar cell |

| JP2021516873A (en) * | 2018-11-27 | 2021-07-08 | チンアオ ソーラー カンパニー リミテッド | Crystalline silicon solar cells and their manufacturing methods, photovoltaic modules |

| JP7068541B2 (en) | 2018-11-27 | 2022-05-16 | チンアオ ソーラー カンパニー リミテッド | Crystalline silicon solar cells and their manufacturing methods, photovoltaic modules |

| US11961930B2 (en) | 2018-11-27 | 2024-04-16 | Jingao Solar Co., Ltd. | Crystalline silicon solar cell and preparation method therefor, and photovoltaic assembly |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2023050822A1 (en) | Method for manufacturing back-contact cell | |

| JP2009524916A (en) | Solar cell | |

| JP6404825B2 (en) | Photoelectric conversion element | |

| NL2023003B1 (en) | Method for preparing full back-contact electrode cell with efficient light trapping and selective doping | |

| CN210926046U (en) | Solar cell | |

| JP2013191656A (en) | Photoelectric conversion element and manufacturing method thereof | |

| CN112510121B (en) | Pre-and-post alkali polishing protection process for perc battery | |

| JP2013511839A (en) | Photovoltaic cell manufacturing method, photovoltaic cell manufactured thereby, and use thereof | |

| CN113644142A (en) | Solar cell with passivation contact and preparation method thereof | |

| CN112820793A (en) | Solar cell and preparation method thereof | |

| JP6032911B2 (en) | Photoelectric conversion element and manufacturing method thereof | |

| WO2015060013A1 (en) | Photoelectric conversion element | |

| CN214753785U (en) | Solar cell with single-side passivation contact | |

| JP2013125890A (en) | Photoelectric conversion element and manufacturing method of the same | |

| JP2013115262A (en) | Photoelectric conversion element | |

| JP2013214672A (en) | Photoelectric conversion element | |

| CN113224210A (en) | Preparation method of P-type IBC battery | |

| JP2013191657A (en) | Photoelectric conversion element and manufacturing method thereof | |

| Wang et al. | Crystal silicon heterojunction solar cells by hot-wire CVD | |

| CN215220733U (en) | Solar cell and front film layer structure thereof, cell module and photovoltaic system | |

| JP2013125891A (en) | Photoelectric conversion element and manufacturing method of the same | |

| CN112382680A (en) | HJT battery and preparation method thereof based on laser induction | |

| JP5956742B2 (en) | Photoelectric conversion element | |

| WO2006049003A1 (en) | Process for producing thin-film photoelectric converter | |

| JP2013197158A (en) | Photoelectric conversion element and manufacturing method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141202 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150522 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150909 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150915 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160126 |