JP2012191005A - 固体撮像素子、固体撮像素子の製造方法および撮像装置 - Google Patents

固体撮像素子、固体撮像素子の製造方法および撮像装置 Download PDFInfo

- Publication number

- JP2012191005A JP2012191005A JP2011053237A JP2011053237A JP2012191005A JP 2012191005 A JP2012191005 A JP 2012191005A JP 2011053237 A JP2011053237 A JP 2011053237A JP 2011053237 A JP2011053237 A JP 2011053237A JP 2012191005 A JP2012191005 A JP 2012191005A

- Authority

- JP

- Japan

- Prior art keywords

- film

- layer

- solid

- imaging device

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000003384 imaging method Methods 0.000 title claims description 95

- 238000004519 manufacturing process Methods 0.000 title claims description 19

- 239000007787 solid Substances 0.000 title abstract 3

- 239000000758 substrate Substances 0.000 claims abstract description 70

- 239000004065 semiconductor Substances 0.000 claims abstract description 62

- 230000003287 optical effect Effects 0.000 claims abstract description 17

- 238000006243 chemical reaction Methods 0.000 claims abstract description 12

- 238000000034 method Methods 0.000 claims description 128

- 238000000231 atomic layer deposition Methods 0.000 claims description 72

- 238000005240 physical vapour deposition Methods 0.000 claims description 46

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 31

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 31

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 claims description 31

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 30

- 229910001936 tantalum oxide Inorganic materials 0.000 claims description 30

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 29

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 28

- 229910052751 metal Inorganic materials 0.000 claims description 21

- 239000002184 metal Substances 0.000 claims description 21

- 238000005229 chemical vapour deposition Methods 0.000 claims description 19

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 claims description 16

- 229910001928 zirconium oxide Inorganic materials 0.000 claims description 16

- 238000012545 processing Methods 0.000 claims description 14

- 239000010410 layer Substances 0.000 description 297

- 238000009825 accumulation Methods 0.000 description 32

- 238000012986 modification Methods 0.000 description 18

- 230000004048 modification Effects 0.000 description 18

- 230000015572 biosynthetic process Effects 0.000 description 15

- 239000000463 material Substances 0.000 description 14

- 238000003860 storage Methods 0.000 description 12

- 229910052845 zircon Inorganic materials 0.000 description 12

- GFQYVLUOOAAOGM-UHFFFAOYSA-N zirconium(iv) silicate Chemical compound [Zr+4].[O-][Si]([O-])([O-])[O-] GFQYVLUOOAAOGM-UHFFFAOYSA-N 0.000 description 12

- 238000010586 diagram Methods 0.000 description 11

- 230000000694 effects Effects 0.000 description 9

- 239000002243 precursor Substances 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 239000012528 membrane Substances 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229910052761 rare earth metal Inorganic materials 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 229910052735 hafnium Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 125000002524 organometallic group Chemical group 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 229910052773 Promethium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- -1 hafnium nitride Chemical class 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- VQMWBBYLQSCNPO-UHFFFAOYSA-N promethium atom Chemical compound [Pm] VQMWBBYLQSCNPO-UHFFFAOYSA-N 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1463—Pixel isolation structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14641—Electronic components shared by two or more pixel-elements, e.g. one amplifier shared by two pixel elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14685—Process for coatings or optical elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/148—Charge coupled imagers

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

Abstract

【課題】暗電流を抑制することができる固体撮像素子を提供する。

【解決手段】固体撮像素子は、光電変換が行われるフォトダイオードが形成された有効領域と、遮光膜により遮光された光学的黒領域とが形成された半導体基板と、前記有効領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第1の膜と、前記遮光領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第2の膜と、を備え、前記第1の膜が有する層の数が前記第2の膜が有する層の数と異なる。

【選択図】図1

【解決手段】固体撮像素子は、光電変換が行われるフォトダイオードが形成された有効領域と、遮光膜により遮光された光学的黒領域とが形成された半導体基板と、前記有効領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第1の膜と、前記遮光領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第2の膜と、を備え、前記第1の膜が有する層の数が前記第2の膜が有する層の数と異なる。

【選択図】図1

Description

本開示は、固体撮像素子、固体撮像素子の製造方法および撮像装置に関する。

CCD(Charge Coupled Device)型やCMOS(Complementary Metal Oxide Semiconductor)型の固体撮像素子では、フォトダイオードにおける結晶欠陥や、半導体基板に形成された受光部とその上の絶縁層との界面における界面準位が、暗電流の原因となることが知られている。

そこで、暗電流の発生を抑制する技術として、半導体基板の全面、例えば、受光画素領域(以下、「有効領域」という)および光学的黒領域(以下、「OB領域」という)上に、負の固定電荷を持つ膜を形成する技術が提案されている。この技術では、半導体基板上に負の固定電荷を持つ膜を形成し、受光部と絶縁層との界面付近に正電荷(ホール)を蓄積することで、界面準位に起因する暗電流の発生を抑制している。

しかしながら、界面準位に起因する暗電流は、有効領域とOB領域とでは、その案電流量が異なる。従って、上述した負の固定電荷を有する膜を半導体基板の全面に形成する場合には、全体的な暗電流量は低減するものの、有効領域とOB領域との暗電流差が発生し、いわゆるOB段差が発生することが問題となっている。

かかる問題に鑑みて、本発明は、有効領域における暗電流と光学的黒領域における暗電流との差を小さくすることができ、いわゆるOB段差を改善することができる固体撮像素子、固体撮像素子の製造方法および撮像装置を提供するものである。

そこで、本開示の固体撮像素子は、光電変換が行われるフォトダイオードが形成された有効領域と、遮光膜により遮光された光学的黒領域とが形成された半導体基板と、前記有効領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第1の膜と、前記遮光領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第2の膜と、を備え、前記第1の膜が有する層の数が前記第2の膜が有する層の数と異なるものである。

また、本開示の固体撮像素子においては、前記第1の膜は、前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、前記第1層上に、前記原子層蒸着法または前記有機金属化学的気相成長法を用いて形成された第2層と、前記第2層上に、物理的気相成長を用いて形成された第3層と、を有し、前記第2の膜は、前記半導体基板上に、前記原子層蒸着法または前記有機金属化学的気相成長法を用いて形成された第1層と、前記第1層上に、前記物理的気相成長を用いて形成された第2層と、を有するものである。

また、本開示の固体撮像素子においては、前記第1の膜は、前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、前記第1層上に、物理的気相成長を用いて形成された第2層と、有し、前記第2の膜は、前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、前記第1層上に、物理的気相成長を用いて形成された第2層と、前記第2層上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第3層と、を有するものである。

また、本開示の固体撮像素子においては、前記第1の膜は、前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、前記第1層上に、物理的気相成長を用いて形成された第2層と、前記第2層上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第3層と、を有し、前記第2の膜は、前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層を有するものである。

また、本開示の固体撮像素子においては、前記第1の膜および前記第2の膜を構成する層は、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなるものである。

また、本開示の固体撮像素子の製造方法は、半導体基板に、光電変換が行われるフォトダイオードが形成された有効領域および遮光膜により遮光された光学的黒領域を形成する工程と、前記有効領域上に負の固定電荷を有する層が少なくとも1層以上積層された第1の膜を形成する工程と、前記遮光領域上に、負の固定電荷を有する層が少なくとも1層以上積層され、前記第1の膜が有する層の数とは異なる数の層を有する第2の膜を形成する工程と、を有するものである。

また、本開示の撮像装置は、前記固体撮像素子と、前記固体撮像素子に被写体像を結像する光学系と、前記固体撮像素子を駆動させる駆動パルスを生成する駆動部と、前記固体撮像素子の出力画像信号を処理する信号処理回路と、を備えるものである。

本開示によれば、有効領域における暗電流と光学的黒領域における暗電流との差を小さくすることができ、いわゆるOB段差を改善することができる。

本開示に係る固体撮像素子では、固体撮像素子の半導体基板におけるフォトダイオードが形成された有効領域上に、負の固定電荷を有する第1の膜(以下、「第1の膜」という)を形成し、遮光膜により遮光された光学的黒領域上に、第1の膜とは積層される層の数が異なる負の固定電荷を有する第2の膜(以下、「第2の膜」という)を形成する。

第1の膜は、例えば、半導体基板上に形成された第1層と、この第1層上に形成された第2層と、この第2層上に形成された第3層とにより構成される。

第1の膜を構成する第1層および第2層は、ALD(Atomic Layer Deposition;原子層蒸着)法またはMOCVD(Metal Organic Chemical Vapor Deposition;有機金属化学的気相成長)法を用いて形成する。また、第1の膜を構成する第3層は、PVD(Physical Vapor Deposition;物理的気相成長)法により形成する。

また、第2の膜は、例えば、半導体基板上に形成された第1層と、この第1層上に形成された第2層とにより構成される。第2の膜を構成する第1層は、ALD法またはMOCVD法を用いて形成する。また、第2の膜を構成する第2層は、PVD法により形成する。

第1の膜および第2の膜を構成する層の材料としては、例えば、酸化ハフニウム(HfO2)、酸化アルミニウム(Al2O3)、酸化ジルコン(ZrO2)、酸化タンタル(Ta2O5)および酸化チタン(TiO2)等の酸化物が挙げられる。これらの酸化物の層は、絶縁ゲート型電界効果トランジスタのゲート絶縁膜等に用いられている実績があるため、形成方法が確立されており、容易に形成することができる。

また、これらの材料のうち、特に、屈折率の比較的高い、酸化ハフニウム(屈折率2.05)、酸化タンタル(屈折率2.16)、酸化チタン(屈折率2.20)等を形成した場合には、反射防止効果をも得ることも可能になる。

上記以外の材料としては、例えば、希土類元素の酸化物が挙げられる。即ち、ランタン、プラセオジム、セリウム、ネオジム、プロメチウム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、ルテチウム、イットリウムの各酸化物が挙げられる。

さらにまた、窒化ハフニウム、窒化アルミニウム、酸窒化ハフニウム、酸窒化アルミニウムを使用することも可能である。

さらにまた、窒化ハフニウム、窒化アルミニウム、酸窒化ハフニウム、酸窒化アルミニウムを使用することも可能である。

負の固定電荷を有する第1層、第2層、第3層に、絶縁性を損なわない範囲で、層中にシリコン(Si)や窒素(N)が添加されていてもよい。その場合、シリコンや窒素の濃度は、層の絶縁性が損なわれない範囲で適宜決定される。このように、シリコンや窒素が添加されることによって、各層の耐熱性やプロセスの中でのイオン注入の阻止能力を上げることが可能になる。

第1の膜を構成する第1層および第2層、および第2の膜を構成する第1層は、上述のとおり、ALD法またはMOCVD法を用いて形成する。ALD法により第1の膜を形成する場合には、例えば、基板温度が200〜500℃、プリカーサの流量が10〜500sccm、プリカーサの照射時間が1〜15秒、O3の流量が5〜50sccmの条件とする。また、MOCVD法により第1の膜を形成する場合には、例えば、基板温度が200〜600℃の条件とする。

なお、半導体基板がシリコン層であり、その上に第1の膜を構成する第1層や第2の膜を構成する第1層をALD法により形成した場合には、同時に、シリコン層の表面に界面準位を低減する酸化シリコン膜を厚さ1nm程度形成することが可能になる。

第1の膜を構成する第2層は、上述のとおり、ALD法またはMOCVD法を用いて形成する。ALD法により、第1の膜を構成する第2層を形成する場合には、例えば、基板温度が200〜500℃、プリカーサの流量が10〜500sccm、プリカーサの照射時間が1〜15秒、O3の流量が5〜50sccmの条件とする。また、MOCVD法により、第1の膜を構成する第2層を形成する場合には、例えば、基板温度が200〜600℃の条件とする。

また、第1の膜を構成する第3層および第2の膜を構成する第2層は、上述のとおり、PVD法を用いて形成する。PVD法により、第1の膜を構成する第3層、および第2の膜を構成する第2層を形成する際には、例えば、圧力が0.01〜50Pa、パワーが500〜2000W、Arの流量が5〜50sccm、O2の流量が5〜50sccmの条件とする。

PVD法により、第1の膜を構成する第3層、および第2の膜を構成する第2層を形成するので、ALD法やMOCVD法と比較して形成速度が速くなり、比較的短い時間で、ある程度厚い膜を形成することが可能になる。

第1の膜を構成する第2層の膜厚、および第2の膜を構成する第1層の膜厚は、特に限定されないが、第1の膜を構成する第3層、および第2の膜を構成する第2層をPVD法により形成する際に半導体基板にダメージを与えることがないように、第1の膜を構成する第2層、および第2の膜を構成する第1層にはある程度以上の厚さが必要である。好ましくは、第1の膜の膜厚を1nm以上とする。

また、第1の膜を構成する第2層、および第2の膜を構成する第1層は、ALD法またはMOCVD法によって形成するため、厚く形成するには時間がかかる。そのため、第1の膜を構成する第2層および第2の膜を構成する第1層の厚さは、5nm程度以下とすることが好ましい。

また、第1の膜を構成する第2層、および第2の膜を構成する第1層は、ALD法またはMOCVD法によって形成するため、厚く形成するには時間がかかる。そのため、第1の膜を構成する第2層および第2の膜を構成する第1層の厚さは、5nm程度以下とすることが好ましい。

本開示に係る固体撮像素子では、有効領域上にて第1層上に第2層を形成し、さらに、第2層上に第3層を形成する第1の膜を備えているため、3つの層を合わせて、充分な負バイアス効果が得られる。また、OB領域上にて第1層上に第2層を形成する第2の膜を備えているため、2つの層を合わせて、充分な負バイアス効果が得られる。

特に、有効領域における第1の膜と、OB領域における第2の膜との膜構造を異なるようにしたため、有効領域における暗電流とOB領域における暗電流の差を小さくして、いわゆるOB段差を改善することができる。また、暗電流量の負の固定電荷を有する膜厚依存性により、各固体撮像素子の暗電流量に合わせて膜厚を調整することでOB段差を調整することもできる。

また、有効領域における第1の膜とOB領域における第2の膜の膜厚を個別に変更することができるため、第1の膜側から受光する場合では、受光画素部は負の固定電荷を有する膜を反射防止膜としての最適膜厚を選択できる。

また、OB領域においては、光の入射を考慮する必要がないため反射防止膜的な効果から離れ暗電流改善のみで第2の膜の膜厚を調整することができる。

また、第1の膜を構成する第2層および第2の膜を構成する第1層をALD法またはMOCVD法を用いて形成するので、第1の膜を構成する第2層および第2の膜を構成する第1層を形成する際に半導体基板にダメージを与えないようにすることができる。

上述したように、本開示によれば、第1の膜の膜厚と、第2の膜の膜厚とを個別に調整することができる。これにより、第1の膜の膜厚を、反射防止膜としての機能を発揮する最適な膜厚にすることができる。

さらに、光学的黒領域には光が入射しないため、第2の膜が反射防止膜としての機能を有する必要がないため、暗電流を改善するための最適な膜厚にすることができる。

以下に、本開示の実施形態に係る固体撮像素子について、図面を参照して説明する。各図において、同一の構成要素には同一の符号を付してある。なお、説明は以下の順序で行う。

1.固体撮像素子の構成

2.固体撮像素子の製造方法

3.撮像装置の構成等

4.その他の固体撮像素子の構成及び製造方法

1.固体撮像素子の構成

2.固体撮像素子の製造方法

3.撮像装置の構成等

4.その他の固体撮像素子の構成及び製造方法

〔1.固体撮像素子の構成〕

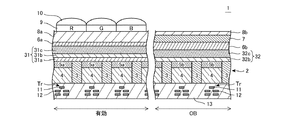

まず、本実施形態に係る固体撮像素子1の構成について、図1を参照して説明する。図1は、本実施形態に係る固体撮像素子の断面構造を示す図である。なお、本実施形態では、本発明を、いわゆる裏面照射型のCMOS固体撮像素子(CMOSイメージセンサ)に適用した例について説明する。

まず、本実施形態に係る固体撮像素子1の構成について、図1を参照して説明する。図1は、本実施形態に係る固体撮像素子の断面構造を示す図である。なお、本実施形態では、本発明を、いわゆる裏面照射型のCMOS固体撮像素子(CMOSイメージセンサ)に適用した例について説明する。

固体撮像素子1は、半導体基板2における有効領域21およびOB領域22に、入射光を光電変換する受光部として、フォトダイオードとなる電荷蓄積領域4が、N型の不純物領域によって形成されている。この電荷蓄積領域4の表面には、正電荷蓄積領域5が形成されており、これら電荷蓄積領域4および正電荷蓄積領域5によって、HAD(Hole-Accumulation Diode sensor)構造が構成されている。なお、それぞれの電荷蓄積領域4および正電荷蓄積領域5は、素子分離領域3により分離されている。

半導体基板2の表面側においては、半導体基板2の電荷蓄積領域4の下方に、MOSトランジスタTrのゲート電極11が形成され、さらに下方に金属配線による配線層12が形成されている。

ゲート電極11および各層の配線層12の間は、層間の絶縁層13によって絶縁されている。なお、絶縁層13は、図示しないが、下方に設けられる支持基板等によって支持されている。

電荷蓄積領域4を有するフォトダイオードによって、それぞれの画素が構成される。各画素には、図示のMOSトランジスタ(この場合は、電荷蓄積領域4に蓄積した電荷を読み出し・転送する転送トランジスタ)Trを含む、1個以上のトランジスタを有して構成される。

各画素の電荷蓄積領域4の間は、P型の素子分離領域3により分離されている。なお、図示しないが、電荷蓄積領域4のMOSトランジスタTrのゲート電極11側の界面に、p+半導体領域を形成して、絶縁層13との界面における暗電流の発生を抑制することが好ましい。

半導体基板2の裏面側において、有効領域21の上層には、負の固定電荷を有する第1の膜(以下、「第1の膜」という)31が形成されている。この第1の膜31は、半導体基板2上に形成された第1層31aと、この第1層31a上に形成された第2層31bと、この第2層31b上に形成された第3層31cとが積層された構成を有する。

第1層31aは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜を有し、ALD法またはMOCVD法により形成される。

また、第2層31bは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜を有し、ALD法またはMOCVD法により形成される。

第1層31a、第2層31bは、いずれもALD法又はMOCVD法で形成されるため、第1層31a、第2層31bをあわせてALD層とも称する。

第1層31a、第2層31bは、いずれもALD法又はMOCVD法で形成されるため、第1層31a、第2層31bをあわせてALD層とも称する。

また、第3層31cは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜を有し、PVD法により形成される。従って、第3層31cをPVD層とも称する。

このように、有効領域21の上層に負の固定電荷を有する第1層31a、第2層31b、第3層31cが積層された第1の膜31を形成している。第1の膜31の中の負の固定電荷によって、電荷蓄積領域4の表面に電界が加わり、電荷蓄積領域4の表面に正電荷蓄積領域5が形成される。これにより、電荷蓄積領域4の表面にイオン注入をしなくても、正電荷蓄積領域5を形成することが可能になる。

第1の膜31上には、例えば酸化シリコン(SiO2)膜からなる絶縁膜6aが形成されており、この絶縁膜6aの上には、平坦化膜8aが形成されている。また、平坦化膜8aの上には、画素毎に、対応する色(赤R、緑G、青B)のカラーフィルタ9が形成されており、各カラーフィルタ9の上には、それぞれ、集光のためのオンチップレンズ10が設けられている。

OB領域22の上層には、負の固定電荷を有する第2の膜(以下、「第2の膜」という)32が形成されている。この第2の膜32は、半導体基板2上に形成された第1層32bと、この第1層32b上に形成された第2層32cとが積層された構成を有する。

第1層32bは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜を有し、ALD法またはMOCVD法により形成される。従って、第1層32bをALD層とも称する。

第2層32cは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜を有し、PVD法により形成される。従って、第2層32cをPVD層とも称する。

このように、OB領域22の上層に、負の固定電荷を有する第1層32b及び第2層32cが積層された第2の膜32を形成しているため、この第2の膜32の中の負の固定電荷によって、電荷蓄積領域4の表面に電界が加わり、電荷蓄積領域4の表面に正電荷蓄積領域5が形成される。これにより、電荷蓄積領域4の表面にイオン注入をしなくても、正電荷蓄積領域5を形成することが可能になる。

第2の膜32上には、例えば酸化シリコン膜からなる絶縁膜6bが形成されており、この絶縁膜6bの上には、OB領域22を覆うように、遮光膜7が形成されている。この遮光膜7によって、フォトダイオードに光が入らない領域(図示しないオプティカルブラック領域)を作り、そのフォトダイオードの出力によって画像での黒レベルを決定することができる。

上述したように、第1の膜31は3層の積層構造であり、第2の膜32は2層の積層構造である。このように、固体撮像素子1は、第1の膜31が有する層の数が第2の膜32が有する層の数と異なる。本実施形態では、第1の膜31が有する層の数は、第2の膜32が有する層の数より多く、第1の膜31の膜厚が第2の膜32の膜厚より厚くなっている。ただし、第1の膜31の膜厚と第2の膜32の膜厚の差(段差)は数nm程度である。この程度の段差は、後述するように第1の膜31及び第2の膜32上に絶縁膜6や平坦化膜8を形成することで吸収することができるため、固体撮像素子1のカラーフィルタ9などを平らな膜上に形成することができる。

絶縁膜6bおよび遮光膜7を覆って、平坦化膜8bが形成されている。

本実施の形態の固体撮像素子1は、図1の上方から光が入射されると、フォトダイオードの電荷蓄積領域4において光を信号電荷に変換する光電変換が生じるため、入射光を受光検出することができる。そして、固体撮像素子1は、フォトダイオードが形成された半導体基板2から見て、下層にある配線層12の側(表面側)とは反対側(裏面側)の上層から光を入射させる、いわゆる裏面照射型構造となっている。

特に、固体撮像素子1では、有効領域21上に第1の膜31を形成し、OB領域22上に第2の膜32を形成しているため、有効領域21における暗電流の低減と、OB領域22における暗電流の低減を個別に行うことができる。これにより、図7に示すように、有効領域21とOB領域22における暗電流量差を低減することができ、いわゆるOB段差の発生を抑制することができる。

本実施の形態の固体撮像素子1においては、特に、有効領域21における第1の膜31が、第1層31aと、その上の第2層31bと、その上の第3層31cとの3層の積層構造となっている。また、OB領域22における第2の膜32が、第1層32bと、その上の第2層32cとの2層の積層構造となっている。

第1の膜31では、第1層31aおよび第2層31bはALD法またはMOCVD法により形成し、第3層31cはPVD法により形成する。また、第2の膜32では、第1層32bはALD法またはMOCVD法により形成し、第2層32cはPVD法により形成する。

これら第1の膜31を構成する第1層31a、第2層31bおよび第3層31cの材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか一つの酸化物を使用することが可能である。また、上述した、窒化物や酸窒化物、希土類元素の酸化物等も、使用することが可能である。

また、第2の膜32を構成する第1層32bおよび第2層32cの材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物を使用することが可能である。また、上述した、窒化物や酸窒化物、希土類元素の酸化物等も、使用することが可能である。

半導体基板2の上層に、第1の膜31および第2の膜32を設けたことにより、界面付近に正電荷(ホール)が蓄積されるようにすることができる。なお、特に、第1の膜31として、屈折率の比較的高い、酸化ハフニウム膜、酸化タンタル膜および酸化チタン等の酸化膜を形成した場合には、反射防止効果を得ることも可能になる。

図2に上述した負の固定電荷を有する膜31,32の膜厚に対する暗電流量の関係を示す。図2(a)は、ALD層の厚さと暗電流量の関係を示す図であり、図2(b)、(c)は、PVD層の厚さと暗電流量の関係を示す図である。図2(b)、(c)に示すように暗電流量は、PVD層の膜厚には大きく依存せず、図2(a)に示すように、暗電流量は、ALD層の厚さに依存する。

図2(a)に示すように、有効領域における暗電流量は、OB領域における暗電流量よりも大きい。また、第1の膜31および第2の膜32ともにALD層の厚さを薄くすることで、暗電流量は減少する。これまでの固体撮像素子は、有効領域及びOB領域のALD層の厚さが等しくなるように半導体基板2上に膜が形成されていた。従って、有効領域とOB領域の暗電流量の差(OB段差)は一定以上発生し、膜厚が大きくなるほどその差が大きくなっていた。

一方、本実施形態の固体撮像素子1は、暗電流量が大きい有効領域のALD層の厚さを、OB領域のALD層より厚くしている。そのため、有効領域における暗電流量と、OB領域における暗電流量との暗電流量差が減少する。

一方、本実施形態の固体撮像素子1は、暗電流量が大きい有効領域のALD層の厚さを、OB領域のALD層より厚くしている。そのため、有効領域における暗電流量と、OB領域における暗電流量との暗電流量差が減少する。

〔2.固体撮像素子の製造方法〕

次に、本実施の形態の固体撮像素子1の製造方法について説明する。図3は固体撮像素子1の製造方法を示す図である。なお、以下の説明は、有効領域21の半導体基板2内に電荷蓄積領域4が形成されており、MOSトランジスタTrのゲート電極11および配線層12が形成されている状態から始めることとする。

次に、本実施の形態の固体撮像素子1の製造方法について説明する。図3は固体撮像素子1の製造方法を示す図である。なお、以下の説明は、有効領域21の半導体基板2内に電荷蓄積領域4が形成されており、MOSトランジスタTrのゲート電極11および配線層12が形成されている状態から始めることとする。

まず、図3(a)に示すように、ALD法またはMOCVD法により、半導体基板2の有効領域21およびOB領域22上に、負の固定電荷を有する膜33として酸化ハフニウム膜を形成する。なお、負の固定電荷を有する膜33aの材料としては、上述した酸化ハフニウム以外にも、例えば、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物を用いることができる。

ALD法で形成する場合の形成条件は、例えば、形成基板温度200〜500℃、プリカーサ流量が10〜500sccm、照射時間1〜15秒、O3流量10〜500sccm、とする。また、負の固定電荷を有する膜33aの膜厚は、好ましくは1nm以上である。

次に、図3(b)に示すように、有効領域21における負の固定電荷を有する膜33a上にレジスト40を形成した後、ウェットエッチングによりレジスト40および露出している負の固定電荷を有する膜33aを除去する。これにより、図3(c)に示すように、半導体基板2の有効領域21上に、第1の膜31を構成する第1層31aを形成する。

次に、図3(d)に示すように、ALD法またはMOCVD法により、第1層31aおよびOB領域22上に、負の固定電荷を有する膜34として酸化ハフニウム膜を形成する。これにより、第1層31a上に第2層31bを形成し、OB領域22上に第2の膜32の第1層32bを形成する。なお、負の固定電荷を有する膜34の材料としては、上述した酸化ハフニウム以外にも、例えば、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物を用いることができる。

なお、ALD法で形成する場合の形成条件は、例えば、形成基板温度200〜500℃、プリカーサ流量が10〜500sccm、照射時間1〜15秒、O3流量10〜500sccm、とする。

次に、図3(e)に示すように、PVD法により、第1の膜31の第2層31bおよび第2の膜32の第1層32b上に、負の固定電荷を有する膜35として酸化タンタル膜を形成する。これにより、第2層31b上に第3層31cを形成し、第1層32b上に第2層32cを形成する。なお、負の固定電荷を有する膜35の材料としては、上述した酸化タンタル以外にも、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコンおよび酸化チタンのうちいずれか1つの酸化物を用いることができる。

なお、PVD法で形成する際の形成条件は、例えば、圧力0.01〜50Pa、DCパワー500〜2000W、Ar流量5〜50sccm、O2流量5〜50sccmとする。

上述した図3(a)〜図3(e)に示す工程により、本実施形態の固体撮像素子1の特徴的な構成である第1の膜31および第2の膜32を形成する。このように、第1の膜31の第2層31bと第2の膜32の第1層32bは、膜34を形成することで一体として形成される。また第1の膜31の第3層31cと第2の膜32の第2層32cは、膜35を形成することで一体として形成される。

次に、図示を省略するが、PVD法により、第1の膜31および第2の膜32上に酸化シリコンからなる絶縁膜6を形成する。具体的には、第1の膜31の第3層31c上に絶縁膜6aを形成し、第2の膜32の第2層32c上に絶縁膜6bを形成する。

なお、OB領域22において、絶縁膜6bを形成することにより、後の遮光膜7のエッチングの際に、第2の膜32の第2層32cの表面を直接エッチングに晒すことを防ぐことが可能になる。また、第2の膜32の第2層32cと遮光膜7を直接接触させることに起因した、第2の膜32の第2層32cと遮光膜7との反応を、抑制することが可能になる。

次に、図示を省略するが、絶縁膜6b上に遮光膜7を形成する。具体的には、PVD法により、絶縁膜6(6a,6b)上に遮光膜7となる金属膜を形成する。続いて、絶縁膜6a上の金属膜上にレジストを形成した後、エッチングによりレジストおよび露出している金属膜を除去する。これにより、絶縁膜6b上に遮光膜7を形成する。

次に、図示を省略するが、塗布法により、絶縁膜6aおよび遮光膜7を覆うように平坦化膜8としての酸化シリコン膜を形成する。この平坦化膜8を充分な厚さに形成することにより、遮光膜7による段差をなくして、表面を平坦化することができる。

最後に、図示を省略するが、有効領域21における平坦化膜8上、すなわち、各画素のフォトダイオードの上方に、カラーフィルタ9およびオンチップレンズ10を順次形成する。なお、カラーフィルタ9とオンチップレンズ10との間に、レンズ加工の際のカラーフィルタ9への加工ダメージを防止するために、光透過性の絶縁膜(図示せず)を形成してもよい。

上述した工程により、図1に示した固体撮像素子1が製造される。このように、本実施形態の固体撮像素子の製造方法では、有効領域21上に第1の膜31を形成することで有効領域21における電荷蓄積領域4の表面に正電荷蓄積領域5aが形成される。この正電荷蓄積領域5aにより、有効領域21における電荷蓄積領域4の表面における暗電流の発生が抑制される。

また、OB領域22上に第2の膜32を形成することでOB領域22における電荷蓄積領域4の表面に正電荷蓄積領域5bが形成される。この正電荷蓄積領域5bにより、OB領域22における電荷蓄積領域4の表面における暗電流の発生が抑制される。

しかも、固体撮像素子1では、第1の膜31および第2の膜32を個別に形成し、互いに異なる膜構成および膜厚としているため、有効領域21とOB領域22において異なる暗電流量の差を小さくすることができる。これにより、いわゆるOB段差を改善することができる。

さらに、第1の膜31および第2の膜32を個別に形成することで、有効領域における第1の膜を反射防止膜としての最適な膜構造および膜厚とすることができる。また、OB領域においては光の入射を考慮する必要がないため、第2の膜32を暗電流改善に特化した膜構成とすることができる。

第1の膜31は、第1層31a、第2層31bおよび第3層31cの3つの膜を合わせて充分な負バイアス効果が得られる。また、第2の膜32は、第1層32bおよび第2層32cの2つの膜を合わせて充分な負バイアス効果が得られる。これらの膜の負の固定電荷によって、界面付近に正電荷蓄積領域5aを形成して、正電荷(ホール)が蓄積されるようにして、界面準位に起因する暗電流の発生を抑制することができる。

従って、本実施の形態により、充分な大きさの負バイアス効果により、界面準位に起因する暗電流の発生を抑制することができ、暗電流を生じることなく安定して動作する、高い信頼性を有する固体撮像素子1を実現することができる。

上述の実施の形態では、CMOS固体撮像素子に本発明を適用した場合であったが、本発明は、その他の構成の固体撮像素子にも適用することができる。例えば、CCD固体撮像素子においても、本発明を適用して、受光部上に、プラズマを用いて形成した酸化シリコン膜および負の固定電荷を有する膜を形成することにより、界面準位に起因する暗電流の発生を抑制することができる。

また、上述の実施の形態では、裏面照射型構造の固体撮像素子に本発明を適用した場合であった。本発明は、フォトダイオードが形成された半導体基板における光が入射する側に配線層や転送電極を形成した、いわゆる表面照射型構造の固体撮像素子にも適用することが可能である。

〔3.撮像装置の構成等〕

以下、このように構成された固体撮像素子1を備えた撮像装置について説明する。図4は上記固体撮像素子1を備えた撮像装置の構成を示す図である。なお、この撮像装置90としては、例えば、ビデオカメラ、デジタルスチルカメラ、携帯電話のカメラ等が挙げられる。

以下、このように構成された固体撮像素子1を備えた撮像装置について説明する。図4は上記固体撮像素子1を備えた撮像装置の構成を示す図である。なお、この撮像装置90としては、例えば、ビデオカメラ、デジタルスチルカメラ、携帯電話のカメラ等が挙げられる。

図4に示すように、撮像装置90は、光学ブロック91、固体撮像素子1、A/D(アナログ/デジタル)変換回路92、信号処理回路93,制御部であるシステムコントローラ94、入力部95を具備する。また、この撮像装置90には、光学ブロック91内の機構を駆動するためのドライバ96、固体撮像素子1を駆動させる駆動パルスを生成する駆動部としてのタイミングジェネレータ(以下、「TG」という)97などが設けられる。

光学ブロック91は、被写体からの光を固体撮像素子1へ集光するためのレンズ、レンズを移動させてフォーカス合わせやズーミングを行うための駆動機構、メカシャッタ、絞りなどを具備している。ドライバ96は、システムコントローラ94からの制御信号に応じて、光学ブロック91内の機構の駆動を制御する。

固体撮像素子1は、TG97により生成された駆動パルスに基づいて駆動され、被写体からの入射光を電気信号に変換する。TG97は、システムコントローラ94の制御の下で駆動パルスを生成する。

A/D変換回路92は、固体撮像素子1から出力された画像信号をA/D変換してデジタル画像信号を出力する。

信号処理回路93は、A/D変換回路92からのデジタル画像信号に対するAF(Auto Focus)、AE(Auto Exposure)、欠陥画素の補間処理などの各種カメラ信号処理を実行する。

システムコントローラ94は、例えば、CPU(Central Processing Unit)、ROM(Read Only Memory)、RAM(Random Access Memory)などから構成される。CPUはROMなどに記憶されたプログラムを実行することにより、この撮像装置の各部を統括的に制御し、また、その制御のための各種演算を実行する。入力部95は、ユーザの操作入力を受け付ける操作キー、ダイアル、レバーなどを含み、操作入力に応じた制御信号をシステムコントローラ94に出力する。

この撮像装置90では、固体撮像素子1で受光され、光電変換された信号電荷に応じた画像信号が、順次A/D変換回路92に供給されてデジタル信号に変換され、信号処理回路93により画質補正処理され、最終的に輝度信号と色差信号とに変換して出力される。信号処理回路93から出力された画像データは、図示しないグラフィックインタフェース回路に供給されて表示用の画像信号に変換され、これにより図示しないモニタにカメラスルー画像が表示される。

〔4.その他の固体撮像素子の構成及び製造方法〕

以下、固体撮像素子の変形例について説明する。

以下、固体撮像素子の変形例について説明する。

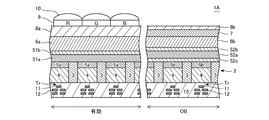

(変形例1)

まず、第1変形例に係る固体撮像素子1Aについて図5を参照して説明する。図5は、変形例1係る固体撮像素子1Aの断面構造を示す図である。本変形例に係る固体撮像素子1Aは、上述した固体撮像素子1に対して負の固定電荷を有する第1の膜および第2の膜の膜構成を異ならせたものである。なお、以下の説明では、図1に示した固体撮像素子1と同一の構成要素については、同一の符号を付して説明する。

まず、第1変形例に係る固体撮像素子1Aについて図5を参照して説明する。図5は、変形例1係る固体撮像素子1Aの断面構造を示す図である。本変形例に係る固体撮像素子1Aは、上述した固体撮像素子1に対して負の固定電荷を有する第1の膜および第2の膜の膜構成を異ならせたものである。なお、以下の説明では、図1に示した固体撮像素子1と同一の構成要素については、同一の符号を付して説明する。

図5に示すように、固体撮像素子1Aは、半導体基板2の有効領域21上に第1の膜51が形成され、OB領域22上に第2の膜52が形成されている。

第1の膜51は、半導体基板2上に形成された第1層51aと、この第1層51a上に形成された第2層51bとが積層された構成を有する。

第1層51aは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、PVD法により形成される。

また、第2層51bは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

また、第2の膜52は、半導体基板2上に形成された第1層52cと、第1層51c上に形成された第2層52aと、第2層51a上に形成された第3層52bとが積層された構成を有する。

第1層52cは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

また、第2層52aは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、PVD法により形成される。

また、第3層52bは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

上述したように、第1の膜51は2層の積層構造であり、第2の膜52は3層の積層構造である。このように、固体撮像素子1Aは、第1の膜51が有する層の数が第2の膜52が有する層の数と異なる。本実施形態では、第1の膜51が有する層の数は、第2の膜52が有する層の数より少なくなっている。

上述したように、第1の膜51は2層の積層構造であり、第2の膜52は3層の積層構造である。このように、固体撮像素子1Aは、第1の膜51が有する層の数が第2の膜52が有する層の数と異なる。本実施形態では、第1の膜51が有する層の数は、第2の膜52が有する層の数より少なくなっている。

次に、本実施の形態の固体撮像素子1Aの製造方法について説明する。図6は固体撮像素子1Aの製造方法を示す図である。ここでは、本変形例の固体撮像素子1Aの製造方法の特徴的な構成である、第1の膜51および第2の膜52を形成する工程について説明し、その他の構成については同一符号を付して説明を省略する。

まず、図6(a)に示すように、ALD法またはMOCVD法により、半導体基板2の有効領域21およびOB領域22上に、負の固定電荷を有する膜53aを形成する。この負の固定電荷を有する膜53aの材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

次に、図6(b)に示すように、OB領域22上に形成された負の固定電荷を有する膜53a上にレジスト40を形成した後、ウェットエッチングする。これにより、図6(c)に示すように、有効領域21上に形成された負の固定電荷を有する膜53を選択的に除去し、OB領域22上に第2の膜52の第1層52cを形成する。

次に、図6(d)に示すように、PVD法により、有効領域21における半導体基板2および第2の膜52の第1層52c上に、負の固定電荷を有する膜54を形成する。これにより、有効領域21における半導体基板2上に第1の膜51の第1層51aを形成し、第2の膜52の第1層52c上に第2層52aを形成する。負の固定電荷を有する膜54の材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

なお、PVD法で形成する際の形成条件は、例えば、圧力0.01〜50Pa、DCパワー500〜2000W、Ar流量5〜50sccm、O2流量5〜50sccmとする。

次に、図6(e)に示すように、ALD法またはMOCVD法により、負の固定電荷を有する膜54上に、負の固定電荷を有する膜55を形成する。これにより、第1の膜51の第1層51a上に第2層51bを形成し、第2の膜52の第2層52a上に第3層52bを形成する。負の固定電荷を有する膜55の材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

ALD法で形成する場合の形成条件は、例えば、形成基板温度200〜500℃、プリカーサ流量が10〜500sccm、照射時間1〜15秒、O3流量10〜500sccm、とする。第1の膜の膜厚は、好ましくは1nm以上である。なお、第1の膜をALD法により形成した場合には、同時に、半導体基板2の表面に、酸化シリコン膜(厚さ1nm程度)が形成されることがある。

第1層51a上に第2層51bを形成することによって、2層51a,51bが積層された第1の膜51が構成される。この第1の膜51によって、有効領域21における電荷蓄積領域4の表面に正電荷蓄積領域5aが形成される。

また、第1層52c上に第2層52aを形成し、この第2層52b上に第3層52bを形成することによって、3層52c,52a,52bが積層された第2の膜52が構成される。この第2の膜52によって、OB領域22における電荷蓄積領域4の表面に正電荷蓄積領域5bが形成される。

第1の膜51の第1層31aと第2の膜52の第2層52aは、膜54を形成することで一体として形成される。また第1の膜51の第2層51bと第2の膜52の第3層52bは、膜55を形成することで一体として形成される。

次に、上述した工程と同様の工程により、絶縁膜6、遮光膜7、平坦化膜8、カラーフィルタ9およびオンチップレンズ10を形成し、図5に示した固体撮像素子1Aを製造することができる。

図7に第2の膜52を第1層52cと第2層52bで形成した場合、及び第2の膜52を本実施形態のように第1乃至第3層52c〜52aで形成した場合の、第2の膜52に対する暗電流量を示す。図7に示すように、第2の膜52を第1乃至第3層52c〜52aの3層で形成した方が、OB領域における暗電流量が少ないことがわかる。

一方、有効領域では、半導体基板2とPVD法により成膜した第1層51aとが接しているため、第1の膜51をALD法などで成膜した層の上にPVD法により成膜した層を積層する場合に比べ暗電流量が増加する。これは、ALD法などで成膜した層に比べPVD法で成膜した層は緻密さに劣るため、負の固定電荷を阻害する物質、例えば水素などが侵入しやすいからである。有効領域では、PVD法で成膜した層が半導体基板2の界面に近いところに形成されるため、半導体基板2上にALD法で成膜した層を積層する場合に比べて暗電流量が増加する。

有効領域に比べOB領域では暗電流が多く発生する。そこで本変形例の固体撮像素子1Aでは、第1の膜51を形成することで有効領域に発生する暗電流量を増やし、第2の膜52を形成することでOB領域に発生する暗電流量を減らしている。これにより、有効領域とOB領域とで発生する暗電流量の差(OB段差)を小さくすることができる。

また、PVD法で成膜された第1の膜51の第1層51a及び第2の膜52の第2層52b上に、第1の膜51の第2層52b及び第2の膜52の第3層52aをALD法などで成膜することで、外部から水素などの負の固定電荷を阻害する物質の侵入を抑制することができる。これは、上述したようにALD法などで成膜された層は、PVD法で成膜された層より緻密であり、外部から物質が侵入しにくいためである。

なお、本変形例の第1の膜51の第1層51aと第2層51bとを入れ替えてもよい。この場合、半導体基板2上にALD法またはMOCVD法により第2層51bを成膜し、第2層51b上にPVD法により第1層51aを成膜する。第2層51bは、第2の膜52の第1層52cと一体で形成してもよい。

(変形例2)

次に、第2変形例の固体撮像素子1Bについて説明する。図8は、第3の実施形態に係る固体撮像素子の構成を示す図である。本実施形態に係る固体撮像素子1Bは、上述した固体撮像素子1Bの負の固定電荷を有する膜の膜構成を変えたものであり、その他の構成については同一符号を付して説明を省略する。

次に、第2変形例の固体撮像素子1Bについて説明する。図8は、第3の実施形態に係る固体撮像素子の構成を示す図である。本実施形態に係る固体撮像素子1Bは、上述した固体撮像素子1Bの負の固定電荷を有する膜の膜構成を変えたものであり、その他の構成については同一符号を付して説明を省略する。

図8に示すように、固体撮像素子1Bは、半導体基板2の有効領域21上に第1の膜61を備え、OB領域22上に第2の膜62を備えている。

第1の膜61は、半導体基板2上に形成された第1層61aと、この第1層61a上に形成された第2層61bと、この第2層61b上に形成された第3層61cとが積層された構成を有する。

第1層61aは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

また、第2層61bは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、PVD法により形成される。

また、第3層61cは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

上第2の膜62は、半導体基板2上に形成された第1層62cを有する。この第1層62cは、例えば、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなり、ALD法またはMOCVD法により形成される。

次に、図9を参照して上記固体撮像素子1Bの製造方法について説明する。ここでは、本変形例の固体撮像素子1Bの特徴的な構成である第1の膜61および第2の膜62を形成する工程について説明し、その他の工程については説明を省略する。

まず、図9(a)に示すように、ALD法またはMOCVD法により、半導体基板2の有効領域21およびOB領域22上に、負の固定電荷を有する膜63を形成する。この負の固定電荷を有する膜63の材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

ALD法で形成する場合の形成条件は、例えば、形成基板温度200〜500℃、プリカーサ流量が10〜500sccm、照射時間1〜15秒、O3流量10〜500sccm、とする。第1の膜の膜厚は、好ましくは1nm以上である。なお、第1の膜をALD法により形成した場合には、同時に、半導体基板2の表面に、酸化シリコン膜(厚さ1nm程度)が形成されることがある。

次に、図9(b)に示すように、PVD法により、負の固定電荷を有する膜63上に負の固定電荷を有する膜64を形成する。負の固定電荷を有する膜64の材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

なお、PVD法で形成する際の形成条件は、例えば、圧力0.01〜50Pa、DCパワー500〜2000W、Ar流量5〜50sccm、O2流量5〜50sccmとする。

次に、図9(c)に示すように、有効領域21上に形成された負の固定電荷を有する膜64上にレジスト40を形成した後、ウェットエッチングすることにより、OB領域22上に形成された2層の負の固定電荷を有する膜63,64を選択的に除去し、有効領域21上に第1の膜61の第1層61aおよび第2層61bを形成する。

次に、図9(c)に示すように、ALD法またはMOCVD法により、第1の膜61の第2層61b上、およびOB領域22における半導体基板2上に、負の固定電荷を有する膜65を形成する。これにより、第1の膜61の第3層61cを形成するとともに、半導体基板2のOB領域22上に、第2の膜62の第1層62cを形成する。第1の膜61の第3層61cおよび第2の膜62の第1層62cの材料としては、例えば、酸化ハフニウム、酸化アルミニウム、酸化ジルコン、酸化タンタルおよび酸化チタンのうちいずれか1つの酸化物が挙げられる。

なお、ALD法で形成する場合の形成条件は、例えば、形成基板温度200〜500℃、プリカーサ流量が10〜500sccm、照射時間1〜15秒、O3流量10〜500sccmとする。

第1層61a上に第2層61bを形成し、第2層61b上に第3層61cを形成することによって、3層61a,61b,61cが積層された第1の膜61が構成される。この第1の膜61によって、有効領域21における電荷蓄積領域4の表面に正電荷蓄積領域5aが形成される。

また、第1層62cにより構成された第2の膜62によって、OB領域22における電荷蓄積領域4の表面に正電荷蓄積領域5bが形成される。

第1の膜61の第3層61cと第2の膜62の第1層62cは、膜55を形成することで一体として形成される。

第1の膜61の第3層61cと第2の膜62の第1層62cは、膜55を形成することで一体として形成される。

次に、上述した工程と同様の工程により、絶縁膜6、遮光膜7、平坦化膜8、カラーフィルタ9およびオンチップレンズ10を形成し、図8に示す固体撮像素子1Bが製造される。

図10は、固体撮像素子1Bの第2の膜62を、ALD法などで成膜した層とPVD法で成膜した層との2層の積層構造とした場合と、ALD法などで成膜した第1層62cの1層とした場合の暗電流量を示す図である。図10に示すように、第2の膜62を2層とするより、本変形例のように1層(単層)とした方がOB領域における暗電流量が低減する。

PVD法で成膜した層は、ALD法で成膜した層に比べて緻密でないため負の固定電荷を阻害する水素などを含みやすい。本変形例のように、第2の膜62をPVD法で成膜した層を含まないALD法などで成膜した層の構造としたことで、水素などの負の固定電荷を阻害する物質が侵入しにくくなる。これにより、固体撮像素子1Bの第2の膜62中の負の固定電荷密度を高くすることができ、負バイアス効果が増加して暗電流が改善すると考えられる。

このように、有効領域より暗電流が多く発生するOB領域に形成する第2の膜62の暗電流量を減らすことで、有効領域の暗電流量とOB領域の暗電流量との差(OB段差)を小さくすることができる。

上述の構成を有する固体撮像素子1Aによれば、OB段差の温度特性が改善される。すなわち、半導体基板の温度が上昇した場合でも、OB段差の悪化が抑制される。

最後に、上述した各実施形態の説明は本発明の一例であり、本発明は上述の実施の形態に限定されることはない。このため、上述した各実施の形態以外であっても、本発明に係る技術的思想を逸脱しない範囲であれば、設計等に応じて種々の変更が可能であることは勿論である。

1 固体撮像素子

2 半導体基板

3 素子分離領域

4 電荷蓄積領域

5,5a,5b 正電荷蓄積領域

6,6a,6b,13 絶縁膜

7 遮光膜

8,8a,8b 平坦化膜

9 カラーフィルタ

10 オンチップレンズ

11 ゲート電極

12 配線層

21 有効領域

22 OB領域

31 第1の膜

31a 第1層

31b 第2層

31c 第3層

32 第2の膜

32b 第1層

32c 第2層

33,34,35 負の固定電荷を有する膜

2 半導体基板

3 素子分離領域

4 電荷蓄積領域

5,5a,5b 正電荷蓄積領域

6,6a,6b,13 絶縁膜

7 遮光膜

8,8a,8b 平坦化膜

9 カラーフィルタ

10 オンチップレンズ

11 ゲート電極

12 配線層

21 有効領域

22 OB領域

31 第1の膜

31a 第1層

31b 第2層

31c 第3層

32 第2の膜

32b 第1層

32c 第2層

33,34,35 負の固定電荷を有する膜

Claims (7)

- 光電変換が行われるフォトダイオードが形成された有効領域、および遮光膜により遮光された光学的黒領域が形成された半導体基板と、

前記有効領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第1の膜と、

前記遮光領域上であって、負の固定電荷を有する層が少なくとも1層以上積層された第2の膜と、を備え、

前記第1の膜が有する層の数が前記第2の膜が有する層の数と異なる

固体撮像素子。 - 前記第1の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、

前記第1層上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第2層と、

前記第2層上に、物理的気相成長を用いて形成された第3層と、を有し、

前記第2の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、

前記第1層上に、物理的気相成長を用いて形成された第2層と、を有する

請求項1に記載の固体撮像素子。 - 前記第1の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、

前記第1層上に、物理的気相成長を用いて形成された第2層と、有し、

前記第2の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、

前記第1層上に、物理的気相成長を用いて形成された第2層と、

前記第2層上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第3層と、を有する

請求項1に記載の固体撮像素子。 - 前記第1の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層と、

前記第1層上に、物理的気相成長を用いて形成された第2層と、

前記第2層上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第3層と、を有し、

前記第2の膜は、

前記半導体基板上に、原子層蒸着法または有機金属化学的気相成長法を用いて形成された第1層を有する

請求項1に記載の固体撮像素子。 - 前記第1の膜および前記第2の膜を構成する層は、酸化ハフニウム膜、酸化アルミニウム膜、酸化ジルコニウム膜、酸化タンタル膜および酸化チタン膜のうちいずれかの1つの膜からなる

請求項1〜4のいずれか1項に記載の固体撮像素子。 - 半導体基板に、光電変換が行われるフォトダイオードが形成された有効領域および遮光膜により遮光された光学的黒領域を形成する工程と、

前記有効領域上に負の固定電荷を有する層が少なくとも1層以上積層された第1の膜を形成する工程と、

前記遮光領域上に、負の固定電荷を有する層が少なくとも1層以上積層され、前記第1の膜が有する層の数とは異なる数の層を有する第2の膜を形成する工程と、を有する

固体撮像素子の製造方法。 - 請求項1〜5のいずれか1項に記載の固体撮像素子と、

前記固体撮像素子に被写体像を結像する光学系と、

前記固体撮像素子を駆動させる駆動パルスを生成する駆動部と、

前記固体撮像素子の出力画像信号を処理する信号処理回路と、を備える

撮像装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011053237A JP2012191005A (ja) | 2011-03-10 | 2011-03-10 | 固体撮像素子、固体撮像素子の製造方法および撮像装置 |

| TW101104780A TW201242000A (en) | 2011-03-10 | 2012-02-14 | Solid-state imaging device, method of manufacturing solid-state imaging device, and imaging apparatus |

| KR1020120016885A KR20120103448A (ko) | 2011-03-10 | 2012-02-20 | 고체 촬상 소자, 고체 촬상 소자의 제조 방법 및 촬상 장치 |

| US13/402,257 US8729450B2 (en) | 2011-03-10 | 2012-02-22 | Solid-state imaging device, method of manufacturing solid-state imaging device, and imaging apparatus |

| CN201210051688.7A CN102683361B (zh) | 2011-03-10 | 2012-03-01 | 固体摄像器件、固体摄像器件的制造方法和摄像装置 |

| US14/246,654 US9653502B2 (en) | 2011-03-10 | 2014-04-07 | Solid-state imaging device, method of manufacturing solid-state imaging device, and imaging apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011053237A JP2012191005A (ja) | 2011-03-10 | 2011-03-10 | 固体撮像素子、固体撮像素子の製造方法および撮像装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012191005A true JP2012191005A (ja) | 2012-10-04 |

| JP2012191005A5 JP2012191005A5 (ja) | 2014-04-10 |

Family

ID=46794659

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011053237A Abandoned JP2012191005A (ja) | 2011-03-10 | 2011-03-10 | 固体撮像素子、固体撮像素子の製造方法および撮像装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8729450B2 (ja) |

| JP (1) | JP2012191005A (ja) |

| KR (1) | KR20120103448A (ja) |

| CN (1) | CN102683361B (ja) |

| TW (1) | TW201242000A (ja) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015070070A (ja) * | 2013-09-27 | 2015-04-13 | ソニー株式会社 | 撮像素子およびその製造方法ならびに電子機器 |

| US10224359B2 (en) | 2012-03-22 | 2019-03-05 | Sionyx, Llc | Pixel isolation elements, devices and associated methods |

| US10229951B2 (en) | 2010-04-21 | 2019-03-12 | Sionyx, Llc | Photosensitive imaging devices and associated methods |

| US10269861B2 (en) | 2011-06-09 | 2019-04-23 | Sionyx, Llc | Process module for increasing the response of backside illuminated photosensitive imagers and associated methods |

| US10347682B2 (en) | 2013-06-29 | 2019-07-09 | Sionyx, Llc | Shallow trench textured regions and associated methods |

| US10374109B2 (en) | 2001-05-25 | 2019-08-06 | President And Fellows Of Harvard College | Silicon-based visible and near-infrared optoelectric devices |

| US10505054B2 (en) | 2010-06-18 | 2019-12-10 | Sionyx, Llc | High speed photosensitive devices and associated methods |

| US10741399B2 (en) | 2004-09-24 | 2020-08-11 | President And Fellows Of Harvard College | Femtosecond laser-induced formation of submicrometer spikes on a semiconductor substrate |

| JP2020145397A (ja) * | 2018-10-17 | 2020-09-10 | キヤノン株式会社 | 光電変換装置、および、それを含む機器 |

| JP2021086979A (ja) * | 2019-11-29 | 2021-06-03 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法 |

| US11121160B2 (en) | 2018-10-17 | 2021-09-14 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment comprising a light shielding part in a light receiving region and a light shielding film in a light shielded region |

| US11244978B2 (en) | 2018-10-17 | 2022-02-08 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment including the same |

| WO2023090053A1 (ja) * | 2021-11-16 | 2023-05-25 | ソニーセミコンダクタソリューションズ株式会社 | 光検出装置及び電子機器 |

| US11990490B2 (en) | 2020-04-07 | 2024-05-21 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5418049B2 (ja) * | 2009-08-03 | 2014-02-19 | ソニー株式会社 | 固体撮像素子及びその製造方法、撮像装置 |

| US20130016203A1 (en) | 2011-07-13 | 2013-01-17 | Saylor Stephen D | Biometric imaging devices and associated methods |

| KR102350138B1 (ko) * | 2013-03-29 | 2022-01-14 | 소니그룹주식회사 | 촬상 소자 및 촬상 장치 |

| JP2015012303A (ja) * | 2013-06-26 | 2015-01-19 | ソニー株式会社 | 固体撮像装置および電子機器 |

| JP6257525B2 (ja) * | 2014-01-27 | 2018-01-10 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US9888198B2 (en) * | 2014-06-03 | 2018-02-06 | Semiconductor Components Industries, Llc | Imaging systems having image sensor pixel arrays with sub-pixel resolution capabilities |

| KR102201594B1 (ko) * | 2014-09-18 | 2021-01-11 | 에스케이하이닉스 주식회사 | 반사방지층을 갖는 이미지 센서 및 그 제조 방법 |

| KR20160100569A (ko) | 2015-02-16 | 2016-08-24 | 삼성전자주식회사 | 이미지 센서 및 이미지 센서를 포함하는 촬상 장치 |

| CN107924929B (zh) * | 2015-09-17 | 2022-10-18 | 索尼半导体解决方案公司 | 固体摄像器件、电子设备以及固体摄像器件的制造方法 |

| KR102666073B1 (ko) | 2016-12-28 | 2024-05-17 | 삼성전자주식회사 | 이미지 센서 |

| KR102495573B1 (ko) | 2017-07-21 | 2023-02-03 | 삼성전자주식회사 | 이미지 센서 |

| KR102534249B1 (ko) | 2018-01-12 | 2023-05-18 | 삼성전자주식회사 | 이미지 센서 |

| WO2020220155A1 (zh) * | 2019-04-28 | 2020-11-05 | 深圳市大疆创新科技有限公司 | 图像传感器芯片、制造方法、图像传感器及拍摄装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4311419B2 (ja) * | 2006-08-02 | 2009-08-12 | ソニー株式会社 | 固体撮像装置 |

| TWI426602B (zh) * | 2007-05-07 | 2014-02-11 | Sony Corp | A solid-state image pickup apparatus, a manufacturing method thereof, and an image pickup apparatus |

| JP2009070912A (ja) * | 2007-09-11 | 2009-04-02 | Fujifilm Corp | 固体撮像素子及び撮像装置 |

| JP5151375B2 (ja) * | 2007-10-03 | 2013-02-27 | ソニー株式会社 | 固体撮像装置およびその製造方法および撮像装置 |

| US8003428B2 (en) * | 2008-03-27 | 2011-08-23 | International Business Machines Corporation | Method of forming an inverted lens in a semiconductor structure |

| JP5347999B2 (ja) | 2009-03-12 | 2013-11-20 | ソニー株式会社 | 固体撮像素子及びその製造方法、撮像装置 |

| JP5418049B2 (ja) * | 2009-08-03 | 2014-02-19 | ソニー株式会社 | 固体撮像素子及びその製造方法、撮像装置 |

-

2011

- 2011-03-10 JP JP2011053237A patent/JP2012191005A/ja not_active Abandoned

-

2012

- 2012-02-14 TW TW101104780A patent/TW201242000A/zh unknown

- 2012-02-20 KR KR1020120016885A patent/KR20120103448A/ko not_active Application Discontinuation

- 2012-02-22 US US13/402,257 patent/US8729450B2/en active Active

- 2012-03-01 CN CN201210051688.7A patent/CN102683361B/zh not_active Expired - Fee Related

-

2014

- 2014-04-07 US US14/246,654 patent/US9653502B2/en active Active

Cited By (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10374109B2 (en) | 2001-05-25 | 2019-08-06 | President And Fellows Of Harvard College | Silicon-based visible and near-infrared optoelectric devices |

| US10741399B2 (en) | 2004-09-24 | 2020-08-11 | President And Fellows Of Harvard College | Femtosecond laser-induced formation of submicrometer spikes on a semiconductor substrate |

| US10229951B2 (en) | 2010-04-21 | 2019-03-12 | Sionyx, Llc | Photosensitive imaging devices and associated methods |

| US10505054B2 (en) | 2010-06-18 | 2019-12-10 | Sionyx, Llc | High speed photosensitive devices and associated methods |

| US10269861B2 (en) | 2011-06-09 | 2019-04-23 | Sionyx, Llc | Process module for increasing the response of backside illuminated photosensitive imagers and associated methods |

| US10224359B2 (en) | 2012-03-22 | 2019-03-05 | Sionyx, Llc | Pixel isolation elements, devices and associated methods |

| US10347682B2 (en) | 2013-06-29 | 2019-07-09 | Sionyx, Llc | Shallow trench textured regions and associated methods |

| US11069737B2 (en) | 2013-06-29 | 2021-07-20 | Sionyx, Llc | Shallow trench textured regions and associated methods |

| US10950644B2 (en) | 2013-09-27 | 2021-03-16 | Sony Corporation | Image pickup element, method of manufacturing image pickup element, and electronic apparatus |

| KR102311825B1 (ko) | 2013-09-27 | 2021-10-13 | 소니그룹주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| US10461110B2 (en) | 2013-09-27 | 2019-10-29 | Sony Corporation | Image pickup element, method of manufacturing image pickup element, and electronic apparatus |

| US9893105B2 (en) | 2013-09-27 | 2018-02-13 | Sony Corporation | Image pickup element, method of manufacturing image pickup element, and electronic apparatus |

| KR20180004061A (ko) * | 2013-09-27 | 2018-01-10 | 소니 주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| KR102664494B1 (ko) | 2013-09-27 | 2024-05-10 | 소니그룹주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| KR20200123064A (ko) * | 2013-09-27 | 2020-10-28 | 소니 주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| KR102183352B1 (ko) * | 2013-09-27 | 2020-11-26 | 소니 주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| JP2015070070A (ja) * | 2013-09-27 | 2015-04-13 | ソニー株式会社 | 撮像素子およびその製造方法ならびに電子機器 |

| US11862652B2 (en) | 2013-09-27 | 2024-01-02 | Sony Group Corporation | Image pickup element, method of manufacturing image pickup element, and electronic apparatus |

| CN106206635A (zh) * | 2013-09-27 | 2016-12-07 | 索尼公司 | 摄像装置和电子设备 |

| KR20210112279A (ko) * | 2013-09-27 | 2021-09-14 | 소니그룹주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| KR102490635B1 (ko) | 2013-09-27 | 2023-01-20 | 소니그룹주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| CN106206635B (zh) * | 2013-09-27 | 2018-04-17 | 索尼公司 | 摄像装置和电子设备 |

| KR20230010801A (ko) * | 2013-09-27 | 2023-01-19 | 소니그룹주식회사 | 촬상 소자 및 그 제조 방법 및 전자 기기 |

| US11557623B2 (en) | 2013-09-27 | 2023-01-17 | Sony Corporation | Image pickup element, method of manufacturing image pickup element, and electronic apparatus |

| JP2022051782A (ja) * | 2018-10-17 | 2022-04-01 | キヤノン株式会社 | 光電変換装置、および、それを含む機器 |

| US11244978B2 (en) | 2018-10-17 | 2022-02-08 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment including the same |

| US11121160B2 (en) | 2018-10-17 | 2021-09-14 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment comprising a light shielding part in a light receiving region and a light shielding film in a light shielded region |

| US11682686B2 (en) | 2018-10-17 | 2023-06-20 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment including the same |

| JP2020145397A (ja) * | 2018-10-17 | 2020-09-10 | キヤノン株式会社 | 光電変換装置、および、それを含む機器 |

| JP2021086979A (ja) * | 2019-11-29 | 2021-06-03 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法 |

| JP7414492B2 (ja) | 2019-11-29 | 2024-01-16 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法 |

| US11978750B2 (en) | 2019-11-29 | 2024-05-07 | Canon Kabushiki Kaisha | Photoelectric conversion device and method of manufacturing photoelectric conversion device |

| US11990490B2 (en) | 2020-04-07 | 2024-05-21 | Canon Kabushiki Kaisha | Photoelectric conversion apparatus and equipment |

| JP7520558B2 (ja) | 2020-04-07 | 2024-07-23 | キヤノン株式会社 | 光電変換装置および機器 |

| WO2023090053A1 (ja) * | 2021-11-16 | 2023-05-25 | ソニーセミコンダクタソリューションズ株式会社 | 光検出装置及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102683361A (zh) | 2012-09-19 |

| TW201242000A (en) | 2012-10-16 |

| US20140218574A1 (en) | 2014-08-07 |

| CN102683361B (zh) | 2016-03-23 |

| US8729450B2 (en) | 2014-05-20 |

| US20120228473A1 (en) | 2012-09-13 |

| US9653502B2 (en) | 2017-05-16 |

| KR20120103448A (ko) | 2012-09-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9653502B2 (en) | Solid-state imaging device, method of manufacturing solid-state imaging device, and imaging apparatus | |

| KR102664494B1 (ko) | 촬상 소자 및 그 제조 방법 및 전자 기기 | |

| JP5347999B2 (ja) | 固体撮像素子及びその製造方法、撮像装置 | |

| JP5418049B2 (ja) | 固体撮像素子及びその製造方法、撮像装置 | |

| US8709958B2 (en) | Solid-state image pickup element, method of manufacturing the same, and image pickup apparatus including the same | |

| JP2011071247A (ja) | 固体撮像装置の製造方法 | |

| JP2006228949A (ja) | 固体撮像装置の製造方法、固体撮像装置およびカメラ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141225 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20150403 |