JP2012151613A - 固体撮像装置及び撮像装置 - Google Patents

固体撮像装置及び撮像装置 Download PDFInfo

- Publication number

- JP2012151613A JP2012151613A JP2011008116A JP2011008116A JP2012151613A JP 2012151613 A JP2012151613 A JP 2012151613A JP 2011008116 A JP2011008116 A JP 2011008116A JP 2011008116 A JP2011008116 A JP 2011008116A JP 2012151613 A JP2012151613 A JP 2012151613A

- Authority

- JP

- Japan

- Prior art keywords

- counter

- bit

- column

- flip

- imaging device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

【課題】回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減する。

【解決手段】本発明に係る固体撮像装置50は、複数の画素101が行列状に配置された画素アレイ100と、複数の画素101から出力されるアナログ信号を並列にデジタル信号に変換する複数のカラムA/D変換回路140と、クロック信号を生成するタイミング制御回路130とを備え、複数のカラムA/D変換回路140の各々は、前記アナログ信号と前記ランプ波との電位を比較し、比較した結果を示す比較結果信号を生成する比較器141と、前記クロック信号をカウントするとともに、比較結果信号が変化する時点での計数値を前記デジタル信号として保持するカラムカウンタ142とを有し、カラムカウンタ142は、直列に接続された複数のカウンタを含み、複数のカウンタの各々は、隣接する計数値を示す計数コードのハミング距離が1である。

【選択図】図1

【解決手段】本発明に係る固体撮像装置50は、複数の画素101が行列状に配置された画素アレイ100と、複数の画素101から出力されるアナログ信号を並列にデジタル信号に変換する複数のカラムA/D変換回路140と、クロック信号を生成するタイミング制御回路130とを備え、複数のカラムA/D変換回路140の各々は、前記アナログ信号と前記ランプ波との電位を比較し、比較した結果を示す比較結果信号を生成する比較器141と、前記クロック信号をカウントするとともに、比較結果信号が変化する時点での計数値を前記デジタル信号として保持するカラムカウンタ142とを有し、カラムカウンタ142は、直列に接続された複数のカウンタを含み、複数のカウンタの各々は、隣接する計数値を示す計数コードのハミング距離が1である。

【選択図】図1

Description

本発明は、固体撮像装置及び撮像装置に関し、特に、複数の画素から出力されるアナログ信号を並列にデジタル信号に変換する複数のカラムA/D変換回路を備える固体撮像装置に関する。

近年、イメージセンサとしてCCD(Charge Coupled Device:電荷結合素子)型センサ(以後「CCDセンサ」と称する)、及び、ロジックLSIに使われている標準プロセスを活用したMOS(Metal−Oxide Semiconductor)型センサ(以後「MOSセンサ」と称する)を用いた固体撮像装置が広く使われている。これらの固体撮像装置は、入射光をその光量に応じた信号電荷に変換する受光部を備えた複数の画素を備える。この複数の画素は、1次元又は2次元のアレイ状に配列されている。また、CCDセンサでは、信号電荷を信号電圧に変換する電荷検出部が画素外に形成されている。一方、MOSセンサでは、当該電荷検出部は画素内に形成されている。

これらの画素から出力されるアナログ信号は必要に応じてA/D変換回路にてデジタル信号に変換する必要がある。これらの固体撮像装置が搭載するA/D変換回路に用いられるA/D変換方式として、多数の方式が提案されている。当該多数の方式は、例えば、パイプライン型A/D変換方式、1ラインの画素データを同時並列的にA/D変換するカラムA/D変換方式、及び、全ての画素データを同時並列的にA/D変換する方式などである。

カラムA/D変換方式の一例として、各カラムA/D変換器がカウンタ回路を有する方式が特許文献1に示されている。また、当該カウンタ回路として、計数値を保持したままアップカウントとダウンカウントとを切り替えることが可能なリップルカウンタ回路を用いる構成が特許文献2に示されている。

図21は、特許文献2に記載された従来の固体撮像素子10の構成を示す図である。また図22は従来の固体撮像素子の動作波形を示す図である。同図を用いて従来の固体撮像素子10について説明する。

この固体撮像素子10は、画素アレイ部11と、行走査回路12と、列走査回路13と、タイミング制御回路14と、ADC群15と、DAC(デジタル−アナログ変換回路)16と、データ出力回路17とを有する。

画素アレイ部11には、単位画素111がマトリクス状に配置されている。

ADC群15は、画素配列の各列に対応して配置されているADC(A/D変換回路)15Aを含む。ADC15Aは、コンパレータ(CMP)151と、非同期アップ/ダウンカウンタ(CNT:以下、カラムカウンタとも呼ぶ)152と、スイッチ154とを含む。コンパレータ151は、DAC16により生成されせたランプ波形RAMPと、単位画素111から得られるアナログ信号とを比較する。カウンタ152は、コンパレータ151の出力及びクロック信号CKを受けてアップダウンカウント(またはダウンカウント)を行うとともに、カウント値を保持する機能を有する。

保持回路としての機能を有するカウンタ152は、初期時にはたとえばアップカウント(またはダウンカウント)状態に有り、リセットカウントを行い、対応するコンパレータ151の出力信号が反転すると、アップカウント動作を停止し、カウント値を保持する。このリセットカウント期間は、単位画素111のリセット成分を読み出している。

カウンタ152は、その後、ダウンカウント(またはアップカウント)状態となり、入射光量に対応したデータカウントを行い、対応するコンパレータ151の出力信号が反転すると、比較期間に応じたカウント値が保持される。

保持されたカウント値は、列走査回路13により走査され、デジタル信号として、データ転送線18を経てデータ出力回路17に入力される。

一般にカラムA/D変換方式では、画素アレイの列ごとにカラムA/D変換回路(カラムA/D変換器)が設けられている。そして画素アレイの列数と等しい数のカラムA/D変換回路が同時に動作する。そのため、A/D変換動作の際にカラムA/D変換回路を構成する各カラムカウンタが発生するノイズをNCNTとし、画素アレイの列数をMCとすると、カラムカウンタが発生するノイズの総和はNCNT×√MCとなる。一般に10Mピクセル以上の画素数をもつ画素アレイではその列数は数千列となるため、カラムカウンタの動作ノイズの影響は大きい。よって、カラムカウンタの動作ノイズを低減することにより良好な画像が得られる。

また、カラムA/D変換回路のレイアウトは画素ピッチに従い大きな制約を受けるため、複雑な回路構成をとることができない。その点においては従来のカラムカウンタは、その構成素子数は比較的少なく単純な構成であるリップルカウンタを用いているため、カラムA/D変換回路を構成するには適している。一方で、リップルカウンタはバイナリカウンタであるためカウント動作における低ノイズ化が考慮されていない。nビットのバイナリカウンタが0から最大値までカウント動作する際のデータの反転回数は(21+22+・・・+2n−n)回となり、同時に変化する最大ビット数はn個となる。

また、一般に低ノイズなカウンタとして、隣接する計数コードのデータ変化量が常に1、つまりハミング距離が1であるグレイコードカウンタが知られている。nビットのグレイコードカウンタが0から最大値までカウント動作する際のデータ反転回数は2n−1回であり、同時に変化する最大ビット数は1である。このように、グレイコードカウンタは、バイナリカウンタと比べデータ変化回数が約1/2であり、同時に変化する最大ビット数が1/nである。

しかしながらnビットグレイコードカウンタでは、各ビットの状態遷移を行うために全ビットの前状態が必要である。このため、各フリップフロップの入力端子にはn入力1出力の論理回路を付加する必要がある。これにより、その構成は複雑になり、かつ構成素子数も非常に多くなる。そのため、このようなグレイコードカウンタは、レイアウトに対して画素ピッチの制約を大きく受けるカラムA/D変換回路の構成要素としては適さない。

また、グレイコードカウンタと同様にハミング距離が1であるカウンタとして、ジョンソンカウンタが知られている。ジョンソンカウンタは、リップルカウンタと同様にその構成が単純であるが、nビットのリップルカウンタが2n進カウンタを構成できるのに対して、nビットのジョンソンカウンタは2n進カウンタとなる。例えば、10ビット精度のカラムA/D変換回路を構成するカラムカウンタは210進カウンタが必要である。従来技術に係るカラムカウンタでは10個のフリップフロップで210個の状態を表すことができるが、ジョンソンカウンタを用いた場合、29個のフリップフロップが必要となる。よって回路規模が非常に大きくなる。

本発明の目的は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる固体撮像装置及び撮像装置を提供することを目的とする。

上記目的を達成するために、本発明の一形態に係る固体撮像装置は、入射光を信号電荷に変換する受光部を有する複数の画素が行列状に配置された画素アレイと、前記複数の画素から出力されるアナログ信号を並列にデジタル信号に変換する複数のカラムA/D変換回路と、ランプ波を生成するランプ波発生回路と、前記複数のカラムA/D変換回路及び前記ランプ波発生回路を制御するとともに、クロック信号を生成するタイミング制御回路と、前記複数のカラムA/D変換回路で変換された前記デジタル信号を伝送する出力バスとを備え、前記複数のカラムA/D変換回路の各々は、前記アナログ信号と前記ランプ波との電位を比較し、比較した結果を示す比較結果信号を生成する比較器と、前記クロック信号をカウントするとともに、前記比較結果信号が変化する時点での計数値を前記デジタル信号として保持するカラムカウンタとを有し、前記カラムカウンタは、直列に接続された複数のカウンタを含み、前記複数のカウンタの各々は、隣接する計数値を示す計数コードのハミング距離が1である。

この構成によれば、本発明の一形態に係る固体撮像装置では、カラムカウンタは、直列に接続された、ハミング距離が1の複数のカウンタで構成されている。これにより、本発明の一形態に係る固体撮像装置は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる。

また、前記複数のカウンタの一部又は全ては、ジョンソンカウンタであり、前記複数のカウンタのうち最下位のカウンタのクロック入力端子には、前記クロック信号が供給され、最下位以外の複数のカウンタのクロック入力端子には、前段のカウンタの最上位ビットの正転又は反転出力信号が供給されてもよい。

また、前記複数のカウンタのうち最上位のカウンタが1ビットのカウンタであり、他のカウンタが2ビットのジョンソンカウンタであってもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる奇数ビットのカラムカウンタを実現できる。

また、前記複数のカウンタの全ては、2ビットのジョンソンカウンタであってもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる偶数ビットのカラムカウンタを実現できる。

また、前記複数のカウンタに含まれるn(nは2以上の整数)ビットのジョンソンカウンタは、アップカウントモードとダウンカウントモードとを切り替え可能であり、前記nビットのジョンソンカウンタは、n個のフリップフロップと、選択部とを備え、前記選択部は、前記アップカウントモード時には、前記n個のフリップフロップのうち、最下位ビットのフリップフロップのデータ入力端子を最上位ビットのフリップフロップの反転出力端子に接続し、前記n個のフリップフロップのうち、前記最下位ビット以外のフリップフロップのデータ入力端子を、当該フリップフロップの前ビットのフリップフロップの正転出力端子に接続し、前記ダウンカウントモード時には、前記最上位ビットのフリップフロップのデータ入力端子を、前記最下位ビットのフリップフロップの反転出力端子に接続し、前記n個のフリップフロップのうち、前記最上位以外のフリップフロップのデータ入力端子を、当該フリップフロップの次ビットのフリップフロップの正転出力端子に接続し、前記最下位以外の複数のカウンタのクロック入力端子に、前段のカウンタの最上位ビットの正転出力信号を供給してもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる、アップカウントモードとダウンカウントモードとを切り替え可能なカラムカウンタを実現できる。

また、前記カラムカウンタは、さらに、ホールドモードを有し、前記選択部は、前記ホールドモード時には、前記n個のフリップフロップの各々のデータ入力端子を自身の正転出力端子に接続し、前記タイミング制御回路は、前記カラムカウンタを前記アップカウントモード及び前記ダウンカウントモードの一方から他方へ切り替える際に、前記カラムカウンタをホールドモードにしたうえで、当該切り替えを行ってもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる、クロック信号が変化した際にも計数値を保持するホールドモードを有するカラムカウンタを実現できる。

また、前記複数のカウンタの一部又は全ては、グレイコードカウンタであり、前記複数のカウンタのうち最下位のカウンタのクロック入力端子には、前記クロック信号が供給され、最下位以外のカウンタのクロック入力端子には、前段のカウンタの最上位ビットの正転又は反転出力信号が供給されてもよい。

また、前記複数のカウンタのうち最上位のカウンタが1ビットのカウンタであり、他のカウンタが2ビットのグレイコードカウンタであってもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる奇数ビットのカラムカウンタを実現できる。

また、前記複数のカウンタの全ては、2ビットのグレイコードカウンタであってもよい。

この構成によれば、回路規模の増大を抑えつつ、ノイズの発生を低減できる偶数ビットのカラムカウンタを実現できる。

また、前記複数のカラムA/D変換回路の各々は、さらに、前記カラムカウンタの計数値を保持するデジタルメモリを備え、前記デジタルメモリに保持されている計数値が前記出力バスに出力されてもよい。

この構成によれば、本発明の一形態に係る固体撮像装置は、A/D変換処理と、メモリに保持された計数値を外部に出力する処理とを並列して行うことができる。これにより、本発明の一形態に係る固体撮像装置は、高速化を実現できる。

また、前記固体撮像装置は、前記出力バスを含み、前記複数のカラムA/D変換回路で変換された前記デジタル信号を伝送する複数の出力バスを備えてもよい。

この構成によれば、本発明の一形態に係る固体撮像装置は、複数の計測値を同時に外部に出力できる。これにより、本発明の一形態に係る固体撮像装置は、高速化を実現できる。

また、前記固体撮像装置は、さらに、前記出力バスにより伝送された前記計数コードを別の計数コードに変換するコード変換回路を備えてもよい。

この構成によれば、本発明の一形態に係る固体撮像装置は、所定の形式に変換したコードを外部に出力できる。これにより、当該固体撮像装置は、当該固体撮像装置の後段に接続される画像処理部等の処理量を低減できる。

また、前記コード変換回路は、前記出力バスにより伝送された前記計数コードをバイナリコードに変換してもよい。

また、前記画素アレイと、前記カラムA/D変換回路とは別チップに形成されていてもよい。

この構成によれば、画素アレイとカラムAD変換回路とを異なる半導体プロセスで製造できる。

なお、本発明は、このような固体撮像装置として実現できるだけでなく、このような固体撮像装置の機能の一部又は全てを実現する半導体集積回路(LSI)として実現したり、このような固体撮像装置を備える撮像装置として実現できる。

以上より、本発明は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる固体撮像装置及び撮像装置を提供できる。

以下、本発明に係る固体撮像装置の実施の形態について、図面を参照しながら詳細に説明する。

(第1の実施形態)

本発明の第1の実施形態に係る固体撮像装置では、カラムカウンタは、直列に接続された、ハミング距離が1の複数のカウンタで構成されている。これにより、本発明の第1の実施形態に係る固体撮像装置は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる。

本発明の第1の実施形態に係る固体撮像装置では、カラムカウンタは、直列に接続された、ハミング距離が1の複数のカウンタで構成されている。これにより、本発明の第1の実施形態に係る固体撮像装置は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる。

図1は、本発明の第1の実施形態に係る固体撮像装置50の構成を示す図である。図2は、本発明の第1の実施形態に係る固体撮像装置50の動作を示すタイミングチャートである。

図1に示す本発明の第1の実施形態に係る固体撮像装置50は、MOSイメージセンサである。この固体撮像装置50は、撮像部としての画素アレイ100と、垂直選択回路110と、水平選択回路120と、タイミング制御回路130と、複数のカラムA/D変換回路140と、D/A変換回路150と、コード変換回路を含む出力回路160とを有する。

画素アレイ100は、行列状に配置されている複数の画素101を含む。複数の画素101の各々は、入射光を信号電荷に変換する受光部であるフォトダイオードを含む。

また、画素アレイ100は、複数の垂直信号線102と、複数の制御信号線103とを含む。複数の垂直信号線102は、列毎に設けられており、対応する列で共通に用いられる出力線である。制御信号線103は、行毎に設けられており、対応する行で共通に用いられる。

垂直選択回路110は、画素アレイ100の画素101を、制御信号線103を通じて行ごとに一括で制御することで、画素101のリセット動作及び信号出力動作を制御する。

複数のカラムA/D変換回路140は、複数の画素101から出力されるアナログ信号を並列にデジタル信号に変換する。具体的には、カラムA/D変換回路140の各々は、画素アレイ100の列ごとに配置されている。各カラムA/D変換回路140の入力端子には、対応する垂直信号線102が接続されている。また、各カラムA/D変換回路140の出力端子は出力バス170に接続されている。このカラムA/D変換回路140は、垂直信号線102のアナログ信号をデジタル信号(デジタルコード)に変換する。

水平選択回路120は、各カラムA/D変換回路140により変換されたデジタル信号を出力バス170に順次読み出す。出力バス170は、複数のカラムA/D変換回路140で変換されたデジタル信号を伝送する。

出力回路160は、各カラムA/D変換回路140から出力バス170を通して読み出されたデジタルコードを別のデジタルコードに変換して外部へ出力する。

タイミング制御回路130は、垂直選択回路110、水平選択回路120、D/A変換回路150及び各カラムA/D変換回路140を制御するための内部クロック及び制御信号を生成する。具体的には、タイミング制御回路130は、リセット信号RST、カウントモード制御信号UD、ホールド制御信号HLD、及び、カウンタクロック信号CKを生成する。

D/A変換回路150は、ランプ波RAMPを生成するランプ波発生回路である。

各カラムA/D変換回路140は、比較器141と、Nビットカラムカウンタ回路であるカラムカウンタ142と、出力スイッチ143とを備える。

比較器141は、複数の画素101から出力されるアナログ信号とランプ波RAMPとの電位を比較し、比較した結果を示す比較結果信号を生成する。具体的には、比較器141の一方の入力端子は、画素アレイ100の垂直信号線102に接続されており、当該一方の入力端子には画素101の出力信号が入力される。また、比較器141の他方の入力端子は、D/A変換回路150出力信号線であるRAMP信号線が接続されており、当該他方の入力端子にはランプ波RAMPが入力される。

カラムカウンタ142は、カウンタクロック信号CKをカウントするとともに、比較器141により出力される比較結果信号が変化する時点での計数値をデジタル信号(計数コード)として保持する。

例えば、カラムカウンタ142は、図3に示すように複数のジョンソンカウンタが直列に接続された構成である。また、当該カラムカウンタ142の計数コードは従来例におけるカラムカウンタである非同期バイナリカウンタ(リップルカウンタ)が生成するバイナリコードとは異なる。

各カラムカウンタ142には、タイミング制御回路130から供給されるリセット信号RST、カウントモード制御信号UD、ホールド制御信号HLD及びカウンタクロック信号CKが入力される。リセット信号RSTはカウンタを初期化するための信号である。カウントモード制御信号UD及びホールド制御信号HLDは、アップカウントモードとダウンカウントモードとホールドモードとの切り替えを制御するための信号である。

出力スイッチ143は、水平選択回路120により制御され、カラムカウンタ142に保持された計数値を順次出力バス170に出力する。また、コード変換回路を含む出力回路160は、出力バス170に出力されたカラムカウンタ142の計数コードをバイナリコードに変換し、変換したバイナリコードを出力する。

なお、カラムカウンタ142及び出力回路160の詳細については後述する。

次に、本発明の第1の実施形態に係る固体撮像装置50の動作について説明する。

先ず、タイミング制御回路130により各カラムA/D変換回路140のカラムカウンタ142及びD/A変換回路150が初期化される。これにより、カラムカウンタ142は予め決められた初期値にリセットされる。また、D/A変換回路150は、ランプ波形RAMPの初期電位を各比較器141の一方の入力端子に供給する。

次に、タイミング制御回路130は、カウントモード制御信号UD及びホールド制御信号HLDを制御することで、各カラムカウンタ142をダウンカウントモードにセットする。

次に、垂直選択回路110は、ある行の複数の画素101を選択するとともに、選択した画素101から画素リセット電位を出力させる。これにより、各列の画素リセット電位は、対応する列の垂直信号線102を通して、対応する列の比較器141のもう一方の入力端子に供給される。

この状態でタイミング制御回路130は各カラムカウンタ142にカウンタクロック信号CKを供給する。これにより、カラムカウンタ142は、カウンタクロック信号CKの計数を開始する。また、タイミング制御回路130は、カウンタクロック信号CKに同期してD/A変換回路150がランプ波形RAMPを生成するよう制御する。

次いで、ある列の比較器141に入力される画素リセット電位とランプ波形RAMPとの電位の大小関係が入れ替わると、その比較器141の出力信号が反転する。これにより、その列のカラムカウンタ142へのカウンタクロック信号CKがマスクされる。よって、その列のカラムカウンタ142は比較器141の出力信号が反転した時点での計数値を保持する。ここで、D/A変換回路150が生成するランプ波形RAMPと、タイミング制御回路130が生成するカウンタクロック信号CKとは互いに同期しているため、選択された画素101から出力される画素リセット電圧に対応した計数値がカラムカウンタ142に保持される。

タイミング制御回路130は、予め決められたパルス数を出力するとカウンタクロック信号CKを停止するとともに、それに同期してD/A変換回路150によるランプ波形RAMPの出力を停止させる。

次に、タイミング制御回路130は、D/A変換回路150を初期化する。これにより、各比較器141の一方の入力端子には再びランプ電圧の初期値が供給される。

次に、タイミング制御回路130は、カウントモード制御信号UD及びHOLD信号を制御することで、各カラムカウンタ142をアップカウントモードにセットする。

次に、垂直選択回路110は、選択している画素101に、入射光量に応じた画素信号電位を出力させる。これにより、各列の画素信号電位は、対応する列の垂直信号線102を通して、対応する列の比較器141のもう一方の入力端子に供給される。この画素信号電位は画素リセット電位をオフセットにもつ。この状態でタイミング制御回路130は各カラムカウンタ142にカウンタクロック信号CKを供給する。これにより、カラムカウンタ142は、カウンタクロック信号CKの計数を開始する。また、タイミング制御回路130は、カウンタクロックに同期してD/A変換回路150がランプ波形RAMPを生成するよう制御する。

次いで、ある列の比較器141に入力される画素信号とランプ波形RAMPとの大小関係が入れ替わると、その比較器141の出力信号が反転する。これにより、その列のカラムカウンタ142へ供給されるカウンタクロック信号CKがマスクされる。よって、その列のカラムカウンタ142は比較器141の出力信号が反転した時点での計数値を保持する。ここで保持されている計数値は、カラムカウンタ142の初期値をCINITとし、画素リセット電位に対応する計数値をCRSTとし、画素信号電位に対応する計数値をCSIGとすると、CINIT−CRST+CSIGとなる。つまり以上の動作により、画素リセット電位と画素信号電位との差分つまり入射光に応じた画素信号電圧に対応するデジタル値が得られることとなる。

次に、タイミング制御回路130は、予め決められたパルス数を出力するとカウンタクロック信号CKを停止するとともに、それに同期してD/A変換回路150によるランプ波形RAMPの出力を停止させる。以上により、画素信号のA/D変換が完了する。また、以上の動作は各列で同時並列的に行われる。

次に、各カラムカウンタ142に保持された計数値は水平選択回路120により順次出力バス170に読み出される。そして、読み出された計数値は、出力回路160に供給される。出力回路160は、コード変換回路を有しており、カラムカウンタ142の計数コードをバイナリコードに変換し、変換したバイナリコードを出力する。

次に、カラムカウンタ142について詳細を説明する。

図3は、本発明の第1の実施形態に係るカラムカウンタ142のブロック図である。本発明の第1の実施形態に係るカラムカウンタ142は、直列に接続されたn個のジョンソンカウンタ301を含む。各ジョンソンカウンタ301は、隣接する計数値を示す計数コードのハミング距離が1である。また、各ジョンソンカウンタ301は、カウントモード制御信号UDによりアップカウントモードとダウンカウントモードとを切り替え可能である。

n個のジョンソンカウンタ301は、それぞれM1〜Mnビットで構成される。また、n個のジョンソンカウンタ301は、そのクロック入力端子CKに供給されるクロック信号が変化した際にも計数を保持するホールドモードを有している。このホールドモードへの切り替えは、ホールド制御信号HLDにより制御される。また、n個のジョンソンカウンタ301は、リセット信号RSTによりカウント値を予め決められた初期値に初期化する機能を有する。

最下位のジョンソンカウンタ301のクロック入力端子CKには図1におけるカウンタクロック信号CKが供給される。x段目(xは1〜n−1)ジョンソンカウンタ301の出力端子Oは次段(x+1段目)のジョンソンカウンタ301のクロック入力端子CKに接続される。言い換えると、最下位以外の複数のジョンソンカウンタ301のクロック入力端子CKには、前段のジョンソンカウンタ301の最上位ビットの正転(非反転)又は反転出力信号が供給される。よって、カラムカウンタ142は、2n×(M1×M2×…×Mn)進カウンタとなる。ここでカラムカウンタ142を構成するn個のジョンソンカウンタ301のビット数M1〜Mnは全て又はその幾つかが同じビット数でもかまわない。

ここでは、

(a)M1〜Mnが全て2

(b)M1〜Mn−1が全て2かつMnが1

の場合をそれぞれ説明する。

(a)M1〜Mnが全て2

(b)M1〜Mn−1が全て2かつMnが1

の場合をそれぞれ説明する。

上記(a)の場合では、カラムカウンタ142は、2nビットで構成される22n進カウンタである。また、当該カラムカウンタ142は、2nビットバイナリカウンタと同様に2nビットで表される全てのコードを使用するフィルドコードカウンタである。

上記(b)の場合では、カラムカウンタ142は、2n+1ビットで構成される22n+1進カウンタである。また、当該カラムカウンタ142は、2n+1ビットバイナリカウンタと同様に2n+1ビットで表される全てのコードを使用するフィルドコードカウンタである。

図4Aは、上記(a)の場合におけるカラムカウンタ142のブロック図である。また、図4Bは、上記(b)の場合におけるカラムカウンタ142のブロック図である。

図4A及び図4Bに示すように、最下位のジョンソンカウンタ401のクロック入力端子CKにはカウンタクロック信号CKが供給され、他のジョンソンカウンタ402及び403のクロック入力端子CKには前段のジョンソンカウンタの出力端子Oが接続される。

次に、本発明の第1の実施形態に係るカラムカウンタ142の構成要素である2ビットU/Dジョンソンカウンタ401について説明する。

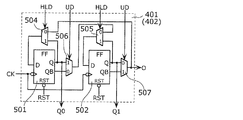

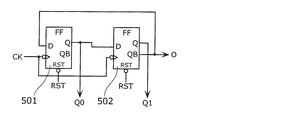

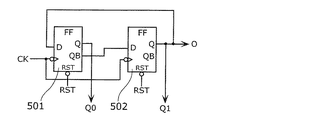

図5は、本発明の第1の実施形態に係る2ビットU/Dジョンソンカウンタ401の回路例を示す図である。なお、2ビットU/Dジョンソンカウンタ402の構成も同様である。

図5に示すように、2ビットU/Dジョンソンカウンタ401は、第0ビットを表すフリップフロップ501と、第1ビットを表すフリップフロップ502と、マルチプレクサ504〜507とを備える。

マルチプレクサ506及び507は、カウントモード制御信号UDにより制御され、アップカウントモードとダウンカウントモードとを切り替えるために用いられる。マルチプレクサ504及び505は、ホールド制御信号HLDにより制御され、アップカウントモードとダウンカウントモードとの切り替え時にフリップフロップ501及び502が保持している値の破壊を回避するために設けられている。これらのマルチプレクサ504〜507は、本発明の選択部に相当する。

先ずアップカウントモードについて説明する。

図6Aは、アップカウントモードにおける2ビットU/Dジョンソンカウンタ401の等価回路を示す図である。

アップカウントモードでは、マルチプレクサ506はフリップフロップ501の正転出力信号Qを選択し、マルチプレクサ507はフリップフロップ502の反転出力信号QBを選択する。また、マルチプレクサ504はマルチプレクサ507の出力信号を選択し、マルチプレクサ505はマルチプレクサ506の出力信号を選択する。

よって、アップカウントモード時には、フリップフロップ501のデータ入力端子Dにはフリップフロップ502の反転出力信号が供給され、フリップフロップ502のデータ入力端子Dにはフリップフロップ501の正転出力信号Qが供給される。また、次段の2ビットU/Dジョンソンカウンタ402又は1ビットU/Dジョンソンカウンタ403のCK入力端子に接続される出力端子Oには、フリップフロップ502の反転出力信号QBが供給される。

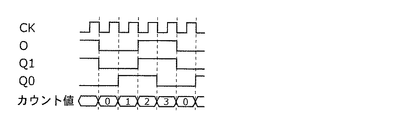

図6Bは、アップカウントモードにおける2ビットU/Dジョンソンカウンタ401のタイミングチャートである。図6Aに示すように、2ビットU/Dジョンソンカウンタ401では、0〜3までのアップカウントにおけるデータ変化回数は、フリップフロップ501が2回、フリップフロップ502が1回の計3回であり、最大同時変化ビット数は1ビットである。

次にダウンカウントモードについて説明する。

図7Aは、ダウンカウントモードにおける2ビットU/Dジョンソンカウンタ401の等価回路を示す図である。

ダウンカウントモードでは、マルチプレクサ506はフリップフロップ501の反転出力信号QBを選択し、マルチプレクサ507はフリップフロップ502の正転出力信号Qを選択する。また、マルチプレクサ504はマルチプレクサ507の出力信号を選択し、マルチプレクサ505はマルチプレクサ506の出力信号を選択する。

よって、ダウンカウントモード時には、フリップフロップ501のデータ入力端子Dにはフリップフロップ502の正転出力信号が供給され、フリップフロップ502のデータ入力端子Dにはフリップフロップ501の反転出力信号が供給される。また、次段の2ビットU/Dジョンソンカウンタ402又は1ビットU/Dジョンソンカウンタ403のCK入力端子に接続される出力端子Oには、フリップフロップ502の正転出力信号Qが供給される。

図7Bは、ダウンカウントモードにおける2ビットU/Dジョンソンカウンタ401のタイミングチャートである。図7Bに示すように、2ビットU/Dジョンソンカウンタ401では、3〜0までのダウンカウントにおけるデータ変化回数は、フリップフロップ501が2回、フリップフロップ502が1回の計3回であり、最大同時変化ビット数は1ビットである。

なお、ジョンソンカウンタ401及び402がnビットの場合、アップカウントモード時には、最下位ビットのフリップフロップのデータ入力端子が最上位ビットのフリップフロップの反転出力端子に接続される。また、最下位ビット以外のフリップフロップのデータ入力端子は、当該フリップフロップの前ビットのフリップフロップの正転出力端子に接続される。また、各ジョンソンカウンタ401及び402の出力端子Oには、最上位ビットのフリップフロップの反転出力端子が接続される。言い換えると、最下位以外の複数のジョンソンカウンタのクロック入力端子には、前段のジョンソンカウンタに含まれる最上位ビットのフリップフロップの反転出力信号が供給される。

また、ダウンカウントモード時には、最上位ビットのフリップフロップのデータ入力端子は、最下位ビットのフリップフロップの反転出力端子に接続される。また、最上位以外のフリップフロップのデータ入力端子は、当該フリップフロップの次ビットのフリップフロップの正転出力端子に接続される。また、各ジョンソンカウンタ401及び402の出力端子Oには、最上位ビットのフリップフロップの正転出力端子が接続される。言い換えると、最下位以外の複数のジョンソンカウンタのクロック入力端子には、前段のジョンソンカウンタに含まれる最上位ビットのフリップフロップの正転出力信号が供給される。

最後にアップカウントモードとダウンカウントモードとの切り替えについて説明する。

前述したように、2ビットU/Dジョンソンカウンタ402のクロック入力端子CKは前段の2ビットU/Dジョンソンカウンタ401又は402の出力端子Oが接続されている。また、アップカウントモード時には、当該クロック入力端子CKは、前段の上位ビットのフリップフロップ501の反転出力端子QBが、ダウンカウントモード時では前段の上位ビットのフリップフロップ501の正転出力端子Qが接続される。よって、アップカウントモードとダウンカウントモードとの切り替え時にクロック入力端子CKの接続先が変化することとなるためフリップフロップ501及び502に保持されているデータが書き換わる可能性がある。

これに対して、本発明の第1の実施形態に係る固体撮像装置50は、カラムカウンタ142をアップカウントモード及びダウンカウントモードの一方から他方へ切り替える際に、ホールド制御信号HLDによりカラムカウンタ142をホールドモードにしたうえで、当該切り替えを行う。

ホールドモードでは、マルチプレクサ504はフリップフロップ501の正転出力信号Qを選択し、マルチプレクサ505はフリップフロップ502の正転出力信号Qを選択する。よって、フリップフロップ501及び502のデータ入力端子Dにはそれぞれ自身の正転出力端子が接続される。これにより、アップカウントモードとダウンカウントモードとの切り替え時にフリップフロップ501及び502の保持データが書き換わることを防止できる。

次に、本発明の第1の実施形態に係るカラムカウンタ142の構成要素のひとつである1ビットU/Dジョンソンカウンタ403について説明する。

図8Aは、本発明の第1の実施形態に係る1ビットU/Dジョンソンカウンタ403の回路例を示す図である。また、図8Bは、1ビットU/Dジョンソンカウンタ403のタイミングチャートである。

1ビットU/Dジョンソンカウンタ403は、1ビットカウンタであるため、アップカウント及びダウンカウントで同じ動作を行う。しかしながら、前述した2ビットU/Dジョンソンカウンタ401と同様にアップカウントモードとダウンカウントモードとの切り替え時にクロック入力端子CKの接続先が変化するため、フリップフロップ503に保持されているデータが書き換わる可能性がある。

これに対して、本発明の第1の実施形態に係る固体撮像装置50は、アップカウントモードとダウンカウントモードとの切り替え時に、ホールド制御信号HLDによりフリップフロップ503をホールドモードにする。ホールドモードにおいて、マルチプレクサ508はフリップフロップ503の正転出力信号を選択する。よって、フリップフロップ503のデータ入力端子にはそれ自身の正転出力端子が接続される。これにより、アップカウントモードとダウンカウントモードとの切り替え時にフリップフロップ503の保持データが書き換わることを防止できる。

以上、本発明の第1の実施形態に係るカラムカウンタ142の構成要素である、2ビットU/Dジョンソンカウンタ401及び402と、1ビットU/Dジョンソンカウンタ403について述べた。以下では、本発明の第1の実施形態に係るカラムカウンタ142について比較例と比較しながら説明する。

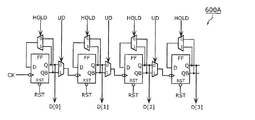

なお、以下では、説明を簡略化するため、図4Aに示すカラムカウンタ142の具体例として2個の2ビットU/Dジョンソンカウンタ401及び402を備える4ビットカラムカウンタ142Aと、図4Bに示すカラムカウンタ142の具体例として2個の2ビットU/Dジョンソンカウンタ401及び402と1個の1ビットU/Dジョンソンカウンタ403とを備える5ビットカラムカウンタ142Bについてそれぞれ比較例である4ビットリップルカウンタ600A及び5ビットリップルカウンタ600Bと比較しながら説明する。

先ず、本発明の第1の実施形態に係る、2個の2ビットU/Dジョンソンカウンタ401及び402から構成される4ビットカラムカウンタ142Aについて説明する。

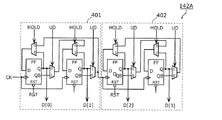

先ず回路の構成素子数について比較例と本発明の第1の実施形態とを比較する。図9Aは、本発明の第1の実施形態に係る4ビットカラムカウンタ142Aの回路図である。図9Bは、比較例である4ビットリップルカウンタ600Aの回路図である。

図9Aに示すように本発明の第1の実施形態に係る4ビットカラムカウンタ142Aは、4個のフリップフロップと、8個のマルチプレクサとを含む。一方、図9Bに示す比較例の4ビットリップルカウンタ600Aは、4個のフリップフロップと、7個のマルチプレクサとを含む。

次にnビット(nは偶数)の場合を考える。図9Aに示すように本発明の第1の実施形態では2ビットU/Dジョンソンカウンタ401及び402は、2個のフリップフロップと2個の2入力マルチプレクサとを含む。よって本発明の第1の実施形態に係るnビット(nは偶数)カラムカウンタはn個のフリップフロップと2n個の2入力マルチプレクサとを含む。

図9Bに示すように比較例のnビットU/Dリップルカウンタでは、最上位ビットを除き各ビットは1個のフリップフロップと2個の2入力マルチプレクサとを含む。また、最上位ビットは1個のフリップフロップと1個の2入力マルチプレクサとを含む。つまり、比較例のnビットのカラムカウンタは、n個のフリップフロップと2n−1個の2入力マルチプレクサとを含む。

以上のことより、本発明の第1の実施形態に係るnビットカラムカウンタ(nは偶数)の構成素子数は比較例とほぼ同等であるといえる。

次に、カウント動作の際のフリップフロップのデータの変化回数及び同時に変化する最大のビット数について、つまりカウント動作におけるフリップフロップのデータが変化することに起因するノイズ量及びそのピーク量について比較例と本発明の第1の実施形態とを比較する。

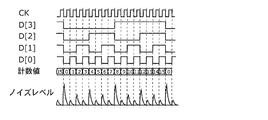

先ず、本発明の第1の実施形態に係る4ビットカラムカウンタ142Aのデータ変化回数について説明する。図10Aは、本発明の第1の実施形態に係る4ビットカラムカウンタ142Aのアップカウントモードにおけるタイミングチャートである。

先ず、第0ビット及び第1ビットについて考える。第0及び第1ビットのクロック入力端子にはカウンタクロック信号CKが入力される。本発明の第1の実施形態の例に示すフリップフロップは、図10Aに示すように、カウンタクロック信号CKの立下りエッジに同期してデータが変化する。本発明の第1の実施形態に係るカラムカウンタの第0、第1ビットはそれぞれカウンタクロック信号CKの立下りエッジが2回入力されるごとに1回データを変化する。よって、0〜15(=24−1)までカウントするためには、15(=24−1)回のカウンタクロック信号CKの立下りエッジが入力される。図10Aに示すように第0ビットは1回目の立下りエッジから変化するため、8(=24−1)回データが変化する。第1ビットは2回目の立下りエッジから変化するため、7(=24−1−1)回データが変化する。

次に第2、第3ビットについて考える。アップカウントモードでは第2、第3ビットのクロック入力端子には第1ビットの正転出力信号が入力される。また、ダウンカウントモードでは、当該クロック入力端子には第1ビットの反転出力信号が入力される。よって、0〜15(=24−1)までカウントするためには第2、第3ビットには立下りエッジが3(=24−2−1)回入力される。図10Aに示すように第2ビットは1回目の立下りエッジから変化するため、2(=22−1)回データが変化する。第3ビットは2回目のパルスから変化するため、1(=22−1−1)回データが変化する。つまりnビットカウンタでは0〜2n−1までカウントアップするのにカラムカウンタを構成するn個のフリップフロップは(2n+2n−2+・・・+24+22−n/2)回そのデータが変化する。例えば分解能が10ビットのカラムA/D変換回路は10ビットのカラムカウンタをもつ。この場合、本発明の第1の実施形態に係るカラムカウンタが0〜1023までカウントする間にカラムカウンタの全フリップフロップのデータは合計で1359回変化する。これはダウンカウントにおいても同様である。

次に、本発明の第1の実施形態に係るカラムカウンタにおいて同時に変化する最大のビット数について説明する。

本発明の第1の実施形態に係るカラムカウンタは、2ビットのジョンソンカウンタを直列に接続した構成である。これにより、偶数ビットから奇数ビットへの桁上がりの際には、つまり該カラムカウンタ142を構成するある2ビットのジョンソンカウンタ内の桁上がりの際には、桁上がりするジョンソンカウンタの1ビットのみしか変化しない。また、奇数ビットから偶数ビットへの桁上がりの際には、つまり概カラムカウンタを構成する2ビットのジョンソンカウンタをまたぐ桁上がりの際には、桁上がりが発生する最上位の2ビットジョンソンカウンタから最下位の2ビットジョンソンカウンタのそれぞれ上位ビットのみが変化する。よって、同時にデータが変化する最大ビット数はn/2ビットとなる。これはダウンカウントにおいても同様である。

本発明の第1の実施形態に係る4ビットカラムカウンタ142Aにおける、カラムカウンタのデータ変化により発生するノイズレベルの概略図を図10Aのタイミングチャートにあわせて示している。

次に、比較例の4ビットリップルカウンタ600Aのデータ変化回数について説明する。比較例の4ビットリップルカウンタ600Aはバイナリカウンタの一種である。比較例の4ビットリップルカウンタ600Aのアップカウントモードにおけるタイミングチャートを図10Bに示す。

先ず第0ビット(最下位ビット)について考える。図10Bに示すように最下位ビットはカウンタクロックの立下りエッジが1回入力されるごとに変化する。よって0〜15までカウントする間に15(=24−1)回の立下りエッジがあるため15(=24−1)回データは変化する。

次に第1ビットについて考える。第1ビットでは第0ビットの正転出力信号がクロック入力信号となっているため、7(=24−1−1)回の立下りエッジが入力される。つまり0〜15までカウントする間に7(=24−1−1)回データが変化する。同様に第2ビットでは3(=22−1)回、第3ビット(最上位ビット)では1(=21−1)回データが変化する。

つまり、nビットカウンタでは0〜2n−1までカウントアップするのにカラムカウンタを構成するn個のフリップフロップは合計で(21+22+・・・+2n−n)回データが変化することとなる。例えば分解能が10ビットのカラムA/D変換回路は10ビットのカラムカウンタをもつ。この場合、比較例のリップルカウンタが0〜1023までカウントする間にカラムカウンタの全フリップフロップのデータは合計で2037回変化する。これはダウンカウントにおいても同様である。

次に、比較例のリップルカウンタの同時に変化する最大のビット数について説明する。比較例のリップルカウンタはバイナリカウンタであるため、桁上がりの際に桁上がりビットとそれ以下のビットが全て同時に変化する。よって、同時にデータが変化する最大ビット数はnビットとなる。これはダウンカウントにおいても同様である。

比較例の4ビットリップルカウンタ600Aにおける、データ変化により発生するノイズレベルの模式図を図10Bのタイミングチャートにあわせて示している。

次に、本発明の第1の実施形態に係るカラムカウンタの具体例である2個の2ビットU/Dジョンソンカウンタと、1個の1ビットU/Dジョンソンカウンタとを含む5ビットカラムカウンタ142Bの例を説明する。

先ず回路の構成素子数について比較例と本発明の第1の実施形態とを比較する。図11Aは、本発明の第1の実施形態に係る5ビットカラムカウンタ142Bの回路図である。図11Bは、比較例の5ビットリップルカウンタ600Bの回路図である。

図11Aに示すように本発明の第1の実施形態に係る5ビットカラムカウンタ142Bは、5個のフリップフロップと9個のマルチプレクサとを含む。一方、比較例の5ビットリップルカウンタ600Bは、5個のフリップフロップと9個のマルチプレクサとを含む。

次に、nビット(nは奇数)の場合を考える。図11Aに示すように本発明の第1の実施形態に係る2ビットU/Dジョンソンカウンタ401及び402は、2個のフリップフロップと2個の2入力マルチプレクサとを含む。また、本発明の第1の実施形態に係る1ビットU/Dジョンソンカウンタ403は、1個のフリップフロップと1個の2入力マルチプレクサとを含む。よって、本発明の第1の実施形態に係るnビット(nは奇数)カラムカウンタは、n個のフリップフロップと、2n−1個の2入力マルチプレクサとを含む。

一方、図11Bに示すように比較例のnビットのリップルカウンタは、最上位ビットを除き各ビットは1個のフリップフロップと、2個の2入力マルチプレクサとを含む。また、最上位ビットは1個のフリップフロップと1個の2入力マルチプレクサとを含む。つまり、比較例のnビットのリップルカウンタはn個のフリップフロップと2n−1個の2入力マルチプレクサとを含む。以上のことより、本発明の第1の実施形態に係るnビットカラムカウンタ(nは奇数)の構成素子数は比較例と同等である。

次に、カウント動作の際のフリップフロップのデータの変化回数及び同時に変化する最大のビット数について、つまりカウント動作におけるフリップフロップのデータが変化することに起因するノイズ量及びそのピーク量について比較例と本発明の第1の実施形態とで比較する。

先ず、本発明の第1の実施形態に係るカラムカウンタのデータ変化回数について説明する。図12Aは、本発明の第1の実施形態に係る5ビットカラムカウンタ142Bのアップカウントモードにおけるタイミングチャートである。

先ず、第0ビット及び第1ビットについて考える。第0及び第1ビットのクロック入力端子にはカウンタクロック信号CKが入力される。本発明の第1の実施形態の例に示すフリップフロップは、図12Aに示すように、カウンタクロック信号CKの立下りエッジに同期してデータが変化する。本発明の第1の実施形態に係るカラムカウンタの第0、第1ビットはそれぞれカウンタクロック信号CKが2パルス入力されるごとに1回データが変化する。よって、0〜31(=25−1)までカウントするためには31(=25−1)回の立下りエッジが入力される。図12Aに示すように第0ビットは1回目の立下りエッジから変化するため、16(=25−1)回データが変化する。第1ビットは2回目の立下りエッジから変化するため、15(=25−1−1)回データが変化する。

次に第2、第3ビットについて考える。アップカウントモードでは第2、第3ビットのクロック入力端子には第1ビットの正転出力信号が入力される。また、ダウンカウントモードでは当該クロック入力端子には第1ビットの反転出力信号が入力される。よって0〜31(=25−1)までカウントするためには第2、第3ビットに入力されるパルスの立下りエッジは7(=25−2−1)回となる。図12Aに示すように第2ビットは1回目の立下りエッジから変化するため、4(=25−3)回データが変化する。第3ビットは2回目の立下りエッジから変化するため、3(=25−3−1)回データが変化する。

次に第5ビットについて説明する。アップカウントモードでは第4ビットのクロック入力端子には第3ビットの正転出力信号が入力される。また、当該クロック入力端子にはダウンカウントモードでは第3ビットの反転出力信号が入力される。よって0〜31(=25−1)までカウントするためには第4ビットに入力される立下りエッジは1(=25−4−1)回である。第4ビット(最上位ビット)はクロック入力端子に立下りエッジが1回入力されるごとに1回データを変化させるため、1(=25−4−1)回データが変化する。つまり、本発明の第1の実施形態に係るnビットのカラムカウンタ(nは奇数)では0〜2n−1までカウントアップするのにカラムカウンタを構成するn個のフリップフロップは(2n+2n−2+・・・+23+21−((n−1)/2+1))回そのデータが変化する。例えば分解能が11ビットのカラムA/D変換回路は11ビットのカラムカウンタをもつ。この場合、本発明の第1の実施形態に係るカラムカウンタが0〜2047までカウントする間にカラムカウンタの全フリップフロップのデータは合計で2724回変化する。これはダウンカウントにおいても同様である。

次に、本発明の第1の実施形態に係るカラムカウンタの同時に変化する最大のビット数について説明する。本発明の第1の実施形態に係るカラムカウンタは、2個の2ビットのジョンソンカウンタと、1個の1ビットのジョンソンカウンタとを直列に接続した構成である。これにより、偶数ビットから奇数ビットへの桁上がりの際には、つまり該カラムカウンタを構成するある2ビットのジョンソンカウンタ内の桁上がりの際には、桁上がりするジョンソンカウンタの1ビットのみしか変化しない。また、奇数ビットから偶数ビットへの桁上がりの際には、つまり概カラムカウンタを構成するジョンソンカウンタをまたぐ桁上がりの際には、桁上がりが発生する最上位のジョンソンカウンタから最下位のジョンソンカウンタのそれぞれ上位ビットのみが変化する。よって、同時にデータが変化する最大ビット数は(n−1)/2+1ビットとなる。これはダウンカウントにおいても同様である。

次に、比較例の5ビットリップルカウンタ600Bのデータ変化回数について説明する。比較例の5ビットリップルカウンタ600Bはバイナリカウンタの一種である。比較例の5ビットリップルカウンタ600Bのアップカウントモードにおけるタイミングチャートを図12Bに示す。

先ず第0ビット(最下位ビット)について考える。図12Bに示すように最下位ビットはカウンタクロック信号CKの立下りエッジが1回入力されるごとに変化する。よって0〜31までカウントする間に31(=25−1)回の立下りエッジがあるため31(=25−1)回データは変化する。

次に第1ビットについて考える。第1ビットでは第0ビットの正転出力信号がクロック入力信号となっているため、15(=25−1−1)回の立下りエッジが入力される。つまり0〜31までカウントする間に15(=25−1−1)回データが変化する。

同様に第2ビットでは7(=25−2−1)回、第3ビットでは3(=25−3−1)回、第4ビットでは1(=25−4−1)回データが変化する。

つまりnビットカウンタでは0〜2n−1までカウントアップするのにリップルカウンタを構成するn個のフリップフロップは合計で(21+22+・・・+2n−n)回データが変化することとなる。例えば分解能が11ビットのカラムA/D変換回路は11ビットのカラムカウンタをもつ。この場合、比較例のリップルカウンタが0〜2047までカウントする間にカラムカウンタの全フリップフロップのデータは合計で4083回変化する。これはダウンカウントにおいても同様である。

次に、比較例のリップルカウンタの同時に変化する最大のビット数について説明する。比較例のリップルカウンタはバイナリカウンタである。よって、桁上がりの際に桁上がりビットとそれ以下のビットが全て同時に変化するため同時にデータが変化する最大ビット数はnビットとなる。これはダウンカウントにおいても同様である。

比較例の5ビットリップルカウンタ600Bのデータ変化により発生するノイズレベルの模式図を図12Bのタイミングチャートにあわせて示している。

以上より、本発明の第1の実施形態に係るカラムA/D変換回路140を構成するカラムカウンタ142は、比較例のリップルカウンタと回路規模はほぼ同等である。また、当該カラムカウンタ142は、カウント動作におけるカウンタのデータ変化回数及び同時に変化するビット数、つまり、カウント動作におけるノイズ量及びピークノイズ量を大幅に低減できる。また、カラムカウンタ142はデータ変化量が少ないため低消費電力化も期待できる。

次に、図1に示す出力回路160について説明する。前述したように本発明に係るカラムA/D変換回路140を構成するカラムカウンタ142の計数コードは一般的なコードとは異なる。よってこの計数コードを、本発明に係る固体撮像装置50の後段に配置されるDSP回路などが処理できるバイナリコードに変換する必要がある。

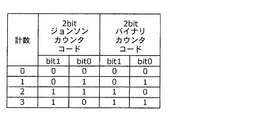

先ず、本発明の第1の実施形態に係るカラムカウンタ142のビット数nが偶数である場合について説明する。図13は、本発明の第1の実施形態に係るカラムカウンタ142を構成する2ビットジョンソンカウンタと、通常の2ビットバイナリカウンタとのコード比較表である。

図13に示すように、本発明の第1の実施形態に係る2ビットジョンソンカウンタの第1ビット(上位ビット)は2ビットバイナリカウンタと同一である。つまり、奇数ビットから偶数ビットへの桁上がりのタイミングはバイナリコードと変わらない。つまり、偶数ビットのみに処理を行うことで、カラムカウンタ142の計数コードをバイナリコードに変換できる。

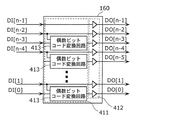

図14Aは、本発明の第1の実施形態に係るnビット(nは偶数)の出力回路160の構成を示す図である。図14Aに示す出力回路160は、コード変換回路411と出力バッファ412とを含む。コード変換回路411は、n/2個の偶数ビットコード変換回路413を含む。各コード変換回路411は、対応する偶数ビットと、当該偶数ビットの上位1ビットとのデータを用いて、当該偶数ビットのデータを、バイナリコードの対応するビットのデータに変換する。

次に、本発明の第1の実施形態におけるカラムカウンタ142のビット数n+1が奇数である場合について説明する。

図4Bに示すように、カラムカウンタ142のビット数が奇数の場合、ビット数が偶数の場合と異なる点は最上位ビットが1ビットのジョンソンカウンタ403で構成される点である。それ以下のnビットについては前述したとおりである。また、前述したようにカラムカウンタ142のビット数が奇数である場合の最上位ビットは比較例のリップルカウンタの最上位ビットと同様の動作となる。よってカラムカウンタ142のビット数が奇数である場合の最上位ビットは他の偶数ビットと異なり、奇数ビットと同様にリップルカウンタと同様となる。よって、最上位ビットを除く偶数ビットのみに処理を行うことで、カラムカウンタ142の計数コードをバイナリコードに変換できる。

図14Bは、本発明の第1の実施形態に係るn+1ビット(nは偶数)の出力回路160の構成を示す図である。図14Bに示す出力回路160は、コード変換回路411と出力バッファ412とを含む。コード変換回路411はn/2個の偶数ビットコード変換回路413を含む。

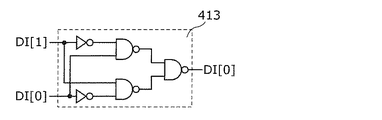

図15は、偶数ビットコード変換回路413の一例を示す図である。図15に示すように偶数ビットコード変換回路413は、2個のインバータと、3個の2入力NANDとを含む。本発明の第1の実施形態では1つのコード変換回路411を全カラムA/D変換回路140で時間分割して使用する。よって、固体撮像装置50に追加する回路規模を非常に小さくできる。また、このコード変換回路411の配置箇所は、カラムA/D変換回路140とは異なり比較的自由度がある。よって、このコード変換回路411を、ノイズに敏感なアナログ回路から離して配置できる。

なお、ここでは、コード変換回路411が、出力バス170により伝送された計数コードをバイナリコードに変換する例を述べたが、コード変換回路411は、当該計数コードをバイナリコード以外の別のコードに変換してもよい。

以上より、本発明の第1の実施形態に係る固体撮像装置50は、カラムカウンタ142を構成要素としてもつカラムA/D変換回路140を備える。カラムカウンタ142は、直列に接続された、ハミング距離が1の複数のカウンタで構成されている。これにより、本発明の第1の実施形態に係る固体撮像装置50は、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる。

また、カラムカウンタ142は、アップカウントモードとダウンカウントモードとを有する。さらに、カラムカウンタ142は、アップカウントモードとダウンカウントモードとの切り替え時にその計数値を保持する機能を有する。これにより、本発明の第1の実施形態に係る固体撮像装置50は、A/D変換動作におけるカウント動作により発生するノイズをより低減できる。

(第1の実施形態の変化例)

図16は、第1の実施形態の変形例に係る固体撮像装置51の構成を示す図である。なお、図1と同様の要素には同一の符号を付しており、重複する説明は省略する。

図16は、第1の実施形態の変形例に係る固体撮像装置51の構成を示す図である。なお、図1と同様の要素には同一の符号を付しており、重複する説明は省略する。

図16に示す固体撮像装置51は、図1に示す固体撮像装置50に対して、カラムA/D変換回路140から画素信号に応じた計数値を読み出すための複数の出力バス171及び複数の出力回路161を備える点が異なる。

また、各カラムA/D変換回路140はそれぞれ1つの出力バス171に接続されている。出力バス171にはそれぞれに出力回路161が接続されている。各出力回路161は上述した出力回路160と同等の構成である。水平選択回路120は異なる出力バス171に接続される複数のカラムA/D変換回路140からそれぞれ1つずつを選択することにより、各出力バス171に並列にカラムA/D変換回路140のカラムカウンタ142に保持された計数コードを読み出す。そして、各出力バス171に接続されている出力回路161は、各々並列にカラムカウンタ142の計数コードをバイナリコードに変換し、変換したバイナリコードを並列に出力する。以上により、この固体撮像装置51は、カラムA/D変換回路140の変換結果を高速に読み出すことができる。

(第2の実施形態)

本発明の第2の実施形態では、上述した第1の実施形態に係る固体撮像装置50の変形例について説明する。

本発明の第2の実施形態では、上述した第1の実施形態に係る固体撮像装置50の変形例について説明する。

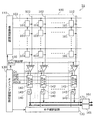

図17は、本発明の第2の実施形態に係る固体撮像装置52の構成を示す図である。なお、図1と同様の要素には同一の符号を付しており、重複する説明は省略する。また、図18は、本発明の第2の実施形態に係る固体撮像装置52の動作を示すタイミングチャートである。

図17に示す第2の実施形態に係る固体撮像装置52は、図1に示す固体撮像装置50に対して、タイミング制御回路230と、カラムA/D変換回路240との機能が異なる。

具体的には、タイミング制御回路230は、さらに、データ転送信号LATを生成する。

カラムA/D変換回路240は、さらに、デジタルメモリ244を備える。このデジタルメモリ244は、カラムカウンタ142が保持している計数コードをコピーし保持する。より詳細には、カラムカウンタ142の出力端子は、デジタルメモリ244に接続されている。このデジタルメモリ244は、タイミング制御回路230から供給されるデータ転送信号LATに応じて、各カラムカウンタ142の計数コードを取り込み保持する。また、デジタルメモリ244に保持された計数コードは、出力スイッチ143を介して、出力バス170に読み出される。

次に、本発明の実施形態に係る固体撮像装置52の動作を説明する。

なお、画素信号のA/D変換処理は、上述した第1の実施形態と同様なので、説明は省略する。

A/D変換処理の後、タイミング制御回路230より生成されたデータ転送信号LATに応じて、各カラムA/D変換回路240に含まれるデジタルメモリ244は、カラムカウンタ142が保持している計数値を取り込む。これにより、各デジタルメモリ244に、各デジタルメモリ244に対応するカラムカウンタ142の計数値がコピーされる。

次に、各デジタルメモリ244に保持された計数値は水平選択回路120により順次出力バス170に読み出される。そして、読み出された計数コードは出力回路160に入力される。出力回路160は、入力された計数コードをバイナリコードに変換し出力する。

また、図18のタイミングチャートに示すように、本発明の第2の実施形態ではカラムカウンタ142に保持されたA/D変換結果である計数値はデジタルメモリ244にコピーされているため、A/D変換結果の読み出し及びバイナリコードへの変換と並列して、次行の画素のA/D変換処理を行うことが可能である。これにより、本発明の第2の実施形態に係る固体撮像装置52は、読み出し時間の短縮つまりフレームレートの向上を実現できる。

なお、固体撮像装置52は、第1の実施形態の変形例と同様に出力バス170を複数備えてもよい。これにより、デジタルメモリ244に保持されたデータの読み出しレートを高速化できるので、フレームレートを向上できる。

(第3の実施形態)

本発明の第3の実施形態では、上述した第1又は第2の実施形態に係る固体撮像装置を複数の半導体チップで構成する場合の例を説明する。

本発明の第3の実施形態では、上述した第1又は第2の実施形態に係る固体撮像装置を複数の半導体チップで構成する場合の例を説明する。

図19は、本発明の第3の実施形態に係る固体撮像装置53を示す図である。本発明の第3の実施形態に係る固体撮像装置53は、半導体チップ710及び720を含む。

半導体チップ710には、画素アレイ100を含む画素部が形成されている。半導体チップ720には、カラムA/D変換回路アレイ721を含むA/D変換部が形成されている。ここで、画素アレイ100は、上述した第1又は第2の実施形態に係る固体撮像装置が備える画素アレイ100と同一のものである。また、カラムA/D変換回路アレイ721は、上述した上述した第1又は第2の実施形態に係る固体撮像装置が備える複数のカラムA/D変換回路140又は240を含む。

このように、画素部とA/D変換部とを別の半導体チップ710及び720上に形成することにより、画素部とA/D変換部とを異なる半導体製造プロセスを用いて形成できる。例えば、画素部を、CCDプロセスを用いて形成し、A/D変換部を、CMOSプロセスを用いて形成できる。言い換えると、本発明はCCDイメージセンサに適用することもできる。

以上のように第1〜第3の実施形態を用いて本発明を例示してきたが、本発明は上記の実施形態においてのみ解釈されるものではなく、特許請求の範囲によってのみその範囲が解釈されるべきである。

例えば、上記実施形態では画素リセット電位にダウンカウントを用いるとともに、画素信号電位にアップカウントを用いてA/D変換を行う例を示したが逆でもかまわない。

また、本発明は、上記第1〜第3の実施形態に係る固体撮像装置を備える撮像装置(カメラ)として実現してもよい。

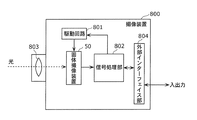

図20は、本発明に係る撮像装置800の構成を示すブロック図である。

図20に示す撮像装置800は、例えば、デジタルスチルカメラ又はデジタルビデオカメラ等であり、固体撮像装置50と、駆動回路801と、信号処理部802と、レンズ803と、外部インターフェイス部804とを備える。

固体撮像装置50は、上述した第1の実施形態に係る固体撮像装置50である。なお、撮像装置800は、当該固体撮像装置50の代わりに、上述した第2又は第3の実施形態に係る固体撮像装置を備えてもよい。

この固体撮像装置50は、レンズ803により集光された光を電気信号に変換することによりデジタル信号を生成する。

駆動回路801は、固体撮像装置50を駆動する。

信号処理部802は、駆動回路801を通して固体撮像装置50を制御するとともに、固体撮像装置50から出力されたデジタル信号に所定の処理を行う。また、信号処理部802は、処理した信号を、外部インターフェイス部804を通して外部に出力したり、撮像装置800が備える記憶部(図示せず)に記憶したりする。

以上の構成により、撮像装置800は、上述した固体撮像装置50を用いることで、回路規模の増大を抑えつつA/D変換時のカウンタ動作によるノイズの発生を低減できる。

また、上記説明では、本発明に係るカラムカウンタは、複数のジョンソンカウンタを直列に接続した構成であるとしたが、複数のグレイコードカウンタを直列にしてもよい。ここで、ジョンソンカウンタ及びグレイコードカウンタは、共に隣接する計数コードのハミング距離が1である。よって、グレイコードカウンタを用いた場合でも、上記と同様の効果を実現できる。また、2ビットのグレイコードカウンタと2ビットのジョンソンカウンタとは等価である。よって、2ビットのグレイコードカウンタは、上述した2ビットのジョンソンカウンタと同様の構成で実現できる。

また、上記説明では、カラムカウンタに含まれる複数のカウンタが全てジョンソンカウンタの場合を例に説明したが、当該複数のカウンタの一部のみがジョンソンカウンタであってもよい。同様に、当該複数のカウンタの一部のみがグレイコードカウンタであってもよい。

また、上記実施の形態に係る固体撮像装置及び撮像装置に含まれる各処理部は典型的には集積回路であるLSIとして実現される。これらは個別に1チップ化されてもよいし、一部又は全てを含むように1チップ化されてもよい。

また、集積回路化はLSIに限るものではなく、専用回路又は汎用プロセッサで実現してもよい。LSI製造後にプログラムすることが可能なFPGA(Field Programmable Gate Array)、又はLSI内部の回路セルの接続や設定を再構成可能なリコンフィギュラブル・プロセッサを利用してもよい。

また、上記実施の形態1〜3に係る、固体撮像装置、撮像装置及びそれらの変形例の機能のうち少なくとも一部を組み合わせてもよい。

また、上記で用いた数字は、全て本発明を具体的に説明するために例示するものであり、本発明は例示された数字に制限されない。さらに、ハイ/ローにより表される論理レベル又はオン/オフにより表されるスイッチング状態は、本発明を具体的に説明するために例示するものであり、例示された論理レベル又はスイッチング状態の異なる組み合わせにより、同等な結果を得ることも可能である。さらに、上で示した論理回路の構成は本発明を具体的に説明するために例示するものであり、異なる構成の論理回路により同等の入出力関係を実現することも可能である。

本発明は、固体撮像装置に適用できる。また、本発明は、固体撮像装置を用いる、デジタルスチルカメラ及びデジタルビデオカメラ等の撮像装置に適用できる。

10 固体撮像素子

11 画素アレイ部

12 行走査回路

13 列走査回路

14 タイミング制御回路

15 ADC群

15A ADC

16 DAC

17 データ出力回路

18 データ転送線

50、51、52、53 固体撮像装置

100 画素アレイ

101 画素

102 垂直信号線

103 制御信号線

110 垂直選択回路

111 単位画素

120 水平選択回路

130、230 タイミング制御回路

140、240 カラムA/D変換回路

141 比較器

142 カラムカウンタ

142A 4ビットカラムカウンタ

142B 5ビットカラムカウンタ

143 出力スイッチ

150 D/A変換回路

151 コンパレータ

152 カウンタ

154 スイッチ

160、161 出力回路

170、171 出力バス

244 デジタルメモリ

301 ジョンソンカウンタ

401、402、403 ジョンソンカウンタ

411 コード変換回路

412 出力バッファ

413 偶数ビットコード変換回路

501、502、503 フリップフロップ

504、505、506、507、508 マルチプレクサ

600A 4ビットリップルカウンタ

600B 5ビットリップルカウンタ

710、720 半導体チップ

721 カラムA/D変換回路アレイ

11 画素アレイ部

12 行走査回路

13 列走査回路

14 タイミング制御回路

15 ADC群

15A ADC

16 DAC

17 データ出力回路

18 データ転送線

50、51、52、53 固体撮像装置

100 画素アレイ

101 画素

102 垂直信号線

103 制御信号線

110 垂直選択回路

111 単位画素

120 水平選択回路

130、230 タイミング制御回路

140、240 カラムA/D変換回路

141 比較器

142 カラムカウンタ

142A 4ビットカラムカウンタ

142B 5ビットカラムカウンタ

143 出力スイッチ

150 D/A変換回路

151 コンパレータ

152 カウンタ

154 スイッチ

160、161 出力回路

170、171 出力バス

244 デジタルメモリ

301 ジョンソンカウンタ

401、402、403 ジョンソンカウンタ

411 コード変換回路

412 出力バッファ

413 偶数ビットコード変換回路

501、502、503 フリップフロップ

504、505、506、507、508 マルチプレクサ

600A 4ビットリップルカウンタ

600B 5ビットリップルカウンタ

710、720 半導体チップ

721 カラムA/D変換回路アレイ

Claims (15)

- 入射光を信号電荷に変換する受光部を有する複数の画素が行列状に配置された画素アレイと、

前記複数の画素から出力されるアナログ信号を並列にデジタル信号に変換する複数のカラムA/D変換回路と、

ランプ波を生成するランプ波発生回路と、

前記複数のカラムA/D変換回路及び前記ランプ波発生回路を制御するとともに、クロック信号を生成するタイミング制御回路と、

前記複数のカラムA/D変換回路で変換された前記デジタル信号を伝送する出力バスとを備え、

前記複数のカラムA/D変換回路の各々は、

前記アナログ信号と前記ランプ波との電位を比較し、比較した結果を示す比較結果信号を生成する比較器と、

前記クロック信号をカウントするとともに、前記比較結果信号が変化する時点での計数値を前記デジタル信号として保持するカラムカウンタとを有し、

前記カラムカウンタは、直列に接続された複数のカウンタを含み、

前記複数のカウンタの各々は、隣接する計数値を示す計数コードのハミング距離が1である

固体撮像装置。 - 前記複数のカウンタの一部又は全ては、ジョンソンカウンタであり、

前記複数のカウンタのうち最下位のカウンタのクロック入力端子には、前記クロック信号が供給され、

最下位以外の複数のカウンタのクロック入力端子には、前段のカウンタの最上位ビットの正転又は反転出力信号が供給される

請求項1記載の固体撮像装置。 - 前記複数のカウンタのうち最上位のカウンタが1ビットのカウンタであり、他のカウンタが2ビットのジョンソンカウンタである

請求項2記載の固体撮像装置。 - 前記複数のカウンタの全ては、2ビットのジョンソンカウンタである

請求項2記載の固体撮像装置。 - 前記複数のカウンタに含まれるn(nは2以上の整数)ビットのジョンソンカウンタは、アップカウントモードとダウンカウントモードとを切り替え可能であり、

前記nビットのジョンソンカウンタは、n個のフリップフロップと、選択部とを備え、

前記選択部は、

前記アップカウントモード時には、

前記n個のフリップフロップのうち、最下位ビットのフリップフロップのデータ入力端子を最上位ビットのフリップフロップの反転出力端子に接続し、

前記n個のフリップフロップのうち、前記最下位ビット以外のフリップフロップのデータ入力端子を、当該フリップフロップの前ビットのフリップフロップの正転出力端子に接続し、

前記ダウンカウントモード時には、

前記最上位ビットのフリップフロップのデータ入力端子を、前記最下位ビットのフリップフロップの反転出力端子に接続し、

前記n個のフリップフロップのうち、前記最上位以外のフリップフロップのデータ入力端子を、当該フリップフロップの次ビットのフリップフロップの正転出力端子に接続し、

前記最下位以外の複数のカウンタのクロック入力端子に、前段のカウンタの最上位ビットの正転出力信号を供給する

請求項2〜4のいずれか1項に記載の固体撮像装置。 - 前記カラムカウンタは、さらに、ホールドモードを有し、

前記選択部は、前記ホールドモード時には、前記n個のフリップフロップの各々のデータ入力端子を自身の正転出力端子に接続し、

前記タイミング制御回路は、前記カラムカウンタを前記アップカウントモード及び前記ダウンカウントモードの一方から他方へ切り替える際に、前記カラムカウンタをホールドモードにしたうえで、当該切り替えを行う

請求項5記載の固体撮像装置。 - 前記複数のカウンタの一部又は全ては、グレイコードカウンタであり、

前記複数のカウンタのうち最下位のカウンタのクロック入力端子には、前記クロック信号が供給され、

最下位以外のカウンタのクロック入力端子には、前段のカウンタの最上位ビットの正転又は反転出力信号が供給される

請求項1記載の固体撮像装置。 - 前記複数のカウンタのうち最上位のカウンタが1ビットのカウンタであり、他のカウンタが2ビットのグレイコードカウンタである

請求項7記載の固体撮像装置。 - 前記複数のカウンタの全ては、2ビットのグレイコードカウンタである

請求項7記載の固体撮像装置。 - 前記複数のカラムA/D変換回路の各々は、さらに、前記カラムカウンタの計数値を保持するデジタルメモリを備え、

前記デジタルメモリに保持されている計数値が前記出力バスに出力される

請求項1〜9のいずれか1項に記載の固体撮像装置。 - 前記固体撮像装置は、

前記出力バスを含み、前記複数のカラムA/D変換回路で変換された前記デジタル信号を伝送する複数の出力バスを備える

請求項1〜10のいずれか1項に記載の固体撮像装置。 - 前記固体撮像装置は、さらに、

前記出力バスにより伝送された前記計数コードを別の計数コードに変換するコード変換回路を備える

請求項1〜11のいずれか1項に記載の固体撮像装置。 - 前記コード変換回路は、前記出力バスにより伝送された前記計数コードをバイナリコードに変換する

請求項12記載の固体撮像装置。 - 前記画素アレイと、前記カラムA/D変換回路とは別チップに形成されている

請求項1〜13のいずれか1項に記載の固体撮像装置。 - 請求項1〜14のいずれか1項に記載の固体撮像装置を備える

撮像装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011008116A JP2012151613A (ja) | 2011-01-18 | 2011-01-18 | 固体撮像装置及び撮像装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011008116A JP2012151613A (ja) | 2011-01-18 | 2011-01-18 | 固体撮像装置及び撮像装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012151613A true JP2012151613A (ja) | 2012-08-09 |

Family

ID=46793464

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011008116A Pending JP2012151613A (ja) | 2011-01-18 | 2011-01-18 | 固体撮像装置及び撮像装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012151613A (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014125859A1 (ja) * | 2013-02-13 | 2014-08-21 | オリンパス株式会社 | 固体撮像装置 |

| JP2014179989A (ja) * | 2013-03-14 | 2014-09-25 | Taiwan Semiconductor Manufactuaring Co Ltd | センサーシステム及びセンサーに用いるデータアウト信号生成方法 |

| US9407846B2 (en) | 2013-12-16 | 2016-08-02 | Sony Corporation | Analog-to-digital conversion device |

| US9509925B2 (en) | 2014-02-25 | 2016-11-29 | Samsung Electronics Co., Ltd. | Device and method of transferring sensed data in image sensor |

| JPWO2016027729A1 (ja) * | 2014-08-20 | 2017-06-01 | ソニー株式会社 | 信号処理装置、撮像素子、並びに、電子機器 |

| CN110462436A (zh) * | 2017-03-29 | 2019-11-15 | 松下知识产权经营株式会社 | 固体摄像装置 |

| JP7408981B2 (ja) | 2019-09-30 | 2024-01-09 | セイコーエプソン株式会社 | 状態遷移器、時間デジタル変換器及びa/d変換回路 |

-

2011

- 2011-01-18 JP JP2011008116A patent/JP2012151613A/ja active Pending

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014125859A1 (ja) * | 2013-02-13 | 2014-08-21 | オリンパス株式会社 | 固体撮像装置 |

| JP2014155156A (ja) * | 2013-02-13 | 2014-08-25 | Olympus Corp | 固体撮像装置 |

| US9609257B2 (en) | 2013-02-13 | 2017-03-28 | Olympus Corporation | Solid-state imaging device |

| JP2014179989A (ja) * | 2013-03-14 | 2014-09-25 | Taiwan Semiconductor Manufactuaring Co Ltd | センサーシステム及びセンサーに用いるデータアウト信号生成方法 |

| US9325923B2 (en) | 2013-03-14 | 2016-04-26 | Taiwan Semiconductor Manufacturing Co., Ltd. | Systems and methods to mitigate transient current for sensors |

| US9407846B2 (en) | 2013-12-16 | 2016-08-02 | Sony Corporation | Analog-to-digital conversion device |

| US9509925B2 (en) | 2014-02-25 | 2016-11-29 | Samsung Electronics Co., Ltd. | Device and method of transferring sensed data in image sensor |

| JPWO2016027729A1 (ja) * | 2014-08-20 | 2017-06-01 | ソニー株式会社 | 信号処理装置、撮像素子、並びに、電子機器 |

| CN110462436A (zh) * | 2017-03-29 | 2019-11-15 | 松下知识产权经营株式会社 | 固体摄像装置 |

| JP7408981B2 (ja) | 2019-09-30 | 2024-01-09 | セイコーエプソン株式会社 | 状態遷移器、時間デジタル変換器及びa/d変換回路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7522082B2 (en) | Digital-to-analog converter, analog-to-digital converter, and semiconductor device | |

| US8130295B2 (en) | Analog-to-digital converter, solid-state image pickup device, and camera system | |

| JP5359521B2 (ja) | バイナリ値変換回路およびその方法、ad変換装置、固体撮像素子、並びにカメラシステム | |

| JP4289206B2 (ja) | カウンタ回路 | |

| US9019142B2 (en) | Solid-state imaging device, imaging system, and method for driving solid-state imaging device | |

| JP2012151613A (ja) | 固体撮像装置及び撮像装置 | |

| KR101834021B1 (ko) | A/d 변환기, a/d 변환 방법, 고체 촬상 소자 및 카메라 시스템 | |

| WO2013175959A1 (ja) | A/d変換器、固体撮像装置および電子機器 | |

| US9871986B2 (en) | Counter, counting method, ad converter, solid-state imaging device, and electronic device | |

| JP5806539B2 (ja) | 固体撮像装置 | |

| US11115611B2 (en) | Solid-state imaging device and imaging system | |

| JP2013012966A (ja) | 撮像装置 | |

| JP6523733B2 (ja) | バイナリ値変換回路及びその方法、ad変換器並びに固体撮像装置 | |

| US9338384B2 (en) | Solid-state imaging apparatus including electrically connected substrates | |

| US9160318B2 (en) | Data processing circuit and solid-state imaging device | |

| US8669898B2 (en) | Ramp wave generation circuit and solid-state imaging device | |

| US8907835B2 (en) | A/D conversion circuit and solid-state image pickup device | |

| JP2011259016A (ja) | 固体撮像素子及び撮像装置 |