JP2012123797A - 統合発火型電子ニューロン、方法およびプログラム - Google Patents

統合発火型電子ニューロン、方法およびプログラム Download PDFInfo

- Publication number

- JP2012123797A JP2012123797A JP2011260006A JP2011260006A JP2012123797A JP 2012123797 A JP2012123797 A JP 2012123797A JP 2011260006 A JP2011260006 A JP 2011260006A JP 2011260006 A JP2011260006 A JP 2011260006A JP 2012123797 A JP2012123797 A JP 2012123797A

- Authority

- JP

- Japan

- Prior art keywords

- membrane potential

- neuron

- inhibitory

- spike

- response

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

- G06N3/049—Temporal neural networks, e.g. delay elements, oscillating neurons or pulsed inputs

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Health & Medical Sciences (AREA)

- Computing Systems (AREA)

- Biomedical Technology (AREA)

- Biophysics (AREA)

- Computational Linguistics (AREA)

- Data Mining & Analysis (AREA)

- Evolutionary Computation (AREA)

- Life Sciences & Earth Sciences (AREA)

- Molecular Biology (AREA)

- Artificial Intelligence (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Software Systems (AREA)

- Health & Medical Sciences (AREA)

- Semiconductor Memories (AREA)

- Feedback Control In General (AREA)

- Measurement And Recording Of Electrical Phenomena And Electrical Characteristics Of The Living Body (AREA)

Abstract

【解決手段】 外部スパイク信号の受信に応じて、外部スパイク信号に基づいて電子ニューロンのデジタル膜電位が更新される。膜電位は漏れ率に基づいて減衰される。膜電位がしきい値を超えたことに応じて、スパイク信号が生成される。

【選択図】 図5

Description

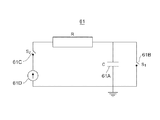

本発明の第1の実装例は、図5のブロック図例によって示されているように、線形漏れ統合発火型(LL−IF)電子ニューロン80を含む。LL−IFニューロン80によって受信された各興奮性スパイクについて、入力積分器モジュール81は一定の量s+だけニューロンの膜電位Vを増加し、ニューロンが受信する各抑制性スパイクについて、入力積分器モジュール81は一定の量s-だけVを減少させる。ニューロン膜漏れは、漏出器(leaker)モジュール82を使用して各時間ステップ内でλだけVを線形に減少させることによってシミュレートされる。1つのデジタル・クロック信号は複数の時間ステップを提供する。比較器モジュール83により、ニューロン80への入力がしきい値θより上にVを増加する場合、スパイクが生成され、Vがリセット値Vresetに設定される。

V(t)=V(t−1)−λ+s+n+−s-n-

ここで、s+は+s+n+がn+のビットシフト加算になるような2の累乗である。さらに、s-は−s-n-がn-のビットシフト減算になるような2の累乗である。

V(t)>θである場合、V(t)=Vresetを設定し、スパイクを放出する。

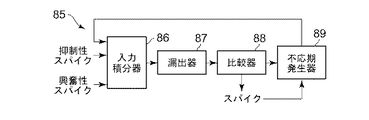

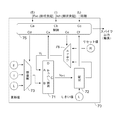

本発明の第2の実装例は、図6のブロック図例によって示されているように、不応期付き凸状減衰近似統合発火型(CD−IF w/RP)電子ニューロン85を含む。CD−IF w/RP電子ニューロン85は不応期を有し、ニューロンが受信する各興奮性スパイクについて、入力積分器86は一定の量s+だけ膜電位Vを増加し、ニューロンが受信する各抑制性スパイクについて、入力積分器86は一定の量s-だけVを減少させる。ニューロン膜漏れは、漏出器モジュール87が各時間ステップ内で時定数τに応じてVを減衰することによってシミュレートされる(したがって、静止膜電位が0であると想定する)。比較器モジュール88により、ニューロンへの入力がしきい値θより上にVを増加する場合、ニューロンはスパイクを生成し、VがVresetに設定される。ニューロンがスパイクを生成すると、不応期発生器モジュール89がρ時間ステップの間、VをVresetに保持することによって不応期がシミュレートされる。

r(t)>0である場合、r(t)=r(t−1)−1であり、Vを更新せず、

さもなければ、

に応じてVを更新する。

ここで、s+は+s+n+がn+のビットシフト加算になるような2の累乗である。さらに、s-は−s-n-がn-のビットシフト減算になるような2の累乗である。さらに、τは−V(t−1)/τがV(t−1)のビットシフト減算になるような2の累乗である。

V(t)>θである場合、r(t)=ρを設定し、スパイクを放出する。

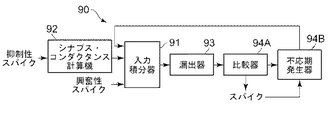

本発明の第3の実装例は、図7のブロック図例によって示されているように、不応期およびコンダクタンスベースの抑制付き凸状減衰近似統合発火型(CD−IF w/RP&CB−I)電子ニューロン90を含む。CD−IF w/RP&CB−Iニューロン90が受信する各興奮性スパイクについて、入力積分器モジュール91は一定の量s+だけ膜電位Vを増加し、入力積分器モジュール91によって受信された各抑制性スパイクについて、入力積分器モジュール91は一定の量s-だけ抑制性チャネル・コンダクタンスgを増加する。シナプス・コンダクタンス計算器モジュール92は各時間ステップで抑制性チャネル・コンダクタンス減衰を提供し、率は時定数τgによって支配される。次に、以下のように膜電位Vを減少させることにより、各時間ステップで入力積分器モジュール91によって抑制が膜電位に統合される。

ここで、gscaleはgの倍率である(これは0という抑制性逆転電位を想定している)。膜漏れは、漏出器モジュール93が各時間ステップ内で時定数τに応じてVを減衰することによってシミュレートされる(したがって、静止膜電位が0であると想定する)。比較器モジュール94Aにより、ニューロンへの入力がしきい値θより上にVを増加する場合、ニューロンはスパイクを生成し、VがVresetに設定される。不応期発生器モジュール94Bにより、ニューロンがスパイクを生成すると、ρ時間ステップの間、VをVresetに保持することによって不応期がシミュレートされる。

ここで、τgは2の累乗であり、−g(t−1)/τgはg(t−1)のビットシフト減算であり、s-は2の累乗であり、−s-n-はn-のビットシフト減算である。

さもなければ、

に応じてVを更新する。

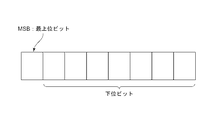

ここで、k=gscale−floor(log2(g(t)))であり、floor(log2(x))はx内の最上位非ゼロ・ビットの位置であり、kは整数であり、(V(t−1)/2k)はV(t−1)のビットシフト・バージョンである。さらに、s+は+s+n+がn+のビットシフト加算になるような2の累乗である。さらに、τは−V(t−1)/τがV(t−1)のビットシフト減算になるような2の累乗である。

V(t)>θである場合、r(t)=ρを設定し、スパイクを放出する。

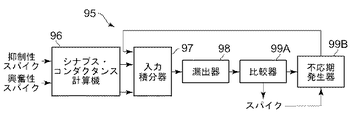

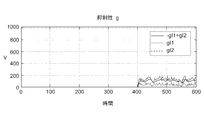

本発明の第4の実装例は、図8のブロック図例によって示されているように、不応期およびコンダクタンスベースのシナプス付き凸状減衰近似統合発火型(CD−IF w/RP&CB−S)電子ニューロン95を含む。シナプス・チャネル・コンダクタンスは指数コンダクタンス変数g1およびg2の差としてモデル化され、これらの変数はニューロンへの各入力によって強度係数sだけ増加する。次に、シナプス・コンダクタンス計算器モジュール96により、コンダクタンス変数は各時間ステップで減衰し、率は時定数τgによって支配される。各時間ステップにおいて、入力積分器モジュール97が以下のようにシナプス電流を使用することにより、ニューロン膜電位Vが変更される。

ここで、gscaleはgの倍率であり、Erevはチャネル逆転電位であって、抑制性チャネルの場合は0になり、興奮性チャネルの場合は210+2EEshiftになるように想定されている。膜漏れは、漏出器モジュール98が各時間ステップ内で時定数τに応じてVを減衰することによってシミュレートされる(したがって、静止膜電位が0であると想定する)。比較器モジュール99Aにより、ニューロン95への入力がしきい値θより上にVを増加する場合、ニューロンはスパイクを生成し、VがVresetに設定される。不応期発生器99Bにより、ニューロンがスパイクを生成すると、ρ時間ステップの間、VをVresetに保持することによって不応期がシミュレートされる。

に応じてgI1を更新する。

に応じてgI2を更新する。

に応じてgE1を更新する。

に応じてgE2を更新する。

ここで、τgは2の累乗であり、−g(t−1)/τgはg(t−1)のビットシフト減算であり、s-は2の累乗であり、−s-n-はn-のビットシフト減算であり、s+は2の累乗であり、+s+n+はn+のビットシフト加算である。

さもなければ、

に応じてVを更新する。

ここで、kI=gIscale−floor(log2(gI1−gI2))であり、kE=gEscale−floor(log2(gE1−gE2))であり、kは整数であり、x/2kはxのビットシフト・バージョンであり、floor(log2(x))はx内の最上位非ゼロ・ビットの位置であり、210−VはVのビット単位の補数であり、210−V+EEShiftは210−Vのビットシフト・バージョンである。さらに、τは−V(t−1)/τがV(t−1)のビットシフト減算になるような2の累乗である。

V(t)>θである場合、r(t)=ρを設定し、スパイクを放出する。

これは、上記の第2および第3の実装例に関するものであり、伝統的な統合発火型(IF)ニューロン・モデルで使用される膜電圧の指数関数的減衰に対する凸状近似を提供し、したがって、以下の対応する膜更新規則に比較してより高度の生物学的リアリズムが得られる。

V(t)=V(t−1)−λ+s+n+−s-n-

これは、本発明の第1の実施形態に関するものであり、時間の経過につれて膜電圧が一定の直線傾斜下降することを使用する。

更新規則:

V=V−Kλ+s+n+−s-n-に応じてVを更新する。

s+は2の累乗であるので、+s+n+はn+のビットシフト加算である。

s-は2の累乗であるので、−s-n-はn-のビットシフト減算である。

スパイク条件:

V(t)>θである場合、

V(t)=Vresetを設定し、スパイクを放出する。

状態カウンタのMSBが1である場合、

状態カウンタのMSBがゼロに設定される。

さもなければ

すべての下位ビットがゼロに設定される。

終了。

容量61Aはスイッチ61Bを介して急速に放電され、電流源61Dからスイッチ61Cを介してもう一度充電を開始する。

状態カウンタ62のMSBが1である場合、

状態カウンタのMSBがゼロに設定される。

さもなければ

すべての下位ビットがゼロに設定される。

終了。

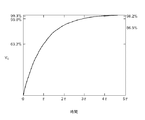

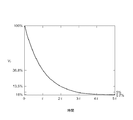

ステップ1:容量Cは開始値からゆっくり充電する(図16)。スパイク・イベントが発生したばかりである場合、開始値はゼロであり、そうではない場合、開始値は、容量Cがすでに備えている電荷である。容量Cが第1のしきい値(たとえば、その完全充電の86.5%)に到達すると、減衰イベントが発生し、以下の動作が実行される。

状態カウンタ62(図13)のMSBが1である場合、

状態カウンタ62のMSBがゼロに設定される。

さもなければ

状態カウンタ62のすべての下位ビットがゼロに設定される。

終了。

ステップ2に移行する。

ステップ2:次に容量Cは、それがすでに備えている電荷から始めて、図17に示されているようにゆっくり放電する。容量Cが第2のしきい値(たとえば、その完全充電の約13.5%または14.5%)に到達すると、減衰イベントが発生し、以下の動作が実行される。

状態カウンタ62(図13)のMSBが1である場合、

状態カウンタ62のMSBがゼロに設定される。

さもなければ

状態カウンタ62のすべての下位ビットがゼロに設定される。

終了。

ステップ1に移行する。ステップ1の充電はこの時点では空の容量からではなく、容量がすでに備えている電荷から始めることになる。

第1のしきい値+第2のしきい値=100%

81 入力積分器

82 漏出器

83 比較器

Claims (26)

- 統合発火型電子ニューロンの外部スパイク信号に応じて、前記外部スパイク信号に基づいてニューロン膜電位を表すデジタル膜電位を更新するステップと、

漏れ率に基づいて前記デジタル膜電位を減衰するステップと、

前記デジタル膜電位がしきい値を超えたことに応じて、スパイク信号を生成するステップと、

を含む、方法。 - 前記膜電位を更新するステップが、

外部興奮性スパイク信号の受信に応じて、1の時間ステップで受信した興奮性スパイク信号の数に第1のスケーリング・パラメータを掛けたものに等しい増加分だけ前記膜電位を増加するステップと、

外部抑制性スパイク信号の受信に応じて、1の時間ステップで受信した抑制性スパイク信号の数に第2のスケーリング・パラメータを掛けたものに等しい減少分だけ前記膜電位を減少させるステップと、

を含む、請求項1記載の方法。 - 前記第1のスケーリング・パラメータが2の倍数であり、前記受信した興奮性スパイクの数に前記倍率を掛けることがデジタル・ビットシフト操作によって行われる、請求項2記載の方法。

- 前記第2のスケーリング・パラメータが2の倍数であり、前記受信した抑制性スパイクの数に前記倍率を掛けることがデジタル・ビットシフト操作によって行われる、請求項2記載の方法。

- 前記膜電位を減衰するステップが、前記膜電位の現在値を時定数で割ったものに等しい漏れ率に基づいて前記膜電位を減衰するステップを含む、請求項4記載の方法。

- 前記時定数が2の倍数であり、前記膜電位を前記時定数値で割ることがデジタル・ビットシフト操作によって行われる、請求項5記載の方法。

- 前記膜電位を更新するステップが、抑制性スパイク信号の受信に応じて、抑制性チャネル・コンダクタンス値を増加するステップを含む、請求項4記載の方法。

- 前記抑制性チャネル・コンダクタンス値の現在値を時定数で割ったものに等しい漏れ率に基づいて前記抑制性チャネル・コンダクタンス値を減衰するステップであって、前記時定数が2の倍数であり、前記抑制性チャネル・コンダクタンス値を前記時定数値で割ることがビットシフト操作によって行われる、ステップと、

前記抑制性チャネル・コンダクタンス値に基づいて前記膜電位を減少させることにより前記膜電位に抑制を適用するステップと、

をさらに含む、請求項7記載の方法。 - 前記膜電位に抑制を適用するステップが、前記膜電位から前記膜電位値の現在値を除数値で割ったものを引くステップを含み、前記除数値が倍率から前記抑制性チャネル・コンダクタンス値内の最上位非ゼロ・ビットを引いたものに等しい冪指数だけ2を累乗したものを含む、請求項8記載の方法。

- 各外部スパイク信号によって強度係数だけ増加する2つの抑制性チャネル・コンダクタンス変数の差として前記電子ニューロン内のシナプス・チャネル・コンダクタンスをモデル化するステップと、

時定数によって支配される減衰率に基づいて前記コンダクタンス変数を減衰するステップであって、前記時定数が2の倍数であり、前記減衰がデジタル・ビットシフト操作によって行われる、ステップと、

をさらに含む、請求項4記載の方法。 - 前記膜電位から前記膜電位の現在値を除数値で割ったものを引くことにより前記膜電位に抑制を適用するステップであって、前記除数値が倍率から前記抑制性チャネル・コンダクタンス変数の前記差の値内の最上位非ゼロ・ビットを引いたものに等しい冪指数だけ2を累乗したものである、ステップと、

合計を生成するためにビットシフト操作を使用して膜電位補数値を興奮性強度シフト係数に加えることにより前記膜電位に興奮を適用し、倍率から前記興奮性チャネル・コンダクタンス変数の前記差の値内の最上位非ゼロ・ビットを引いたものに等しい冪指数だけ2を累乗したものである除数で前記合計を割るステップと、

をさらに含む、請求項10記載の方法。 - 統合発火型電子ニューロンの膜電位を表すデジタル・カウンタと、

外部スパイク信号に基づいて前記膜電位を更新するために構成されたコントローラであって、

外部興奮性スパイク信号の受信に応じて、変更する必要がある前記カウンタ内のビットのみが変更されるようなビット単位の操作を使用して増加分だけ前記膜電位を増分すること、

外部抑制性スパイク信号の受信に応じて、変更する必要がある前記カウンタ内のビットのみが変更されるようなビット単位の操作を使用して減少分だけ前記膜電位を減分すること、

によって前記膜電位を更新するためのコントローラと、

アナログ抵抗−容量・モデルを使用して時定数に基づいて前記膜電位を減衰するために構成された減衰モジュールと、

前記膜電位がしきい値を超えたことに応じて、スパイク信号を生成するために構成されたスパイク・モジュールと、

を含む、統合発火型電子ニューロン。 - 前記減衰モジュールが、アナログ抵抗−容量モデルを使用して時定数に基づいて減衰イベントを発生することにより前記膜電位を減衰するために構成される、請求項12記載の統合発火型電子ニューロン。

- 減衰イベントの発生に応じて、前記カウンタの最上位ビットが1である場合に前記カウンタの前記最上位ビットがゼロに設定され、そうではない場合に前記カウンタのすべての下位ビットがゼロに設定される、請求項13記載の統合発火型電子ニューロン。

- 前記ニューロンがスパイク信号を生成すると、前記容量が急速に放電され、ある充電率で充電され、前記充電がしきい値への到達に応じて、減衰イベントが発生される、請求項14記載の統合発火型電子ニューロン。

- 前記ニューロンがスパイク信号を生成すると、前記容量が急速に放電され、ある充電率で充電され、前記充電が第1のしきい値への到達に応じて、減衰イベントが発生され、

前記容量がある率で放電され、前記充電が第2のしきい値への到達に応じて、減衰イベントが発生される、請求項14記載の統合発火型電子ニューロン。 - 前記抵抗−容量・モデルが2つの容量を含み、

前記膜の前記電位が、

前記ニューロンが第1のスパイク信号を生成したときに、第2の容量に切り替わりながら第1の容量を急速に放電することと、

前記ニューロンが第2のスパイク信号を生成したときに、前記第1の容量に切り替わりながら前記第2の容量を急速に放電すること

によって減衰される、請求項13記載の統合発火型電子ニューロン。 - イベント・ドリブン統合発火型電子ニューロン内で外部スパイク信号を受信したことに応じて、前記外部スパイク信号に基づいて電子ニューロンのデジタル膜電位を更新するステップと、

漏れ率に基づいて前記膜電位を減衰するステップと、

前記膜電位がしきい値を超えたことに応じて、スパイク信号を生成するステップを含み、

前記膜電位を更新するステップが、興奮性イベント・タイプの発生に応じて、興奮性シナプス強度増加分だけ前記膜電位を増分するステップをさらに含む、方法。 - 前記膜電位を更新するステップが、抑制性イベント・タイプの発生に応じて、抑制性シナプス強度減少分だけ前記膜電位を減分するステップをさらに含む、請求項18記載の方法。

- 前記膜電位を更新するステップが、減衰イベント・タイプの発生に応じて、漏れ強度減少分だけ前記膜電位を減分するステップをさらに含む、請求項19記載の方法。

- スパイク信号を生成するステップが、前記膜電位をリセット値に設定するステップをさらに含む、請求項20記載の方法。

- 減衰イベントの発生に応じて、前記膜電位がしきい値より上である場合に前記ニューロンがスパイク・イベントを送信し、シミュレーションとハードウェアとの対応を維持する、請求項18記載の方法。

- デジタル膜電位カウンタと、

統合発火型電子ニューロン内の外部スパイク信号に応じて、前記外部スパイク信号に基づいてデジタル膜電位を更新するために構成されたコントローラ・モジュールであって、前記デジタル膜電位がニューロン膜電位を表す、コントローラ・モジュールと、

漏れ率に基づいて前記デジタル膜電位を減衰するために構成された減衰モジュールと、

前記デジタル膜電位がしきい値を超えたことに応じて、スパイク信号を生成するために構成されたスパイク・モジュールと、

を含む、統合発火型電子ニューロン。 - 前記コントローラ・モジュールが、

外部興奮性スパイク信号の受信に応じて、1つの時間ステップで受信した興奮性スパイク信号の数に第1のスケーリング・パラメータを掛けたものに等しい増加分だけ前記膜電位を増加することと、

外部抑制性スパイク信号の受信に応じて、1つの時間ステップで受信した抑制性スパイク信号の数に第2のスケーリング・パラメータを掛けたものに等しい減少分だけ前記膜電位を減少させること

によって前記膜電位を更新するためにさらに構成される、請求項23記載の統合発火型電子ニューロン。 - 前記第1のスケーリング・パラメータが2の倍数であり、前記受信した興奮性スパイクの数に前記倍率を掛けることがデジタル・ビットシフト操作によって行われるようになっており、

前記第2のスケーリング・パラメータが2の倍数であり、前記受信した抑制性スパイクの数に前記倍率を掛けることがデジタル・ビットシフト操作によって行われるようになっている、請求項24記載の統合発火型電子ニューロン。 - 請求項1〜11、18〜22のいずれかに記載の方法の各ステップを実行させるプログラム・コードを含む、プログラム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/963558 | 2010-12-08 | ||

| US12/963,558 US8473439B2 (en) | 2010-12-08 | 2010-12-08 | Integrate and fire electronic neurons |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012123797A true JP2012123797A (ja) | 2012-06-28 |

| JP2012123797A5 JP2012123797A5 (ja) | 2014-08-14 |

| JP5623372B2 JP5623372B2 (ja) | 2014-11-12 |

Family

ID=46200367

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011260006A Active JP5623372B2 (ja) | 2010-12-08 | 2011-11-29 | 統合発火型電子ニューロン、方法およびプログラム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8473439B2 (ja) |

| JP (1) | JP5623372B2 (ja) |

| CN (1) | CN102567784B (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017529592A (ja) * | 2014-08-08 | 2017-10-05 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | 非同期パルス変調を用いた人工ニューロンおよびスパイキングニューロン |

| JP2021527910A (ja) * | 2018-06-06 | 2021-10-14 | マイクロン テクノロジー,インク. | メモリデバイスを使用するウエイトストイレージ |

Families Citing this family (73)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9269042B2 (en) | 2010-09-30 | 2016-02-23 | International Business Machines Corporation | Producing spike-timing dependent plasticity in a neuromorphic network utilizing phase change synaptic devices |

| US20120084240A1 (en) * | 2010-09-30 | 2012-04-05 | International Business Machines Corporation | Phase change memory synaptronic circuit for spiking computation, association and recall |

| US9015093B1 (en) | 2010-10-26 | 2015-04-21 | Michael Lamport Commons | Intelligent control with hierarchical stacked neural networks |

| US8775341B1 (en) | 2010-10-26 | 2014-07-08 | Michael Lamport Commons | Intelligent control with hierarchical stacked neural networks |

| US8812414B2 (en) | 2011-05-31 | 2014-08-19 | International Business Machines Corporation | Low-power event-driven neural computing architecture in neural networks |

| US9566710B2 (en) | 2011-06-02 | 2017-02-14 | Brain Corporation | Apparatus and methods for operating robotic devices using selective state space training |

| US9053428B2 (en) | 2011-07-21 | 2015-06-09 | Qualcomm Incorporated | Method and apparatus of robust neural temporal coding, learning and cell recruitments for memory using oscillation |

| US8843425B2 (en) * | 2011-07-29 | 2014-09-23 | International Business Machines Corporation | Hierarchical routing for two-way information flow and structural plasticity in neural networks |

| US9147155B2 (en) | 2011-08-16 | 2015-09-29 | Qualcomm Incorporated | Method and apparatus for neural temporal coding, learning and recognition |

| US8909576B2 (en) | 2011-09-16 | 2014-12-09 | International Business Machines Corporation | Neuromorphic event-driven neural computing architecture in a scalable neural network |

| US9092735B2 (en) | 2011-09-21 | 2015-07-28 | Qualcomm Incorporated | Method and apparatus for structural delay plasticity in spiking neural networks |

| US9111224B2 (en) * | 2011-10-19 | 2015-08-18 | Qualcomm Incorporated | Method and apparatus for neural learning of natural multi-spike trains in spiking neural networks |

| US8909575B2 (en) | 2012-02-29 | 2014-12-09 | Qualcomm Incorporated | Method and apparatus for modeling neural resource based synaptic placticity |

| US8959040B1 (en) * | 2012-03-08 | 2015-02-17 | Hrl Laboratories, Llc | Spike timing dependent plasticity apparatus, system and method |

| US8990137B2 (en) * | 2012-03-29 | 2015-03-24 | Rhode Island Board Of Education, State Of Rhode Island And Providence Plantations | Apparatus for memristor/neuron emulation and testing |

| US8832009B2 (en) * | 2012-05-15 | 2014-09-09 | The United States Of America As Represented By The Secretary Of The Air Force | Electronic charge sharing CMOS-memristor neural circuit |

| US9064215B2 (en) | 2012-06-14 | 2015-06-23 | Qualcomm Incorporated | Learning spike timing precision |

| US8924322B2 (en) * | 2012-06-15 | 2014-12-30 | International Business Machines Corporation | Multi-processor cortical simulations with reciprocal connections with shared weights |

| EP2877958B1 (en) * | 2012-07-25 | 2019-09-04 | HRL Laboratories, LLC | Neuron circuit and method |

| US9141906B2 (en) * | 2013-03-13 | 2015-09-22 | Google Inc. | Scoring concept terms using a deep network |

| US9764468B2 (en) | 2013-03-15 | 2017-09-19 | Brain Corporation | Adaptive predictor apparatus and methods |

| US9242372B2 (en) | 2013-05-31 | 2016-01-26 | Brain Corporation | Adaptive robotic interface apparatus and methods |

| CN104240753B (zh) * | 2013-06-10 | 2018-08-28 | 三星电子株式会社 | 突触阵列、脉冲整形电路和神经形态系统 |

| US9418333B2 (en) | 2013-06-10 | 2016-08-16 | Samsung Electronics Co., Ltd. | Synapse array, pulse shaper circuit and neuromorphic system |

| US9314924B1 (en) | 2013-06-14 | 2016-04-19 | Brain Corporation | Predictive robotic controller apparatus and methods |

| US9792546B2 (en) | 2013-06-14 | 2017-10-17 | Brain Corporation | Hierarchical robotic controller apparatus and methods |

| US9384443B2 (en) | 2013-06-14 | 2016-07-05 | Brain Corporation | Robotic training apparatus and methods |

| US9436909B2 (en) | 2013-06-19 | 2016-09-06 | Brain Corporation | Increased dynamic range artificial neuron network apparatus and methods |

| US9558443B2 (en) | 2013-08-02 | 2017-01-31 | International Business Machines Corporation | Dual deterministic and stochastic neurosynaptic core circuit |

| US9449270B2 (en) | 2013-09-13 | 2016-09-20 | Qualcomm Incorporated | Implementing structural plasticity in an artificial nervous system |

| US9296101B2 (en) | 2013-09-27 | 2016-03-29 | Brain Corporation | Robotic control arbitration apparatus and methods |

| US9579789B2 (en) | 2013-09-27 | 2017-02-28 | Brain Corporation | Apparatus and methods for training of robotic control arbitration |

| US9305256B2 (en) * | 2013-10-02 | 2016-04-05 | Qualcomm Incorporated | Automated method for modifying neural dynamics |

| US9924490B2 (en) * | 2013-10-09 | 2018-03-20 | International Business Machines Corporation | Scaling multi-core neurosynaptic networks across chip boundaries |

| US11501143B2 (en) | 2013-10-11 | 2022-11-15 | Hrl Laboratories, Llc | Scalable integrated circuit with synaptic electronics and CMOS integrated memristors |

| US9597797B2 (en) | 2013-11-01 | 2017-03-21 | Brain Corporation | Apparatus and methods for haptic training of robots |

| US9463571B2 (en) | 2013-11-01 | 2016-10-11 | Brian Corporation | Apparatus and methods for online training of robots |

| US9248569B2 (en) | 2013-11-22 | 2016-02-02 | Brain Corporation | Discrepancy detection apparatus and methods for machine learning |

| US9358685B2 (en) | 2014-02-03 | 2016-06-07 | Brain Corporation | Apparatus and methods for control of robot actions based on corrective user inputs |

| US9346167B2 (en) | 2014-04-29 | 2016-05-24 | Brain Corporation | Trainable convolutional network apparatus and methods for operating a robotic vehicle |

| US9195903B2 (en) * | 2014-04-29 | 2015-11-24 | International Business Machines Corporation | Extracting salient features from video using a neurosynaptic system |

| US9373058B2 (en) | 2014-05-29 | 2016-06-21 | International Business Machines Corporation | Scene understanding using a neurosynaptic system |

| US10115054B2 (en) | 2014-07-02 | 2018-10-30 | International Business Machines Corporation | Classifying features using a neurosynaptic system |

| US9630318B2 (en) | 2014-10-02 | 2017-04-25 | Brain Corporation | Feature detection apparatus and methods for training of robotic navigation |

| CN105629148B (zh) | 2014-10-28 | 2018-08-28 | 国际商业机器公司 | 测试电路中的多个模块的测试方法和测试设备 |

| US10489705B2 (en) | 2015-01-30 | 2019-11-26 | International Business Machines Corporation | Discovering and using informative looping signals in a pulsed neural network having temporal encoders |

| US9717387B1 (en) | 2015-02-26 | 2017-08-01 | Brain Corporation | Apparatus and methods for programming and training of robotic household appliances |

| US20160335534A1 (en) * | 2015-05-14 | 2016-11-17 | Thalchemy Corporation | Neural sensor hub system |

| US10318861B2 (en) * | 2015-06-17 | 2019-06-11 | International Business Machines Corporation | Artificial neuron apparatus |

| KR102565273B1 (ko) | 2016-01-26 | 2023-08-09 | 삼성전자주식회사 | 뉴럴 네트워크에 기초한 인식 장치 및 뉴럴 네트워크의 학습 방법 |

| CN109196528B (zh) * | 2016-05-17 | 2022-03-18 | 硅存储技术公司 | 使用非易失性存储器阵列的深入学习神经网络分类器 |

| KR102182583B1 (ko) | 2016-05-17 | 2020-11-24 | 실리콘 스토리지 테크놀로지 인크 | 비휘발성 메모리 어레이를 사용하는 딥러닝 신경망 분류기 |

| US10147035B2 (en) | 2016-06-30 | 2018-12-04 | Hrl Laboratories, Llc | Neural integrated circuit with biological behaviors |

| US10423878B2 (en) * | 2016-09-07 | 2019-09-24 | International Business Machines Corporation | Artificial neuron apparatus |

| US11551074B2 (en) * | 2017-01-20 | 2023-01-10 | Tsinghua University | Self-adaptive threshold neuron information processing method, self-adaptive leakage value neuron information processing method, system computer device and readable storage medium |

| US10339444B2 (en) * | 2017-01-20 | 2019-07-02 | International Business Machines Corporation | Monitoring potential of neuron circuits |

| FR3064384B1 (fr) * | 2017-03-23 | 2019-05-03 | Stmicroelectronics Sa | Bloc refractaire pour dispositif integre de neurone artificiel |

| FR3064383B1 (fr) | 2017-03-23 | 2019-11-15 | Stmicroelectronics Sa | Dispositif integre de neurone artificiel |

| KR20180111156A (ko) * | 2017-03-31 | 2018-10-11 | 에스케이하이닉스 주식회사 | 피드-백 라인을 가진 포스트-시냅틱 뉴런을 포함하는 뉴로모픽 소자 및 뉴로모픽 소자의 동작 방법 |

| US11301753B2 (en) * | 2017-11-06 | 2022-04-12 | Samsung Electronics Co., Ltd. | Neuron circuit, system, and method with synapse weight learning |

| US10699779B2 (en) | 2017-11-29 | 2020-06-30 | Silicon Storage Technology, Inc. | Neural network classifier using array of two-gate non-volatile memory cells |

| FR3083896B1 (fr) * | 2018-07-12 | 2021-01-08 | Commissariat Energie Atomique | Circuit neuromorphique impulsionnel implementant un neurone formel |

| US12141676B2 (en) * | 2019-01-14 | 2024-11-12 | Tetramem Inc. | Implementing hardware neurons using tunneling devices |

| US11409352B2 (en) | 2019-01-18 | 2022-08-09 | Silicon Storage Technology, Inc. | Power management for an analog neural memory in a deep learning artificial neural network |

| US10720217B1 (en) | 2019-01-29 | 2020-07-21 | Silicon Storage Technology, Inc. | Memory device and method for varying program state separation based upon frequency of use |

| CN109948786B (zh) * | 2019-02-21 | 2021-05-11 | 山东师范大学 | 一种仿脑的数模混合神经元电路及方法 |

| US11423979B2 (en) | 2019-04-29 | 2022-08-23 | Silicon Storage Technology, Inc. | Decoding system and physical layout for analog neural memory in deep learning artificial neural network |

| US12353503B2 (en) * | 2019-05-02 | 2025-07-08 | Silicon Storage Technology, Inc. | Output array neuron conversion and calibration for analog neural memory in deep learning artificial neural network |

| JP7620574B2 (ja) * | 2019-06-02 | 2025-01-23 | エヌパーバー,インコーポレイテッド | ストリームをまたがる共有イベントの検出のための方法及び装置 |

| US20230135011A1 (en) * | 2021-11-04 | 2023-05-04 | Seoul National University R&Db Foundation | Neuron circuit, operating method thereof, and neuromorphic device including neuron circuit |

| CN114386587B (zh) * | 2021-12-30 | 2024-11-15 | 中电海康集团有限公司 | 一种基于神经形态器件的逻辑门 |

| CN114819115B (zh) * | 2022-05-09 | 2024-11-05 | 厦门壹普智慧科技有限公司 | 一种神经元计算方法 |

| CN114997391B (zh) * | 2022-08-02 | 2022-11-29 | 深圳时识科技有限公司 | 电子神经系统中的泄露方法、芯片及电子设备 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002533823A (ja) * | 1998-12-30 | 2002-10-08 | アービン・センサーズ・コーポレイション | 重み付けされたシナプスアレイを最大限に使用する入力アーキテクチャを備えたニューラル処理モジュール |

| JP2010146514A (ja) * | 2008-12-22 | 2010-07-01 | Sharp Corp | 情報処理装置及びこれを用いたニューラルネットワーク回路 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4518866A (en) | 1982-09-28 | 1985-05-21 | Psychologics, Inc. | Method of and circuit for simulating neurons |

| US5148385A (en) | 1987-02-04 | 1992-09-15 | Texas Instruments Incorporated | Serial systolic processor |

| US5201029A (en) | 1988-10-24 | 1993-04-06 | U.S. Philips Corporation | Digital data processing apparatus using daisy chain control |

| US4974169A (en) | 1989-01-18 | 1990-11-27 | Grumman Aerospace Corporation | Neural network with memory cycling |

| US5185851A (en) | 1989-07-12 | 1993-02-09 | Ricoh Company, Ltd. | Neuron unit and neuron unit network |

| US5963930A (en) | 1991-06-26 | 1999-10-05 | Ricoh Company Ltd. | Apparatus and method for enhancing transfer function non-linearities in pulse frequency encoded neurons |

| JPH07114524A (ja) | 1993-10-14 | 1995-05-02 | Ricoh Co Ltd | 信号処理装置 |

| JPH0877129A (ja) * | 1994-09-09 | 1996-03-22 | Kokusai Electric Co Ltd | カオスニューロン回路 |

| JP3305267B2 (ja) * | 1998-08-07 | 2002-07-22 | 株式会社モノリス | シナプス素子、しきい値回路およびニューロン装置 |

| JP4392089B2 (ja) | 1999-05-27 | 2009-12-24 | 株式会社デンソー | ニューロン、当該ニューロンを用いて構成された階層型ニューラルネットワーク及び当該ニューロン内部での乗算処理に用いられる乗算回路 |

| US6292023B1 (en) | 1999-09-29 | 2001-09-18 | Agere Systems Guardian Corp. | Spike-triggered asynchronous finite state machine |

| US7054850B2 (en) | 2000-06-16 | 2006-05-30 | Canon Kabushiki Kaisha | Apparatus and method for detecting or recognizing pattern by employing a plurality of feature detecting elements |

| US20050101995A1 (en) * | 2002-02-19 | 2005-05-12 | Innovationsagentur Gesellschaft | Arrangement for receiving electrical signals from living cells and for the selective transmission of electrical stimulation to living cells |

| GB0207372D0 (en) | 2002-03-28 | 2002-05-08 | Cogniscience Ltd | Digital memory |

| US7174325B1 (en) | 2002-06-07 | 2007-02-06 | George Mason Intellectual Properties, Inc. | Neural processor |

| US7430546B1 (en) | 2003-06-07 | 2008-09-30 | Roland Erwin Suri | Applications of an algorithm that mimics cortical processing |

| US8346692B2 (en) | 2005-12-23 | 2013-01-01 | Societe De Commercialisation Des Produits De La Recherche Appliquee-Socpra-Sciences Et Genie S.E.C. | Spatio-temporal pattern recognition using a spiking neural network and processing thereof on a portable and/or distributed computer |

| WO2008072994A1 (fr) * | 2006-12-13 | 2008-06-19 | Evgeny Nikolaevich Zakharov | Élément neuronal |

-

2010

- 2010-12-08 US US12/963,558 patent/US8473439B2/en active Active

-

2011

- 2011-09-30 CN CN201110305539.4A patent/CN102567784B/zh active Active

- 2011-11-29 JP JP2011260006A patent/JP5623372B2/ja active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002533823A (ja) * | 1998-12-30 | 2002-10-08 | アービン・センサーズ・コーポレイション | 重み付けされたシナプスアレイを最大限に使用する入力アーキテクチャを備えたニューラル処理モジュール |

| JP2010146514A (ja) * | 2008-12-22 | 2010-07-01 | Sharp Corp | 情報処理装置及びこれを用いたニューラルネットワーク回路 |

Non-Patent Citations (2)

| Title |

|---|

| CSNG200900534005; 久保田 直行: '人間共生システム' 知能と情報 第21巻/第5号, 20091015, pp.683-692, 日本知能情報ファジィ学会 * |

| JPN6014026757; 久保田 直行: '人間共生システム' 知能と情報 第21巻/第5号, 20091015, pp.683-692, 日本知能情報ファジィ学会 * |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017529592A (ja) * | 2014-08-08 | 2017-10-05 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | 非同期パルス変調を用いた人工ニューロンおよびスパイキングニューロン |

| JP2021527910A (ja) * | 2018-06-06 | 2021-10-14 | マイクロン テクノロジー,インク. | メモリデバイスを使用するウエイトストイレージ |

| JP7048768B2 (ja) | 2018-06-06 | 2022-04-05 | マイクロン テクノロジー,インク. | メモリデバイスを使用するウエイトストイレージ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102567784B (zh) | 2015-03-25 |

| CN102567784A (zh) | 2012-07-11 |

| US20120150781A1 (en) | 2012-06-14 |

| JP5623372B2 (ja) | 2014-11-12 |

| US8473439B2 (en) | 2013-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5623372B2 (ja) | 統合発火型電子ニューロン、方法およびプログラム | |

| US9984324B2 (en) | Dual deterministic and stochastic neurosynaptic core circuit | |

| US11295201B2 (en) | Time-division multiplexed neurosynaptic module with implicit memory addressing for implementing a neural network | |

| KR102592146B1 (ko) | 시냅스 가중치 학습을 위한 뉴런 회로, 시스템 및 방법 | |

| US9373073B2 (en) | Time-division multiplexed neurosynaptic module with implicit memory addressing for implementing a universal substrate of adaptation | |

| US11238343B2 (en) | Scalable neural hardware for the noisy-OR model of Bayesian networks | |

| US10339041B2 (en) | Shared memory architecture for a neural simulator | |

| JP5680751B2 (ja) | 離散順位シナプス及び確率的なstdpによるデジタル神経処理のための方法及びシステム | |

| US10248906B2 (en) | Neuromorphic circuits for storing and generating connectivity information | |

| US20120173471A1 (en) | Synaptic weight normalized spiking neuronal networks | |

| JP6133503B2 (ja) | 擬似乱数のプログラム可能な確率分布関数を生成するための方法および装置 | |

| JP2015510195A (ja) | スパイキングニューラル計算のための方法および装置 | |

| CN109325587B (zh) | 可变历元尖峰序列滤波 | |

| JP2017510890A (ja) | 一般的なニューロンモデルの効率的な実装のための方法および装置 | |

| US20150278683A1 (en) | Plastic synapse management | |

| CA2924468A1 (en) | Congestion avoidance in networks of spiking neurons | |

| JP6219509B2 (ja) | シナプス遅延を動的に割り当てることおおよび検査すること | |

| US20190095211A1 (en) | Computational method for temporal pooling and correlation | |

| CN119378618B (zh) | 一种基于近似计算的可在线学习神经形态处理器 | |

| US20180174039A1 (en) | Computationally-efficient spike train filtering | |

| WO2014197175A2 (en) | Efficient implementation of neural population diversity in neural system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140610 Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140610 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20140610 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20140610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140611 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140613 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20140620 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140718 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140815 Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140815 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140911 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140911 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20140911 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140924 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5623372 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |