JP2010147544A - 駆動装置 - Google Patents

駆動装置 Download PDFInfo

- Publication number

- JP2010147544A JP2010147544A JP2008319553A JP2008319553A JP2010147544A JP 2010147544 A JP2010147544 A JP 2010147544A JP 2008319553 A JP2008319553 A JP 2008319553A JP 2008319553 A JP2008319553 A JP 2008319553A JP 2010147544 A JP2010147544 A JP 2010147544A

- Authority

- JP

- Japan

- Prior art keywords

- current

- circuit

- output

- current mirror

- drive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000006243 chemical reaction Methods 0.000 claims description 20

- 238000001514 detection method Methods 0.000 claims description 9

- 238000004904 shortening Methods 0.000 abstract 1

- NCGICGYLBXGBGN-UHFFFAOYSA-N 3-morpholin-4-yl-1-oxa-3-azonia-2-azanidacyclopent-3-en-5-imine;hydrochloride Chemical compound Cl.[N-]1OC(=N)C=[N+]1N1CCOCC1 NCGICGYLBXGBGN-UHFFFAOYSA-N 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 7

- 238000010586 diagram Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 4

- 230000000295 complement effect Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Landscapes

- Inverter Devices (AREA)

- Electronic Switches (AREA)

Abstract

【課題】直列接続されたスイッチング素子の貫通電流を防止するとともに、オンオフ切替時に生じる両スイッチング素子の同時オフ期間を短縮する。

【解決手段】MOSFET7に電流が流れると、MOSFET13および抵抗15を通して電流が流れ、抵抗15に電圧が発生する。この電圧によりトランジスタ24、カレントミラー回路27、28に電流が流れ、トランジスタ32がオンして駆動回路10の出力端子を電源線3の電位付近にまで引き下げるので、ゲート駆動信号SG1はオフ駆動の信号状態となる。同様に、MOSFET6に電流が流れると、トランジスタ39がオンして駆動回路11の出力端子を電源線3の電位付近にまで引き下げるので、ゲート駆動信号SG2はオフ駆動の信号状態となる。

【選択図】図1

【解決手段】MOSFET7に電流が流れると、MOSFET13および抵抗15を通して電流が流れ、抵抗15に電圧が発生する。この電圧によりトランジスタ24、カレントミラー回路27、28に電流が流れ、トランジスタ32がオンして駆動回路10の出力端子を電源線3の電位付近にまで引き下げるので、ゲート駆動信号SG1はオフ駆動の信号状態となる。同様に、MOSFET6に電流が流れると、トランジスタ39がオンして駆動回路11の出力端子を電源線3の電位付近にまで引き下げるので、ゲート駆動信号SG2はオフ駆動の信号状態となる。

【選択図】図1

Description

本発明は、第1および第2の直流電源線の間に出力端子を挟んで直列に接続された第1および第2のスイッチング素子の駆動装置に関する。

この種の接続形態は、Hブリッジ回路などで用いられている。Hブリッジ回路では、第1および第2のスイッチング素子を相補的にオンオフ駆動するが、両スイッチング素子が同時にオンする期間があると貫通電流が流れる。貫通電流が増大すると、消費電流、電源電圧変動、ノイズなどが増加し、スイッチング素子自体やその駆動回路が故障する虞がある。そこで、両スイッチング素子が同時にオフとなる期間を確保するためデッドタイムを設けている。

特許文献1記載の発明では、制御信号のHレベル/Lレベルに応じてコンデンサを定電流で充電/放電させ、そのコンデンサの電圧を電圧クランプ回路により下限電圧から上限電圧までの間に制限する。そして、第2判定電圧>第1判定電圧の関係の下で、コンデンサの電圧が第1判定電圧以下の場合に第1のスイッチング素子をオンさせ、コンデンサの電圧が第2判定電圧以上の場合に第2のスイッチング素子をオンさせる。その結果、制御信号の変化に伴いコンデンサの電圧が変化し、コンデンサの電圧が第1判定電圧と第2判定電圧との範囲内にある間、第1、第2のスイッチング素子を共にオフさせ、貫通電流の発生を抑制できる。

特開平10−56796号公報

スイッチング素子は、駆動回路からオフ制御信号が出力されてから電流が実際に遮断されるまでに遅れが生じる。この遅れは、駆動回路の電流出力能力、FETのゲート容量などに依存する。特許文献1記載の切替回路を用いる場合でも、スイッチング素子のターンオン時間およびターンオフ時間のばらつきを考慮して、余裕を持ったデッドタイムを設定する必要がある。そのため、コンデンサの容量値を大きくせざるを得ず、第1判定電圧と第2判定電圧との範囲内にある期間が長くなって高速動作の妨げとなる。

本発明は上記事情に鑑みてなされたもので、その目的は、直列接続された第1、第2のスイッチング素子の貫通電流を防止するとともに、オンオフ切替時に生じる両スイッチング素子の同時オフ期間を短縮できる駆動装置を提供することにある。

請求項1に記載した手段によれば、第1、第2のスイッチング素子は、第1、第2の直流電源線の間に出力端子を挟んで直列接続されており、それぞれ第1、第2の駆動回路から出力される駆動信号により駆動される。第2のスイッチング素子に電流が流れていると、第2の電源線を接地電位として動作する第2のカレントミラー回路の入力側トランジスタと第2の電源線との間に、第2の電流−電圧変換回路によって電流に応じた電圧が発生する。この電圧により、第2のカレントミラー回路の出力側トランジスタに、ミラー比に従った電流よりも大きい電流が流れ、第1の信号制御回路は、第1の駆動回路から出力される駆動信号をオフ駆動の信号状態とする。同様にして、第1のスイッチング素子に電流が流れていると、第2の信号制御回路は、第2の駆動回路から出力される駆動信号をオフ駆動の信号状態とする。

このように、直列接続された第1、第2のスイッチング素子は、相手側のスイッチング素子に実際に電流が流れている時、第1、第2の駆動回路からの駆動信号にかかわらず強制的にオフ駆動状態となる。従って、駆動信号相互間のデッドタイムの設定が不要となり、スイッチング素子のターンオフ時間の大小やばらつきにかかわらず、一方のスイッチング素子がオフして実際に電流が遮断されると同時に他方のスイッチング素子をオンさせることが可能となる。これにより、貫通電流を防止できるとともに、オンオフ切替時に生じる両スイッチング素子の同時オフ期間を短くできる。

請求項2に記載した手段によれば、第2のスイッチング素子に電流が流れていると、第2のカレントミラー回路を介して第3のカレントミラー回路、さらには第4のカレントミラー回路に電流が流れる。このとき、第4のカレントミラー回路の出力側トランジスタにより、第1の駆動回路の出力線と第2の電源線との間が短絡され、第1の駆動回路から出力される駆動信号はオフ駆動の信号状態となる。同様にして、第1のスイッチング素子に電流が流れていると、第1、第5、第6のカレントミラー回路に電流が流れ、第2の駆動回路から出力される駆動信号はオフ駆動の信号状態となる。

請求項3に記載した手段によれば、第1、第2の信号制御回路は、それぞれ第1、第2の駆動回路に内蔵されており、駆動回路の構成に適した種々の構成を採用することができる。

請求項4に記載した手段によれば、第1のスイッチング素子に電流が流れると、第1の電流−電圧変換回路において、第1のスイッチング素子と制御端子同士が接続された第1の電流検出用トランジスタに電流が流れ、その電流を第1の抵抗に流すことより電流−電圧変換が行われる。第2の電流−電圧変換回路も同様である。

請求項5に記載した手段によれば、第1の電流−電圧変換回路は、第1のスイッチング素子と出力端子との間に接続された第1の抵抗により構成され、第2の電流−電圧変換回路は、第2のスイッチング素子と第2の電源線との間に接続された第2の抵抗により構成されている。本手段によれば、請求項4に記載した手段と比べ電流−電圧変換回路を構成する素子数を低減できる。

(第1の実施形態)

以下、本発明の第1の実施形態について図1ないし図3を参照しながら説明する。

図2は、ICに内蔵されたHブリッジ回路の構成図である。IC1内の電源線2、3(第1、第2の直流電源線)には、例えばバッテリ電圧VBに基づいて生成された一定の制御電圧Vccが与えられている。Hブリッジ回路4の各アーム4a、4bは、それぞれ、電源線2、3間に出力端子5a、5bを挟んで直列に接続されたハイサイド側、ロウサイド側のNチャネル型MOSFET6、7(第1、第2のスイッチング素子)から構成されている。これらMOSFET6、7は、後述する駆動装置8により駆動される。IC1の出力端子5a、5b間には、外部の負荷9例えばアンテナが接続されるようになっている。

以下、本発明の第1の実施形態について図1ないし図3を参照しながら説明する。

図2は、ICに内蔵されたHブリッジ回路の構成図である。IC1内の電源線2、3(第1、第2の直流電源線)には、例えばバッテリ電圧VBに基づいて生成された一定の制御電圧Vccが与えられている。Hブリッジ回路4の各アーム4a、4bは、それぞれ、電源線2、3間に出力端子5a、5bを挟んで直列に接続されたハイサイド側、ロウサイド側のNチャネル型MOSFET6、7(第1、第2のスイッチング素子)から構成されている。これらMOSFET6、7は、後述する駆動装置8により駆動される。IC1の出力端子5a、5b間には、外部の負荷9例えばアンテナが接続されるようになっている。

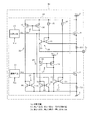

図1は、一対のMOSFET6、7とその駆動装置8(1アーム分)の構成を示している。MOSFET6、7は、それぞれ第1、第2の駆動回路10、11から出力されるゲート駆動信号SG1、SG2により駆動される。駆動回路10は、チャージポンプ回路等からなる昇圧回路を備えており、制御電圧Vccよりも少なくともMOSFET6のしきい値電圧Vthだけ高いゲート駆動信号SG1を出力可能である。

MOSFET6、7には、それぞれ電流センス用のMOSFET12、13(第1、第2の電流検出用トランジスタ)が接続されている。MOSFET6、12のゲート同士およびドレイン同士並びにMOSFET7、13のゲート同士およびドレイン同士は接続されている。MOSFET12と出力端子5aの間、MOSFET13と電源線3との間にはそれぞれ第1、第2の抵抗14、15が接続されており、MOSFET12と抵抗14、MOSFET13と抵抗15により、それぞれ第1、第2の電流−電圧変換回路16、17が構成されている。

第1のカレントミラー回路18は、出力端子5aを接地電位として動作するもので、上記抵抗14を介して出力端子5aに接地された入力側トランジスタ19と出力端子5aに直接接地された出力側トランジスタ20とから構成されている。入力側トランジスタ19のコレクタ(ベース)と電源線2との間には定電流回路21が接続されている。同様に、第2のカレントミラー回路22は、電源線3を接地電位として動作するもので、上記抵抗15を介して電源線3に接地された入力側トランジスタ23と電源線3に直接接地された出力側トランジスタ24とから構成されている。入力側トランジスタ23のコレクタ(ベース)と電源線2との間には定電流回路25が接続されている。

第1の信号制御回路26は、カレントミラー回路22の出力側トランジスタ24に電流が流れている時に、駆動回路10から出力されるゲート駆動信号SG1をオフ駆動の信号状態とするもので、第3のカレントミラー回路27と第4のカレントミラー回路28とから構成されている。第3のカレントミラー回路27は、電源線2を接地電位として動作するもので、電源線2と出力側トランジスタ24との間に接続された入力側MOSFET29と、電源線2と入力側トランジスタ31(後述)との間に接続された出力側MOSFET30とから構成されている。また、第4のカレントミラー回路28は、電源線3を接地電位として動作するもので、出力側MOSFET30と電源線3との間に接続された入力側トランジスタ31と、駆動回路10の出力端子と電源線3との間に接続された出力側トランジスタ32とから構成されている。

同様に、第2の信号制御回路33は、カレントミラー回路18の出力側トランジスタ20に電流が流れている時に、駆動回路11から出力されるゲート駆動信号SG2をオフ駆動の信号状態とするもので、第5のカレントミラー回路34と第6のカレントミラー回路35とから構成されている。カレントミラー回路34は、電源線2を接地電位として動作するもので、電源線2と出力側トランジスタ20との間に接続された入力側MOSFET36と、電源線2と入力側トランジスタ38(後述)との間に接続された出力側MOSFET37とから構成されている。また、第6のカレントミラー回路35は、電源線3を接地電位として動作するもので、出力側MOSFET37と電源線3との間に接続された入力側トランジスタ38と、駆動回路11の出力端子と電源線3との間に接続された出力側トランジスタ39とから構成されている。

次に、本実施形態の作用および効果について説明する。

図3(a)および(b)は、それぞれ駆動装置8および従来の駆動装置で用いるハイサイド側とロウサイド側の駆動信号Sin1、Sin2の一例である。駆動回路10、11は、それぞれ駆動信号Sin1、Sin2をMOSFET6、7のゲート駆動電圧に適したレベルに変換してゲート駆動信号SG1、SG2として出力する。図中に示すしきい値電圧Vaは、MOSFET6、7のしきい値電圧Vthに対応するレベルである。

図3(a)および(b)は、それぞれ駆動装置8および従来の駆動装置で用いるハイサイド側とロウサイド側の駆動信号Sin1、Sin2の一例である。駆動回路10、11は、それぞれ駆動信号Sin1、Sin2をMOSFET6、7のゲート駆動電圧に適したレベルに変換してゲート駆動信号SG1、SG2として出力する。図中に示すしきい値電圧Vaは、MOSFET6、7のしきい値電圧Vthに対応するレベルである。

図3(a)に示す駆動信号Sin1、Sin2はデッドタイムのない完全なる相補信号であり、従来の駆動装置であれば少なくとも期間T1、T2においてMOSFET6、7を同時にオン駆動してしまうものである。MOSFET6、7をオフさせるには、ゲート容量に応じたターンオフ時間も必要であるため、従来の駆動装置は、図3(b)に示すようにターンオフ時間まで含めた余裕のあるデッドタイム(デッドオフ)を確保していた。

図3(a)に示す期間T1における駆動装置8の動作は以下のようになる。

期間T1の間、駆動信号Sin2はしきい値電圧Vaよりも高いので、ロウサイド側のMOSFET7に電流が流れ続ける。MOSFET7に電流が流れると、MOSFET13および抵抗15を通して検出電流が流れ、抵抗15にMOSFET7に流れる電流に応じた電圧が発生する。この電圧の発生により、カレントミラー回路22の出力側トランジスタ24には、定電流回路25の出力電流とミラー比とで定まる電流よりも大きい電流が流れる。

期間T1の間、駆動信号Sin2はしきい値電圧Vaよりも高いので、ロウサイド側のMOSFET7に電流が流れ続ける。MOSFET7に電流が流れると、MOSFET13および抵抗15を通して検出電流が流れ、抵抗15にMOSFET7に流れる電流に応じた電圧が発生する。この電圧の発生により、カレントミラー回路22の出力側トランジスタ24には、定電流回路25の出力電流とミラー比とで定まる電流よりも大きい電流が流れる。

この電流は、第3のカレントミラー回路27を介して第4のカレントミラー回路28の入力側トランジスタ31に流れ、その出力側トランジスタ32がオンする。その結果、駆動回路10の出力端子はトランジスタ32を介して電源線3の電位(0V)付近にまで引き下げられ、ゲート駆動信号SG1はオフ駆動の信号状態となる。つまり、ハイサイド側の駆動回路10にオン指令の駆動信号Sin1が入力されても、ロウサイド側のMOSFET7に実際に電流が流れている限り、ハイサイド側のMOSFET6はオンすることがない。

一方、図3(a)に示す期間T2における駆動装置8の動作は以下のようになる。

期間T2の間、駆動信号Sin1はしきい値電圧Vaよりも高いので、ハイサイド側のMOSFET6に電流が流れ続ける。MOSFET6に電流が流れると、MOSFET12および抵抗14を通して検出電流が流れ、抵抗14にMOSFET6に流れる電流に応じた電圧が発生する。この電圧の発生により、カレントミラー回路18の出力側トランジスタ20には、定電流回路21の出力電流とミラー比とで定まる電流よりも大きい電流が流れる。

期間T2の間、駆動信号Sin1はしきい値電圧Vaよりも高いので、ハイサイド側のMOSFET6に電流が流れ続ける。MOSFET6に電流が流れると、MOSFET12および抵抗14を通して検出電流が流れ、抵抗14にMOSFET6に流れる電流に応じた電圧が発生する。この電圧の発生により、カレントミラー回路18の出力側トランジスタ20には、定電流回路21の出力電流とミラー比とで定まる電流よりも大きい電流が流れる。

この電流は、第5のカレントミラー回路34を介して第6のカレントミラー回路35の入力側トランジスタ38に流れ、その出力側トランジスタ39がオンする。その結果、駆動回路11の出力端子はトランジスタ39を介して電源線3の電位(0V)付近にまで引き下げられ、ゲート駆動信号SG2はオフ駆動の信号状態となる。つまり、ロウサイド側の駆動回路11にオン指令の駆動信号Sin2が入力されても、ハイサイド側のMOSFET6に実際に電流が流れている限り、ロウサイド側のMOSFET7はオンすることがない。

以上説明したように、本実施形態の駆動装置8は、駆動信号Sin1、Sin2に従ってMOSFET6、7を駆動するが、互いに相手側のMOSFET7、6に電流が流れている時には、インターロックをかけてMOSFET6、7へのゲート駆動信号SG1、SG2をオフ駆動の信号状態とする。その結果、駆動信号Sin1、Sin2のオン期間が重なることによりまたはターンオフ時間が存在することにより、従来構成であればMOSFET6、7が同時にオンする場合であっても、駆動装置8を用いれば貫通電流の発生を確実に防止することができる。

しかも、デッドタイムを付加しない駆動信号Sin1、Sin2を用いることにより、MOSFET6、7のうち一方のMOSFETが実際にオフになるのとほぼ同時に他方のMOSFETがオンするので、オンオフ切替時に生じるMOSFET6、7の同時オフ期間が短くなり、無駄のない(デッドオフの短い)高速駆動が可能となる。また、素子のターンオン時間、ターンオフ時間などのばらつきを考慮する必要もなくなる。

(第2の実施形態)

図4は、本発明の第2の実施形態であって、図1と同一部分には同一符号を付している。以下、図1と異なる構成について説明する。IC41に形成された駆動装置42は、MOSFET6、7を駆動する駆動回路43、44を備えている。駆動回路43は、出力側トランジスタ24のコレクタを電源線2にプルアップする抵抗45、当該コレクタの電圧を入力とするヒステリシス付きのバッファ回路46、および駆動信号Sin1とバッファ回路46の出力信号を入力とするANDゲート47を備えている。ANDゲート47の出力信号は、図中省略されたレベルシフト回路を経てゲート駆動信号SG1として出力される。

図4は、本発明の第2の実施形態であって、図1と同一部分には同一符号を付している。以下、図1と異なる構成について説明する。IC41に形成された駆動装置42は、MOSFET6、7を駆動する駆動回路43、44を備えている。駆動回路43は、出力側トランジスタ24のコレクタを電源線2にプルアップする抵抗45、当該コレクタの電圧を入力とするヒステリシス付きのバッファ回路46、および駆動信号Sin1とバッファ回路46の出力信号を入力とするANDゲート47を備えている。ANDゲート47の出力信号は、図中省略されたレベルシフト回路を経てゲート駆動信号SG1として出力される。

同様に、駆動回路44は、出力側トランジスタ20のコレクタ電位のレベルシフト回路(図中省略)、レベルシフトされた出力側トランジスタ20のコレクタ電位を電源線2にプルアップする抵抗48、当該コレクタの電圧を入力とするヒステリシス付きのバッファ回路49、および駆動信号Sin2とバッファ回路49の出力信号を入力とするANDゲート50を備えている。ANDゲート50の出力信号は、必要に応じてレベルシフトされゲート駆動信号SG2として出力される。

駆動回路43、44は、本発明でいう第1、第2の信号制御回路としての機能も備えている。すなわち、MOSFET7に電流が流れている期間、電源線2から抵抗45および出力側トランジスタ24を介して電流が流れるのでバッファ回路46の出力信号はLレベルとなり、駆動信号Sin1のレベルにかかわらずゲート駆動信号SG1はオフ駆動の信号状態となる。同様に、MOSFET6に電流が流れている期間もゲート駆動信号SG2はオフ駆動の信号状態となる。従って、本実施形態によっても第1の実施形態と同様の作用および効果が得られる。

(第3の実施形態)

図5は、本発明の第3の実施形態であって、図1と同一部分には同一符号を付している。IC51に形成された駆動装置52は、上述した各実施形態の第1、第2の電流−電圧変換回路16、17に替えて、それぞれMOSFET6と出力端子5aとの間に接続された第1の抵抗53、MOSFET7と電源線3との間に接続された第2の抵抗54を備えている。抵抗53、54には負荷9の電流が流れるので、損失を減らすために低抵抗のシャント抵抗を用いる。本実施形態によっても第1の実施形態と同様の作用および効果が得られる他、電流−電圧変換回路を構成する素子数を低減できる。

図5は、本発明の第3の実施形態であって、図1と同一部分には同一符号を付している。IC51に形成された駆動装置52は、上述した各実施形態の第1、第2の電流−電圧変換回路16、17に替えて、それぞれMOSFET6と出力端子5aとの間に接続された第1の抵抗53、MOSFET7と電源線3との間に接続された第2の抵抗54を備えている。抵抗53、54には負荷9の電流が流れるので、損失を減らすために低抵抗のシャント抵抗を用いる。本実施形態によっても第1の実施形態と同様の作用および効果が得られる他、電流−電圧変換回路を構成する素子数を低減できる。

(第4の実施形態)

図6は、本発明の第4の実施形態であって、図1と実質的に同一な部分には同一符号を付している。IC61にはMOS製造プロセスが採用されており、駆動装置62を構成するトランジスタは全てMOSFETにより形成されている。本実施形態によっても第1の実施形態と同様の作用および効果が得られる。

図6は、本発明の第4の実施形態であって、図1と実質的に同一な部分には同一符号を付している。IC61にはMOS製造プロセスが採用されており、駆動装置62を構成するトランジスタは全てMOSFETにより形成されている。本実施形態によっても第1の実施形態と同様の作用および効果が得られる。

(その他の実施形態)

なお、本発明は上記し且つ図面に示す各実施形態に限定されるものではなく、例えば以下のように変形または拡張が可能である。

第2、第3の実施形態においても、バイポーラトランジスタをFETに置き替えてもよい。また、各実施形態において、FETをバイポーラトランジスタに置き替えてもよい。

駆動信号Sin1、Sin2は、図3(a)に示した台形波に限らず、例えば立ち上がり時間および立ち下がり時間がほぼゼロの方形波であってもよい。この場合でも、デッドタイムを設ける必要はない。

なお、本発明は上記し且つ図面に示す各実施形態に限定されるものではなく、例えば以下のように変形または拡張が可能である。

第2、第3の実施形態においても、バイポーラトランジスタをFETに置き替えてもよい。また、各実施形態において、FETをバイポーラトランジスタに置き替えてもよい。

駆動信号Sin1、Sin2は、図3(a)に示した台形波に限らず、例えば立ち上がり時間および立ち下がり時間がほぼゼロの方形波であってもよい。この場合でも、デッドタイムを設ける必要はない。

図面中、2、3は電源線(第1、第2の直流電源線)、5a、5bは出力端子、6、7はMOSFET(第1、第2のスイッチング素子)、8、42、52、62は駆動装置、10、11は第1、第2の駆動回路、12、13はMOSFET(第1、第2の電流検出用トランジスタ)、14、15は第1、第2の抵抗、16、17は第1、第2の電流−電圧変換回路、18、22は第1、第2のカレントミラー回路、26、33は第1、第2の信号制御回路、27、28、34、35は第3、第4、第5、第6のカレントミラー回路、43は駆動回路(第1の信号制御回路)、44は駆動回路(第2の信号制御回路)、53は第1の抵抗(第1の電流−電圧変換回路)、54は第2の抵抗(第2の電流−電圧変換回路)である。

Claims (5)

- 第1および第2の直流電源線の間に出力端子を挟んで直列に接続された第1および第2のスイッチング素子の駆動装置であって、

前記第1のスイッチング素子の制御端子に駆動信号を出力する第1の駆動回路と、

前記第2のスイッチング素子の制御端子に駆動信号を出力する第2の駆動回路と、

前記出力端子を接地電位として動作する第1のカレントミラー回路と、

前記第2の電源線を接地電位として動作する第2のカレントミラー回路と、

前記第1のカレントミラー回路の入力側トランジスタと前記出力端子との間に前記第1のスイッチング素子に流れる電流に応じた電圧を生じさせる第1の電流−電圧変換回路と、

前記第2のカレントミラー回路の入力側トランジスタと前記第2の電源線との間に、前記第2のスイッチング素子に流れる電流に応じた電圧を生じさせる第2の電流−電圧変換回路と、

前記第2のカレントミラー回路の出力側トランジスタに電流が流れている時に、前記第1の駆動回路から出力される駆動信号をオフ駆動の信号状態とする第1の信号制御回路と、

前記第1のカレントミラー回路の出力側トランジスタに電流が流れている時に、前記第2の駆動回路から出力される駆動信号の状態をオフ駆動の信号状態とする第2の信号制御回路とを備えていることを特徴とする駆動装置。 - 前記第1の信号制御回路は、

前記第1の電源線を接地電位として動作し、前記第2のカレントミラー回路の出力電流を入力とする第3のカレントミラー回路と、

前記第2の電源線を接地電位として動作し、前記第3のカレントミラー回路の出力電流を入力とし、出力側トランジスタが前記第1の駆動回路の出力線と前記第2の電源線との間に接続された第4のカレントミラー回路とから構成され、

前記第2の信号制御回路は、

前記第1の電源線を接地電位として動作し、前記第1のカレントミラー回路の出力電流を入力とする第5のカレントミラー回路と、

前記第2の電源線を接地電位として動作し、前記第5のカレントミラー回路の出力電流を入力とし、出力側トランジスタが前記第2の駆動回路の出力線と前記第2の電源線との間に接続された第6のカレントミラー回路とから構成されていることを特徴とする請求項1記載の駆動装置。 - 前記第1、第2の信号制御回路は、それぞれ前記第1、第2の駆動回路に内蔵されていることを特徴とする請求項1記載の駆動装置。

- 前記第1の電流−電圧変換回路は、前記第1のスイッチング素子と制御端子同士が接続された第1の電流検出用トランジスタと、この第1の電流検出用トランジスタと前記出力端子との間に接続された第1の抵抗との直列回路により構成され、前記第1のカレントミラー回路の入力側トランジスタは前記第1の抵抗を介して前記出力端子に接続されており、

前記第2の電流−電圧変換回路は、前記第2のスイッチング素子と制御端子同士が接続された第2の電流検出用トランジスタと、この第2の電流検出用トランジスタと前記第2の電源線との間に接続された第2の抵抗との直列回路により構成され、前記第2のカレントミラー回路の入力側トランジスタは前記第2の抵抗を介して前記第2の電源線に接続されていることを特徴とする請求項1ないし3の何れかに記載の駆動装置。 - 前記第1の電流−電圧変換回路は、前記第1のスイッチング素子と前記出力端子との間に接続された第1の抵抗により構成され、

前記第2の電流−電圧変換回路は、前記第2のスイッチング素子と前記第2の電源線との間に接続された第2の抵抗により構成されていることを特徴とする請求項1ないし3の何れかに記載の駆動装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008319553A JP2010147544A (ja) | 2008-12-16 | 2008-12-16 | 駆動装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008319553A JP2010147544A (ja) | 2008-12-16 | 2008-12-16 | 駆動装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010147544A true JP2010147544A (ja) | 2010-07-01 |

Family

ID=42567563

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008319553A Pending JP2010147544A (ja) | 2008-12-16 | 2008-12-16 | 駆動装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010147544A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019515558A (ja) * | 2016-09-20 | 2019-06-06 | ミツビシ・エレクトリック・アールアンドディー・センター・ヨーロッパ・ビーヴィMitsubishi Electric R&D Centre Europe B.V. | スイッチングを制御する装置及び方法 |

-

2008

- 2008-12-16 JP JP2008319553A patent/JP2010147544A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019515558A (ja) * | 2016-09-20 | 2019-06-06 | ミツビシ・エレクトリック・アールアンドディー・センター・ヨーロッパ・ビーヴィMitsubishi Electric R&D Centre Europe B.V. | スイッチングを制御する装置及び方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8324880B2 (en) | Power converting system with function of reducing dead-time | |

| JP5934925B2 (ja) | ゲートドライバおよびこれを備えたパワーモジュール | |

| JP5315026B2 (ja) | 半導体装置 | |

| JP4005999B2 (ja) | 半導体装置 | |

| CN102027663A (zh) | 降压开关稳压器 | |

| US9024660B2 (en) | Driving circuit with zero current shutdown and a driving method thereof | |

| JPWO2009044602A1 (ja) | ゲート駆動回路 | |

| CN103141028A (zh) | 电平移动电路 | |

| KR101297460B1 (ko) | 게이트 구동 장치 | |

| US7724069B1 (en) | Analog switch for operation outside power rails with low supply current | |

| JP2006314154A (ja) | 電力変換器 | |

| CN115776297B (zh) | 一种低功耗、宽电源电压范围的栅极驱动集成电路 | |

| US9312848B2 (en) | Glitch suppression in an amplifier | |

| JP2010028522A (ja) | 半導体装置 | |

| JP5842223B2 (ja) | ドライバ回路 | |

| CN101542905A (zh) | 反相器电路 | |

| JP2018074676A (ja) | ゲート駆動回路 | |

| JP5382702B2 (ja) | ドライバ回路 | |

| CN115224913B (zh) | 功率开关电路及对应操作方法 | |

| JP2010147544A (ja) | 駆動装置 | |

| JP3759499B2 (ja) | 過電流を全く生じることなく電流をターン・オンおよびターン・オフさせるための回路構造 | |

| US20040227193A1 (en) | Mosfet gate driver with a negative gate bias voltage | |

| US7733154B2 (en) | Semiconductor device | |

| US8294506B2 (en) | Driving system for switching power supply to reduce switch noise and switching loss | |

| JP2002315317A (ja) | Dc/dcコンバータおよびそのスイッチングノイズ低減方法 |