JP2010146601A - 半導体記憶装置及びその制御方法 - Google Patents

半導体記憶装置及びその制御方法 Download PDFInfo

- Publication number

- JP2010146601A JP2010146601A JP2008319643A JP2008319643A JP2010146601A JP 2010146601 A JP2010146601 A JP 2010146601A JP 2008319643 A JP2008319643 A JP 2008319643A JP 2008319643 A JP2008319643 A JP 2008319643A JP 2010146601 A JP2010146601 A JP 2010146601A

- Authority

- JP

- Japan

- Prior art keywords

- potential

- memory device

- semiconductor memory

- dummy word

- bit line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 51

- 238000000034 method Methods 0.000 title description 6

- 230000000295 complement effect Effects 0.000 claims description 15

- 230000008878 coupling Effects 0.000 claims description 7

- 238000010168 coupling process Methods 0.000 claims description 7

- 238000005859 coupling reaction Methods 0.000 claims description 7

- 230000003213 activating effect Effects 0.000 claims description 2

- 230000007704 transition Effects 0.000 claims 2

- 230000008859 change Effects 0.000 abstract description 5

- 238000010586 diagram Methods 0.000 description 9

- 238000003491 array Methods 0.000 description 7

- 230000003071 parasitic effect Effects 0.000 description 7

- 230000003321 amplification Effects 0.000 description 6

- 238000003199 nucleic acid amplification method Methods 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 3

- 230000004913 activation Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000001808 coupling effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

Images

Landscapes

- Dram (AREA)

Abstract

【課題】半導体記憶装置の駆動電圧の低下電圧化に伴い参照電位が低下しても十分なセンスマージンを確保する。

【解決手段】互いに相補に対を成すビット線2a,2bから成るビット線対と、該ビット線対のビット線2a,2bの各々に対して該ビット線2a,2bと交差して配置される本ワード線3a,3bと、ビット線2a,2bと本ワード線3a,3bの交点に配置されデータを電位として保持するメモリセル4a,4bと、ビット線対のビット線2a,2bの各々と接続され、メモリセル4a,4bに保持されているデータの読出しにより、ビット線2a,2bの一方の電位が変化して生じたビット線対間の電位差を増幅するセンスアンプ1とを有する半導体記憶装置において、ビット線対間に電位差が生じた後、センスアンプ1によって当該電位差を増幅する前にビット線対のビット線2a,2bの各々の電位を共に引き上げる電位上昇手段を有する。

【選択図】図1

【解決手段】互いに相補に対を成すビット線2a,2bから成るビット線対と、該ビット線対のビット線2a,2bの各々に対して該ビット線2a,2bと交差して配置される本ワード線3a,3bと、ビット線2a,2bと本ワード線3a,3bの交点に配置されデータを電位として保持するメモリセル4a,4bと、ビット線対のビット線2a,2bの各々と接続され、メモリセル4a,4bに保持されているデータの読出しにより、ビット線2a,2bの一方の電位が変化して生じたビット線対間の電位差を増幅するセンスアンプ1とを有する半導体記憶装置において、ビット線対間に電位差が生じた後、センスアンプ1によって当該電位差を増幅する前にビット線対のビット線2a,2bの各々の電位を共に引き上げる電位上昇手段を有する。

【選択図】図1

Description

本発明は、半導体記憶装置及びその制御方法に関する。

半導体記憶装置には、本ワード線とビット線が格子状に配置され、それらの交点にデータを記憶するためのメモリセルが設けられている。なお、メモリセルは‘0’もしくは‘1’に対応するデータを記憶するために、それらに対応付けられた高電位Hもしくは低電位Lを保持する。

この様な半導体記憶装置においては、メモリセルからデータを読み出すために、データ読出し前にビット線を参照電位にプリチャージする。そして、ビット線のプリチャージを解除してフローティング状態にした後、アドレス入力により決定される本ワード線を駆動して対応するメモリセルを選択する。これにより、選択したメモリセルに保持されている高電位Hもしくは低電位Lに基づいてビット線の電位が変化する。さらに、電位が変化したビット線と、そのビット線と相補に対を成すビット線との電位差をセンスアンプで増幅し、この増幅した電位差に基づいて、外部へ記憶データの読み出しが行われる。

なお、通常、半導体装置においては、センスアンプは、2つのPチャネルMOSトランジスタPchTrと2つのNチャネルMOSトランジスタNchTrとを備えて構成されている。この様なセンスアンプにおいて、一般的にNチャネルMOSトランジスタNchTrの方がPチャネルMOSトランジスタPchTrよりもペアのトランジスタの閾値電圧Vtのアンバランスが小さいため、NチャネルMOSトランジスタNchTrを先に駆動し、ビット線間の電位差がPチャネルMOSトランジスタPchTrの閾値電圧Vtのアンバランスよりも大きくなった時点でPチャネルMOSトランジスタPchTrを駆動する。

また、低電圧で動作するダイナミック型半導体記憶装置(DRAM)において、動作速度を確保するためのビット線のプリチャージ方式として、例えば、特許文献1には、容量結合型のダミーセルを用いて適切なビット線の参照電位を設定する技術が記載されている。

特開2001−307479号公報

近年、半導体記憶装置が携帯端末等にも搭載されるようになり、半導体記憶装置の駆動電圧(電源電圧)の低電圧化が求められており、駆動電圧の低電圧化に伴い参照電位も低下しつつある。つまり、参照電位が、徐々に、センスアンプを構成するNチャネルMOSトランジスタNchTrの閾値電圧Vtに近づきつつある。

そのため、特に低電位Lのデータを保持しているメモリセルからの読出しに基づいて変化したビット線間の電位差をセンスアンプで増幅する際に、先行して駆動させるこのNチャネルMOSトランジスタNchTrのゲート・ソース間電位差Vgsおよびドレインソース間電位差Vds自体が小さくなり、NチャネルMOSトランジスタNchTrのドレインソース間電流Idsが減少しており、ビット線間の電位差をセンスアンプで増幅するのに十分なセンスマージンを確保するのが難しくなってきている。

この問題に対して、NチャネルMOSトランジスタNchTrの閾値電圧Vtを低下させる手段が考えられるが、この場合、アクティブスタンバイ時のチャネル間リーク電流が増加する方向となるため、オフ電流Ioffの増加が懸念される。

また、特許文献1に記載の技術は、参照電位の調整のために補助セルアレイを設けたり、または、予備ワード線を設けたりする必要があり、回路およびレイアウトの規模が大きくなったり、制御が複雑になることが懸念される。

上記目的を達成するために本発明の半導体記憶装置は、

互いに相補なビット線間の電位差を増幅するセンスアンプを備え、

アドレス入力によりワード線が活性化し、メモリセルに保持されているデータに応じて前記相補なビット線の一方のビット線の電位が変化した後、前記センスアンプが活性化される前に前記相補なビット線の電位を共に上昇させる電位上昇手段を備えることを特徴とする。

互いに相補なビット線間の電位差を増幅するセンスアンプを備え、

アドレス入力によりワード線が活性化し、メモリセルに保持されているデータに応じて前記相補なビット線の一方のビット線の電位が変化した後、前記センスアンプが活性化される前に前記相補なビット線の電位を共に上昇させる電位上昇手段を備えることを特徴とする。

この様に、互いに相補なビット線間の電位差を増幅するセンスアンプを備えており、メモリセルに保持されているデータに応じて相補なビット線の一方のビット線の電位が変化した後、センスアンプが活性化される前に相補なビット線の電位を共に上昇させる電位上昇手段を備えている。

そのため、メモリセルからのデータの読み出しに基づくビット線間電位差の増幅時に、センスアンプを構成するNチャネルMOSトランジスタNchTrのゲート・ソース間電位Vgsおよびドレインソース間電位Vdsが大きくなり、NチャネルMOSトランジスタNchTrのドレインソース間電流Idsが増加するため、NチャネルMOSトランジスタNchTrの閾値電圧Vtを低下させなくても十分なセンスマージンを確保することが出来る。

本発明は、従来より半導体記憶装置が備えているダミーワード線を用いて構成することが可能であり、大幅なハードウェアの追加を必要とせず効果的にセンスマージンの拡大を図れるものである。

以下に、本発明を実施するための最良の形態について図面を参照して説明する。

(第1の実施形態)

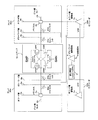

図1は、本発明の半導体記憶装置の第1の実施形態の構成を示すブロック図である。

図1は、本発明の半導体記憶装置の第1の実施形態の構成を示すブロック図である。

なお、図1におけるアレイ30aには、本来、多数の本ワード線3aと一端が夫々センスアンプ1に接続される多数のビット線BLB2aとが格子状に配置され、その交点にはデータを記憶するメモリセルが設けられる。また、アレイ30bにも、多数の本ワード線3bと一端が夫々センスアンプ1に接続される多数のビット線BLT2bとが格子状に配置され、その交点にはデータを記憶するメモリセルが設けられる。しかし、図1ではセンスアンプを1つのみ表し、その両側に配置されるアレイ30a及び30bの構成についても、本ワード線1本と、センスアンプに一端が接続されるビット線1本で代表させている。

図1に示すように、本実施形態の半導体記憶装置においては、センスアンプ1にビット線BLB2aおよびビット線BLT2bが接続されており、ビット線BLB2aと交差するように本ワード線3aが配置され、ビット線BLT2bと交差するように本ワード線3bが配置されている。また、ビット線BLB2aと本ワード線3aの交点にはメモリセル4aが設けられ、ビット線BLT2bと本ワード線3bの交点にメモリセル4bが設けられている。さらに、本ワード線3aと並行してダミーワード線5a,5bが配置され、本ワード線3bと並行してダミーワード線5c,5dが配置されている。また、ビット線BLB2aと、本ワード線3aと、メモリセル4aと、ダミーワード線5a,5bとによりアレイ30aが構成され、ビット線BLT2bと、本ワード線3bと、メモリセル4bと、ダミーワード線5c,5dとによりアレイ30bが構成されている。また、ダミーワード線5a〜5dはダミーワード線駆動部6に接続されており、本ワード線3a,3bは行デコーダ35a,35bの一部を構成する本ワード線駆動部7a,7bに接続されている。また、ダミーワード線駆動部6には、本ワード線駆動部7a,7bと同様に、外部から供給された電源電圧VDD(例えば1.5V)を昇圧電源9で昇圧した昇圧電位VPP(例えば2.6V)が供給されている。そして制御信号8によりダミーワード線駆動部6が活性化されると、その昇圧電源9で昇圧した昇圧電位VPPをダミーワード線5a〜5dに供給する。

なお、本発明におけるビット線の電位上昇手段は、ダミーワード線駆動部6とダミーワード線5a〜5dとを含んで構成される。

また、ダミーワード線5a〜5dは、センスアンプ1と本ワード線3a,3bとの間に配置されている。これは、アレイ30a,30bのセンスアンプ1と接する側のアレイ端、つまりビット線BLB2a、ビット線BLT2bがセンスアンプ1に接続される位置に隣接する領域では、セルアレイの繰り返しが途切れる為、露光装置等の形状に対する粗密の影響によりワード線やコンタクト等の形状が崩れ易い。その対策として、アレイ端に本ワード線の形状確保用のダミーワード線5a〜5dを配置することで、本ワード線3a,3bに形状不良が生じるのを防ぐためである。通常、アレイ端にはこの様なダミーワード線が2〜4本程度配置される。

ビット線BLB2aとビット線BLT2bとは、互いに相補を成すビット線対を構成している。ビット線BLB2aおよびビット線BLT2bは、メモリセル4a,4bからのデータ読出し前に参照電位VBLP(例えば、0.55V)にプリチャージされる。

メモリセル4a,4bは、‘1’もしくは‘0’に対応するデータを記憶するために、それらに対応付けられた高電位Hもしくは低電位Lを保持する。

本ワード線駆動部7a,7bは、メモリセル4a,4bからのデータの読出しの際に対応する本ワード線3a,3bを駆動し、対応するメモリセル4a,4bに保持されている電位に基づいてビット線BLB2a又はビット線BLT2bの電位を変化させる。

ダミーワード線5aとビット線BLB2aとの間には寄生容量(静電容量)20aが存在し、ダミーワード線5bとビット線BLB2aとの間には寄生容量(静電容量)20bが存在している。また、ダミーワード線5cとビット線BLT2bとの間には寄生容量(静電容量)20cが存在し、ダミーワード線5dとビット線BLT2bとの間には寄生容量(静電容量)20dが存在している。なお、これらダミーワード線とビット線との間に容量素子を設けてキャパシタ20a〜20dとしても良い。また、ダミーワード線駆動部6が活性化される前の非駆動時においては、ダミーワード線5a〜5dの電位は低レベル電位の0V或いは負電圧(例えば、−0.4V)とされている。そして、本ワード線駆動部7a(又は7b)には、外部から供給された電源電圧VDD(例えば1.5V)を昇圧電源9で昇圧した昇圧電位VPPが供給されている。

アドレスが入力されて行デコーダ35aにより本ワード線駆動部7a(又は7b)が本ワード線3a(又は3b)を高レベル電位H(例えば、VPP:2.6V)とし、メモリセル4a(又はメモリセル4b)からのデータの読み出しによりビット線BLB2a(又はビット線BLT2b)の電位が変化する。一般的には、続いて、センスアンプ1のNチャネルMOSトランジスタソース電位SAN及びPチャネルMOSトランジスタソース電位SAPが印加されてセンスアンプ1が活性化される。しかし、ここでは、センスアンプ1が活性化されてビット線BLB2aとビット線BLT2bとの間の電位差の増幅が開始される前に、制御信号8によりダミーワード線駆動部6が活性化され、ダミーワード線駆動部6はダミーワード線5a〜5dを同時に駆動し、それらの電位を低レベル電位である0Vから高レベル電位VPP(例えば、2.6V)に引き上げる。これにより、ビット線BLB2aおよびビット線BLT2bの電位が、寄生容量20a〜20dを介した容量性カップリングにより互いにほぼ同じ値分引き上げられる。つまり、各ビット線の電位変化はほぼ同じとなる。

ここで、アクティブコマンドと共にアドレス(ロウアドレス)が入力され、ロウアドレス系が活性化されてから所定の遅延時間後に、上記制御信号8が、例えば低レベル電位から高レベル電位(VDDレベル)に変化することで、ダミーワード線駆動部6が活性化される。

なお、本実施形態においては、1つのダミーワード線駆動部6が、ダミーワード線5a〜5dを全て駆動している。しかし、複数のダミーワード線駆動部6で駆動してもよい。この場合、ビット線BLB2aおよびビット線BLT2bの電位を期待する程度に十分引き上げることが出来るように、アレイ30aのビット線BLB2aに交差するダミーワード線の本数と、アレイ30bのビット線BLT2bに交差するダミーワード線の本数とを同数となる条件で調整し、複数のダミーワード線駆動部6を準備して駆動してもよい。

また、アレイ30aとアレイ30bとで同数のダミーワード線本数とし、アレイ30aのダミーワード線とアレイ30bのダミーワード線とを、夫々別個のダミーワード線駆動部6により駆動する構成としてもよい。

さらに、各アレイにおいて、同数本のダミーワード線ずつ複数組に分け、各組毎にダミーワード線駆動部6を準備して駆動する構成としてもよい。

図1のように、センスアンプ1は、NチャネルMOSトランジスタNchTr11a,11bと、PチャネルMOSトランジスタPchTr12a,12bとを備えて構成されている。ダミーワード線駆動部6によりビット線BLB2aおよびビット線BLT2bの電位が引き上げられた後、センスアンプ1のNチャネルMOSトランジスタソース電位SANが先行して印加され、NチャネルMOSトランジスタNchTr11a,11bが活性化され増幅を開始する。そして、その所定時間後にPチャネルMOSトランジスタソース電位SAPが印加され、PチャネルMOSトランジスタPchTr12a,12bが活性化されてセンスアンプ1全体が活性化される。これにより、メモリセル4a,4bからのデータの読出しにより生じたビット線BLB2aとビット線BLT2bとの間の電位差を増幅する。

具体的には、データ読み出しが行われると、メモリセルに保持されていた高電位Hまたは低電位Lに基づいてビット線BLB2a又はビット線BLT2bに僅かな電位変化(プリチャージ電位である参照電位VBLPからSAP側又はSAN側のいずれかへ変化)が生じ、この電位変化をセンスアンプ1の活性化により増幅する。そして、最終的に、メモリセル4a,4bからの読み出しデータに応じて、ビット線BLB2a及びビット線BLT2bの一方の電位はPチャネルMOSトランジスタソース電位SAPまで増幅され、その他方の電位はNチャネルMOSトランジスタソース電位SANまで増幅される。その結果、ビット線BLB2aとビット線BLT2bとのビット線間の電位差は、SAP−SANの値まで増幅されている。 以下に、本実施形態の半導体記憶装置の動作について説明する。

図2は、図1に示した半導体記憶装置の動作を説明する図である。なお、図2においては、横軸は経過時間を、縦軸はダミーワード線5a〜5dやビット線BLB2a、ビット線BLT2b等の電位をそれぞれ示している。

ここでは、図1に示したメモリセル4aに低電位Lが保持されている状態において、メモリセル4aからデータを読み出す場合の本実施形態の半導体記憶装置の動作について説明する。

図2に示すように、ビット線BLB2a、ビット線BLT2bが参照電位VBLP(例えば、0.55V)にプリチャージされている状態において、入力されたアドレス(ロウアドレス)に基づいてタイミングT0でロウアドレス系が活性化され、行デコーダ35aにより本ワード線駆動部7aが本ワード線3aを高レベル電位Hとする。これにより、メモリセル4aからビット線BLB2aにデータの読出しが行われてビット線BLB2aの電位が低下し、ビット線BLT2bとの間に電位差が生じる。

なお、本ワード線3aの高レベル電位Hは、前記したように電源電圧VDDを昇圧したVPP(例えば、2.6V)のレベルとしても良いし、電源電圧VDD(例えば、1.5V)そのものレベルとしても良い。

ロウアドレス系が活性化してビット線間に電位差が生じた後、タイミングT1で、制御信号8を、例えば低レベル電位(0V)から高レベル電位(VDD:例えば1.5V)に変化させることで、ダミーワード線駆動部6を活性化する。活性化されたダミーワード線駆動部6が、ダミーワード線5a〜5dを駆動し、ダミーワード線5a〜5dの電位を低レベル電位の0Vから昇圧電源9の出力である昇圧電位VPP(例えば、2.6V)の高レベル電位に引き上げる。

このとき、寄生容量20a〜20dを介したダミーワード線5a〜5dとの容量性カップリングにより、ビット線BLB2a及びビット線BLT2bの電位がタイミングT1以前の電位よりも高電位に引き上げられる。なお、図2に示すように、このとき、ビット線BLB2a、ビット線BLT2bに対してそれぞれ同数のダミーワード線5a〜5dの電位が同時に高レベル電位に引き上げられるため、ビット線BLB2a及びビット線BLT2bの電位は互いにほぼ同じ値分引き上げられる。

次に、センスアンプ1において、ビット線BLB2aおよびビット線BLT2bの電位が引き上げられた後のタイミングT2でNチャネルMOSトランジスタソース電位SANが印加され(例えば、0V)、NチャネルMOSトランジスタNchTr11a,11bが活性化される。このとき、NチャネルMOSトランジスタNchTr11aのソース電位はNチャネルMOSトランジスタソース電位SANに、ゲート電位はビット線BLT2bの電位に、ドレイン電位はビット線BLB2aの電位になる。また、NチャネルMOSトランジスタNchTr11bのソース電位はNチャネルMOSトランジスタソース電位SANに、ゲート電位はビット線BLB2aの電位に、ドレイン電位はビット線BLT2bの電位になる。

そのため、ビット線BLB2aおよびビット線BLT2bの電位の引き上げを行わない場合と比較して、容量性カップリングにより引き上げられた値分だけNチャネルMOSトランジスタNchTr11a,11bのゲート・ソース間電位差Vgsおよびドレインソース間電位差Vdsが大きくなり、ドレインソース間電流Idsを増加することが出来る。

なお、図2においては、ダミーワード線5a〜5dの高レベル電位として、電源電圧VDD(例えば、1.5V)を昇圧電源9により昇圧した昇圧電位VPP(例えば、2.6V)を使用している。ダミーワード線5a〜5dの高レベル電位として昇圧電位VPPを使用する場合、電源電圧VDDからの変換効率により消費電流が大きくなりやすいため、昇圧電源9を取り除き、電源電圧VDDをそのまま高レベル電位として使用しても良い。この場合、昇圧電位VPPを使用する場合よりも容量性カップリングによるビット線電位の引き上げ効果が小さくなる可能性があるため、配置するダミーワード線の本数を増やし、ダミーワード線駆動部6が駆動するダミーワード線の本数を増やす手段もある。

なお、図2には図示していないが、NチャネルMOSトランジスタソース電位SANが印加されてセンスアンプ1のNチャネルMOSトランジスタNchTr11a,11bが活性化されて増幅を開始した後、PチャネルMOSトランジスタソース電位SAPが印加されてセンスアンプ1のPチャネルMOSトランジスタPchTr12a,12bが活性化される。これにより、PチャネルMOSトランジスタPchTr12a,12bによる増幅も開始されることになる。

上述したように、本実施形態の半導体記憶装置においては、ダミーワード線駆動部6は、メモリセルからのデータ読出しにより生じたビット線BLB2aとビット線BLT2bとの間の電位差をセンスアンプ1で増幅する前に、ダミーワード線5a〜5dを駆動することで、ビット線BLB2a、ビット線BLT2bの電位を互いにほぼ同じ値分だけ引き上げることができる。

そのため、NチャネルMOSトランジスタソース電位SANが印加されてセンスアンプ1を構成するNチャネルMOSトランジスタNchTr11a,11bが活性化して増幅を開始する際に、これらNチャネルMOSトランジスタNchTr11a,11bのゲート・ソース間電位Vgsおよびドレインソース間電位Vdsが大きくなり、NチャネルMOSトランジスタNchTr11a,11bのドレインソース間電流Idsが増加する。これにより、センスアンプ1を構成するPチャネルMOSトランジスタPchTr12a,12bが増幅を開始する時に、これらPチャネルMOSトランジスタのうち少なくとも一方のPチャネルMOSトランジスタのゲート・ソース間電位Vgsが、これら2つのPチャネルMOSトランジスタ間の閾値電圧Vtのアンバランス以上の値に達することが容易となる。

このため、NチャネルMOSトランジスタNchTrの閾値電圧Vtを低下させなくても十分なセンスマージンを確保することが出来る。

(第2の実施形態)

本発明の半導体記憶装置の第2の実施形態は、第1の実施形態と比較して、本ワード線とダミーワード線の配置が異なる。

本発明の半導体記憶装置の第2の実施形態は、第1の実施形態と比較して、本ワード線とダミーワード線の配置が異なる。

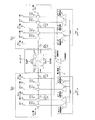

図3は、本発明の半導体記憶装置の第2の実施形態の構成を示すブロック図である。

図3に示すように、本実施形態の半導体記憶装置においては、センスアンプ1にビット線BLB2aおよびビット線BLT2bが接続されており、ビット線BLB2aと交差するように本ワード線3c〜3fが配置され、ビット線BLB2bと交差するように本ワード線3g〜3jが配置されている。また、ビット線BLB2aと本ワード線3c〜3fの交点にはそれぞれメモリセル4c〜4fが設けられ、ビット線BLT2bと本ワード線3g〜3jの交点にはそれぞれメモリセル4g〜4jが設けられている。また、本ワード線3c〜3fと並行してダミーワード線5e,5fが配置され、本ワード線3g〜3jと並行してダミーワード線5g,5hが配置されている。また、ビット線BLB2aと、本ワード線3c〜3fと、メモリセル4c〜4fと、ダミーワード線5e,5fとを備えてアレイ30cが構成され、ビット線BLT2bと、本ワード線3g〜3jと、メモリセル4g〜4jと、ダミーワード線5g,5hとを備えてアレイ30dが構成されている。また、ダミーワード線5e〜5hはダミーワード線駆動部6に接続されており、本ワード線3c〜3jは行デコーダ35c,35dの一部を構成する本ワード線駆動部7c〜7jに夫々接続されている。また、本ワード線駆動部7c〜7jと同様に、ダミーワード線駆動部6には、外部から供給された電源電圧VDD(例えば、1.5V)を昇圧電源9で昇圧した昇圧電位VPP(例えば、2.6V)が供給されている。そして制御信号8によりダミーワード線駆動部6が活性化されると、その昇圧電源9で昇圧した昇圧電位VPPをダミーワード線5a〜5dに供給する。

なお、本実施形態の半導体記憶装置においては、アレイ30c,30d内において本ワード線3c〜3j及びダミーワード線5e〜5hをビット線方向に等間隔に配置することで、アレイ30c,30d内の粗密を無くし規則性を維持している。特に、2本の本ワード線3c、3d(3g、3h)と1本のダミーワード線5e(5g)を一組とし、2本の本ワード線3e、3f(3i、3j)と1本のダミーワード線5f(5h)を他の一組としてビット線方向に等間隔で配置する本実施形態の構成は、6F2セル(本例ではワード線方向が3Fピッチ、ビット線方向が2Fピッチ)の設計ルールにおいてアレイ30c,30d内の粗密を無くし規則性を維持するのに適している。また、本実施形態においては、2本の本ワード線と1本のダミーワード線を一組としてビット線方向に等間隔で配置している。しかし、ビット線BLB2aおよびビット線BLT2bに対して同数の本ワード線と同数のダミーワード線が配置されていれば、アレイ30c,30dの各アレイに等間隔で配置される本ワード線の本数およびダミーワード線の本数は任意の本数でよい。

各構成要素の動作については、図1に示した第1の実施形態の半導体記憶装置の同様の構成要素と同じであるため説明を割愛する。

図4は、図3に示した半導体記憶装置の変形例の構成を示すブロック図である。

図4に示すように、本変形例の半導体記憶装置においては、センスアンプ1にビット線BLB2aおよびビット線BLT2bが接続されており、ビット線BLB2aと交差するように本ワード線3c〜3fが配置され、ビット線BLB2bと交差するように本ワード線3g〜3jが配置されている。また、ビット線BLB2aと本ワード線3c〜3fの交点にはそれぞれメモリセル4c〜4fが設けられ、ビット線BLT2bと本ワード線3g〜3jの交点にはそれぞれメモリセル4g〜4jが設けられている。また、本ワード線3c〜3fと並行してダミーワード線5a,5b,5e,5fが配置され、本ワード線3g〜3jと並行してダミーワード線5c,5d,5g,5hが配置されている。また、ビット線BLB2aと、本ワード線3c〜3fと、メモリセル4c〜4fと、ダミーワード線5a,5b,5e,5fとを備えてアレイ30eが構成され、ビット線BLT2bと、本ワード線3g〜3jと、メモリセル4g〜4jと、ダミーワード線5c,5d,5g,5hとを備えてアレイ30fが構成されている。また、ダミーワード線5a〜5hはダミーワード線駆動部6に接続されており、本ワード線3c〜3jは行デコーダ35e,35fの一部を構成する本ワード線駆動部7c〜7jに夫々接続されている。また、本ワード線駆動部7c〜7jと同様に、ダミーワード線駆動部6には、外部から供給された電源電圧VDD(例えば、1.5V)を昇圧電源9で昇圧した昇圧電位VPP(例えば、2.6V)が供給されている。制御信号8によりダミーワード線駆動部6が活性化されると、その昇圧電位VPPをダミーワード線5a〜5hに供給する。

なお、本変形例においては、図3に示した半導体記憶装置と比較して、図1に示した第1の実施形態の半導体記憶装置と同様にアレイ30e,30fのセンスアンプ1側のアレイ端にダミーワード線5a〜5dを配置している点が異なる。この様にすることで、アレイ端での本ワード線3c〜3jの形状不良を防ぎつつ、アレイ30e,30f内の粗密を無くし規則性を維持することができる。

(第3の実施形態)

本発明の半導体記憶装置の第3の実施形態は、第1、第2の実施形態と比較して、ビット線とダミーワード線の間に大きな静電容量(キャパシタとも言う)を得るためにダミーワード線に隣接してビットコンタクトを設ける点が異なる。

本発明の半導体記憶装置の第3の実施形態は、第1、第2の実施形態と比較して、ビット線とダミーワード線の間に大きな静電容量(キャパシタとも言う)を得るためにダミーワード線に隣接してビットコンタクトを設ける点が異なる。

図5は、本発明の半導体記憶装置の第3の実施形態の構成を示す図である。図5(a)は半導体記憶装置のアレイ30gの上面図を示しており、図5(b)は図5(a)のビット線上での断面図を示している。なお、図5(a)(b)においては、作図の都合上、各センスアンプ1に接続されるビット線対の一方のビット線2cを含むアレイ30gのみを記載し、他方のビット線を含むアレイや本ワード線駆動部、ダミーワード線駆動部、昇圧電源等を省略している。

図5(a)に示すように、本実施形態の半導体記憶装置においては、アレイ30gのセンスアンプ1側のアレイ端からビット線の延在方向に対して、4本のダミーワード線5j〜5mと、2本の本ワード線3k,3lと、ダミーワード線5iと、が等間隔で配置されている。また、2本の本ワード線3k,3lの間にビットコンタクト40aが設けられ、更に、ビット線とダミーワード線の間に大きな静電容量を得るため、アレイ端に配置された互いに隣接する2本のダミーワード線5k,5lの間にビットコンタクト40bが設けられている。

図6は、図5(b)に示したA部の拡大図である。

図6に示すように、ビット線2cとビットコンタクト40bとが直接接続されて電気的な導通が取られており、また、ビットコンタクト40bとその両隣のダミーワード線5k,5lとが絶縁膜50a,50bを介して静電容量を形成している。この様にビットコンタクト40bを設けることにより、ダミーワード線5k,5lとビット線2cとの間の間隔よりも、ダミーワード線5k,5lとビットコンタクト40bとの間隔の方が短くなる。それによりダミーワード線5k,5lとビット線2cとの間で得られる静電容量(寄生容量)20i,20jよりも大きな静電容量20k,20lをダミーワード線5k,5lとビットコンタクト40bとの間で得ることができる。

この構成において、図2のビット線間に電位差が生じたタイミングT1で制御信号8によりダミーワード線駆動部6を活性化して電源電圧VDDを昇圧電源9で昇圧した昇圧電位VPP(例えば、2.6V)をダミーワード線5i〜5mに供給し、ダミーワード線5i〜5mの電位を低レベル電位の0Vから高レベル電位VPPに引き上げる。このとき、大きな静電容量20k、20lを介したダミーワード線5k〜5lとの容量性カップリングにより、効果的にビット線2cの電位がタイミングT1以前の電位よりも高電位に引き上げられる。このように、ダミーワード線5k,5lを駆動した際に、ダミーワード線5k,5lとビットコンタクト40bとの間で大きな容量性カップリングの効果を得ることができ、ビットコンタクト40bを設けない場合よりもビット線2cの電位をより高い電位に引き上げることができる。

なお、図6においては、大きな静電容量20k,20lを得るため、ビットコンタクト40bとダミーワード線5k,5lの夫々に、絶縁膜50a、50bを介して対向する凸部を設けている。しかしながら、ビットコンタクト40b又はダミーワード線5k,5lのいずれか一方のみに凸部を設けても良いし、凸部を設けなくても良い。ビットコンタクト40bとダミーワード線5k,5lとの間隔は、製造プロセスに依存する最小設計寸法およびダミーワード線の駆動電位(高レベル電位)等を考慮しながら、ビット線の電位引き上げ値が所望の値となるように調節すれば良い。

また、本実施形態においては、ビットコンタクト40bをアレイ30gのセンスアンプ1側のアレイ端に配置されるダミーワード線5k,5lの間に配置しているが、これは、ビットコンタクト40bをセンスアンプ1に近い位置に配置したほうが、より大きなビット線2cの電位の引き上げ効果が期待できるためである。

なお、図1に示した第1の実施形態の半導体記憶装置においても、本実施形態のようにアレイ端に配置されたダミーワード線5a、5bおよびダミーワード線5c,5dの間にビットコンタクトを設けることで同様の効果を得ることができる。

1 センスアンプ

2a〜2c ビット線

3a〜3l 本ワード線

4a〜4j メモリセル

5a〜5m ダミーワード線

6 ビット線駆動部

7a〜7j 本ワード線駆動部

8 制御信号

9 昇圧電源

11a,11b NチャネルトランジスタNchTr

12a,12b PチャネルトランジスタPchTr

20a〜20l 静電容量(キャパシタ)

30a〜30g アレイ

35a〜35f 行デコーダ

40a,40b ビットコンタクト

50a,50b 絶縁膜

2a〜2c ビット線

3a〜3l 本ワード線

4a〜4j メモリセル

5a〜5m ダミーワード線

6 ビット線駆動部

7a〜7j 本ワード線駆動部

8 制御信号

9 昇圧電源

11a,11b NチャネルトランジスタNchTr

12a,12b PチャネルトランジスタPchTr

20a〜20l 静電容量(キャパシタ)

30a〜30g アレイ

35a〜35f 行デコーダ

40a,40b ビットコンタクト

50a,50b 絶縁膜

Claims (8)

- 互いに相補なビット線間の電位差を増幅するセンスアンプと、

アドレス入力によりワード線が活性化し、メモリセルに保持されているデータに応じて前記相補なビット線の一方のビット線の電位が変化した後、前記センスアンプが活性化される前に前記相補なビット線の電位を共に上昇させる電位上昇手段とを備えることを特徴とする半導体記憶装置。 - 請求項1に記載の半導体記憶装置において、

前記センスアンプの活性化の際に、前記センスアンプに対して低電位電源が印加された後に高電位電源が印加される、半導体記憶装置。 - 請求項1又は請求項2に記載の半導体記憶装置において、

前記電位上昇手段が、ダミーワード線の電位遷移時における前記ダミーワード線と前記ビット線との容量性カップリングを用いるものである、半導体記憶装置。 - 請求項1又は請求項2に記載の半導体記憶装置において、

前記ビット線に電気的導通を有するビットコンタクトが、絶縁層を介してダミーワード線と隣接して設けられ、

前記電位上昇手段が、前記ダミーワード線の電位遷移時における前記ダミーワード線と前記ビットコンタクトとの容量性カップリングを用いるものである、半導体記憶装置。 - 請求項4に記載の半導体記憶装置において、

前記ビットコンタクトが、互いに並行する前記ダミーワード線の間に設けられている、半導体記憶装置。 - 請求項5に記載の半導体記憶装置において、

前記互いに並行するダミーワード線が、前記センスアンプと該センスアンプに最も近く配置された本ワード線との間に設けられている、半導体記憶装置。 - 請求項3乃至請求項6のいずれか1項に記載の半導体記憶装置において、

前記相補なビット線の夫々に同じ本数の前記ダミーワード線が交差して設けられている、半導体記憶装置。 - 互いに相補なビット線間の電位差を増幅するセンスアンプを備え、

アドレス入力によりワード線を活性化し、メモリセルに保持されているデータに応じて前記相補なビット線の一方のビット線の電位を変化させる第1のステップと、

前記第1のステップの後、前記センスアンプが活性化される前に前記相補なビット線の電位を共に上昇させる第2のステップと、を含むことを特徴とする半導体記憶装置の制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008319643A JP2010146601A (ja) | 2008-12-16 | 2008-12-16 | 半導体記憶装置及びその制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008319643A JP2010146601A (ja) | 2008-12-16 | 2008-12-16 | 半導体記憶装置及びその制御方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010146601A true JP2010146601A (ja) | 2010-07-01 |

Family

ID=42566885

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008319643A Pending JP2010146601A (ja) | 2008-12-16 | 2008-12-16 | 半導体記憶装置及びその制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010146601A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010218671A (ja) * | 2009-03-19 | 2010-09-30 | Renesas Electronics Corp | 半導体記憶装置 |

-

2008

- 2008-12-16 JP JP2008319643A patent/JP2010146601A/ja active Pending

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010218671A (ja) * | 2009-03-19 | 2010-09-30 | Renesas Electronics Corp | 半導体記憶装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8169847B2 (en) | Semiconductor memory apparatus and refresh control method of the same | |

| US7492632B2 (en) | Memory array having a programmable word length, and method of operating same | |

| US7733693B2 (en) | Semiconductor memory device and method of operating same | |

| CN1197089C (zh) | 半导体器件 | |

| KR101096225B1 (ko) | 반도체 메모리 장치 및 그 구동방법 | |

| US7345938B2 (en) | Semiconductor device | |

| JP2007305231A (ja) | 半導体記憶装置 | |

| JP2005302234A (ja) | 半導体記憶装置 | |

| JP2003228981A (ja) | 半導体記憶装置 | |

| JP2015170379A (ja) | 半導体装置 | |

| CN1983445A (zh) | 包括浮体晶体管无电容器存储单元的存储器件及相关方法 | |

| JP5068615B2 (ja) | 半導体装置 | |

| JP2016091573A (ja) | 半導体記憶装置 | |

| KR20090009699A (ko) | 커패시터가 없는 동적 메모리 셀을 구비한 반도체 메모리장치, 이 장치를 위한 동적 메모리 셀, 및 이 장치를구비한 메모리 시스템 | |

| US20160099041A1 (en) | Semiconductor Device | |

| US6324111B1 (en) | Semiconductor memory | |

| US6973002B2 (en) | Semiconductor integrated circuit comprising sense amplifier activating circuit for activating sense amplifier circuit | |

| JP2010146601A (ja) | 半導体記憶装置及びその制御方法 | |

| US20100103758A1 (en) | Semiconductor memory device having sense amplifier | |

| US7542364B2 (en) | Semiconductor memory device | |

| US9443573B2 (en) | Semiconductor device including main amplifers between memory cell arrays | |

| US8553483B2 (en) | Semiconductor memory device | |

| KR100927396B1 (ko) | 반도체 메모리 장치 | |

| KR100945789B1 (ko) | 서브 워드라인 드라이버 및 이를 포함하는 반도체 메모리장치 | |

| JP3686951B2 (ja) | 半導体記憶装置 |