JP2010141246A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2010141246A JP2010141246A JP2008318392A JP2008318392A JP2010141246A JP 2010141246 A JP2010141246 A JP 2010141246A JP 2008318392 A JP2008318392 A JP 2008318392A JP 2008318392 A JP2008318392 A JP 2008318392A JP 2010141246 A JP2010141246 A JP 2010141246A

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- single crystal

- substrate

- hydrogen ion

- ion implantation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Element Separation (AREA)

Abstract

【課題】加熱による不具合の発生を回避した半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置1の製造方法は、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部41が形成されているSi基板を用いてSi薄膜トランジスタを形成しており、水素イオン注入部41にマイクロ波M1を照射して水素イオン注入部41を熱処理する照射工程と、照射工程の後、水素イオン注入部41においてSi基板を劈開剥離して、酸化膜、ゲートパターンおよび不純物イオン注入部を有するSi薄膜を分離する剥離工程と、Si薄膜を絶縁基板上に接合する接合工程とを含む。

【選択図】図1

【解決手段】本発明に係る半導体装置1の製造方法は、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部41が形成されているSi基板を用いてSi薄膜トランジスタを形成しており、水素イオン注入部41にマイクロ波M1を照射して水素イオン注入部41を熱処理する照射工程と、照射工程の後、水素イオン注入部41においてSi基板を劈開剥離して、酸化膜、ゲートパターンおよび不純物イオン注入部を有するSi薄膜を分離する剥離工程と、Si薄膜を絶縁基板上に接合する接合工程とを含む。

【選択図】図1

Description

本発明は、半導体装置の製造方法に関し、詳細には、Si薄膜デバイスが形成される半導体装置の製造方法に関する。

従来、ガラス基板上に形成された非晶質Siまたは多結晶Siの薄膜トランジスタ(Thin Film Transistor、以下、TFTと記す)により、液晶表示パネルおよび有機ELパネル等の駆動を行う液晶表示装置が使用されている。

とりわけ、移動度が高く高速で動作する多結晶Siを用いて周辺ドライバを集積化したものが用いられるようになっている。しかしながら、多結晶Siでは、結晶性の不完全性に起因するギャップ内の局在準位や結晶粒界付近の欠陥、ギャップ内局在準位に起因する移動度の低下やS係数(サブスレショルド係数)の増大のため、高性能なSiのデバイスを形成するには、トランジスタの性能が充分ではない。そのため、さらに高い性能が要求されるイメージプロセッサおよびタイミングコントローラ等のシステム集積化のためには、より高性能なSiデバイスが求められている。

そこで、さらに高性能なSiのデバイスを形成するため、単結晶Si薄膜からなる薄膜トランジスタ等のデバイスを予め形成し、これを絶縁基板上に貼り付けて半導体装置を形成する技術が研究されてきている(例えば、特許文献1,2および非特許文献1,2参照)。

特表平7−503557号公報(1995年4月13日公表)

特開2004−165600号公報(2004年6月10日公開)

J.P.Salerno "Single Crystal Silicon AMLCDs",Conference Record of the 1994 International Display Research Conference(IDRC), 1994, 39-44

Q.-Y.Tong & U.Gesele, SEMICONDUCTOR WAFER BONDING : SCIENCE AND TECHNOLOGY, John Wiley & Sons, New York, 1999

特許文献1には、予め別に作製した単結晶Si薄膜トランジスタを、接着剤を用いてガラス基板上に転写した半導体装置を使用して、アクティブマトリクス型液晶表示装置の表示パネルのディスプレイを作製する技術が開示されている。

しかしながら、上記特許文献1に記載の半導体装置の製造方法では、高性能なデバイスである単結晶Si薄膜トランジスタを、ガラス基板上に貼り合わせるために接着剤を使用しているため、貼り付け作業が面倒で、生産性が悪い等の問題点を有している。また、完成した半導体装置についても、接着剤による接合であるため、耐熱性に問題があり、以降に高品質の無機絶縁膜やTFTの形成等は不可能である。そのため、アクティブマトリクス基板を製造する場合、TFTアレイを含むデバイスを形成した後で、使用する基板に貼り付ける必要があり、サイズコスト、配線形成の点に大きな問題があった。

上記特許文献2に開示されている技術によれば、この問題を解決することができる。しかしながら、耐熱性の観点から、より信頼性が高く、より安全性の高いプロセスの構築が望まれている。

そこで、本発明は上記の問題点に鑑みてなされたものであり、その目的は、加熱による不具合の発生を回避した半導体装置の製造方法を提供することにある。

本発明に係る半導体装置の製造方法は、上記課題を解決するために、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部が形成されているSi基板を用いてSi薄膜デバイスを形成する、半導体装置の製造方法であって、上記水素イオン注入部にマイクロ波を照射して上記水素イオン注入部を熱処理する照射工程と、上記照射工程の後、上記水素イオン注入部において上記Si基板を劈開剥離して、上記酸化膜、上記ゲートパターンおよび上記不純物イオン注入部を有するSi薄膜を分離する剥離工程と、上記Si薄膜を絶縁基板上に接合する接合工程とを含む構成である。

上記構成によれば、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有しており、表面から所定の深さに水素イオン注入部が形成されているSi基板を用いて半導体装置を形成する場合において、まず、その水素イオン注入部においてSi基板を劈開剥離する。劈開剥離されたSi基板のうち、酸化膜、ゲートパターンおよび不純物イオン注入部を有しているSi薄膜を絶縁基板上に接合する。これにより、Si薄膜デバイスに含まれる構成が絶縁基板上に形成される。

ここで、水素イオン注入部においてSi基板を劈開剥離するために、水素イオン注入部にマイクロ波を照射して、水素イオン注入部に熱処理を施している。マイクロ波を水素イオン注入部に照射することにより、水素イオン注入部のみを加熱する。すなわち、水素イオン注入部以外の部分が加熱されることを防止することができる。そのため、水素イオン注入部以外の部分に含まれているアルミニウムなどの配線材料が昇温により溶断するといった不具合の発生を回避することができる。したがって、信頼性および安全性により優れた、半導体装置の製造方法を提供できる。

また、本発明に係る半導体装置の製造方法において、上記マイクロ波は、集束マイクロ波であることが好ましい。

上記構成によれば、水素イオン注入部に照射されるマイクロ波は集束したマイクロ波であるため、水素イオン注入部以外の近傍部分にマイクロ波が照射されることを、より確実に防ぐことができる。そのため、水素イオン注入部以外の部分に設けられている配線材料が熱により溶断するといった不具合の発生を、より確実に抑えることができる。

また、本発明に係る半導体装置の製造方法において、上記照射工程および上記剥離工程は、上記Si基板を上記絶縁基板とは異なる支持台に固定して行うことが好ましい。

上記構成によれば、Si薄膜デバイスを形成する絶縁基板上ではマイクロ波照射および剥離操作を行わず、Si基板を別の支持体に固定してマイクロ波照射および剥離操作を行う。そのため、絶縁基板上の他の構成要素が汚染したり、損傷を受けたりすることを防止することができる。

また、本発明に係る半導体装置の製造方法において、上記接合工程では、上記Si薄膜を上記絶縁基板上に接合するよりも前に、上記絶縁基板上における上記Si薄膜と接合させる領域を、ハロゲン化物のガス・クラスター・イオン・ビームにより平坦化することが好ましい。

上記構成によれば、ハロゲン化物のガス・クラスター・イオン・ビーム(GCIB:Gas Cluster Ion Beam)を照射することにより、Si薄膜が接合される領域に対してエッチングが行われ、表面のマイクロラフネスが改善される。そのため、接合の効率を大幅に向上させることができる。

本発明に係る半導体装置の製造方法は、上記課題を解決するために、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部が形成されている単結晶Si基板を用いて単結晶Si薄膜デバイスを形成する、該単結晶Si薄膜デバイスと非単結晶Si薄膜デバイスとを備えている半導体装置の製造方法において、上記水素イオン注入部にマイクロ波を照射して上記水素イオン注入部を熱処理する照射工程と、上記照射工程の後、上記水素イオン注入部において上記単結晶Si基板を劈開剥離して、上記酸化膜、上記ゲートパターンおよび上記不純物イオン注入部を有する単結晶Si薄膜を分離する剥離工程と、上記単結晶Si薄膜を絶縁基板上に接合する接合工程とを含む構成である。

上記構成によれば、アルミニウムなどの配線材料の溶断といった不具合の発生を回避して、単結晶Si薄膜デバイスと非単結晶Si薄膜デバイスとを1つの基板上の異なる領域に備えている半導体装置を製造することができる。

また、本発明に係る半導体装置の製造方法は、上記接合工程よりも前に、上記絶縁基板上に上記非単結晶Si薄膜を形成することが好ましい。

上記構成によれば、非単結晶Si薄膜を単結晶Si薄膜デバイス形成前に形成するため、単結晶Si薄膜デバイスを形成した後で非単結晶Si薄膜を形成する場合と比較して、単結晶Si薄膜が汚染されたり、損傷を受けたりすることを防止できる。

以上のように、本発明に係る半導体装置の製造方法は、表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部が形成されているSi基板の水素イオン注入部にマイクロ波を照射することにより、水素イオン注入部を熱処理し、水素イオン注入部においてSi基板を劈開剥離し、酸化膜、ゲートパターンおよび不純物イオン注入部を有するSi薄膜を分離して、このSi薄膜を絶縁基板上に接合する。そのため、Si薄膜デバイスの製造工程において、Si基板および絶縁基板全体が加熱されることがなく、アルミニウムなどの配線材料の溶断などによる不具合の発生を抑えることができる。

本発明に係る製造方法の一実施形態について、図1および2に基づいて説明すれば以下の通りである。

〔半導体装置〕

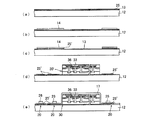

まず、本発明に係る半導体装置の製造方法(以下、本発明の製造方法ともいう)により製造される半導体装置の一実施形態について図2(e)を参照しながら説明する。

まず、本発明に係る半導体装置の製造方法(以下、本発明の製造方法ともいう)により製造される半導体装置の一実施形態について図2(e)を参照しながら説明する。

図2(e)は、本実施の形態により製造された半導体装置1の断面模式図である。半導体装置1は、非単結晶Si薄膜デバイスとしてMOS型の非単結晶Si薄膜トランジスタ20と、単結晶Si薄膜デバイスとしてMOS型の単結晶Si薄膜トランジスタ30とが絶縁基板12上の異なる領域に形成された半導体装置である。そのため、半導体装置1は、高性能化および高機能化に適しており、TFTによるアクティブマトリクス基板に形成される。

半導体装置1は、図2(e)に示すように、絶縁基板12上に、SiO2膜(酸化膜)13と、連続結晶粒界Siからなる非単結晶Si薄膜25’を含むMOS型の非単結晶Si薄膜トランジスタ20と、単結晶Si薄膜(Si薄膜)35を含むMOS型の単結晶Si薄膜トランジスタ30と、金属配線(不図示)とを備えている。

MOS型の両薄膜トランジスタ20,30は、活性半導体層、ゲート電極、ゲート絶縁膜、ゲート両側に形成された高濃度不純物ドープ部(ソース・ドレイン電極)からなり、ゲート電極により、ゲート下の半導体層のキャリア濃度が変調され、ソース−ドレイン間を流れる電流が制御される一般的なトランジスタである。

絶縁基板12は、絶縁性を有していればよく、ここでは、高歪点ガラスであるコーニング社のcode1737(アルカリ土類−アルミノ硼珪酸ガラス)が用いられている。

SiO2膜13は、絶縁基板12の表面全体に、膜厚約50nmで形成されている。

非単結晶Si薄膜25’を含むMOS型の非単結晶Si薄膜トランジスタ20は、SiO2膜13上に、非単結晶Si薄膜25’、ゲート絶縁膜としてのSiO2膜17およびゲート電極26を有している。

非単結晶Si薄膜25’には、結晶成長方向の揃った多結晶Si、いわゆる連続結晶粒界Si(CGS:Continuous Grain Silicon)を用いている。これにより、通常の多結晶Siからなる非単結晶Si薄膜トランジスタよりも特性が高い非単結晶Si薄膜トランジスタ20を得ることができる。

ゲート電極26は、多結晶SiとWシリサイドとから形成されているが、多結晶Si、他のシリサイドまたはポリサイド等から形成されていてもよい。

単結晶Si薄膜35を含むMOS型の単結晶Si薄膜トランジスタ30は、ゲート電極(ゲートパターン)36を有する平坦化層、ゲート絶縁膜としてのSiO2膜(酸化膜)33、および単結晶Si薄膜35を有している。

ゲート電極36の材料は、ヘビードープの多結晶Si膜およびWシリサイドを用いているが、材料は多結晶Si単独であっても、また他の高融点金属およびシリサイドであってもよく、必要な抵抗および耐熱性を考慮して選択される。

単結晶Si薄膜トランジスタ30を形成するゲート電極36、ゲート絶縁膜33および単結晶Si薄膜35は、後述するように、絶縁基板12とは別の単結晶Si基板(Si基板)上で形成される。単結晶Si基板の所定の位置で劈開剥離し、ゲート電極36などの各構成を全て有する単結晶Si薄膜35を絶縁基板12上に接合することにより、単結晶Si薄膜トランジスタ30が形成される。よって、ゲート電極36の形成、およびソース・ドレイン電極形成のための不純物イオン注入は、単結晶Si基板上で行われる。この場合、絶縁基板12上に単結晶Si薄膜を形成して薄膜トランジスタを形成するよりも、単結晶Si薄膜への微細加工を容易に行うことができる。

本発明の製造方法に用いられる単結晶Si基板は、薄膜化して単結晶Si薄膜35を形成する材料となるものであり、表面にゲート電極36などが形成された後、最終的に不要部分42と単結晶Si薄膜35とに分けられる。

非単結晶Si薄膜25’の領域と単結晶Si薄膜35の領域とは、少なくとも0.3μm以上、好ましくは0.5μm以上離れている。これにより、単結晶Si薄膜35に、Ni、Pt、SnおよびPd等の金属原子が拡散することを防止することができ、単結晶Si薄膜トランジスタ30の特性を安定化させることができる。

以上のように、半導体装置1は、1枚の絶縁基板12上に、MOS型の非単結晶Si薄膜トランジスタ20と、MOS型の単結晶Si薄膜トランジスタ30とが共存しているため、特性が異なる複数の回路を集積化した高性能・高機能を有する半導体装置を実現している。

液晶表示装置のアクティブマトリクス基板に半導体装置1を含む場合には、さらにSiNX(窒化Si)、樹脂平坦化膜、ビアホール、透明電極が形成される。また、非単結晶Si薄膜25’の領域には、ドライバおよび表示部用のTFTが形成される。さらに、より高性能が要求されるデバイスに適用可能な単結晶Si薄膜35の領域には、タイミングコントローラが形成される。なお、ドライバ部は、単結晶Siであってもよく、コストと性能とを考慮して決定されればよい。

〔半導体装置の製造方法〕

次に、本発明に係る半導体装置の製造方法の一実施形態について、図1および2を参照しながら説明する。

次に、本発明に係る半導体装置の製造方法の一実施形態について、図1および2を参照しながら説明する。

本発明の製造方法では、単結晶Si基板上に、薄膜化すれば単結晶Si薄膜トランジスタ30となる部分(以下、単結晶薄膜トランジスタ形成部分)30’を形成し、この部分を劈開剥離により分離して、絶縁基板12上に移すことにより、絶縁基板12上に単結晶Si薄膜トランジスタ30を形成している。

(単結晶Si薄膜トランジスタ形成部分製造工程)

まず、単結晶Si基板上に単結晶Si薄膜トランジスタ形成部分30’を形成する方法について説明する。

まず、単結晶Si基板上に単結晶Si薄膜トランジスタ形成部分30’を形成する方法について説明する。

予め一般的なIC製造ラインにおいて、単結晶Si基板上に、ゲート電極36、ゲート絶縁膜33を形成し、ソース・ドレイン不純物イオン注入(BF3+、P+)し、P型およびN型各のチャネル部分へチャネル注入を行う。ゲート電極36上に保護絶縁膜、平坦化膜(BPSG)を形成した後、CMP(Chemical-mechanical Polishing)によって平坦化処理を行う。続いて、膜厚約10nmのSiO2膜を形成し、5×1016/cm2のドーズ量の水素イオンを所定のエネルギーにて注入することにより、単結晶Si基板内に水素イオン注入部41を形成する。水素イオン注入部41を熱処理することにより、水素イオン注入部41において単結晶Si基板を劈開剥離することが可能となる。水素イオン注入部41は、劈開剥離を行ったときにゲート電極36およびゲート絶縁膜33などと一体となって単結晶Si薄膜が作り出される位置に形成される。次いで、単結晶Si薄膜トランジスタ形成部分30’が形成された単結晶Si基板を、絶縁基板12上の単結晶Si薄膜トランジスタ形成領域に適合した所定のサイズに切断する。

次いで、所定のサイズに切断した単結晶Si基板をウェハ保持テーブル(支持台)62に固定し、水素イオン注入部41にマイクロ波M1を照射して水素イオン注入部41を加熱する。マイクロ波照射による加熱後、水素イオン注入部41を境に劈開剥離を行って、単結晶Si基板を、単結晶Si薄膜トランジスタ形成部分30’と不要部分42とに分離する。すなわち、単結晶Si薄膜トランジスタ形成部分30’は、ゲート絶縁膜33、ゲート電極36およびソース・ドレイン不純物イオン注入部などを有するSi薄膜からなる。

ここで、まず、マイクロ波照射による加熱処理に関し、マイクロ波を用いることの利点について説明する。水素イオン注入部41のみを昇温させる手段としては、レーザー光線照射およびマイクロ波照射が考えられる。レーザー光線は、一般的に、ある一点にエネルギーを集中させることで、その部分の温度を上げることができる。しかし、レーザー光線は、金属などのエネルギーをよく吸収する物質にのみ有効に作用し、ガラスなどSi系物質に対しては、エネルギーを集中させることが難しい。そのため、レーザー光線を用いてSi系物質を昇温させることは難しい。これに対してマイクロ波照射による昇温においては、レーザー光線と異なり、エネルギーの集中はさほど必要ではない。そのため、ガラスなどSi系物質を昇温させる場合においても、好適に用い得る。そのため、単結晶Si基板における水素イオン注入部41を昇温させる場合には、マイクロ波照射を用いる場合の方がレーザー光線を用いる場合よりもプロセス的に有利となる。

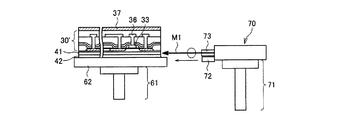

次に、マイクロ波照射による加熱処理について、図1を参照しながら詳細に説明する。

図1に示すように、まず、単結晶Si薄膜トランジスタ形成部分30’を形成して所定のサイズに切断した単結晶Si基板をウェハ保持テーブル62に固定する。次いで、マイクロ波発生装置70に取り付けられている位置センサ72およびウェハ位置制御装置71を用いて、マイクロ波発生装置70と水素イオン注入部41との位置合わせを行う。位置合わせは、位置センサ72により単結晶Si薄膜トランジスタ形成部分30’表面を検知し、単結晶Si薄膜トランジスタ形成部分30’表面から水素イオン注入部41まで検知を行いながら、ウェハ保持テーブル62を上下方向に動かして、所定の位置を検出することにより行う。ウェハ位置制御装置71は、位置センサ72からの情報に基づき、単結晶Si薄膜トランジスタ形成部分30’の水素イオン注入部41に対してマイクロ波M1が最適な位置で照射されるように、ウェハ保持テーブル62とマイクロ波発生装置70との位置関係を設定する。この設定がウェハ保持テーブル駆動装置61に伝達され、ウェハ保持テーブル駆動装置61は、ウェハ位置制御装置71からの情報に基づき、ウェハ保持テーブル62を上下左右に移動させる。これにより、微妙な位置関係の設定にも逐一対応できる。

位置合わせが完了すると、マイクロ波発生装置70からマイクロ波M1を水素イオン注入部41に照射する。照射するマイクロ波M1の強度は、水素イオン注入部41の大きさ、水素イオン注入部までの距離などによって適宜変更し得る。また、照射するマイクロ波M1の周波数は、特に制限はなく、一般的に使用されている周波数でよい。例えば、周波数が2.45GHz〜5GHzのマイクロ波を使用することができる。このマイクロ波照射により、水素イオン注入部41の温度を、単結晶Siから水素が離脱する温度以上まで昇温する。これにより、水素イオン注入部41を境に劈開剥離することができる。なお、マイクロ波発生装置70は従来公知のマイクロ波発生装置を使用すればよい。

マイクロ波M1の照射方法は、水素イオン注入部41にマイクロ波M1が照射されるものであれば特に限定されないが、本実施形態においては、マイクロ波発生装置70からマイクロ波を照射している間、ウェハ保持テーブル62を回転させている。これにより水素イオン注入部41には、2次元の全方向からマイクロ波M1が照射されることになる。そのため、より効率的に、マイクロ波M1を水素イオン注入部41に照射することができ、劈開剥離を容易かつ確実に行うことができる。

マイクロ波M1は、マイクロ波発生装置70の照射口付近に取り付けられている集束装置73を経由して、水素イオン注入部41に照射される。したがって、照射されるマイクロ波M1は集束装置73によって集束した集束マイクロ波となっている。これにより、マイクロ波M1をより確実に水素イオン注入部41に照射し、他の部分を照射してしまうことを防ぐことができる。集束装置73は、電磁場を制御できるものであれば、特に制限されるものではない。

水素イオン注入部41の昇温を行った後、水素イオン注入部41を境に、単結晶Si基板を、単結晶Si薄膜トランジスタ形成部分30’と不要部分42とに劈開剥離により分離する。

従来の方法では、水素イオン注入部を保持する単結晶Si基板を絶縁基板に貼り合わせた後に、全体を高温にする必要がある。単結晶Si薄膜トランジスタを形成する部分を含む単結晶Si基板上または絶縁基板上にはAlなどの材料により形成されている配線が設けられており、これらが高温に加熱されると配線が溶解するなどの不具合が発生してしまう。しかしながら上述のように、マイクロ波照射を行うことにより、ピンポイントで水素イオン注入部41を高温に加熱することができ、水素イオン注入部41以外の部分の昇温を防ぐことができる。すなわち、マイクロ波照射を利用することにより、Al配線における不具合を発生させることなく、単結晶Si薄膜トランジスタ形成部分30’を劈開剥離により不要部分42から分離させ、絶縁基板13への貼り合わせることができる。

また、本実施の形態では、単結晶Si基板についての水素イオン注入部41へのマイクロ波照射処理および劈開剥離操作を、絶縁基板12に密着させる前、絶縁基板12とは別のウェハ保持テーブル62の上で行っている。そのため、絶縁基板12上の他の構成要素が汚染したり、損傷を受けたりすることを防止することができる。また、マイクロ波照射および劈開剥離に必要な構成のみを配置できるため、マイクロ波照射処理および劈開剥離操作が容易となる。

(半導体装置形成工程)

次に、劈開剥離によりSi基板から分離させた単結晶Si薄膜トランジスタ形成部分30’を用いて半導体装置1を製造する方法について図2を参照しながら以下に説明する。

次に、劈開剥離によりSi基板から分離させた単結晶Si薄膜トランジスタ形成部分30’を用いて半導体装置1を製造する方法について図2を参照しながら以下に説明する。

図2(a)に示すように、まず、TEOS(Tetra Ethoxy Silane)とO2との混合ガスを用いたプラズマCVDにより、絶縁基板12の表面全体に約100nmのSiO2膜13を堆積させる。本実施の形態では、絶縁基板12としてコーニング社のcode1737(アルカリ土類−アルミノ硼珪酸ガラス)を用いている。

さらに、SiH4ガスを用いたプラズマCVDにより、SiO2膜13の表面全体に約50nmの非晶質Si薄膜25を堆積させる。さらに、SiH4とN2Oとの混合ガスを用いたプラズマCVDにより、非晶質Si薄膜25上に約200nmのSiO2膜14を堆積させる。

次いで、図2(b)に示すように、SiO2膜14における所定の領域にエッチングにより開口部を形成する。この開口部における非晶質Si薄膜25の表面の親水性をコントロールするために、非晶質Si薄膜25の表面を酸化して薄い酸化膜(SiO2膜)を形成し、その上に酢酸ニッケル水溶液をスピンコートする。

次に、580℃の温度にて約8時間固相成長を行い、結晶成長方向の揃った結晶成長を促進させた多結晶Si、いわゆる連続結晶粒界Siを成長させて連続結晶粒界Si薄膜25’を形成させる。

次いで、図2(c)に示すように、連続結晶粒界Si薄膜25’上のSiO2膜14を除去する。その後、連続結晶粒界Si薄膜25’の所定の領域をエッチングにより除去する。

本実施の形態では、単結晶Si薄膜トランジスタ30を絶縁基板12上に形成前に、連続結晶粒界Si薄膜25’を形成している。そのため、絶縁基板12上に単結晶Si薄膜トランジスタ30を形成した後で連続結晶粒界Si薄膜25’を形成する場合と比較して、単結晶Si薄膜35が汚染されたり、損傷を受けたりすることを防止できる。

次いで、連続結晶粒界Si薄膜25’を除去した部分を、低エネルギー(約3keV)のハロゲン化物を含むガスのGCIB(Gas Cluster Ion Beam)により平坦化する。これにより、ゲート電極36などを有する単結晶Si薄膜35の接合性が向上する。なお、この上にTEOSまたはTMCTS(Tetramethylcyclotetrasiloxane)を用いたPECVDにより約10nmのSiO2膜を形成してもよい。この場合、単結晶Si薄膜35の接合性がさらに向上する。

次いで、図2(d)に示すように、上記単結晶Si薄膜トランジスタ形成部分製造工程において製造しマイクロ波照射により劈開剥離した単結晶Si薄膜トランジスタ形成部分30’を、絶縁基板12上の、連続結晶粒界Si薄膜25’をエッチングにより除去した領域に密着させて接合する。

単結晶Si薄膜トランジスタ形成部分30’の接合では、まず、単結晶Si薄膜トランジスタ形成部分30’上にあるレジスト37を取り除く。次いで、絶縁基板12および単結晶Si薄膜トランジスタ形成部分30’を、パーティクル除去と表面の活性化のためSC−1洗浄する。SC−1洗浄とは、一般にRCA洗浄と呼ばれる洗浄法の一つであって、アンモニアと過酸化水素水と純水とからなる洗浄液を用いる。SC−1洗浄後、単結晶Si薄膜トランジスタ形成部分30’を所定の位置にアライメントする。アライメントは、透明基板12を通して、CCDカメラを用いて、透明基板12側から可視光により単結晶Si薄膜トランジスタ形成部分30’上の位置合わせマークと透明基板12側の位置合わせマークとを検出して行う。なお、単結晶Si薄膜トランジスタ形成部分30’の劈開剥離により形成された面とは反対側の面を、絶縁基板12上のSiO2膜13に接合させる。また、単結晶Si薄膜トランジスタ形成部分30’とガラス製の絶縁基板12とは、Van der Waals力で接合されている。その後、400℃〜600℃、ここでは約550℃の温度での処理で、下記化学反応式:

−Si−OH + −Si−OH → −Si−O−Si− + H2O

の反応を起こさせて、原子同士の強固な結合に変化させ、単結晶Si薄膜トランジスタ形成部分30’と透明基板12側との接合をより強固なものにする。

−Si−OH + −Si−OH → −Si−O−Si− + H2O

の反応を起こさせて、原子同士の強固な結合に変化させ、単結晶Si薄膜トランジスタ形成部分30’と透明基板12側との接合をより強固なものにする。

単結晶Si薄膜トランジスタ形成部分30’を接合させた後に、劈開剥離によって生じた単結晶Si薄膜トランジスタ形成部分30’の剥離面の損傷部分を、等方性プラズマエッチングまたはウェットエッチングなどのライトエッチングにより除去する。本実施の形態では、バッファフッ酸によるウェットエッチングにて約10nmを除去する。これにより、絶縁基板12上に連続結晶粒界Si薄膜25’と、単結晶Si薄膜35とが形成される。

次に、デバイスの活性領域近傍のSiO2膜に開口部を形成し、結晶成長を促進させるために添加したNiをゲッタリングするため高濃度のP+イオンを注入し(15keV、5×1015/cm2)、RTAにて約800℃の温度で1分間の熱処理を行う。なお、単結晶Si薄膜35中にNi原子が拡散しないように物理的にスペースをとってはいるが、ごく微量のNi原子が、プロセス中に混入する可能性がある。そこで、単結晶Si薄膜35の活性領域についてもゲッタリングを行うことが望ましいが、スペースを優先する場合には、設計上の選択肢としてゲッタリングを省略してもよい。

次いで、デバイスの活性領域となる部分を残し、連続結晶粒界Si薄膜25’の不要部分と、単結晶Si薄膜35の不要部分とをエッチングにより除去し、島上のパターンを形成する。

次いで、TEOSと酸素との混合ガスを用いて、プラズマCVDにより膜厚約350nmのSiO2膜を堆積させる。その後、このSiO2膜に対して異方性エッチングであるRIE(リアクティブイオンエッチング)によって約400nmのエッチバックを行う。次いで、図2(e)に示すように、SiH4とN2Oとの混合ガスを用いたプラズマCVDにより、ゲート絶縁膜としての膜厚約60nmのSiO2膜17を形成する。このとき、連続結晶粒界Si薄膜25’のパターンおよび単結晶Si薄膜35のパターンの端部には、サイドウォールが形成される。

さらに、ゲート電極26を形成した後、TEOSとO2との混合ガスを用いたプラズマCVDにより、層間平坦化絶縁膜として膜厚約350nmのSiO2膜を形成する。そして、コンタクトホールを開口し、コンタクトホールに金属(AlSi)配線を形成する。

以上のようにして、アルミニウムなどの配線材料を高温に曝すことなく、単結晶Siトランジスタ30と非単結晶Siトランジスタ20とを有する半導体装置1を製造することができる。

なお、本実施の形態では、非単結晶Si薄膜25’として連続結晶粒界Si薄膜を用いているが、本発明はこれに限定されるものではなく、非単結晶Si薄膜25’は、連続結晶粒界Si薄膜以外の多結晶Si薄膜であってもよい。

また、本実施の形態では、単結晶Si薄膜トランジスタ形成部分30’を接合する前に、非単結晶Si薄膜25’を形成しているが、本発明はこの場合に限らず、単結晶Si薄膜トランジスタ形成部分30’を絶縁基板12上に接合した後に、非単結晶Si薄膜25’を形成してもよい。

さらに、本実施の形態では、単結晶Si薄膜トランジスタ30として形成するトランジスタがMOS型であるが、これに限定されるものではなく、バイポーラ型の単結晶Si薄膜トランジスタであってもよい。

なお、特許文献2の開示内容は、全ての目的に関して、本出願にそのまま参考として援用される。

本発明は上述した実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能である。すなわち、請求項に示した範囲で適宜変更した技術的手段を組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

本発明によれば、加熱による配線の不具合を発生させることなく、単結晶Si薄膜トランジスタを絶縁基板上に形成させることができるため、高性能Siデバイスの製造において有用である。

1 半導体装置

12 絶縁基板

13、14 SiO2膜

17 SiO2膜(ゲート絶縁膜)

20 非単結晶Si薄膜トランジスタ(非単結晶Si薄膜デバイス)

25’ 非単結晶Si薄膜

26 ゲート電極

30 単結晶Si薄膜トランジスタ(Si薄膜デバイス、単結晶Si薄膜デバイス)

30’ 単結晶Si薄膜トランジスタ形成部分

33 SiO2膜(酸化膜、ゲート絶縁膜)

35 単結晶Si薄膜(Si薄膜、Si基板)

36 ゲート電極(ゲートパターン)

37 レジスト

41 水素イオン注入部

42 不要部分(Si基板)

61 ウェハ保持テーブル駆動装置

62 ウェハ保持テーブル(支持台)

70 マイクロ波発生装置

71 ウェハ位置制御装置

72 位置センサ

73 集束装置

M1 マイクロ波

12 絶縁基板

13、14 SiO2膜

17 SiO2膜(ゲート絶縁膜)

20 非単結晶Si薄膜トランジスタ(非単結晶Si薄膜デバイス)

25’ 非単結晶Si薄膜

26 ゲート電極

30 単結晶Si薄膜トランジスタ(Si薄膜デバイス、単結晶Si薄膜デバイス)

30’ 単結晶Si薄膜トランジスタ形成部分

33 SiO2膜(酸化膜、ゲート絶縁膜)

35 単結晶Si薄膜(Si薄膜、Si基板)

36 ゲート電極(ゲートパターン)

37 レジスト

41 水素イオン注入部

42 不要部分(Si基板)

61 ウェハ保持テーブル駆動装置

62 ウェハ保持テーブル(支持台)

70 マイクロ波発生装置

71 ウェハ位置制御装置

72 位置センサ

73 集束装置

M1 マイクロ波

Claims (6)

- 表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部が形成されているSi基板を用いてSi薄膜デバイスを形成する、半導体装置の製造方法であって、

上記水素イオン注入部にマイクロ波を照射して上記水素イオン注入部を熱処理する照射工程と、

上記照射工程の後、上記水素イオン注入部において上記Si基板を劈開剥離して、上記酸化膜、上記ゲートパターンおよび上記不純物イオン注入部を有するSi薄膜を分離する剥離工程と、

上記Si薄膜を絶縁基板上に接合する接合工程とを含むことを特徴とする半導体装置の製造方法。 - 上記マイクロ波は、集束マイクロ波であることを特徴とする請求項1に記載の製造方法。

- 上記照射工程および上記剥離工程は、上記Si基板を上記絶縁基板とは異なる支持台に固定して行うことを特徴とする請求項1または2に記載の製造方法。

- 上記接合工程では、上記Si薄膜を上記絶縁基板上に接合するよりも前に、上記絶縁基板上における上記Si薄膜と接合させる領域を、ハロゲン化物のガス・クラスター・イオン・ビームにより平坦化することを特徴とする請求項1から3までの何れか1項に記載の製造方法。

- 表面に酸化膜、ゲートパターンおよび不純物イオン注入部を有し所定の深さに水素イオン注入部が形成されている単結晶Si基板を用いて単結晶Si薄膜デバイスを形成する、該単結晶Si薄膜デバイスと非単結晶Si薄膜デバイスとを備えている半導体装置の製造方法において、

上記水素イオン注入部にマイクロ波を照射して上記水素イオン注入部を熱処理する照射工程と、

上記照射工程の後、上記水素イオン注入部において上記単結晶Si基板を劈開剥離して、上記酸化膜、上記ゲートパターンおよび上記不純物イオン注入部を有する単結晶Si薄膜を分離する剥離工程と、

上記単結晶Si薄膜を絶縁基板上に接合する接合工程とを含むことを特徴とする半導体装置の製造方法。 - 上記接合工程よりも前に、上記絶縁基板上に上記非単結晶Si薄膜を形成することを特徴とする請求項5に記載の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008318392A JP2010141246A (ja) | 2008-12-15 | 2008-12-15 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008318392A JP2010141246A (ja) | 2008-12-15 | 2008-12-15 | 半導体装置の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010141246A true JP2010141246A (ja) | 2010-06-24 |

Family

ID=42351091

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008318392A Pending JP2010141246A (ja) | 2008-12-15 | 2008-12-15 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010141246A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016518700A (ja) * | 2013-03-14 | 2016-06-23 | クアルコム,インコーポレイテッド | 誘電体基板上への複製回路および変成器の統合 |

| US9906318B2 (en) | 2014-04-18 | 2018-02-27 | Qualcomm Incorporated | Frequency multiplexer |

| US10002700B2 (en) | 2013-02-27 | 2018-06-19 | Qualcomm Incorporated | Vertical-coupling transformer with an air-gap structure |

| US10354795B2 (en) | 2013-08-30 | 2019-07-16 | Qualcomm Incorporated | Varying thickness inductor |

-

2008

- 2008-12-15 JP JP2008318392A patent/JP2010141246A/ja active Pending

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10002700B2 (en) | 2013-02-27 | 2018-06-19 | Qualcomm Incorporated | Vertical-coupling transformer with an air-gap structure |

| JP2016518700A (ja) * | 2013-03-14 | 2016-06-23 | クアルコム,インコーポレイテッド | 誘電体基板上への複製回路および変成器の統合 |

| US10116285B2 (en) | 2013-03-14 | 2018-10-30 | Qualcomm Incorporated | Integration of a replica circuit and a transformer above a dielectric substrate |

| US10354795B2 (en) | 2013-08-30 | 2019-07-16 | Qualcomm Incorporated | Varying thickness inductor |

| US9906318B2 (en) | 2014-04-18 | 2018-02-27 | Qualcomm Incorporated | Frequency multiplexer |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4794810B2 (ja) | 半導体装置の製造方法 | |

| JP4651924B2 (ja) | 薄膜半導体装置および薄膜半導体装置の製造方法 | |

| CN100573824C (zh) | 单晶硅及soi基板、半导体装置及其制造方法、显示装置 | |

| JP5849077B2 (ja) | Soi基板の作製方法 | |

| KR100532557B1 (ko) | 반도체 장치 및 그의 제조 방법, soi기판 및 그것을사용하는 표시 장치 및 soi기판의 제조 방법 | |

| JP4540359B2 (ja) | 半導体装置およびその製造方法 | |

| US20060073678A1 (en) | System and method for hydrogen exfoliation gettering | |

| JP4837240B2 (ja) | 半導体装置 | |

| WO2011070855A1 (ja) | 半導体装置の製造方法および半導体装置 | |

| WO2007111008A1 (ja) | 半導体素子の転写方法及び半導体装置の製造方法並びに半導体装置 | |

| JP5113999B2 (ja) | 水素イオン注入剥離方法 | |

| US8946820B2 (en) | Method for manufacturing semiconductor substrate, substrate for forming semiconductor substrate, stacked substrate, semiconductor substrate, and electronic device | |

| WO2010109712A1 (ja) | 半導体装置用の絶縁基板、及び、半導体装置 | |

| JP2010141246A (ja) | 半導体装置の製造方法 | |

| US20050236626A1 (en) | Semiconductor device, producing method of semiconductor substrate, and producing method of semiconductor device | |

| JP3970814B2 (ja) | 半導体装置の製造方法 | |

| JP5414203B2 (ja) | 半導体装置の作製方法 | |

| JP2004119636A (ja) | 半導体装置およびその製造方法 | |

| JP2005026472A (ja) | 半導体装置の製造方法 | |

| JP5064343B2 (ja) | 半導体装置の製造方法 | |

| WO2006103825A1 (ja) | 半導体装置及びその製造方法 | |

| JP4076930B2 (ja) | 半導体装置の製造方法 | |

| JP4519932B2 (ja) | 半導体装置 | |

| JP2005217050A (ja) | 半導体装置の製造方法 | |

| JP2010027769A (ja) | 回路基板の製造方法および半導体装置の製造方法並びに回路基板 |