JP2010079774A - 半導体記憶システム - Google Patents

半導体記憶システム Download PDFInfo

- Publication number

- JP2010079774A JP2010079774A JP2008249531A JP2008249531A JP2010079774A JP 2010079774 A JP2010079774 A JP 2010079774A JP 2008249531 A JP2008249531 A JP 2008249531A JP 2008249531 A JP2008249531 A JP 2008249531A JP 2010079774 A JP2010079774 A JP 2010079774A

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory

- memory cell

- stored

- pages

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1072—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in multilevel memories

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5641—Multilevel memory having cells with different number of storage levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

Abstract

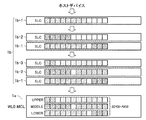

【解決手段】メモリセルアレイは、1つのメモリセルMC中に3ビットの情報を記憶することが可能に構成されている。ECC回路は、メモリセルアレイから読み出されたデータを冗長データに基づいて訂正する。1つのワード線WLを共有し一度に書き込み又は読み出しが可能なメモリセルMCの数が2のべき乗である。また各メモリセルMCがそれぞれ複数ページのデータを格納する。複数ページUPPER,MIDDLE、LOWERに格納される実効データの合計のデータ量が2のべき乗のビット数に設定され、複数ページの残余の部分に冗長データが格納される。

【選択図】図8

Description

を含み、1つのワード線を共有し一度に書き込み又は読み出しが可能な前記メモリセルが複数ページのデータを格納し、前記複数ページに格納されるデータの合計のデータ量が2のべき乗のビット数に設定され、前記複数ページの残余の部分に前記冗長データが格納されるように構成されたことを特徴とする。

まず、本発明の第1の実施の形態に係る不揮発性メモリシステムを、図1等を参照して説明する。

図1は、第1の実施の形態による不揮発性メモリシステムであるメモリカード20の全体構成を示すブロック図である。このメモリカード20は、NAND型フラッシュメモリチップ21とその読み出し/書き込みを制御するメモリコントローラ22によりモジュールを構成する。

フラッシュメモリチップ21は、複数のメモリチップの場合もある。図1では二つのメモリチップchip1,chip2を示しているが、その場合も一つのメモリコントローラ22で制御される。メモリコントローラ22は、メモリチップ21との間でデータ転送を行うためのNANDフラッシュインタフェース23、ホストデバイスとの間でデータ転送を行うためのホストインタフェース25、読み出し/書き込みデータ等を一時保持するバッファRAM26、データ転送制御の他メモリカード全体の動作制御を行うMPU24、NAND型フラッシュメモリ21内のファームウェア(FW)の読み出し/書き込みのシーケンス制御等に用いられるハードウェアシーケンサ27を有する1チップコントローラである。

次に、本発明の第2の実施の形態を、図9を参照して説明する。

次に、本発明の第3の実施の形態を、図10を参照して説明する。この実施の形態は、半導体記憶システムの全体構成等(図1〜図6)に関しては第1の実施の形態と略同様である。また、この実施の形態は、外部のホストデバイスから2のべき乗のビット数単位で供給されたデータを、まず2値メモリ領域1bに書き込み、その後、3ぺージのデータに変換して多値メモリ領域1aに再度書き込む点で第2の実施の形態と同様である。

次に、本発明の第4の実施の形態を、図11、図12を参照して説明する。この実施の形態は、半導体記憶システムの全体構成等(図1〜図6)に関しては第1の実施の形態と略同様である。また、この実施の形態は、外部のホストデバイスから2のべき乗のビット数単位で供給されたデータを、まず2値メモリ領域1bに書き込み、その後、3ぺージのデータに変換して多値メモリ領域1aに再度書き込む点でも第2及び第3の実施の形態と同様である。

以上、発明の実施の形態を説明したが、本発明はこれらに限定されるものではなく、発明の趣旨を逸脱しない範囲内において、種々の変更、追加等が可能である。例えば、上記の実施の形態では、1つのメモリセルに3ビットのデータを格納する場合を例として説明したが、本発明はこれに限定されるものではなく、Nビット(Nは2のべき乗でない3以上の自然数)のデータを1つのメモリセルに格納する場合にも適用され得る。

Claims (5)

- 1つのメモリセル中にNビット(ただし、Nは2のべき乗でない3以上の自然数)の情報を記憶することが可能なメモリセルを複数配列させたメモリセルアレイと、

前記メモリセルアレイに対する読み出し動作、書き込み動作及び消去動作を制御する制御回路と、

前記メモリセルアレイから読み出されたデータを冗長データに基づいて訂正するECC回路と

を含み、

1つのワード線を共有し一度に書き込み又は読み出しが可能な前記メモリセルが複数ページのデータを格納し、

前記複数ページに格納されるデータの合計のデータ量が2のべき乗のビット数に設定され、前記複数ページの残余の部分に前記冗長データが格納されるように構成された

ことを特徴とする半導体記憶システム。 - 前記メモリセルアレイは、

1つの前記メモリセル中に1ビットの情報を格納するように構成された2値メモリ領域と、

1つの前記メモリセル中に前記Nビットの情報を格納するように形成された多値メモリ領域と

を備え、

前記制御回路は、

前記メモリセルアレイに書き込むために2のべき乗のビット数のデータ単位毎に外部から供給されたデータを、前記2値メモリ領域に格納し、次に前記2値メモリ領域に格納されたデータを、順次前記多値メモリ領域に転送する

ことを特徴とする請求項1に記載の半導体記憶システム。 - 前記制御回路は、前記2のべき乗のビット数のデータ単位のデータが、前記多値メモリ領域において全てのページに分散して格納させることを特徴とする請求項2に記載の半導体記憶システム。

- 前記2値メモリ領域は、前記2のべき乗のビット数のデータ単位よりも大きな単位記憶領域を有し、

前記制御回路は、前記単位記憶領域に1つの前記データ単位のデータを格納した後、その単位記憶領域に残余の領域がある場合、その残余の領域に次の前記データ単位のデータの少なくとも一部を格納する

ことを特徴とする請求項2記載の半導体記憶システム。 - 前記複数ページのうちの1つは、2のべき乗のビット数とは異なるビット数のデータが格納されることを特徴とする請求項1記載の半導体記憶システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008249531A JP4746658B2 (ja) | 2008-09-29 | 2008-09-29 | 半導体記憶システム |

| US12/557,898 US7978512B2 (en) | 2008-09-29 | 2009-09-11 | Semiconductor memory system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008249531A JP4746658B2 (ja) | 2008-09-29 | 2008-09-29 | 半導体記憶システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010079774A true JP2010079774A (ja) | 2010-04-08 |

| JP4746658B2 JP4746658B2 (ja) | 2011-08-10 |

Family

ID=42057319

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008249531A Expired - Fee Related JP4746658B2 (ja) | 2008-09-29 | 2008-09-29 | 半導体記憶システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7978512B2 (ja) |

| JP (1) | JP4746658B2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012048791A (ja) * | 2010-08-27 | 2012-03-08 | Toshiba Corp | 多値不揮発性半導体メモリシステム |

| CN102623050A (zh) * | 2011-01-28 | 2012-08-01 | 株式会社东芝 | 半导体集成电路及存储器系统 |

| US8582358B2 (en) | 2011-03-28 | 2013-11-12 | Kabushiki Kaisha Toshiba | Memory system, controller, and method for controlling memory system |

| JP2014523595A (ja) * | 2011-07-22 | 2014-09-11 | サンディスク テクノロジィース インコーポレイテッド | データを蓄積するシステムおよび方法 |

| US10936203B2 (en) | 2018-03-30 | 2021-03-02 | Toshiba Memory Corporation | Memory storage device and system employing nonvolatile read/write buffers |

| CN113314182A (zh) * | 2020-02-27 | 2021-08-27 | 台湾积体电路制造股份有限公司 | 存储器器件及动态误差监视和修复的方法 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6906961B2 (en) * | 2003-06-24 | 2005-06-14 | Micron Technology, Inc. | Erase block data splitting |

| JP2013089082A (ja) | 2011-10-19 | 2013-05-13 | Toshiba Corp | メモリコントローラ、半導体記憶システムおよびメモリ制御方法 |

| US9190162B2 (en) * | 2012-03-13 | 2015-11-17 | Micron Technology, Inc. | Nonconsecutive sensing of multilevel memory cells |

| US9189322B2 (en) * | 2012-08-31 | 2015-11-17 | Kabushiki Kaisha Toshiba | Memory system |

| US10229735B1 (en) * | 2017-12-22 | 2019-03-12 | Intel Corporation | Block management for dynamic single-level cell buffers in storage devices |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07234823A (ja) * | 1993-12-28 | 1995-09-05 | Toshiba Corp | 記憶システム |

| JP2001250386A (ja) * | 2000-03-02 | 2001-09-14 | Mitsubishi Electric Corp | 半導体メモリ |

| JP2005063662A (ja) * | 2004-07-16 | 2005-03-10 | National Chiao Tung Univ | マルチレベルメモリセルを組み合わせ、且つこれにエラー訂正メカニズムを具えさせる方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE60045073D1 (de) | 2000-10-13 | 2010-11-18 | St Microelectronics Srl | Verfahren zum Speichern und Lesen von Daten eines nichtflüchtigen Multibitspeichers mit einer nichtbinären Anzahl von Bits pro Zelle |

| US7379330B2 (en) * | 2005-11-08 | 2008-05-27 | Sandisk Corporation | Retargetable memory cell redundancy methods |

| JP2008077810A (ja) | 2006-09-25 | 2008-04-03 | Toshiba Corp | 不揮発性半導体記憶装置 |

-

2008

- 2008-09-29 JP JP2008249531A patent/JP4746658B2/ja not_active Expired - Fee Related

-

2009

- 2009-09-11 US US12/557,898 patent/US7978512B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07234823A (ja) * | 1993-12-28 | 1995-09-05 | Toshiba Corp | 記憶システム |

| JP2001250386A (ja) * | 2000-03-02 | 2001-09-14 | Mitsubishi Electric Corp | 半導体メモリ |

| JP2005063662A (ja) * | 2004-07-16 | 2005-03-10 | National Chiao Tung Univ | マルチレベルメモリセルを組み合わせ、且つこれにエラー訂正メカニズムを具えさせる方法 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012048791A (ja) * | 2010-08-27 | 2012-03-08 | Toshiba Corp | 多値不揮発性半導体メモリシステム |

| US8605500B2 (en) | 2010-08-27 | 2013-12-10 | Kabushiki Kaisha Toshiba | Multilevel nonvolatile semiconductor memory system |

| CN102623050A (zh) * | 2011-01-28 | 2012-08-01 | 株式会社东芝 | 半导体集成电路及存储器系统 |

| US8582358B2 (en) | 2011-03-28 | 2013-11-12 | Kabushiki Kaisha Toshiba | Memory system, controller, and method for controlling memory system |

| JP2014523595A (ja) * | 2011-07-22 | 2014-09-11 | サンディスク テクノロジィース インコーポレイテッド | データを蓄積するシステムおよび方法 |

| US10936203B2 (en) | 2018-03-30 | 2021-03-02 | Toshiba Memory Corporation | Memory storage device and system employing nonvolatile read/write buffers |

| CN113314182A (zh) * | 2020-02-27 | 2021-08-27 | 台湾积体电路制造股份有限公司 | 存储器器件及动态误差监视和修复的方法 |

| US11935610B2 (en) | 2020-02-27 | 2024-03-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Dynamic error monitor and repair |

Also Published As

| Publication number | Publication date |

|---|---|

| US7978512B2 (en) | 2011-07-12 |

| US20100080056A1 (en) | 2010-04-01 |

| JP4746658B2 (ja) | 2011-08-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4746658B2 (ja) | 半導体記憶システム | |

| JP4970834B2 (ja) | 奇数状態メモリセルを用いて仮想的ページ記憶を支援する集積回路デバイスとフラッシュメモリアレイ | |

| JP4510072B2 (ja) | 不揮発性半導体記憶装置とその書き込み方法 | |

| KR101098656B1 (ko) | 반도체 기억 장치 및 그 판독 방법 | |

| JP5150245B2 (ja) | 半導体記憶装置 | |

| US7518909B2 (en) | Non-volatile memory device adapted to reduce coupling effect between storage elements and related methods | |

| US7907446B2 (en) | Nonvolatile semiconductor memory device and method of driving the same | |

| JP2013143155A (ja) | 不揮発性半導体記憶装置とその書き込み方法 | |

| US10026484B2 (en) | High-speed readable semiconductor storage device | |

| JP2010160873A (ja) | 半導体記憶装置と半導体記憶システム | |

| JP2019053805A (ja) | メモリシステム | |

| JP2009016021A (ja) | Nand型フラッシュメモリ | |

| TWI537723B (zh) | 半導體儲存裝置以及資料處理方法 | |

| JP5204069B2 (ja) | 不揮発性半導体記憶装置 | |

| US8036034B2 (en) | Semiconductor storage device equipped with a sense amplifier for reading data and threshold-voltage-information data | |

| JP2011044200A (ja) | 不揮発性半導体記憶装置 | |

| TW201535400A (zh) | 半導體裝置及其操作方法 | |

| JP2009048750A (ja) | 不揮発性半導体記憶装置 | |

| JP4672673B2 (ja) | 半導体装置および半導体装置の制御方法 | |

| US8238156B2 (en) | Nonvolatile semiconductor memory device and method of operating the same | |

| JP2014132512A (ja) | 不揮発性半導体記憶装置とその書き込み方法 | |

| US20110239096A1 (en) | Data memory device and method of programming to the same | |

| JP5731622B2 (ja) | フラッシュメモリ、バッドブロックの管理方法および管理プログラム | |

| US8456920B2 (en) | Semiconductor memory device capable of executing high-speed page copy | |

| JP2009301679A (ja) | 不揮発性半導体記憶装置とその書き込み方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110201 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110331 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110419 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110513 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140520 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140520 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |