JP2010056685A - 撮像装置、補正回路および補正方法 - Google Patents

撮像装置、補正回路および補正方法 Download PDFInfo

- Publication number

- JP2010056685A JP2010056685A JP2008217256A JP2008217256A JP2010056685A JP 2010056685 A JP2010056685 A JP 2010056685A JP 2008217256 A JP2008217256 A JP 2008217256A JP 2008217256 A JP2008217256 A JP 2008217256A JP 2010056685 A JP2010056685 A JP 2010056685A

- Authority

- JP

- Japan

- Prior art keywords

- video signal

- correction

- flicker

- shutter speed

- imaging

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

- H04N23/745—Detection of flicker frequency or suppression of flicker wherein the flicker is caused by illumination, e.g. due to fluorescent tube illumination or pulsed LED illumination

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N23/00—Cameras or camera modules comprising electronic image sensors; Control thereof

- H04N23/70—Circuitry for compensating brightness variation in the scene

- H04N23/76—Circuitry for compensating brightness variation in the scene by influencing the image signals

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S348/00—Television

- Y10S348/91—Flicker reduction

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Studio Devices (AREA)

- Picture Signal Circuits (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

【解決手段】先にフリッカを含まない基準映像信号を生成しておき、当該基準映像信号とフリッカを含む映像信号との比較を行う。そして、この比較結果に基づいて、補正波形の位相と振幅を調整し、この補正波形を用いて映像信号からフリッカを除去する。

【選択図】図5

Description

フリッカが生じる条件を以下の(1)〜(3)に示す。

(1)蛍光灯等の明滅する光源下における撮像である。

(2)光源の明滅周期が毎秒撮像フレーム数の整数倍である。

(3)電子シャッタを使用している。

図1(a)は、60Hz蛍光灯の明るさの時系列変化を示すグラフである。

縦軸は、60Hz蛍光灯の明るさを示す。横軸は、時間軸を表す。波形102からわかるように蛍光灯の明滅周期は、120Hzである。

前述の条件(2)を満たすようにするため、撮像素子で撮像する映像のフレームレートは60frames/secとする。つまり、1フレーム分の画像を撮像するのに必要な時間(露光時間)は1/60secである。また、CMOS素子に設定される条件(3)の電子シャッタのシャッタ速度は、1/2000secとする。

図4に示す撮像装置401は図示しないレンズを有し、このレンズを介して撮像光が撮像素子404の図示しない撮像面に結像される。撮像素子404は、CMOS(complementary metal oxide silicon)素子であり、レンズ1を介して結像された撮像光を水平ライン毎に所定のタイミングで光電変換して所定のアナログ信号を生成する。そして、撮像素子404で生成されたアナログ信号はゲイン調整回路405に供給される。また、この撮像素子404は、電子シャッタ機能を有しており、後述するマイコン402からの指示に基づいて、電子シャッタのシャッタ速度を決定する。なお、本例では、撮像素子404で撮像された映像のフレームレートが60frames/secであるとし、撮像素子404の水平ラインの数が1125であるとする。

図5は、本例の撮像装置401の補正回路406を示すブロック図である。

図5に示す補正回路406の第一水平積分処理部502は、ゲイン調整回路405から供給される基準映像信号を利用して、当該基準信号で表される画像の各水平ラインを構成する画素の輝度の総和(以下、「基準値」という。)を算出するものである。算出した基準値はメモリ503に記憶される。

次に、図6を参照して、撮像装置401を構成する各機能ブロックにおける処理の流れについて説明を行う。

図6は、撮像装置401の動作を示すフローチャートである。

ビデオ装置による撮像中にシャッタ速度およびゲインを変更する場合、ユーザは操作部403に対し所定の操作を行う。すると、マイコン402を通じて、撮像素子404の電子シャッタおよびゲイン調整回路405に所定のシャッタ速度および基準ゲインがそれぞれ設定される。(ステップS601)。以下では、このステップS601の処理でユーザの設定したシャッタ速度およびゲインをそれぞれ「撮像用シャッタ速度」および「撮像用ゲイン」という。

ステップS604の処理が完了後、撮像素子404およびゲイン調整回路405を通じて、基準シャッタ速度で撮像された、基準ゲインが反映された映像信号(以下、「基準映像信号」という。)が第一水平積分処理部502に供給される。そして、基準映像信号の水平ライン毎の輝度の積分値が算出され(以下、「水平積分」という。)、基準映像信号の水平積分結果が基準値としてメモリ503に記憶される(ステップS605)。

図7および図8は、図6のステップS607の処理である、フリッカ補正処理の詳細な処理の流れを示すフローチャートである。以下、第二水平積分処理部507、相関検出部504、補正値生成部505および振幅補正部506が行うフリッカ補正処理について説明する。

相関検出部504では、補正後の映像が基準映像にどこまで近づいたかを見るための差分和を検出する。そして、相関検出部504はこの差分和から相関の強弱を判断し補正方針(位相の変化方向、振幅の増減方向)が間違っていないかを判断する。前回の補正がその前の補正よりも差分和が大きくなり相関が弱くなったと判断すれば、補正方針が間違っていたとして、今回の補正では補正対象である補正波形の位相変化の方向や振幅の増減方向を逆にする。逆に前回の補正がその前の補正よりも差分が小さくなっていれば、補正方針は合っていたものとして、今回の補正では補正対象の補正波形の位相、振幅の増減方向はそのままにする。その結果として、相関検出部504は、補正信号の位相と振幅それぞれの増減方向(+/−)を変化させる制御信号を生成し、生成した制御信号を補正値生成部505に出力することになる。

図9(a)は、60Hz蛍光灯の明るさの時系列変化を示すグラフである。

縦軸は、60Hz蛍光灯の明るさを示す。横軸は、時間軸を表す。波形902からわかるように蛍光灯の明滅周期は、120Hzである。

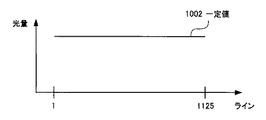

前述のように、撮像素子404で撮像する映像のフレームレートは60frames/secである。つまり、1フレーム目の画像を撮像するのに必要な時間は1/60secとなる。撮像素子404の電子シャッタを使用しない、すなわちシャッタ速度が1/60secの場合、撮像素子404の各水平ラインの露光時間903は1/60sec間隔となる。前述したが、この1/60secという露光時間903は、60Hzの蛍光灯下においては撮像する映像にフリッカが発生しない露光時間(前述の基準シャッタ速度)である。

次に、フリッカ補正処理のイメージについて図12〜図13を参照して説明する。

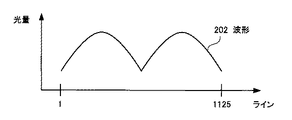

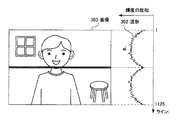

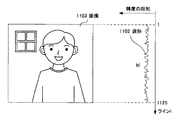

図3に示す、フリッカの発生している画像303に対しフリッカ補正処理を行う例について述べる。画像303は、60Hzの蛍光灯の下、電子シャッタのシャッタ速度1/2000secで撮像を行った場合、ゲイン調整回路405で生成される撮像用映像信号で表される画像である。このような画像303の各水平ラインの輝度は、蛍光灯下光量(図2の波形202)が撮像対象物に反射した反射光量で決定されるので、波形302のようになる。この波形302が、図8のステップS802〜ステップS805のループ処理で算出される撮像値に相当する。本例では、図3に示す波形302をaiと定義する。なお、iはラインを示す変数である。

[他の実施形態の撮像装置の構成]

以下、本発明の他の実施の形態の例について、図15〜図17を参照して説明する。

図15は、本例の撮像装置を示すブロック図である。

図16は、本例の撮像装置の補正回路を示すブロック図である。

撮像装置1501は、映像の記録指示があるまで、基準値の取り込みと、当該取り込んだ基準値を利用したフリッカ補正処理を1フレーム毎に交互に行うものである。このため、他の実施形態のマイコン1502は、ユーザによる操作部403からの記録指示があるまで、垂直同期信号を利用して1フレーム飛ばしのタイミングで前述の基準値取り込み指示を撮像素子404に供給する。なお、マイコン1502の他の機能は一実施形態のマイコン402と同じである。

次に、図17を参照して撮像装置1501を構成する各機能ブロックにおける処理の流れを説明する。

図17は、撮像装置1501の動作を示すフローチャートである。

まず、ユーザは、撮像装置1501の電源を入れ、シャッタ速度およびゲインの設定を行う。具体的には、マイコン1502が、ユーザの操作部403に対する操作に基づいて、撮像素子404およびゲイン調整回路405に前述の、撮像用シャッタ速度および撮像用ゲインを設定する(ステップS1701)。

302…波形、303…画像、401…撮像装置401、402…マイコン402、403…操作部403、404…撮像素子404、405…ゲイン調整回路405、406…補正回路406、407…画像処理回路407、408…表示部408、409…記録部409、502…第一水平積分処理部502、503…メモリ、504…相関検出部504、505…補正値生成部505、506…振幅補正部506、507…第二水平積分処理部507、508…メモリ、902…波形、903…露光時間、1002…一定量、1102…波形、1103…画像、1202…波形、1302…補正波形、1402…画像

Claims (12)

- 所定のフレームレートおよび水平ライン総数に基づくタイミングで動作し、シャッタ速度を設定可能な電子シャッタを備え、該電子シャッタのシャッタ速度に応じた期間における入射光を、水平ライン毎に光電変換して所定の信号を生成する撮像素子と、

前記撮像素子で生成された信号のゲインを調整して所定のレベルの信号を生成して映像信号を生成するゲイン調整回路と、

前記入射光の明滅周期がフレームレートの整数倍であり、かつ前記電子シャッタに所定のシャッタ速度が設定されているときに前記ゲイン調整回路で生成される映像信号と、前記入射光の明滅周期がフレームレートの整数倍であり、かつ前記電子シャッタに入射光の明滅周期の整数倍のシャッタ速度が設定されているときに前記ゲイン調整回路で生成される、フリッカの発生しない基準映像信号を比較し、前記映像信号に含まれる、該映像信号で表される画像の垂直方向に現れるフリッカ成分を算出し、該算出結果に応じて前記映像信号で表される画像から前記フリッカを除去する補正回路と

を有する撮像装置。 - さらに、

前記基準映像信号の取り込み時は、前記入射光の明滅周期と、予めユーザにより指示されたシャッタ速度および該シャッタ速度に応じたゲインとに基づいて前記基準映像信号取り込み用のシャッタ速度およびゲインをそれぞれ算出し、前記算出したシャッタ速度およびゲインを前記電子シャッタおよび前記ゲイン調整回路にそれぞれ設定し、前記基準映像信号の取り込みが終われば、前記予めユーザにより指示されたシャッタ速度およびゲインを前記電子シャッタおよび前記ゲイン調整回路にそれぞれ設定する制御部を備える

請求項1に記載の撮像装置。 - 前記補正回路は、算出した垂直方向に現れる前記フリッカ成分と少なくとも逆相の補正波形を算出し、該補正波形を前記映像信号で表される画像の各水平ラインに重畳することにより該映像信号で表される画像から前記フリッカを除去する

請求項2に記載の撮像装置。 - 前記補正回路は、

前記基準映像信号で表される画像の水平ライン方向に該基準映像信号を積分することにより、該基準映像信号の水平ライン毎の信号レベルの総和である基準値を算出し、

また前記映像信号で表される画像の水平ライン方向に該映像信号を積分することにより、該映像信号の水平ライン毎の信号レベルの総和である撮像値を算出する水平積分処理部と、

算出された前記基準値を記憶する第一メモリと、

前記第一メモリから前記基準値を読み出し、読み出した前記基準値と、前記水平積分処理部で算出された前記撮像値との差分を検出する相関検出部と、

前記相関検出部の検出結果に基づいて前記補正波形を補正/生成する補正値生成部と、

生成された前記補正波形を前記映像信号で表される画像の各ラインに重畳することにより該映像信号で表される画像から前記フリッカを除去する振幅補正部と、

を備える

請求項3に記載の撮像装置。 - さらに、

前記相関検出部で前回検出された差分の総和である差分和を記憶する第二メモリを備え、

前記相関検出部は、今回生成した前記差分和と、前記第二メモリに記憶されている、前回生成された前記差分和とを比較し、

前記補正値生成部は、該比較結果に基づいて今回の前記補正波形を生成する

請求項4に記載の撮像装置。 - 前記相関検出部は、前記第二メモリに記憶された、前回生成された前記差分和と、今回生成した前記差分和との大小を比較し、

前記補正値生成部は、前記相関検出部での比較結果に基づいて新たな補正波形を生成する

請求項5に記載の撮像装置。 - 前記相関検出部は、前記第二メモリに記憶された、前回生成された前記差分和と、今回生成した前記差分和とを比較し、

前記補正値生成部は、今回生成した前記差分和の方が大きいとき、前回生成した補正波形の位相および振幅の増減方向を反転し、位相および振幅を所定量変化させた、新たな補正波形を生成する

請求項6に記載の撮像装置。 - 前記相関検出部は、前記第二メモリに記憶された、前回生成された前記差分和と、今回生成した前記差分和とを比較し、

前記補正値生成部は、今回生成した前記差分和の方が小さいとき、前回生成した補正波形の位相および振幅の増減方向をそのままに、位相および振幅を所定量変化させた、新たな補正波形を生成する

請求項7に記載の撮像装置。 - さらに、

操作部を備え、

前記制御部は、ユーザからの前記操作部に対する基準映像信号の取り込み指示を検出して前記入射光の明滅周期に対応するシャッタ速度を前記電子シャッタに設定するとともに、前記設定したシャッタ速度と、前記予めユーザが設定した、シャッタ速度およびゲインに基づいて所定のゲインを算出し、算出したゲインを前記ゲイン調整回路に設定する

請求項5に記載の撮像装置。 - 前記制御部は、前記撮像素子および前記ゲイン調整回路を制御し、所定の間隔で基準映像信号を生成させる

請求項5に記載の撮像装置。 - 撮像素子が備える電子シャッタのシャッタ速度が該撮像素子に入る入射光の明滅周期の整数倍のときに該撮像素子から入力される、該撮像素子の垂直方向にフリッカが生じない画像に対応する基準映像信号を、該基準映像信号で表される画像の水平ライン方向に積分することにより、前記基準映像信号の前記水平ライン毎の信号レベルの総和である基準値を算出し、また撮像素子が備える電子シャッタに所定のシャッタ速度が設定されているときに該撮像素子から入力される映像信号を、該映像信号で表される画像の水平ライン方向に積分することにより、前記映像信号の前記水平ライン毎の信号レベルの総和である撮像値を算出する水平積分処理部と、

算出された前記基準値を記憶するメモリと、

前記メモリから前記基準値を読み出し、読み出した前記基準値と、前記水平積分処理部で算出された前記撮像値との差分を計算することにより前記フリッカ成分を算出する相関検出部と、

前記相関検出部で算出した前記フリッカ成分と少なくとも逆相の補正波形を生成する補正値生成部と、

生成された前記補正波形を前記映像信号で表される画像の各ラインに重畳することにより該映像信号で表される画像から前記フリッカを除去する振幅補正部と、

を備える補正回路。 - 所定のフレームレートおよび水平ライン総数に基づくタイミングで動作し、シャッタ速度を設定可能な電子シャッタのシャッタ速度を設定するシャッタ速度設定ステップと、

設定された前記電子シャッタのシャッタ速度に応じた期間における入射光を、水平ライン毎に光電変換して所定の信号を生成する信号生成ステップと、

前記信号生成ステップで生成された前記信号のゲインを調整して所定のレベルの前記信号を生成して映像信号を生成する映像信号生成ステップと、

前記入射光の明滅周期がフレームレートの整数倍であり、かつ前記電子シャッタに所定のシャッタ速度が設定されているときに前記ゲイン調整回路で生成される映像信号と、前記入射光の明滅周期がフレームレートの整数倍であり、かつ前記電子シャッタに入射光の明滅周期の整数倍のシャッタ速度が設定されているときに前記ゲイン調整回路で生成される、フリッカの発生しない基準映像信号を比較し、前記映像信号に含まれる、該映像信号で表される画像の垂直方向に現れるフリッカ成分を算出し、該算出結果に応じて前記映像信号で表される画像から前記フリッカを除去するフリッカ除去ステップと

を有する補正方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008217256A JP4626689B2 (ja) | 2008-08-26 | 2008-08-26 | 撮像装置、補正回路および補正方法 |

| US12/546,729 US8218029B2 (en) | 2008-08-26 | 2009-08-25 | Image taking apparatus, correction circuit and correction method |

| CN2009101684708A CN101662591B (zh) | 2008-08-26 | 2009-08-26 | 图像摄取设备、校正电路和校正方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008217256A JP4626689B2 (ja) | 2008-08-26 | 2008-08-26 | 撮像装置、補正回路および補正方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056685A true JP2010056685A (ja) | 2010-03-11 |

| JP4626689B2 JP4626689B2 (ja) | 2011-02-09 |

Family

ID=41724810

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008217256A Expired - Fee Related JP4626689B2 (ja) | 2008-08-26 | 2008-08-26 | 撮像装置、補正回路および補正方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8218029B2 (ja) |

| JP (1) | JP4626689B2 (ja) |

| CN (1) | CN101662591B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018051615A1 (ja) * | 2016-09-14 | 2018-03-22 | ソニー株式会社 | 撮像制御装置および撮像制御方法 |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011091775A (ja) | 2009-10-26 | 2011-05-06 | Toshiba Corp | 固体撮像装置 |

| JP5625371B2 (ja) * | 2010-01-29 | 2014-11-19 | ソニー株式会社 | 画像処理装置、および信号処理方法、並びにプログラム |

| CN102025920B (zh) * | 2010-11-17 | 2012-08-29 | 无锡中星微电子有限公司 | 曝光时间调整方法和装置以及应用此装置的摄像头 |

| TWI469632B (zh) * | 2011-11-09 | 2015-01-11 | Silicon Motion Inc | 抗閃爍攝錄裝置與攝錄方法 |

| CN103108132B (zh) * | 2011-11-15 | 2016-06-15 | 慧荣科技股份有限公司 | 抗闪烁摄录装置与摄录方法 |

| EP2713608B1 (en) | 2012-10-01 | 2015-04-29 | Axis AB | A device and a method for image acquisition |

| US9083887B2 (en) * | 2013-04-08 | 2015-07-14 | Samsung Electronics Co., Ltd. | Image capture devices configured to generate compensation gains based on an optimum light model and electronic apparatus having the same |

| JP6170355B2 (ja) * | 2013-06-26 | 2017-07-26 | キヤノン株式会社 | 撮像装置及びその制御方法 |

| JP2015192393A (ja) * | 2014-03-28 | 2015-11-02 | ソニー株式会社 | 映像信号処理装置、映像信号処理方法およびプログラム |

| JP6381380B2 (ja) * | 2014-09-08 | 2018-08-29 | キヤノン株式会社 | 撮像装置、制御方法及びそのプログラム |

| JP6525757B2 (ja) * | 2015-06-17 | 2019-06-05 | キヤノン株式会社 | 撮像装置、光量変化特性の算出方法、プログラム及び記憶媒体 |

| WO2017064829A1 (ja) * | 2015-10-15 | 2017-04-20 | ソニー株式会社 | 映像信号処理装置、映像信号処理方法およびプログラム |

| JP2018026716A (ja) * | 2016-08-10 | 2018-02-15 | オリンパス株式会社 | 撮像装置、撮像方法及び撮像プログラム |

| JP6863381B2 (ja) * | 2016-08-16 | 2021-04-21 | ソニーグループ株式会社 | 撮像制御装置、撮像制御方法および撮像システム |

| KR20220003129A (ko) * | 2019-05-30 | 2022-01-07 | 벡톤 디킨슨 앤드 컴퍼니 | 무선 주파수 다중화 신호의 위상 보정 |

| CN110868550B (zh) * | 2019-11-25 | 2021-04-06 | 维沃移动通信(杭州)有限公司 | 一种拍照方法及终端设备电子设备 |

| CN115529419B (zh) | 2021-06-24 | 2024-04-16 | 荣耀终端有限公司 | 一种多人工光源下的拍摄方法及相关装置 |

| CN115866421A (zh) * | 2021-09-24 | 2023-03-28 | 北京小米移动软件有限公司 | 一种拍摄方法、拍摄装置及存储介质 |

| EP4352947A4 (en) * | 2021-12-16 | 2024-09-04 | Samsung Electronics Co., Ltd. | METHOD AND APPARATUS FOR ELIMINATING FLICKER IN A VIDEO |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007251611A (ja) * | 2006-03-16 | 2007-09-27 | Sanyo Electric Co Ltd | 撮像装置 |

| WO2007145168A1 (ja) * | 2006-06-13 | 2007-12-21 | Panasonic Corporation | 階調補正装置 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11164192A (ja) | 1997-11-27 | 1999-06-18 | Toshiba Corp | 撮像方法及び装置 |

| JP3749038B2 (ja) * | 1999-06-30 | 2006-02-22 | 株式会社東芝 | 固体撮像装置 |

| CN1156152C (zh) * | 1999-10-08 | 2004-06-30 | 松下电器产业株式会社 | 照明闪烁检测、补偿装置和交流电源频率检测装置及其方法 |

| JP4953498B2 (ja) * | 2000-07-12 | 2012-06-13 | 富士重工業株式会社 | フェールセーフ機能を有する車外監視装置 |

| JP4337353B2 (ja) * | 2002-03-25 | 2009-09-30 | セイコーエプソン株式会社 | フリッカ検出装置、フリッカ補正装置、撮像装置、フリッカ検出プログラムおよびフリッカ補正プログラム |

| JP3605099B2 (ja) | 2002-07-15 | 2004-12-22 | 日本アビオニクス株式会社 | 液晶表示装置のフリッカ抑止回路 |

| JP4423889B2 (ja) * | 2002-11-18 | 2010-03-03 | ソニー株式会社 | フリッカ低減方法、撮像装置およびフリッカ低減回路 |

| CN100589533C (zh) * | 2002-11-18 | 2010-02-10 | 索尼株式会社 | 闪烁降低方法、图像拾取装置与闪烁降低电路 |

| US7142234B2 (en) * | 2002-12-10 | 2006-11-28 | Micron Technology, Inc. | Method for mismatch detection between the frequency of illumination source and the duration of optical integration time for imager with rolling shutter |

| JP4329677B2 (ja) | 2004-11-09 | 2009-09-09 | セイコーエプソン株式会社 | 動き検出装置 |

| JP4539449B2 (ja) * | 2005-06-10 | 2010-09-08 | ソニー株式会社 | 画像処理装置および撮像装置 |

| JP4335849B2 (ja) * | 2005-06-13 | 2009-09-30 | 富士通マイクロエレクトロニクス株式会社 | フリッカ検出可能な撮像装置 |

| US8068148B2 (en) * | 2006-01-05 | 2011-11-29 | Qualcomm Incorporated | Automatic flicker correction in an image capture device |

| CN101622859B (zh) * | 2007-03-05 | 2011-06-15 | 瑞萨电子株式会社 | 成像装置和闪烁检测方法 |

| JP5147302B2 (ja) * | 2007-06-13 | 2013-02-20 | 株式会社エルモ社 | ビデオカメラおよびビデオカメラにおけるフリッカ低減方法 |

| JP2009004845A (ja) * | 2007-06-19 | 2009-01-08 | Panasonic Corp | 撮像装置、撮像方法、プログラム、および集積回路 |

| JP4836896B2 (ja) * | 2007-08-27 | 2011-12-14 | 三洋電機株式会社 | ビデオカメラ |

| TW200926767A (en) * | 2007-12-07 | 2009-06-16 | Sunplus Mmedia Inc | Automatic flicker detection and correction apparatus and method in a video capture device |

-

2008

- 2008-08-26 JP JP2008217256A patent/JP4626689B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-25 US US12/546,729 patent/US8218029B2/en not_active Expired - Fee Related

- 2009-08-26 CN CN2009101684708A patent/CN101662591B/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007251611A (ja) * | 2006-03-16 | 2007-09-27 | Sanyo Electric Co Ltd | 撮像装置 |

| WO2007145168A1 (ja) * | 2006-06-13 | 2007-12-21 | Panasonic Corporation | 階調補正装置 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018051615A1 (ja) * | 2016-09-14 | 2018-03-22 | ソニー株式会社 | 撮像制御装置および撮像制御方法 |

| JPWO2018051615A1 (ja) * | 2016-09-14 | 2019-06-24 | ソニー株式会社 | 撮像制御装置および撮像制御方法 |

| US10972677B2 (en) | 2016-09-14 | 2021-04-06 | Sony Corporation | Imaging control apparatus and imaging control method |

Also Published As

| Publication number | Publication date |

|---|---|

| US8218029B2 (en) | 2012-07-10 |

| US20100053369A1 (en) | 2010-03-04 |

| CN101662591B (zh) | 2011-12-07 |

| JP4626689B2 (ja) | 2011-02-09 |

| CN101662591A (zh) | 2010-03-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4626689B2 (ja) | 撮像装置、補正回路および補正方法 | |

| TWI508555B (zh) | 用於進行影像合成的影像處理設備和影像處理方法 | |

| CN105323474B (zh) | 摄像设备及其控制方法 | |

| JP4487640B2 (ja) | 撮像装置 | |

| JP5035025B2 (ja) | 画像処理装置、フリッカ低減方法、撮像装置及びフリッカ低減プログラム | |

| US20060115297A1 (en) | Imaging device and imaging method | |

| US10986262B2 (en) | Imaging apparatus, control method, and non-transitory storage medium | |

| JP6355454B2 (ja) | 撮像装置及びその制御方法、プログラム、記憶媒体 | |

| US20090135276A1 (en) | Flicker correction apparatus, flicker correction method, and image sensing apparatus | |

| JP4501994B2 (ja) | 撮像装置 | |

| JP4479845B2 (ja) | 画像補正装置、画像補正方法、画像補正プログラム | |

| JP2010147786A (ja) | 撮像装置及び画像処理方法 | |

| JP5218239B2 (ja) | 画像データ処理装置および撮像装置 | |

| JP2019201387A (ja) | 追尾制御装置 | |

| JP2005223898A (ja) | 画像処理方法及び撮像装置 | |

| US20220321743A1 (en) | Image processing apparatus and method, and image capturing apparatus | |

| JP2002290988A (ja) | 撮像装置 | |

| WO2012147337A1 (ja) | フリッカ検出装置、フリッカ検出方法およびフリッカ検出プログラム | |

| US20140078326A1 (en) | Focus control device, method for controlling focus and image pickup apparatus | |

| JP2006135381A (ja) | キャリブレーション方法およびキャリブレーション装置 | |

| JP5711005B2 (ja) | フリッカ補正方法および画像処理装置 | |

| US11330192B2 (en) | Acquisition method, computer readable recording medium and image apparatus | |

| JP4613710B2 (ja) | 画像処理装置及びプログラム | |

| US20220272252A1 (en) | Imaging apparatus, method for reducing color unevenness due to flicker, and computer readable recording medium | |

| JP6322955B2 (ja) | 撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100617 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100622 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100819 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101012 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101025 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131119 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131119 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |