JP2010045391A - 層状構造体製造方法、半導体基板、素子回路製造方法、及び太陽電池素子の直列接続回路 - Google Patents

層状構造体製造方法、半導体基板、素子回路製造方法、及び太陽電池素子の直列接続回路 Download PDFInfo

- Publication number

- JP2010045391A JP2010045391A JP2009258859A JP2009258859A JP2010045391A JP 2010045391 A JP2010045391 A JP 2010045391A JP 2009258859 A JP2009258859 A JP 2009258859A JP 2009258859 A JP2009258859 A JP 2009258859A JP 2010045391 A JP2010045391 A JP 2010045391A

- Authority

- JP

- Japan

- Prior art keywords

- layered structure

- layer

- semiconductor substrate

- porous layer

- porous

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

Landscapes

- Photovoltaic Devices (AREA)

Abstract

【解決手段】本発明は、半導体材料からなる層状構造体(28)を製造する層状構造体製造方法において、半導体基板(10)上に多孔性層(18)が形成され、多孔性層上に層状構造体(28)が設けられ、層状構造体は、多孔性層を目的の分離位置として利用して半導体基板から分離され、半導体基板の表面が多孔性層の生成前に構造化されるか、あるいは上記多孔性層の表面が構造化され、層状構造体が少なくとも部分的にエピタキシャル成長により多孔性表面上に設けられ、層状構造体に属する少なくとも1つの半導体層がエピタキシャル成長によって多孔性層の表面上に設けられる、ことを特徴としている。

【選択図】図1

Description

a)(100)方向付け及び研磨を行ったSiウエハーの1000℃での45分間の酸化(1%トランスLC)。100nm厚さのSiO2層が生成される。

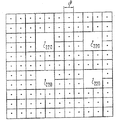

b)網状マスクを使用して、回転させて光食刻法で露出したフォトレジスト。マスクの構成によって、約2μm幅のウェブ上での現像後フォトレジストのみが残り、11×11μm2の自由面がウェブに形成される。

c)約2分間で緩衝HFで酸化物を除去する。フォトレジストが除去される。

d)RCA1及びRCA2洗浄はHFに浸すことで終了する。

e)逆ピラミッド部分を80℃の温度で10分間8%のKOH溶液でエッチングする。エッチング処理の後、サンプルを高純度水で濯いで乾燥させる。酸化ウェブを目に見える程度まで除去する。この異方性エッチング手法により、配向の結晶表面(111)が生じる。面(111)の自由結合部分に安定して水素を染み込ませることができるので、表面でのSiO2の生成を確実に防ぐことができる。従って、次のエピタキシャル過程でも、方法と反応体は酸化物の熱伝導を生じさせないものとして考慮される。

f)他の方法:

f1)KOHでの異方性エッチングにより不規則に配列されたピラミッド(光食刻法ではない)

f2)特殊形状の鋸歯(代表的構造のサイズは100μm)での機械的研削

f3)深くならい削りされた多孔性シリコンを、不均一照明(n−タイプSi)で生成し、後に再び除去する

f4)開始ウエハーは、例えばブロック鋳造材料などの単結晶Siでよい。

b)エッチング装置はEP−A−0536788の図2bに開示されているものに相当する。HFとH2Oとエタノールでの陽極腐食法で多孔性シリコンを生成する。なお、HF:H2O:エタノール=1:1:2(室温で)。基板の構造化側は陰極を向いている。層の多孔性は電流濃度によって調整され、また代表的な電流濃度は1〜100mA/cm2である。

c)低多孔性(約35%)の約150nm厚さの第1多孔性層を生成し、次ぎに高多孔性(50%)の約10μm厚さの第2多孔性層を生成する。

d)構造化多孔性面を有するシリコン円板を乾燥したO2雰囲気の中で30分間400℃酸化させ、エピタキシーの前に不活性気体(N2)で保存する。

この処理はS.Oelting,D.Martini,D.Bonnetによる論文「イオン援用沈着による結晶薄膜シリコン太陽電池素子」に詳細に説明されている。図2〜4に示すようにSEMが記録されているサンプルを以下のようにエピタキシー処理する。

a)HFに浸してRCA1及びRCA2洗浄を行う(5%のHFで30秒、その後脱イオン水で濯ぐ)。

b)反応装置に送り込み、400℃〜500℃で気体除去する。

c)残留酸化物を除去するために、10分間850℃に加熱する。

d)5×1017cm-3のGaドープで、(基板ウエハーの巨視的表面垂直線に平行に測定した)10μm厚さのシリコン層が成長した。Gaだまりの温度は670℃であり、また基板温度は700℃である。沈着速度は4μm/hである。高真空(<10-5Pa)で被覆を行う。連続してドーピングした層、特にエピタキシーの間に生成されたpn接合部分は同様に問題なく分離した。

e)他のエピタキシー法

e1)液相エピタキシー(LPE)。LPEは850℃未満の温度で可能であるため興味深い。

e2)非晶質Si(a−Si)の固相結晶化(SPC)。大領域のa−Si沈着を行う沈着プラントは先行技術であるため興味深い。SPCの速度が遅いのが欠点である(再結晶化に5〜10時間)。

e3)Canonによる特許に開示されている気相エピタキシー(CVD)。CVDでは900℃を超える沈着温度が必要となり、多孔性物質が焼結してしまうのが欠点である。機械的分離は困難または不可能である。

e4)プラズマ援用気相エピタキシー(LPCVD)。低温で可能であるため興味深い。

e5)低温(<600℃)で高沈着速度(>1nm/s)が可能であるため、熱線エピタキシー。

e6)迅速であり、また基板及び多孔性Siの低温積載のみ行われるため、非晶質Siのレーザー結晶化。

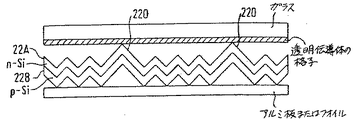

a)基板ウエハーの多孔性層上の10μm厚さのエピタキシャル層を125°の温度で加熱板上に置く。エピタキシャル層が上になるようにする。

b)加熱したエピタキシャル層の上にグリコールフタル酸塩を載せ、更にその上に2cm×2cm=4cm2のサイズのカバーガラスを置く。この透明高分子は軟化し、ガラス板の重みを受けて流れ、10分後にエピタキシャル層とガラスの間の部分の空気を完全に除去する。冷却後、ガラスは構造化エピタキシャル層に結合される。

b1)グリコールフタル酸塩とは異なる接着剤、例えは光起電性分野で通例となっているプラスチックを使用。

b2)ガラス以外の機械的キャリア、例えばプラスチックフォイルの使用。このような柔軟キャリアは、薄い構造化エピタキシャル層も非常に柔軟であると(弾性太陽電池素子)いうことを利用している。

b3)エピタキシャル層上に…に記載されている。」を「b3)エピタキシャル層上に成形して硬化させることが可能なソル−ゲルガラスの使用。ソル−ゲル手法の詳細については、論文「結晶薄膜においてライトトラップを行うためのソル−ゲル被覆」(R.Brendel et al.,Journal of non-crystalline solids,218(1997),391-394)の「実験」セクションに記載されている。

b4)ガラスへの構造化エピタキシャル層の陽極結合またはSiへのエピタキシャル層の「直接ウエハー結合」。

c)ガラスはエピタキシャル層と共に簡単に分離される。多孔性層は中央部分で一部破損しており、一部は基板に残留しまた別の一部はエピタキシャル層に固着する。2分間の超音波処理により、全ての多孔性Siの残留物は除去される。エピタキシャル層はガラスにしっかりと結合する。剥離の前に超音波処理を実行する場合、ガラスをエピタキシャル層と共に基板から剥離するのに弱い機械的な力が必要である。

c1)軽い振動でエピタキシャル層を(例えば)衝撃的に加熱すると、多孔性層に大きな温度勾配が生じ、これによって多孔性層が破砕する。

c2)多孔性層の中空キャビティに液体または気体を充填する。液体または気体は膨張して、エピタキシャル層を破壊する。

c3)エピタキシャル層に大きな機械的圧力を加える。

c4)多孔性層への共振放射結合は導波管として機能するので、多孔性物質に放射が集中する。

結晶シリコンの薄層太陽電池素子は、例えば[1]の文献から既知である。この文献及び次に挙げられる文書には角括弧内に記された番号が付され、要約の目的で一覧の説明末尾部分に記載されている。結晶シリコンの薄膜太陽電池素子には、本質的に3つの必要事項がある。

多孔性シリコンのエピタキシーは、絶縁基板[6]上へのこの単結晶シリコン層の生成で詳細に調査した。この処理において、エピタキシャル層は温度T>1000℃でのCVD処理により、多孔性表面を有する平坦な単結晶シリコンウエハー上で成長する。次に、エピタキシャル層は、ウエハー結合により絶縁体上に圧着される。そして機械的研削で、基板ウエハーが除去される。残留する多孔性層のケミカルエッチングで処理は完了する。ライトトラッブ特性の欠如、結合処理、基板ウエハーの消耗があるため、コストの面からもこの技術を光起電力技術には使用できない。

b)基板の表面を、厚さWPSの多孔性シリコン層(多孔性Si層、PSL)に変化させる。PSL内のシリコンの配向性は、基板の配向性に関する情報を伝える。

c)シリコンはPSL上に順次エピタキシャルに成長する。PLSの内面でのシリコン原子の表面移動性は850℃を超える温度[7]での焼結処理に至るので、低温エピタキシャル技術は有益である。

この時点では、エピタキシャル層の外面に自由に触れることができる。約850℃未満の温度で行われる各処理によって、セルのエミッタを形成することができる。エピタキシャルエミッタの他に、逆転層や異質接合エミッタが可能である。表面の被膜保護と格子形成については、例えば[5,8,9]に記載されている革新的技術を使用するとよい。

d)上に重なる基板(例えばガラス)は、透明な接着剤で前面に固定される。上に重なる基板及び接着剤の温度安定性によって、その後に行われる全ての処理段階の最高処理温度が決まる。

e)基板からセルを分離させるために、基板シリコンと比較して低いPSLの機械的強度を使用する。複数の様々な処理方法が可能である。例えば、大きな内部応力を生じさせる加熱、膨張する液体または気体の穴の中への充填、圧縮または引っ張り応力によるPSLの引っ張り、あるいは超音波処理が挙げられる。どの場合も、PSLはシリコンの穿孔(Psi)として機能するので、(と呼ぶ。

f)セルの後側は、表面被覆保護及び反射体の形成のために触れることができる。オフセット反射体も、少数電荷キャリアの低組み換えに耐える点接触を形成することができる。

3.1 サンプルの用意

ホウ素で1019cm-3にドープし、(100)の方向を配向され、4インチ直径を有するp+タイプの単結晶シリコンウエハーに、光食刻法及びKOHを使った異方性エッチングにより、周期性p=13μmで逆ピラミッド構造を与える。希釈HFでの陽極腐食法によって、約2分でWPS=6μm厚さの多孔性シリコン層が生成される。エピタキシーの前に、サンプルを約10分間850℃に加熱して、PSL表面から自然発生した酸化物を除去する。WPS=5,8μm厚さのGaドーピングしたエピタキシャルシリコン層は、700℃でのイオン援用沈着技術(IAD)[10]によって成長する。成長速度は、平面で4μm/hになる。透明なポリ(エチレン−フタル塩酸)により、2×2cm2寸法のガラス表面がエピタキシャル層に固定される。約2分間の超音波処理はPSL層を不安定にし、化学エッチングを行わなくてもエピタキシャル層の機械的な除去を用意にする。また、超音波処理を実行することなく、エピタキシャル層及び基板を互いに分離させることも可能である。

図2及び4は、φ処理で生成された自由定常シリコンワッフル構造体を走査電子顕微鏡で記録したものを示している。超音波処理は別として、走査電子顕微鏡を使った調査の前には洗浄は行わない。図2の透視平面図は、基板ウエハーの元の表面構造のコピーである規則的逆ピラミッドを示している。図4はワッフル構造の断面を斜めに示している。ピラミッドの先端は下側を向いている。亀裂は見られない。ピラミッド型の結晶面に垂直な層厚さは、Wf=5.8μmである。上面側には図2及び4の目に見えない窪みがあり、その窪みの深さ及び直径はそれぞれ0.1μm未満である、これは一種の極小粗さを表している。これらの窪みは、非構造化基板シリコン上で成長する平坦なエピタキシャル層でも生じるので、IAD技術に対応する。

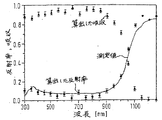

図2及び4に示す形状を有する結晶シリコン層の考えられる効率を、理論モデリングで調査する。光学モデルでは、蒸気のSUNRAYSによる光線追跡を実行する。小数電荷キャリアの生成速度をシリコン層において空間的に均一になるようにし、またこれをjSC*及びセル容積から計算する。光学モデルに加えて、電子伝達のモデルも必要である。シリコンワッフルにおける複雑な三次元電荷キャリア拡散を、ピラミッド型結晶面に垂直な純一次元伝達で概算する。セルの効率は、小数電荷キャリア拡散長さL及び(鏡面組み換え速度SRV)Sによって異なる。固定のL及びS[14]の考えられうる効率を正しく推定するために、セル厚さWfを最適化することは非常に重要である。従って、シミュレーションによって、理想的なセル効率の膜厚さWが変化する。シリコンセルは1019cm-3及び0.5μm厚さにpドープしたエミッタを備え、1018cm-3にBドープした基部を有する。W<1μm厚さの場合、基部及びエミッタの厚さは同一である。自由パラメータの数を減らすために、拡散長さL及び表面組み換え速度Sは基部及びエミッタに対して同等と見なされる。空間電荷ゾーンにおける組み替えを[15]で説明する。cシリコンのバンドギャップ縮小の移動性値及びパラメータは、文書[14]から引用する。

・金属接点を使用せずに済む。溝のエッチングを行わなくてよい。これらにより処理コストを節約できる。

・必要なマスクは1つのみであり、その形状の精度は重要ではない。

・ワイヤー格子を使用しなくてよい。

・ワイヤーが反応装置の加熱領域外に固定されている場合、加熱中にワイヤー間隔が変わることはない。これにより、大きなマスクの熱膨張に伴う未知の問題が回避される。

・シャドーマスクは沈着中に被覆され、時が経つにつれて使用できなくなる。

ワイヤーマスクは、反応装置のワイヤーを再びリールに巻くことで簡単に再生できる。

1.ドープの順序を変えることができる。例えば、n+を最下部に、p+を最上部にする。

2.例えば金属層や、導電及び非導電層の半透明金属酸化物または層系をエミッタ上に設けて、エミッタの相互導電性を高める。これらの層は全てシャドウマスクで設けることができる。

3.ワイヤー直径及びワイヤー間隔を層毎に変えることができる。

4.ワイヤーマスク及びサンプルまたは基板の相対位置を、層の沈着中に連続的に変えることができる。

5.シャドーマスクはワイヤーだけでなく金属片で構成される。

6.シャドーマスクの原理を用いて、所望の外形の半導体層を生成することもできる。例えば、円形開口部を有するマスクを多孔性Si層の前に保持する場合、腕時計の太陽電池素子として使用できる円形単結晶半導体層が生成される。その後、半導体層を所望の形状に切り出す必要はない。

(1) J.H ヴェルナー、R。ベルクマン及びR.ブレンデル共著

「固体問題ノソリッドステート(固体)物理学の進歩」第34巻。R.ヘルビッヒ社発行(1994年、ブラウンシュバイク市フイヴエク)、第15項。

2) R.ブレンデル著、「第13回ヨーロッパ光電池太陽エネルギー会議議事録」発行者、W,フライエスレーベン、W,パルツ、H.Aオセンブリンク及びP.ヘルム(1995年ヘドフォード市フテフェンス)、第436項。

(3) D.ソルプ、P.カムベル及びS.R.ヴェンハム共著「光電池の進歩4」205(1995年)

(4) R.ブレンデル、R.B.ベルクマン、P.リョルゲン、M.ヴォルフ及びJ.H.ヴェルナー共著「応用物理学、レター70」390(1997年)

(5) T.ラウインジャ、J.シュミット、A.G.アベリー及びR.ヘッエル共著「応用物理学、レター68」1232(1995年)

(6) N.佐藤、K.坂口、K.山形、Y.藤山及びT.米沢共著、「日本電気化学協会、142」3116(1995年)

(7) C.オウレス、A.ハリマウイ、J.L.リゴリニイ、R.ヘリノ、A.ペリオ、D.ベンサヘル及びG.ボムチル共著、「材料サイエンス及びエンジニアリングB4」,435(1989年)

(8) R.ヘッエル著、「第24回電気・電子技術者協会、光電池専門家会議、議事録」(ニューヨーク市、電気・電子技術者協会、1995年)第1466項。

(9) G.ヴィルケ及びP.ファース共著「応用物理学、レター64」1274(1994年)

(10) S,オールディング、D.マルティニィ及びD.ボネット共著「第12回ヨーロッパ光電池太陽エネルギー会議、議事録」、発行者、R.ヒル、W.ペルツ及びP.ヘルム(ベドフオード市、H.S.ステフェンス)、第1815項。

(11) M.ショフサーラー及びR.ブレンデル共著,「第一回世界会議、光電池エネルギー変換」(ニューヨーク市、電気・電子技術者協会、1994年)第1509項

(12) M.ショフサーラー及びR.ブレンデル共著,「応用物理学77」3162(1995年)

(13) R.ブレンデル著、「光電池の進歩3」25(1995年)

(14) M.J.ストックス、A.クーバス及びA.W.ブラッカース共著「光電池の進歩4」35(1995)。

(15) S.C.チョー著「ソリッドステート エレクトロン39」308(1996)、Eg3

12 構造体

14 ピラミッド型窪

16 格子

18 多孔性基板、多孔性層

18A 多孔性層

19 境界面

22 エピタキシャルシリコン層

22 層状構造体

22D ピラミッド先端

24 格子電極

25 格子電極

26 ガラス層

28 層状構造体

30 アルミニウムシート

30 金属板

32 ピラミッド型先端

50 溝状断面

52 縦溝

54 ウェブ

54A ウェブ

54A セクション

54B ウェブ残留物

56 接着層

58 キャリア

58 第2基板

60 円筒棒

62 格子電極

72 室

74 圧電素子

76 非晶質層

78 表面

80 バネ

300 領域

301 シャドーマスク

302 溝

304 層

306 n+Si層

400 nタイプエピタキシャル層

402 pタイプエピタキシャル層

404 キャリア

Claims (28)

- 半導体材料からなる層状構造体(28)を製造する層状構造体製造方法において、

半導体基板(10)上に多孔性層(18)が形成され、

上記多孔性層上に層状構造体(28)が設けられ、

上記層状構造体は、多孔性層を目的の分離位置として利用して半導体基板から分離され、

上記半導体基板の表面が多孔性層の生成前に構造化されるか、あるいは上記多孔性層の表面が構造化され、

上記層状構造体が少なくとも部分的にエピタキシャル成長により多孔性表面上に設けられ、層状構造体に属する少なくとも1つの半導体層がエピタキシャル成長によって多孔性層の表面上に設けられる、

ことを特徴とする層状構造体製造方法。 - 上記半導体基板の表面が、

a)光食刻法

b)食刻処理

c)化学的方法

d)機械的フライス削り

e)レーザー処理

の内1つまたは複数の方法によって構造化される、ことを特徴とする請求項1に記載の層状構造体製造方法。 - 上記多孔性層の表面が、

a)光食刻法

b)食刻処理

c)化学的方法

d)機械的フライス削り

e)レーザー処理

f)機械的コイニング

の内1つまたは複数の方法によって構造化される、ことを特徴とする請求項1に記載の層状構造体製造方法。 - 上記層状構造体が金属層(30)の付着によって少なくとも部分的に形成され、金属層は加熱及び表面拡散によって層状構造体の隣接物質に施行される、ことを特徴とする請求項1から3の何れか1項に記載の層状構造体製造方法。

- 上記層状構造体の形成過程は、透明または光透過ウィンドウ層(26)の形成において、誘電体を設ける過程を含む、ことを特徴とする請求項1から4の何れか1項に記載の層状構造体製造方法。

- 接着結合、ウエハー結合、または拡散蝋着法によって層状構造体に結合するか、あるいは層状構造体の一部として形成されるキャリア層を設ける、ことを特徴とする請求項1から5の何れか1項に記載の層状構造体製造方法。

- 上記半導体基板から層状構造体を分離した後、目的の破砕位置を形成する層状構造体の、任意で構造化した表面に別の層状構造体を設ける、ことを特徴とする請求項1から6の何れか1項に記載の層状構造体製造方法。

- 上記別の層状構造体を設ける前に、層状構造体の表面を、洗浄及び/または部分的除去及び/または新規構造化または多孔化する、ことを特徴とする請求項7に記載の層状構造体製造方法。

- 目的の破砕位置で半導体基板から層状構造体を分離した後、多孔性層の残留物を除去してからあるいは除去しないまま、半導体基板を層状構造体を設けるための半導体基板として再び使用する、ことを特徴とする請求項1から8の何れか1項に記載の層状構造体製造方法。

- 構造化多孔性層、すなわち非平坦平行板形状の多孔性層を有する半導体基板を新たに使用する場合、最後に使用した半導体基板にエッチングまたは超音波洗浄処理によって行われる洗浄処理を施す、ことを特徴とする請求項9に記載の層状構造体製造方法。

- 上記半導体基板から層状構造体を分離する前または後で、半導体基板から離れた層状構造体の表面に別の多孔性層を生成し、さらにその上に別の層状構造体を形成する、ことを特徴とする請求項1から10の何れか1項に記載の層状構造体製造方法。

- 各別の層状構造体は、エピタキシャル成長によって、半導体基板の方を向くように形成された層状構造体の表面で成長する、ことを特徴とする請求項11に記載の層状構造体製造方法。

- 上記半導体基板は、単結晶pタイプSiまたは単結晶nタイプSiから成る、ことを特徴とする請求項1から12の何れか1項に記載の層状構造体製造方法。

- 上記層状構造体またはその一部は、多孔性層内または多孔性層との界面での機械的応力の生成中に半導体基板から分離される、ことを特徴とする請求項1から13の何れか1項に記載の層状構造体製造方法。

- 上記多孔性層内で作用し、半導体基板から層状構造体またはその一部を分離させる機械的応力の生成は、

a)半導体基板からの層状半導体基板の剥離

b)超音波処理

c)強熱勾配の生成

d)多孔性層の孔に充填された流体(気体または液体)または溶剤の、膨張または状態変化(液相から気相、液相から固相への変化)

の何れかの方法によって行われる、ことを特徴とする請求項1から14の何れか1項に記載の層状構造体製造方法。 - 半導体材料からなる層状構造体(28)を製造する層状構造体製造方法において、

半導体基板(10)上に多孔性層(18)が形成され、

上記多孔性層上に層状構造体(28)が設けられ、

上記層状構造体は、多孔性層を目的の分離位置として利用して半導体基板から分離され、

上記半導体基板の表面が多孔性層の生成前に構造化されるか、あるいは上記多孔性層の表面が構造化され、

上記層状構造体が少なくとも部分的にエピタキシャル成長により多孔性表面上に設けられ、層状構造体に属する少なくとも1つの半導体層がエピタキシャル成長によって多孔性層の表面上に設けられ、

上記半導体基板から層状構造体を分離する前または後で、半導体基板から離れた層状構造体の表面に別の多孔性層を生成し、さらにその上に別の層状構造体を形成し、この形成処理を複数回繰り返し、目的の破砕位置を形成する多孔性層によって隣接する層状構造体から互いに分離している構造化された層状構造体が互いに重なり合って生成され、この多重の層状構造体を生成した後、各多孔性層内で機械的歪みを発生させることによりまたは各多孔性層との境界面での陽極化処理によりそれぞれの層状構造体を互いに分離する、

ことを特徴とする層状構造体製造方法。 - それぞれの層状構造体の分離後、各層状構造体の一方及び/または他方の自由表面に別の層状構造体を生成する、ことを特徴とする請求項16に記載の層状構造体製造方法。

- 上記多重の層状構造体から各層状構造体を分離する前は、各層状構造体はそれぞれキャリア層(404)を備えているかあるいはキャリア層(404)に固定されている、ことを特徴とする請求項16に記載の層状構造体製造方法。

- 表面上に多孔性層(18)を有する半導体基板(10)であって、

上記多孔性層(18)の自由表面が構造化されている、ことを特徴とする半導体基板(10)。 - 上記半導体基板は単結晶から成る、ことを特徴とする請求項19に記載の半導体基板。

- エピタキシャル成長によって多孔性層の表面上で成長する、半導体材料から成る層状構造体(28)と結合する、ことを特徴とする請求項19に記載の半導体基板。

- 上記多孔性層の構造化された表面に付着した第2基板と結合する、ことを特徴とする請求項19に記載の半導体基板。

- 上記第2基板と多孔性層との結合は、接着剤、結合処理、拡散蝋着処理、またはエピタキシャル処理によって実現される、ことを特徴とする請求項22に記載の半導体基板。

- 上記層状構造体は単結晶半導体材料から成り、半導体基板から離れた層状構造体の表面は半導体基板の多孔性層の自由表面と同じ表面構造を有し、またこの表面構造を削除して平面にすることが可能であり、更に該表面を同様にこの構造化された層上に配置した別の層状構造体を有する多孔性層として実現する、ことを特徴とする請求項21に記載の半導体基板。

- 請求項19から24の何れか1項に記載の半導体基板(10,18)を使用するとともに、異なる導電率、及び/または異なる伝導型タイプの複数の層(300,304,306)を各々含む太陽電池素子の直列接続回路を製造する素子回路製造方法において、

上記半導体基板の多孔性層上への各層(300,304,306)の沈着時に、シャドーマスク(301)が、半導体基板の前に配置され、沈着される原子の移動方向に交差し、層の選択的な成長の制御に使用される、ことを特徴とする素子回路製造方法。 - 層の成長中または各層(300,304,306)の成長の合間に、シャドーマスク(301)と半導体基板(10)は互いに平行に配置され、シャドーマスクの第1位置で第1伝導型タイプの層(300)の層領域間でトレンチ(302)を生成し、またシャドーマスクの別の位置で第2伝導型タイプの層(306)の端部領域と、該トレンチ(302)に隣接する第1伝導型タイプの層(300)の露出端部領域との間に重なり部分を生成し、これによって2つの端部領域間、すなわち該トレンチの両側の層によって形成される2つの半導体素子間が直列接続される、ことを特徴とする請求項25に記載の素子回路製造方法。

- 上記シャドウマスクは、所望の断面形状のワイヤーから形成される、ことを特徴とする請求項25または26に記載の素子回路製造方法。

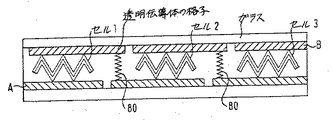

- 請求項25から27の何れか1項に記載の方法によって製造される太陽電池素子の直列接続回路において、

トレンチ(302)によって互いに分離される第1伝導型タイプの層(300)の第1及び第2領域と、

第2伝導型タイプの層(306)であり、第1伝導型タイプの層の真上に沈着されるかあるいは他の層によって第1伝導型タイプの層から分離される当該第2伝導型タイプの層(306)の第1及び第2領域と、

トレンチ(302)を覆って横断するとともに、第1伝導型タイプの層(300)の第2領域の端部領域に直接重なるの第2伝導型タイプ(306)の第1領域の端部領域と、

を有することを特徴とする太陽電池素子の直列接続回路。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE19727791 | 1997-06-30 | ||

| DE19730975A DE19730975A1 (de) | 1997-06-30 | 1997-07-18 | Verfahren zur Herstellung von schichtartigen Gebilden auf einem Substrat, Substrat sowie mittels des Verfahrens hergestellte Halbleiterbauelemente |

| DE19758300 | 1997-12-31 | ||

| DE19730975.5 | 1997-12-31 | ||

| DE19758300.8 | 1997-12-31 | ||

| DE19727791.8 | 1997-12-31 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP50631999A Division JP4473349B2 (ja) | 1997-06-30 | 1998-06-30 | 層状構造体製造方法、及び半導体基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010045391A true JP2010045391A (ja) | 2010-02-25 |

| JP5637473B2 JP5637473B2 (ja) | 2014-12-10 |

Family

ID=40076291

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009258859A Expired - Fee Related JP5637473B2 (ja) | 1997-06-30 | 2009-11-12 | 層状構造体製造方法、半導体基板、素子回路製造方法、及び太陽電池素子の直列接続回路 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP5637473B2 (ja) |

| DE (1) | DE59814320D1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013191342A (ja) * | 2012-03-13 | 2013-09-26 | Ushio Inc | 色素増感型太陽電池 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05217821A (ja) * | 1992-01-31 | 1993-08-27 | Canon Inc | 半導体基板の作製方法 |

| JPH07302889A (ja) * | 1994-03-10 | 1995-11-14 | Canon Inc | 半導体基板の作製方法 |

| JPH08213645A (ja) * | 1995-02-02 | 1996-08-20 | Sony Corp | 基体から素子形成層を分離する方法 |

| JPH1079524A (ja) * | 1996-09-04 | 1998-03-24 | Sony Corp | 薄膜太陽電池の製造方法 |

| JPH10326758A (ja) * | 1997-03-26 | 1998-12-08 | Canon Inc | 薄膜の形成方法 |

-

1998

- 1998-06-30 DE DE59814320T patent/DE59814320D1/de not_active Expired - Lifetime

-

2009

- 2009-11-12 JP JP2009258859A patent/JP5637473B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05217821A (ja) * | 1992-01-31 | 1993-08-27 | Canon Inc | 半導体基板の作製方法 |

| JPH07302889A (ja) * | 1994-03-10 | 1995-11-14 | Canon Inc | 半導体基板の作製方法 |

| JPH08213645A (ja) * | 1995-02-02 | 1996-08-20 | Sony Corp | 基体から素子形成層を分離する方法 |

| JPH1079524A (ja) * | 1996-09-04 | 1998-03-24 | Sony Corp | 薄膜太陽電池の製造方法 |

| JPH10326758A (ja) * | 1997-03-26 | 1998-12-08 | Canon Inc | 薄膜の形成方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013191342A (ja) * | 2012-03-13 | 2013-09-26 | Ushio Inc | 色素増感型太陽電池 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5637473B2 (ja) | 2014-12-10 |

| DE59814320D1 (de) | 2009-01-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4473349B2 (ja) | 層状構造体製造方法、及び半導体基板 | |

| JP3619053B2 (ja) | 光電変換装置の製造方法 | |

| JP4838409B2 (ja) | 支持基板上に薄い層を形成するための方法 | |

| JP3492142B2 (ja) | 半導体基材の製造方法 | |

| CN102763226B (zh) | 使用薄平面半导体的高效光伏背触点太阳能电池结构和制造方法 | |

| JPWO1998043304A1 (ja) | 光起電力素子及びその製造方法 | |

| JP2004235274A (ja) | 多結晶シリコン基板およびその粗面化法 | |

| WO2000045426A1 (en) | Method for fabricating thin film semiconductor devices | |

| KR101027493B1 (ko) | 와이어 어레이를 이용한 태양광 전지 및 그 제조 방법 | |

| JPH11214720A (ja) | 薄膜結晶太陽電池の製造方法 | |

| US8173452B1 (en) | Method to form a device by constructing a support element on a thin semiconductor lamina | |

| CN102137959A (zh) | 晶体制造装置、使用该晶体制造装置制造的半导体设备以及使用该晶体制造装置制造半导体设备的方法 | |

| JP2943126B2 (ja) | 太陽電池及びその製造方法 | |

| JP3777668B2 (ja) | 薄膜太陽電池の製造方法 | |

| CN104362209B (zh) | 一种背面抛光晶硅太阳能电池及其制备工艺 | |

| JP2006156646A (ja) | 太陽電池の製造方法 | |

| JPH11214725A (ja) | 光電変換装置の製造方法 | |

| JP5637473B2 (ja) | 層状構造体製造方法、半導体基板、素子回路製造方法、及び太陽電池素子の直列接続回路 | |

| JP2000036609A (ja) | 太陽電池の製造方法と薄膜半導体の製造方法、薄膜半導体の分離方法及び半導体形成方法 | |

| JP2002076404A (ja) | シリコン基板の粗面化法 | |

| JP3542521B2 (ja) | 半導体基体及び太陽電池の製造方法と陽極化成装置 | |

| TWI376813B (en) | Solar cell with backside passivation | |

| JP2007142471A (ja) | 太陽電池の製造方法 | |

| JPH1168133A (ja) | 薄膜素子モジュールおよびその製造方法 | |

| JP4247964B2 (ja) | 太陽電池素子の形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091211 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121002 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121228 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130108 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130130 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130204 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130618 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131017 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20131213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140218 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140513 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140516 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140603 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140826 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140827 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140916 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141010 |

|

| LAPS | Cancellation because of no payment of annual fees |