JP2010045353A - 基板上にパターン金属を誘導する方法 - Google Patents

基板上にパターン金属を誘導する方法 Download PDFInfo

- Publication number

- JP2010045353A JP2010045353A JP2009182935A JP2009182935A JP2010045353A JP 2010045353 A JP2010045353 A JP 2010045353A JP 2009182935 A JP2009182935 A JP 2009182935A JP 2009182935 A JP2009182935 A JP 2009182935A JP 2010045353 A JP2010045353 A JP 2010045353A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- directing

- transistor

- conductive

- pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 144

- 229910052751 metal Inorganic materials 0.000 title claims abstract description 45

- 239000002184 metal Substances 0.000 title claims abstract description 45

- 238000000034 method Methods 0.000 title claims description 72

- 230000001939 inductive effect Effects 0.000 title claims description 4

- 238000010884 ion-beam technique Methods 0.000 claims abstract description 32

- 238000004070 electrodeposition Methods 0.000 claims abstract description 31

- 238000000151 deposition Methods 0.000 claims abstract description 30

- 239000004020 conductor Substances 0.000 claims abstract description 22

- 230000008021 deposition Effects 0.000 claims abstract description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims abstract description 16

- 239000002243 precursor Substances 0.000 claims abstract description 16

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 16

- 239000010703 silicon Substances 0.000 claims abstract description 16

- 238000004519 manufacturing process Methods 0.000 claims abstract description 14

- 238000005530 etching Methods 0.000 claims abstract description 12

- 150000002500 ions Chemical class 0.000 claims description 36

- 239000000463 material Substances 0.000 claims description 31

- 239000003792 electrolyte Substances 0.000 claims description 26

- 239000002019 doping agent Substances 0.000 claims description 18

- 239000004065 semiconductor Substances 0.000 claims description 18

- 239000002245 particle Substances 0.000 claims description 15

- 239000007769 metal material Substances 0.000 claims description 13

- 230000008859 change Effects 0.000 claims description 11

- 238000006243 chemical reaction Methods 0.000 claims description 10

- 230000004907 flux Effects 0.000 claims description 10

- 229920002120 photoresistant polymer Polymers 0.000 claims description 10

- 230000001965 increasing effect Effects 0.000 claims description 9

- 238000010894 electron beam technology Methods 0.000 claims description 8

- 230000000737 periodic effect Effects 0.000 claims description 6

- 238000012544 monitoring process Methods 0.000 claims description 4

- 239000007943 implant Substances 0.000 claims description 3

- 238000005498 polishing Methods 0.000 claims description 3

- 229910001111 Fine metal Inorganic materials 0.000 claims description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical group [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 abstract description 9

- CKHJYUSOUQDYEN-UHFFFAOYSA-N gallium(3+) Chemical compound [Ga+3] CKHJYUSOUQDYEN-UHFFFAOYSA-N 0.000 abstract description 4

- 150000002739 metals Chemical class 0.000 abstract description 3

- 239000010410 layer Substances 0.000 description 68

- 239000000523 sample Substances 0.000 description 20

- 230000008569 process Effects 0.000 description 19

- 238000010586 diagram Methods 0.000 description 15

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical group [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 12

- 229910052733 gallium Inorganic materials 0.000 description 12

- 239000007789 gas Substances 0.000 description 10

- 238000009713 electroplating Methods 0.000 description 9

- 238000003801 milling Methods 0.000 description 9

- 238000009792 diffusion process Methods 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 239000008151 electrolyte solution Substances 0.000 description 6

- 238000012360 testing method Methods 0.000 description 6

- 238000003384 imaging method Methods 0.000 description 5

- 238000001888 ion beam-induced deposition Methods 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 4

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 238000004458 analytical method Methods 0.000 description 3

- 229910000365 copper sulfate Inorganic materials 0.000 description 3

- ARUVKPQLZAKDPS-UHFFFAOYSA-L copper(II) sulfate Chemical compound [Cu+2].[O-][S+2]([O-])([O-])[O-] ARUVKPQLZAKDPS-UHFFFAOYSA-L 0.000 description 3

- OPQARKPSCNTWTJ-UHFFFAOYSA-L copper(ii) acetate Chemical compound [Cu+2].CC([O-])=O.CC([O-])=O OPQARKPSCNTWTJ-UHFFFAOYSA-L 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 229910001338 liquidmetal Inorganic materials 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 238000007747 plating Methods 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- BLIQUJLAJXRXSG-UHFFFAOYSA-N 1-benzyl-3-(trifluoromethyl)pyrrolidin-1-ium-3-carboxylate Chemical compound C1C(C(=O)O)(C(F)(F)F)CCN1CC1=CC=CC=C1 BLIQUJLAJXRXSG-UHFFFAOYSA-N 0.000 description 2

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 102100031237 Cystatin-A Human genes 0.000 description 2

- 101000921786 Homo sapiens Cystatin-A Proteins 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- -1 argon ions Chemical class 0.000 description 2

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 2

- 229910052794 bromium Inorganic materials 0.000 description 2

- FQNHWXHRAUXLFU-UHFFFAOYSA-N carbon monoxide;tungsten Chemical group [W].[O+]#[C-].[O+]#[C-].[O+]#[C-].[O+]#[C-].[O+]#[C-].[O+]#[C-] FQNHWXHRAUXLFU-UHFFFAOYSA-N 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000003487 electrochemical reaction Methods 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- PNDPGZBMCMUPRI-UHFFFAOYSA-N iodine Chemical compound II PNDPGZBMCMUPRI-UHFFFAOYSA-N 0.000 description 2

- 229910021645 metal ion Inorganic materials 0.000 description 2

- 238000005459 micromachining Methods 0.000 description 2

- LGQLOGILCSXPEA-UHFFFAOYSA-L nickel sulfate Chemical compound [Ni+2].[O-]S([O-])(=O)=O LGQLOGILCSXPEA-UHFFFAOYSA-L 0.000 description 2

- 229910000363 nickel(II) sulfate Inorganic materials 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 239000000047 product Substances 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 239000011163 secondary particle Substances 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- QAOWNCQODCNURD-UHFFFAOYSA-L Sulfate Chemical compound [O-]S([O-])(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-L 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- XKRFYHLGVUSROY-UHFFFAOYSA-N argon Substances [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 239000002659 electrodeposit Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000012467 final product Substances 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 238000001746 injection moulding Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052755 nonmetal Inorganic materials 0.000 description 1

- 150000002902 organometallic compounds Chemical class 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000011253 protective coating Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/30—Electron-beam or ion-beam tubes for localised treatment of objects

- H01J37/305—Electron-beam or ion-beam tubes for localised treatment of objects for casting, melting, evaporating, or etching

- H01J37/3053—Electron-beam or ion-beam tubes for localised treatment of objects for casting, melting, evaporating, or etching for evaporating or etching

- H01J37/3056—Electron-beam or ion-beam tubes for localised treatment of objects for casting, melting, evaporating, or etching for evaporating or etching for microworking, e. g. etching of gratings or trimming of electrical components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/30—Electron-beam or ion-beam tubes for localised treatment of objects

- H01J37/317—Electron-beam or ion-beam tubes for localised treatment of objects for changing properties of the objects or for applying thin layers thereon, e.g. for ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/30—Electron-beam or ion-beam tubes for localised treatment of objects

- H01J37/317—Electron-beam or ion-beam tubes for localised treatment of objects for changing properties of the objects or for applying thin layers thereon, e.g. for ion implantation

- H01J37/3178—Electron-beam or ion-beam tubes for localised treatment of objects for changing properties of the objects or for applying thin layers thereon, e.g. for ion implantation for applying thin layers on objects

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

- H01L21/2885—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition using an external electrical current, i.e. electro-deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/006—Details of gas supplies, e.g. in an ion source, to a beam line, to a specimen or to a workpiece

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/31701—Ion implantation

- H01J2237/31706—Ion implantation characterised by the area treated

- H01J2237/3171—Ion implantation characterised by the area treated patterned

- H01J2237/31713—Focused ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/31732—Depositing thin layers on selected microareas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/31735—Direct-write microstructures

- H01J2237/31737—Direct-write microstructures using ions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/3174—Etching microareas

- H01J2237/31742—Etching microareas for repairing masks

- H01J2237/31744—Etching microareas for repairing masks introducing gas in vicinity of workpiece

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/3174—Etching microareas

- H01J2237/31745—Etching microareas for preparing specimen to be viewed in microscopes or analyzed in microanalysers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/30—Electron or ion beam tubes for processing objects

- H01J2237/317—Processing objects on a microscale

- H01J2237/31749—Focused ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76886—Modifying permanently or temporarily the pattern or the conductivity of conductive members, e.g. formation of alloys, reduction of contact resistances

- H01L21/76892—Modifying permanently or temporarily the pattern or the conductivity of conductive members, e.g. formation of alloys, reduction of contact resistances modifying the pattern

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/14—Measuring as part of the manufacturing process for electrical parameters, e.g. resistance, deep-levels, CV, diffusions by electrical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Analytical Chemistry (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Plasma & Fusion (AREA)

- Electrodes Of Semiconductors (AREA)

- Electroplating Methods And Accessories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Micromachines (AREA)

- Drying Of Semiconductors (AREA)

- Weting (AREA)

Abstract

【解決手段】導電率が高められたパターン形成された領域を生成し、または露出させ、次いでこの領域上に、電着を使用して導体を形成することによって、微小金属構造が製造される。いくつかの実施形態では、基板上に微小金属構造が形成され、次いで基板からこの構造を除去するために、基板がエッチングされる。いくつかの実施形態では、付着前駆体ガスを含まない集束ガリウム・イオン・ビームが、シリコン基板上をあるパターンで走査して、導電パターンを生成し、次いでこの導電パターン上に、1種または数種の金属の電気化学付着によって銅構造が形成される。エッチングによってこの構造を基板から取り出すことができ、またはその場で使用することができる。ビームを使用して、トランジスタの活性層にアクセスすることができ、導体を電着させて、トランジスタが機能している間にその動作を感知しまたは変化させるためのリードを形成することができる。

【選択図】図1

Description

付着前駆体ガスが存在しない状況で基板表面に向かって集束ビームを誘導して、導電シード・パターンを生成するステップと、

導電シード・パターンの少なくとも一部分を電解液で覆うステップと、

電解液を通して導電パターンに電流を流して、導電シード・パターン上に導電材料を付着させるステップとを含む。

より高導電率の層を覆っている、より低導電率の層に向かって集束ビームを誘導するステップであり、より高導電率の層が、電着反応を支えるのに十分な導電率を有し、より低導電率の層が、電着反応を支えるには不十分な導電率を有し、集束ビームが、ビームが衝突した位置において電着反応を支えるために、より高導電率の層の少なくとも一部分を露出させるステップ、

荷電粒子ビームをある2次元パターンに誘導するステップ、

荷電粒子ビームを誘導して、ある3次元構造を除去しまたは追加するステップ、

トランジスタの活性領域と接触するために、荷電粒子ビームを誘導して基板の一部分を除去するステップ

を含むことができ、かつ/あるいは、

電解液を通して導電パターンに電流を流して導電材料を付着させるステップが、活性領域への電気接触を提供する導電リードを付着させるステップを含む。

前駆体ガスが存在しない状況で基板に向かってイオンまたは原子を誘導して、導電率が高められたパターン形成された領域を生成するステップと、

導電率が高められたパターン形成された領域の上に金属材料を電気化学付着させるステップとを含む。

基板の上にフォトレジスト層を塗布するステップ、

フォトレジストを露光するステップ、

フォトレジストを現像して、露出した基板表面のパターンを残すステップ、

基板の露出した領域を、イオン・フラックスまたは原子フラックスに露出するステップ、および/または

残ったフォトレジストを除去するステップを含む。

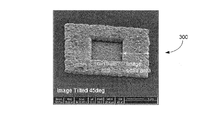

基板に集束ビームを誘導して、導電パターンを形成するステップと、

導電パターン上へ金属材料を電着させて、微小金属構造を形成するステップと、

基板から微小金属構造を取り出すステップとを含む。

基板を全体的に薄化するステップと、

基板のトランジスタの上のある領域をさらに薄化するステップと、

荷電粒子ビームを誘導して、トランジスタの活性領域にアクセスするための穴をミリングするステップと、

穴の中に導体を電着させて、トランジスタの活性領域への電気接触を提供するステップとを含む。

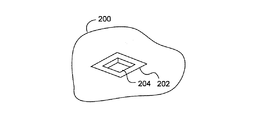

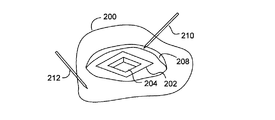

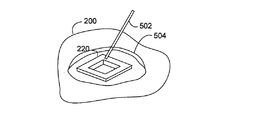

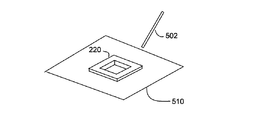

202 より大きな領域

204 より小さな領域

208 電解液

210 電極

212 第2の電極

220 付着構造

502 プローブ

504 選択エッチング剤

510 別の基板

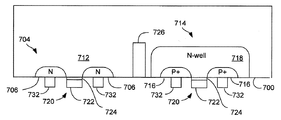

700 薄化された基板

702 CMOSトランジスタ

704 PチャネルMOSFET

706 N領域

712 P型基板領域

714 NチャネルMOSFET

716 P+領域

718 Nウェル領域

732 導電コンタクト

740 トレンチ

742 穴

750 電解液

752 電極

756 金属材料

760 キャップ

762 プローブ

Claims (33)

- 微小導電構造を製造する方法であって、

付着前駆体ガスが存在しない状況で基板表面に向かって集束ビームを誘導して、導電シード・パターンを生成するステップと、

前記導電シード・パターンの少なくとも一部分を電解液で覆うステップと、

前記電解液を通して前記導電パターンに電流を流して、前記導電シード・パターン上に導電材料を付着させるステップと

を含む方法。 - 基板表面に向かって集束ビームを誘導するステップが、半導体基板内へドーパント・イオンの集束ビームを誘導して、前記基板表面内にドーパント原子粒子を注入するステップを含む、請求項1に記載の方法。

- 基板表面に向かって集束ビームを誘導するステップが、周期表の第3または第5列からなるグループからのイオンのビームを誘導するステップを含み、前記基板が、周期表の第4列からなるグループからの材料からなる、請求項1または2に記載の方法。

- 前記基板表面に向かって集束ビームを誘導するステップが、より高導電率の層を覆っている、より低導電率の層に向かって集束ビームを誘導するステップを含み、前記より高導電率の層が、電着反応を支えるのに十分な導電率を有し、前記より低導電率の層が、電着反応を支えるには不十分な導電率を有し、前記集束ビームが、前記ビームが衝突した位置において電着反応を支えるために、前記より高導電率の層の少なくとも一部分を露出させる、請求項1〜3のいずれかに記載の方法。

- より高導電率の層を覆っている、より低導電率の層に向かって集束ビームを誘導するステップが、ドープされた半導体シリコン層の上の酸化物層に向かって集束イオン・ビームを誘導するステップを含む、請求項4に記載の方法。

- より高導電率の層を覆っている、より低導電率の層に向かって集束ビームを誘導するステップが、前記より低導電率の層に向かってレーザ・ビームまたは電子ビームを誘導するステップを含む、請求項4に記載の方法。

- 前記基板上に前記より低導電率の層を成長させる、または付着させるステップをさらに含む、請求項4〜6のいずれかに記載の方法。

- 付着前駆体ガスが存在しない状況で基板表面に向かって集束ビームを誘導して導電シード・パターンを生成するステップが、基板内のある構造を除去するステップを含む、請求項1〜7のいずれかに記載の方法。

- 基板表面に向かって集束ビームを誘導するステップが、荷電粒子ビームをある2次元パターンに誘導するステップを含む、請求項1〜8のいずれかに記載の方法。

- 基板表面に向かって集束ビームを誘導するステップが、荷電粒子ビームを誘導して、ある3次元構造を除去しまたは追加するステップを含む、請求項1〜9のいずれかに記載の方法。

- 基板表面に向かって集束ビームを誘導するステップが、トランジスタの活性領域と接触するために、荷電粒子ビームを誘導して基板の一部分を除去するステップを含み、

前記電解液を通して前記導電パターンに電流を流して導電材料を付着させるステップが、前記活性領域への電気接触を提供する導電リードを付着させるステップを含む、

請求項1に記載の方法。 - 前記導電リードを通して、前記トランジスタの電気動作を感知するステップをさらに含む、請求項11に記載の方法。

- 前記リードに電流源または電圧源を提供して、動作中の前記トランジスタの特性を変化させるステップをさらに含む、請求項11または12に記載の方法。

- 前記基板をエッチングして、前記導電材料を取り出すステップをさらに含む、請求項11〜13のいずれかに記載の方法。

- 前記電流を監視して、前記導電シード・パターン上の導電材料の付着速度または付着量を決定するステップをさらに含む、請求項1〜14のいずれかに記載の方法。

- 微小導電構造を製造する方法であって、

前駆体ガスが存在しない状況で基板に向かってイオンまたは原子を誘導して、導電率が高められたパターン形成された領域を生成するステップと、

前記導電率が高められたパターン形成された領域の上に金属材料を電気化学付着させるステップと

を含む方法。 - 前駆体ガスが存在しない状況で基板に向かってイオンまたは原子を誘導するステップが、前記基板に向かって集束イオン・ビームをあるパターンで走査するステップを含む、請求項16に記載の方法。

- 電着中に電流または電圧を監視して、電着の付着速度または付着量を決定するステップをさらに含む、請求項16または17に記載の方法。

- 前駆体ガスが存在しない状況で基板に向かってイオンまたは原子を誘導するステップが、

基板の上にフォトレジスト層を塗布するステップと、

前記フォトレジストを露光するステップと、

前記フォトレジストを現像して、露出した基板表面のパターンを残すステップと、

前記基板の露出した領域を、イオン・フラックスまたは原子フラックスに露出するステップと、

残ったフォトレジストを除去するステップと

を含む、請求項16〜18のいずれかに記載の方法。 - 前記基板の露出した領域を、イオン・フラックスまたは原子フラックスに露出するステップが、ドーパント・イオンまたはドーパント原子を注入することによって、前記露出した基板表面の導電率を増大させるステップを含む、請求項19に記載の方法。

- 前記基板の露出した領域を、イオン・フラックスまたは原子フラックスに露出するステップが、低導電率層を除去することによって、前記露出した基板表面の導電率を増大させるステップを含む、請求項19に記載の方法。

- 微小金属構造を製造する方法であって、

基板に集束ビームを誘導して、導電パターンを形成するステップと、

前記導電パターン上へ金属材料を電着させて、前記微小金属構造を形成するステップと、

前記基板から前記微小金属構造を取り出すステップと

を含む方法。 - 前記基板から前記微小金属構造を取り出すステップが、前記微小金属構造の下の前記基板をエッチングするステップを含む、請求項22に記載の方法。

- 導電パターンを形成するステップが金属材料を付着させるステップを含み、前記基板から前記微小金属構造を取り出すステップが前記金属材料をエッチングするステップを含む、請求項22に記載の方法。

- 導電パターンを形成するステップが金属材料を付着させるステップを含む、請求項24に記載の方法。

- 下面の方に金属層を有するパッケージ上に取り付けられた集積回路上のトランジスタの特性を決定する方法であって、

前記基板を全体的に薄化するステップと、

前記基板の前記トランジスタの上のある領域をさらに薄化するステップと、

荷電粒子ビームを誘導して、前記トランジスタの活性領域にアクセスするための穴をミリングするステップと、

前記穴の中に導体を電着させて、前記トランジスタの前記活性領域への電気接触を提供するステップと

を含む方法。 - 前記基板を全体的に薄化するステップが、前記基板を研磨するステップを含み、

前記基板のある領域をさらに薄化するステップが、レーザ・ビームを誘導して、前記基板から材料を除去するステップを含む、

請求項26に記載の方法。 - 荷電粒子ビームを誘導して、活性領域にアクセスするための穴をミリングするステップが、ビームの衝突点に向かってエッチング強化ガスを誘導するステップを含む、請求項26または27に記載の方法。

- 荷電粒子ビームを誘導して、前記トランジスタの活性領域にアクセスするための穴をミリングするステップが、イオン・ビームを誘導するステップを含み、前記方法が、エッチング剤を使用して、注入されたイオンを前記穴の側壁から除去するステップを含む、請求項26〜28のいずれかに記載の方法。

- 電気ノードを電気的に接触させて、前記トランジスタの動作中に前記トランジスタの特性を観察するステップをさらに含む、請求項26〜29のいずれかに記載の方法。

- 電気ノードを電気的に接触させて、動作中に前記トランジスタの動作を変化させるステップをさらに含む、請求項26〜30のいずれかに記載の方法。

- 動作中に前記トランジスタの動作を変化させるステップが、前記電気接触を通して電圧を印加し、または前記電気接触を通して電流を注入するステップを含む、請求項31に記載の方法。

- 前記トランジスタがCMOSトランジスタである、請求項26〜32のいずれかに記載の方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US8760508P | 2008-08-08 | 2008-08-08 | |

| US61/087,605 | 2008-08-08 | ||

| US12/210,781 US8278220B2 (en) | 2008-08-08 | 2008-09-15 | Method to direct pattern metals on a substrate |

| US12/210,781 | 2008-09-15 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014094903A Division JP2014187371A (ja) | 2008-08-08 | 2014-05-01 | 半導体試験方法 |

| JP2014094902A Division JP2014187370A (ja) | 2008-08-08 | 2014-05-01 | 微小金属構造の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010045353A true JP2010045353A (ja) | 2010-02-25 |

| JP2010045353A5 JP2010045353A5 (ja) | 2012-08-30 |

| JP5656311B2 JP5656311B2 (ja) | 2015-01-21 |

Family

ID=41228378

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009182935A Expired - Fee Related JP5656311B2 (ja) | 2008-08-08 | 2009-08-06 | 基板上にパターン金属を誘導する方法 |

| JP2014094903A Withdrawn JP2014187371A (ja) | 2008-08-08 | 2014-05-01 | 半導体試験方法 |

| JP2014094902A Withdrawn JP2014187370A (ja) | 2008-08-08 | 2014-05-01 | 微小金属構造の製造方法 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014094903A Withdrawn JP2014187371A (ja) | 2008-08-08 | 2014-05-01 | 半導体試験方法 |

| JP2014094902A Withdrawn JP2014187370A (ja) | 2008-08-08 | 2014-05-01 | 微小金属構造の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8278220B2 (ja) |

| EP (2) | EP2151859A3 (ja) |

| JP (3) | JP5656311B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012252004A (ja) * | 2011-06-03 | 2012-12-20 | Fei Co | Tem画像化用の薄い試料を作製する方法 |

| JP2015130471A (ja) * | 2014-01-02 | 2015-07-16 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | チップ電子部品の製造方法 |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2199434A1 (en) * | 2008-12-19 | 2010-06-23 | FEI Company | Method for forming microscopic structures on a substrate |

| EP2226830B1 (en) | 2009-03-06 | 2014-01-08 | FEI Company | Charged particle beam processing |

| EP2261395A1 (en) * | 2009-06-12 | 2010-12-15 | Fei Company | Au-containing layer obtainable by charged particle beam processing |

| CN103403520B (zh) | 2011-01-28 | 2015-12-23 | Fei公司 | Tem样品制备 |

| US8986524B2 (en) | 2011-01-28 | 2015-03-24 | International Business Machines Corporation | DNA sequence using multiple metal layer structure with different organic coatings forming different transient bondings to DNA |

| JP2013101929A (ja) | 2011-11-07 | 2013-05-23 | Fei Co | 荷電粒子ビーム・システムの絞り |

| US9733164B2 (en) | 2012-06-11 | 2017-08-15 | Fei Company | Lamella creation method and device using fixed-angle beam and rotating sample stage |

| US8759764B2 (en) | 2012-06-29 | 2014-06-24 | Fei Company | On-axis detector for charged particle beam system |

| US9046511B2 (en) | 2013-04-18 | 2015-06-02 | International Business Machines Corporation | Fabrication of tunneling junction for nanopore DNA sequencing |

| US9188578B2 (en) | 2013-06-19 | 2015-11-17 | Globalfoundries Inc. | Nanogap device with capped nanowire structures |

| US9182369B2 (en) | 2013-06-19 | 2015-11-10 | Globalfoundries Inc. | Manufacturable sub-3 nanometer palladium gap devices for fixed electrode tunneling recognition |

| JP6290559B2 (ja) | 2013-09-03 | 2018-03-07 | 株式会社日立ハイテクサイエンス | 断面加工観察方法、断面加工観察装置 |

| EP3139929A4 (en) * | 2014-05-09 | 2018-01-03 | Auromedics Pharma LLC | Formulations of cyclophosphamide liquid concentrate |

| EP3043372B1 (en) | 2015-01-12 | 2017-01-04 | Fei Company | Method of modifying a sample surface layer from a microscopic sample |

| US10103008B2 (en) | 2016-01-12 | 2018-10-16 | Fei Company | Charged particle beam-induced etching |

| EP3249676B1 (en) | 2016-05-27 | 2018-10-03 | FEI Company | Dual-beam charged-particle microscope with in situ deposition functionality |

| ES2738911A1 (es) * | 2018-07-25 | 2020-01-27 | Consejo Superior Investigacion | Procedimiento para depositar elementos sobre un sustrato de interes y dispositivo |

| US11298547B2 (en) | 2018-07-27 | 2022-04-12 | Medtronic, Inc. | Fluid status detection from a cardiac electrical signal and impedance signal |

| CN111413727B (zh) * | 2020-04-15 | 2021-12-28 | 中国科学院电工研究所 | 一种电子束发散角测量装置及其制备方法和测量方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60145612A (ja) * | 1984-01-09 | 1985-08-01 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JPH0320026A (ja) * | 1989-01-25 | 1991-01-29 | Rikagaku Kenkyusho | 選択的金属薄膜の形成方法 |

| JP2005303319A (ja) * | 2004-04-13 | 2005-10-27 | Fei Co | 微細構造を改修するためのシステム |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3013955A (en) | 1959-04-29 | 1961-12-19 | Fairchild Camera Instr Co | Method of transistor manufacture |

| US3043955A (en) | 1960-01-25 | 1962-07-10 | Hughes Aircraft Co | Discriminating radiation detector |

| GB1062365A (en) | 1965-03-01 | 1967-03-22 | Hughes Aircraft Co | A method of electroplating an ohmic contact bump upon a semiconductor body |

| US3506545A (en) * | 1967-02-14 | 1970-04-14 | Ibm | Method for plating conductive patterns with high resolution |

| JPS60143630A (ja) * | 1983-12-29 | 1985-07-29 | Fujitsu Ltd | イオン注入方法 |

| JPS63210845A (ja) * | 1987-02-27 | 1988-09-01 | Hitachi Ltd | 欠陥修正方法 |

| US4874460A (en) | 1987-11-16 | 1989-10-17 | Seiko Instruments Inc. | Method and apparatus for modifying patterned film |

| US5976980A (en) | 1994-11-23 | 1999-11-02 | Intel Corporation | Method and apparatus providing a mechanical probe structure in an integrated circuit die |

| US6153891A (en) | 1994-11-23 | 2000-11-28 | Intel Corporation | Method and apparatus providing a circuit edit structure through the back side of an integrated circuit die |

| JP2000232078A (ja) | 1999-02-10 | 2000-08-22 | Toshiba Corp | メッキ方法及びメッキ装置 |

| US6319831B1 (en) | 1999-03-18 | 2001-11-20 | Taiwan Semiconductor Manufacturing Company | Gap filling by two-step plating |

| JP3541931B2 (ja) | 1999-05-17 | 2004-07-14 | 富士ゼロックス株式会社 | 電着膜形成方法、電極形成方法および電着膜形成装置 |

| US6372529B1 (en) | 1999-09-30 | 2002-04-16 | Advanced Micro Devices, Inc. | Forming elongated probe points useful in testing semiconductor devices |

| US6838380B2 (en) | 2001-01-26 | 2005-01-04 | Fei Company | Fabrication of high resistivity structures using focused ion beams |

| US6815358B2 (en) * | 2001-09-06 | 2004-11-09 | Seagate Technology Llc | Electron beam lithography method for plating sub-100 nm trenches |

| KR100465063B1 (ko) | 2002-04-01 | 2005-01-06 | 주식회사 하이닉스반도체 | 반도체 소자의 금속배선 형성방법 |

| US6974768B1 (en) | 2003-01-15 | 2005-12-13 | Novellus Systems, Inc. | Methods of providing an adhesion layer for adhesion of barrier and/or seed layers to dielectric films |

| US6958248B1 (en) * | 2003-02-28 | 2005-10-25 | Credence Systems Corporation | Method and apparatus for the improvement of material/voltage contrast |

| US20060251801A1 (en) | 2005-03-18 | 2006-11-09 | Weidman Timothy W | In-situ silicidation metallization process |

| EP1890136A1 (en) | 2006-08-16 | 2008-02-20 | FEI Company | Method for obtaining images from slices of a specimen |

-

2008

- 2008-09-15 US US12/210,781 patent/US8278220B2/en not_active Expired - Fee Related

-

2009

- 2009-08-06 EP EP09167312A patent/EP2151859A3/en not_active Withdrawn

- 2009-08-06 EP EP09167311A patent/EP2151854A3/en not_active Ceased

- 2009-08-06 JP JP2009182935A patent/JP5656311B2/ja not_active Expired - Fee Related

-

2014

- 2014-05-01 JP JP2014094903A patent/JP2014187371A/ja not_active Withdrawn

- 2014-05-01 JP JP2014094902A patent/JP2014187370A/ja not_active Withdrawn

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60145612A (ja) * | 1984-01-09 | 1985-08-01 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JPH0320026A (ja) * | 1989-01-25 | 1991-01-29 | Rikagaku Kenkyusho | 選択的金属薄膜の形成方法 |

| JP2005303319A (ja) * | 2004-04-13 | 2005-10-27 | Fei Co | 微細構造を改修するためのシステム |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012252004A (ja) * | 2011-06-03 | 2012-12-20 | Fei Co | Tem画像化用の薄い試料を作製する方法 |

| JP2015130471A (ja) * | 2014-01-02 | 2015-07-16 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | チップ電子部品の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2151859A2 (en) | 2010-02-10 |

| EP2151854A2 (en) | 2010-02-10 |

| JP5656311B2 (ja) | 2015-01-21 |

| EP2151859A3 (en) | 2011-08-17 |

| EP2151854A3 (en) | 2011-11-16 |

| JP2014187370A (ja) | 2014-10-02 |

| US8278220B2 (en) | 2012-10-02 |

| JP2014187371A (ja) | 2014-10-02 |

| US20100032302A1 (en) | 2010-02-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5656311B2 (ja) | 基板上にパターン金属を誘導する方法 | |

| TWI493625B (zh) | 修改小結構之系統 | |

| US9812286B2 (en) | Localized, in-vacuum modification of small structures | |

| US11999016B2 (en) | Methods of forming parts using laser machining | |

| JP2002170784A (ja) | 炭化珪素半導体装置及びその製造方法 | |

| US8557707B2 (en) | Focused ion beam deep nano-patterning apparatus and method | |

| JP2005256110A (ja) | 電鋳用型の構造と製造方法およびその電鋳用型を用いた電鋳方法 | |

| US7902062B2 (en) | Electrodepositing a metal in integrated circuit applications | |

| CN100592466C (zh) | 用于修改小结构的系统 | |

| US20020027204A1 (en) | Electron beam exposure apparatus, device for shaping a beam of charged particles and method for manufacturing the device | |

| US11233017B2 (en) | Ex-situ manufacture of metal micro-wires and FIB placement in IC circuits | |

| JP2011179959A (ja) | 電気特性測定用試料の作製方法、測定方法及び試料加工測定装置 | |

| JP2006507675A (ja) | 金属、特に銅を電着する方法、この方法の使用、および集積回路構造 | |

| KR20250105457A (ko) | 깊은 다중층 구조의 개선된 편집 | |

| CN110940689B (zh) | SiC器件样品的制备方法及SiC器件的形貌分析方法 | |

| RU2762129C2 (ru) | Способ обработки несогласованностей в устройствах на основе солнечных элементов и устройства, полученные с его помощью | |

| KR20250030921A (ko) | 2차 전자 산출율이 증가된 이온 빔 검사 및 수리 | |

| Cheng | Metallic nanotransistors. | |

| KR100238237B1 (ko) | 전자빔 셀 투영 리소그래피용 마스크 및 그 제조방법 | |

| Spiegel | Electrochemical Investigation of Ion Implanted P-Si |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120714 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120714 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130930 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131101 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140131 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140205 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140226 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140303 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140331 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140403 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140430 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140527 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140826 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140829 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140925 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141024 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141122 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5656311 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |