JP2010041020A - トランジェントノイズ検出回路 - Google Patents

トランジェントノイズ検出回路 Download PDFInfo

- Publication number

- JP2010041020A JP2010041020A JP2008262741A JP2008262741A JP2010041020A JP 2010041020 A JP2010041020 A JP 2010041020A JP 2008262741 A JP2008262741 A JP 2008262741A JP 2008262741 A JP2008262741 A JP 2008262741A JP 2010041020 A JP2010041020 A JP 2010041020A

- Authority

- JP

- Japan

- Prior art keywords

- unit

- circuit

- transient noise

- rectifier

- detection circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000001514 detection method Methods 0.000 title claims abstract description 80

- 230000001052 transient effect Effects 0.000 title claims abstract description 45

- 239000003990 capacitor Substances 0.000 claims abstract description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 3

- 229910052710 silicon Inorganic materials 0.000 claims description 3

- 239000010703 silicon Substances 0.000 claims description 3

- 230000004044 response Effects 0.000 claims description 2

- 230000003071 parasitic effect Effects 0.000 abstract description 6

- 238000012360 testing method Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 238000000034 method Methods 0.000 description 3

- 238000013461 design Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/0046—Arrangements for measuring currents or voltages or for indicating presence or sign thereof characterised by a specific application or detail not covered by any other subgroup of G01R19/00

- G01R19/0053—Noise discrimination; Analog sampling; Measuring transients

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R19/00—Arrangements for measuring currents or voltages or for indicating presence or sign thereof

- G01R19/04—Measuring peak values or amplitude or envelope of ac or of pulses

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R29/00—Arrangements for measuring or indicating electric quantities not covered by groups G01R19/00 - G01R27/00

- G01R29/26—Measuring noise figure; Measuring signal-to-noise ratio

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/001—Measuring interference from external sources to, or emission from, the device under test, e.g. EMC, EMI, EMP or ESD testing

- G01R31/002—Measuring interference from external sources to, or emission from, the device under test, e.g. EMC, EMI, EMP or ESD testing where the device under test is an electronic circuit

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Measurement Of Current Or Voltage (AREA)

Abstract

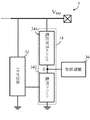

【解決手段】トランジェントノイズ検出回路2はトリガ回路22、整流回路24及び制御装置26を備える。トリガ回路がトランジェントノイズを受信すると、トリガ回路はトリガ信号を発生させる。整流回路は直列に接続される整流ユニット242と電流制御ユニット244を備える。整流ユニットがトリガ回路からトリガ信号を受信すると、整流ユニットはトリガ信号により起動される。制御装置は整流ユニットと電流制御ユニットの間の検出ノードDへ接続される。制御装置は検出ノード電圧に基づき、トランジェントノイズ電圧レベルを決定するために使用される。

【選択図】図3(A)

Description

3:検出回路

12:電源オン/リセット回路

14:内部回路

22、32:トリガ回路

24、34:整流回路

26、36:制御装置

242、342:整流ユニット

244、344:電流制限ユニット

Claims (8)

- トランジェントノイズを受信すると、トリガ信号を発生させる、電源レールとアースノード間に接続されるトリガ回路;

前記トリガ回路から前記トリガ信号を受信すると、前記トリガ信号により起動され、直列に接続される整流ユニットと、電流制限ユニットを備え、前記トリガ回路、前記電源レール、および前記アースノードへ接続される整流回路;

前記検出ノードの電圧に基づき前記トランジェントノイズ電圧レベルを決定する、前記整流ユニットと前記電流制限ユニット間の検出ノードへ接続される制御装置;

を備えるトランジェントノイズ電圧レベルを検出するためのトランジェントノイズ検出回路。 - 前記整流ユニットはシリコン制御整流器(SCR)であることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

- 前記電流制限ユニットはPMOSであり、前記PMOSは前記電源レールと前記整流ユニット間に接続され、そして前記整流ユニットは前記アースノードに接続されることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

- 前記電流制限ユニットはPMOSスタックであり、前記POMSスタックは前記電源レールと前記整流ユニットの間に接続され、そして前記整流ユニットは前記アースノードへ接続されることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

- 前記電流制限ユニットはNMOSであり、前記NMOSは前記アースノードと前記整流ユニット間に接続され、前記整流ユニットは前記電源レールへ接続されることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

- 前記電流制限ユニットはNMOSスタックであり、前記NMOSスタックは前記アースノードと前記整流ユニットの間に接続され、そして前記整流ユニットは前記電源レールへ接続されることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

- 前記トリガ回路は:

前記電源レールと前記アースノードへ接続され、直列に接続される抵抗とキャパシタを備えるRCユニット;及び

前記電源レール、前記アースノード、前記整流ユニット、および前記RCユニットへ接続されるインバータ;を備え、

前記RCユニットが前記トランジェントノイズを受信すると、前記RCユニットはRC遅延信号を発生させ、次に前記インバータは前記RC遅延信号に応じて前記トリガ信号を発生させることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。 - 前記トリガ回路は:

前記電源レールと前記アースノードへ接続され、直列に接続される抵抗とキャパシタを備えるRCユニット;及び

前記電源レール、前記アースノード、前記整流ユニット、および前記RCユニットへ接続されるインバータチェーン;を備え、

前記RCユニットが前記トランジェントノイズを受信すると、前記RCユニットはRC遅延信号を発生させ、次に前記インバータはRC遅延信号に応じて前記トリガ信号を発生させることを特徴とする、請求項1に記載のトランジェントノイズ検出回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/188,000 US20100033164A1 (en) | 2008-08-07 | 2008-08-07 | Transient noise detection circuit |

| US12/188,000 | 2008-08-07 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010041020A true JP2010041020A (ja) | 2010-02-18 |

| JP5096282B2 JP5096282B2 (ja) | 2012-12-12 |

Family

ID=41652308

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008262741A Active JP5096282B2 (ja) | 2008-08-07 | 2008-10-09 | トランジェントノイズ検出回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20100033164A1 (ja) |

| JP (1) | JP5096282B2 (ja) |

| TW (1) | TW201012070A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015537423A (ja) * | 2012-10-04 | 2015-12-24 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | クラスdパワー増幅器に関する静電気放電の保護 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8737028B2 (en) | 2011-12-06 | 2014-05-27 | International Business Machines Corporation | RC-triggered ESD clamp device with feedback for time constant adjustment |

| CN112067926B (zh) * | 2020-09-08 | 2021-07-06 | 西安电子科技大学 | 一种检测mcu芯片抗eft干扰能力的电路及方法 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09297626A (ja) * | 1996-03-07 | 1997-11-18 | Matsushita Electric Ind Co Ltd | 基準電圧源回路及び電圧フィードバック回路 |

| US20020122280A1 (en) * | 2001-03-05 | 2002-09-05 | Taiwan Semiconductor Manufacturing Co., Ltd. | SCR devices with deep-N-well structure for on-chip ESD protection circuits |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100400383B1 (ko) * | 1996-03-07 | 2003-12-31 | 마츠시타 덴끼 산교 가부시키가이샤 | 기준 전압원 회로 및 전압 피드백 회로 |

| EP2395620B1 (en) * | 2001-03-16 | 2015-06-17 | Sofics BVBA | Electrostatic discharge protection structures for high speed technologies with mixed and ultra-low voltage supplies |

| US6573566B2 (en) * | 2001-07-09 | 2003-06-03 | United Microelectronics Corp. | Low-voltage-triggered SOI-SCR device and associated ESD protection circuit |

| US6521952B1 (en) * | 2001-10-22 | 2003-02-18 | United Microelectronics Corp. | Method of forming a silicon controlled rectifier devices in SOI CMOS process for on-chip ESD protection |

| US7102864B2 (en) * | 2004-06-14 | 2006-09-05 | King Billion Electronics Co., Ltd. | Latch-up-free ESD protection circuit using SCR |

-

2008

- 2008-08-07 US US12/188,000 patent/US20100033164A1/en not_active Abandoned

- 2008-09-12 TW TW097135226A patent/TW201012070A/zh unknown

- 2008-10-09 JP JP2008262741A patent/JP5096282B2/ja active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09297626A (ja) * | 1996-03-07 | 1997-11-18 | Matsushita Electric Ind Co Ltd | 基準電圧源回路及び電圧フィードバック回路 |

| US20020122280A1 (en) * | 2001-03-05 | 2002-09-05 | Taiwan Semiconductor Manufacturing Co., Ltd. | SCR devices with deep-N-well structure for on-chip ESD protection circuits |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015537423A (ja) * | 2012-10-04 | 2015-12-24 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | クラスdパワー増幅器に関する静電気放電の保護 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100033164A1 (en) | 2010-02-11 |

| JP5096282B2 (ja) | 2012-12-12 |

| TW201012070A (en) | 2010-03-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8116047B2 (en) | Electrostatic discharge protective circuit having rise time detector and discharge sustaining circuitry | |

| US8830640B2 (en) | Electrostatic discharge protection circuit | |

| US9843183B2 (en) | ESD protection circuit | |

| US8067952B2 (en) | System-level ESD detection circuit | |

| US20150245546A1 (en) | Electrostatic discharge protection circuit | |

| US6819539B1 (en) | Method for circuit recovery from overstress conditions | |

| JP4516102B2 (ja) | Esd保護回路 | |

| US20150249334A1 (en) | Electrostatic discharge circuit with reduced standby current | |

| US10158225B2 (en) | ESD protection system utilizing gate-floating scheme and control circuit thereof | |

| US20140092507A1 (en) | Mitigating cross-domain transmission of electrostatic discharge (esd) events | |

| US8570694B2 (en) | Low voltage electrostatic discharge protection | |

| KR20130121047A (ko) | 게이트 유전체 보호 | |

| EP2919347B1 (en) | Surge-protection circuit and surge-protection method | |

| JP5096282B2 (ja) | トランジェントノイズ検出回路 | |

| TWI495217B (zh) | 靜電放電防護電路與電子裝置 | |

| US20070242400A1 (en) | Device to protect semiconductor device from electrostatic discharge | |

| US20100118457A1 (en) | Electrostatic discharge protection circuit | |

| TWI487087B (zh) | 靜電放電保護裝置 | |

| TWI406385B (zh) | 靜電放電保護裝置 | |

| JP2010183721A (ja) | Ac電源検出回路および直流電源装置 | |

| US20080074813A1 (en) | Discharge protection circuit | |

| US10079487B2 (en) | Clamp circuit for electrical overstress and electrostatic discharge | |

| TWI653797B (zh) | Esd保護積體電路以及esd檢測電路 | |

| CN101394081A (zh) | 低电容的静电放电保护设计 | |

| US20070252615A1 (en) | Logic-keeping apparatus for improving system-level electrostatic discharge robustness |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120327 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120626 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120717 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120821 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120920 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5096282 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150928 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |