JP2010039192A - フォトマスク、及びフォトレジストパターンの形成方法 - Google Patents

フォトマスク、及びフォトレジストパターンの形成方法 Download PDFInfo

- Publication number

- JP2010039192A JP2010039192A JP2008201948A JP2008201948A JP2010039192A JP 2010039192 A JP2010039192 A JP 2010039192A JP 2008201948 A JP2008201948 A JP 2008201948A JP 2008201948 A JP2008201948 A JP 2008201948A JP 2010039192 A JP2010039192 A JP 2010039192A

- Authority

- JP

- Japan

- Prior art keywords

- pattern

- ratio

- photomask

- photoresist

- chips

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 229920002120 photoresistant polymer Polymers 0.000 title claims abstract description 90

- 238000000034 method Methods 0.000 title claims description 59

- 238000012545 processing Methods 0.000 claims description 8

- 238000011161 development Methods 0.000 claims description 7

- 238000012360 testing method Methods 0.000 claims description 3

- 235000012431 wafers Nutrition 0.000 description 22

- 238000011156 evaluation Methods 0.000 description 18

- 238000005530 etching Methods 0.000 description 16

- 238000004519 manufacturing process Methods 0.000 description 10

- 239000004065 semiconductor Substances 0.000 description 10

- 238000010586 diagram Methods 0.000 description 8

- 239000011159 matrix material Substances 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000013523 data management Methods 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000011077 uniformity evaluation Methods 0.000 description 1

Images

Landscapes

- Preparing Plates And Mask In Photomechanical Process (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

Abstract

【解決手段】少ない種類のTEGパターンチップ31(=31a〜31f)を有するフォトマスク30を用いて、そのTEGパターンチップ31の種類よりも多い種類の、且つそれぞれ異なるパターンレシオの単位ブロックBKのフォトレジストパターン40(=40−1〜40−9)をウェハ上に形成するようにしている。即ち、フォトマスク30に形成されたパターンレシオ比の異なる複数のTEGパターンチップ31を組み合わせることで、各ウェハの任意領域に対して様々なパターンレシオ比のフォトレジストパターン40を形成するようにしているので、予めフォトマスク30上に形成する必要チップ数を抑えられる。

【選択図】図1

Description

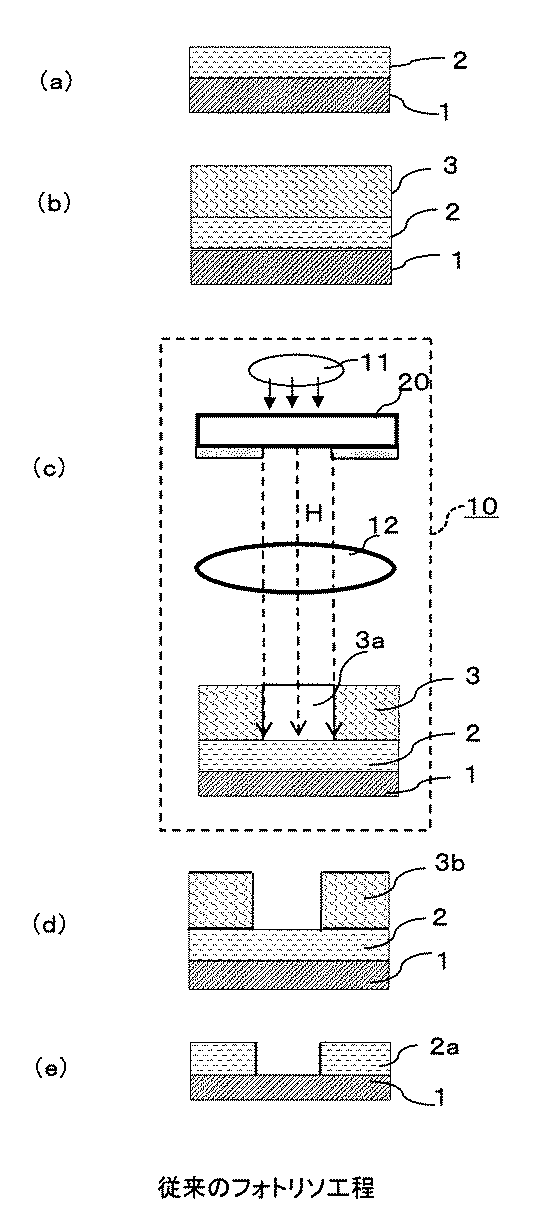

図8及び図9(a)、(b−1)、(b−2)は、従来のパターンレシオ比のテスト・エレメント・グループ(Test Element Group、以下「TEG」という。)パターンの形成方法を示す図である。特に、図8は、従来において異なるパターンレシオ比のTEGパターンを形成したフォトマスクの例を示す平面図である。更に、図9(a)、(b−1)、(b−2)は、従来において図7のフォトマスクによる露光で形成したフォトレジストパターンの例を示す平面図であり、同図(a)はウェハの図、同図(b−1)は図8のTEGパターンチップ22bにより形成したフォトレジストパターンの図、及び、同図(b−2)は図8のTEGパターンチップ22dにより形成したフォトレジストパターンの図である。

図1(a)、(b)は、本発明の実施例1におけるフォトマスク及びフォトレジストパターンの例を示す平面図であり、同図(a)は異なるパターンレシオ比のTEGパターンを形成したフォトマスクを示す図、及び、同図(b)は同図(a)のフォトマスクによる露光で形成したフォトレジストパターンを示す図である。

図2(a)〜(e)は、本発明の実施例1におけるエッチング評価の適用例を示す工程図、図3は、図2の適用例で使用する露光装置を示す概略の構成図である。

フォトリソ工程の露光処理を行うために、図2(a)において、図3の露光装置の移動台60にウェハ50(例えば、50−1)を載置すると共に、図1(a)のフォトマスク30をセットする。ウェハ50−1上には、予め、被エッチング膜51が堆積され、この上にフォトレジスト52が塗布されている。フォトマスク移動機構64によりフォトマスク30を水平方向に移動し、この上の遮光板63によってフォトマスク30中のTEGパターン31(=31b〜31f)を遮蔽してTEGパターン31aのみを光透過可能な状態にする。露光光源62からフォトマスク30中のTEGパターンチップ31aを透過した露光光Hを、投影レンズ65によってフォトレジスト52上に結像し、ウェハ50−1上のフォトレジスト52中に回路パターンの潜像52aを形成する。同様に、移動台60を水平方向へ移動させ、マトリクス状に、フォトレジスト52中に回路パターンの潜像52aを形成する。

本実施例1によれば、次の(a)〜(c)のような効果がある。

(a) 本実施例1によれば、少ない種類のTEGパターンチップ31(=31a〜31f)を有するフォトマスク30を用いて、そのTEGパターンチップ31(=31a〜31f)の種類よりも多い種類の、且つそれぞれ異なるパターンレシオの単位ブロックBKのフォトレジストパターン40(=40−1〜40−9)をウェハ50(=50−1〜50−9)上に形成するようにしている。即ち、フォトマスク30に形成されたパターンレシオ比の異なる複数のTEGパターンチップ31(=31a,31b,31f)を組み合わせることで、各ウェハ50(=50−1〜50−9)の任意領域に対して様々なパターンレシオ比のフォトレジストパターン40(=40−1〜40−9)を形成するようにしているので、予めフォトマスク30上に形成する必要チップ数を抑えられる。そのため、従来技術に比べ、マスクデータ作図工数の軽減、マスクデータ容量の圧縮、及びマスク占有面積縮小が可能となる。

本実施例1では、次の(i)、(ii)のように変形することも可能である。

図4は、本発明の実施例2におけるフォトマスクの例を示す平面図である。

図5(a)のステップ1において、図3の露光装置を用い、TEGパターンチップ34−1,34−2に対するブラインド露光処理により、TEGパターン34a,34bの像をフォトレジスト52中に潜像し、フォトレジスト潜像34a’’,34b’’を形成する(第1の露光処理)。

本実施例2によれば、フォトマスク70上に形成された異なるTEG種のTEGパターンチップ34−1,34−2と、フォトマスク70上に形成された任意のレシオ調整用チップ35−1〜35−3と、を組み合わせてフォトレジスト80のパターンレシオ比を実現しているので、フォトマスク70上に、TEG種毎にパターンレシオ比の異なるチップを作成する必要がなく、予めフォトマスク70上に形成する必要チップ数を抑えられる。そのため、従来技術に比べ、マスクデータ作図工数の軽減、マスクデータ容量の圧縮、及びマスク占有面積縮小が可能となる。

本実施例2では、次の(i)、(ii)のように変形することも可能である。

31,31a〜31f,34−1,34−2 TEGパターンチップ

32,34a,34b TEGパターン

33,35b ダミーパターン

35,35−1〜35−3 レシオ調整用チップ

35a 遮光パターン

40,40−1〜40−9,80 フォトレジストパターン

50,50−1〜50−9 ウェハ

52 フォトレジスト

BK 単位ブロック

Claims (7)

- パターンレシオ比の異なる回路パターンが形成された複数の回路チップと、

パターンレシオ比の異なる複数のレシオ調整用チップと、

を有することを特徴とするフォトマスク。 - 前記回路パターンは、テスト・エレメント・グループパターンであることを特徴とする請求項1記載のフォトマスク。

- 前記レシオ調整用チップには、

前記回路パターンを被覆するための遮光パターンと、

単位面積当たりの個数が異なるレシオ調整用のダミーパターンと、

が形成されていることを特徴とする請求項1又は2記載のフォトマスク。 - 請求項3記載のフォトマスクを用いたフォトレジストパターン形成方法であって、

前記回路チップのレシオを制御するために前記フォトマスク中の前記複数の回路チップと前記複数のレシオ調整用チップとを組み合わせ、

前記回路チップのみを露光する第1の露光処理と、

前記第1の露光処理における露光ショットの位置と等しく、且つ前記第1の露光処理に続けて、前記レシオ調整用チップのみを連続露光する第2の露光処理と、

を行って前記回路パターン及び前記ダミーパターンを有するフォトレジストパターンをウェハ上に形成することを特徴とするフォトレジストパターンの形成方法。 - 前記露光処理では、ブラインド露光を行うことを特徴とする請求項4記載のフォトレジストパターンの形成方法。

- 前記回路パターンは、テスト・エレメント・グループパターンであることを特徴とする請求項4又は5記載のフォトレジストパターンの形成方法。

- パターンレシオ比の異なる複数の回路チップが形成されたフォトマスクを用い、

露光処理及び現像処理により、前記回路チップの種類よりも多い種類の、且つそれぞれ異なるパターンレシオの単位ブロックからなるフォトレジストパターンをウェハ上に形成することを特徴とするフォトレジストパターンの形成方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008201948A JP5138496B2 (ja) | 2008-08-05 | 2008-08-05 | フォトマスク、及びフォトレジストパターンの形成方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008201948A JP5138496B2 (ja) | 2008-08-05 | 2008-08-05 | フォトマスク、及びフォトレジストパターンの形成方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010039192A true JP2010039192A (ja) | 2010-02-18 |

| JP5138496B2 JP5138496B2 (ja) | 2013-02-06 |

Family

ID=42011819

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008201948A Expired - Fee Related JP5138496B2 (ja) | 2008-08-05 | 2008-08-05 | フォトマスク、及びフォトレジストパターンの形成方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5138496B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010278204A (ja) * | 2009-05-28 | 2010-12-09 | Oki Semiconductor Co Ltd | レジストパターンの形成方法 |

| CN102799060A (zh) * | 2011-05-26 | 2012-11-28 | 联华电子股份有限公司 | 虚设图案以及形成虚设图案的方法 |

| US9857677B2 (en) | 2011-05-20 | 2018-01-02 | United Microelectronics Corp. | Dummy patterns |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11102062A (ja) * | 1997-07-31 | 1999-04-13 | Toshiba Corp | マスクデータ作成方法及びその作成装置、マスクデータ補正方法及びマスクデータ補正装置コンピュータ読み取り可能な記録媒体 |

| JP2004347834A (ja) * | 2003-05-22 | 2004-12-09 | Sony Corp | 露光マスクの作製方法 |

| JP2005084379A (ja) * | 2003-09-09 | 2005-03-31 | Renesas Technology Corp | フォトマスクおよび半導体装置の製造方法 |

| JP2005208233A (ja) * | 2004-01-21 | 2005-08-04 | Toshiba Corp | 露光用マスク及びパターン形成方法 |

| JP2005250308A (ja) * | 2004-03-08 | 2005-09-15 | Sony Corp | 露光用マスク群および露光用マスク群の製造方法 |

| JP2007189140A (ja) * | 2006-01-16 | 2007-07-26 | Fujitsu Ltd | 半導体装置の製造方法、マスクの製造方法、露光方法 |

| JP2007287928A (ja) * | 2006-04-17 | 2007-11-01 | Nec Electronics Corp | 半導体集積回路およびその製造方法ならびにマスク |

-

2008

- 2008-08-05 JP JP2008201948A patent/JP5138496B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11102062A (ja) * | 1997-07-31 | 1999-04-13 | Toshiba Corp | マスクデータ作成方法及びその作成装置、マスクデータ補正方法及びマスクデータ補正装置コンピュータ読み取り可能な記録媒体 |

| JP2004347834A (ja) * | 2003-05-22 | 2004-12-09 | Sony Corp | 露光マスクの作製方法 |

| JP2005084379A (ja) * | 2003-09-09 | 2005-03-31 | Renesas Technology Corp | フォトマスクおよび半導体装置の製造方法 |

| JP2005208233A (ja) * | 2004-01-21 | 2005-08-04 | Toshiba Corp | 露光用マスク及びパターン形成方法 |

| JP2005250308A (ja) * | 2004-03-08 | 2005-09-15 | Sony Corp | 露光用マスク群および露光用マスク群の製造方法 |

| JP2007189140A (ja) * | 2006-01-16 | 2007-07-26 | Fujitsu Ltd | 半導体装置の製造方法、マスクの製造方法、露光方法 |

| JP2007287928A (ja) * | 2006-04-17 | 2007-11-01 | Nec Electronics Corp | 半導体集積回路およびその製造方法ならびにマスク |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010278204A (ja) * | 2009-05-28 | 2010-12-09 | Oki Semiconductor Co Ltd | レジストパターンの形成方法 |

| US9857677B2 (en) | 2011-05-20 | 2018-01-02 | United Microelectronics Corp. | Dummy patterns |

| CN102799060A (zh) * | 2011-05-26 | 2012-11-28 | 联华电子股份有限公司 | 虚设图案以及形成虚设图案的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5138496B2 (ja) | 2013-02-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7987436B2 (en) | Sub-resolution assist feature to improve symmetry for contact hole lithography | |

| TWI356285B (en) | Pattern decomposition method for double exposure | |

| JPH0766178B2 (ja) | フォトリソグラフィ・プロセスの最適化方法 | |

| CN109426083B (zh) | 光刻工艺的优化方法及其优化系统和光刻方法 | |

| US9520299B2 (en) | Etch bias control | |

| JP5138496B2 (ja) | フォトマスク、及びフォトレジストパターンの形成方法 | |

| US9136092B2 (en) | Structure and method for E-beam writing | |

| US8736816B2 (en) | Asymmetric complementary dipole illuminator | |

| JP2013197497A (ja) | ドーズ量の補正マップの作成方法、露光方法及び半導体装置の製造方法 | |

| US7050156B2 (en) | Method to increase throughput in a dual substrate stage double exposure lithography system | |

| KR100861169B1 (ko) | 반도체 소자의 형성 방법 | |

| US20060192933A1 (en) | Multiple exposure apparatus and multiple exposure method using the same | |

| US10282487B2 (en) | Mask data generation method | |

| JP5211635B2 (ja) | ダミーチップ露光方法及び半導体集積回路装置の製造方法 | |

| JPH11133585A (ja) | 露光用マスク及びその製造方法 | |

| KR101614410B1 (ko) | 높은 선택비를 갖는 식각방법 및 이를 이용한 패턴 형성방법 | |

| JP2005250308A (ja) | 露光用マスク群および露光用マスク群の製造方法 | |

| JP2005283609A (ja) | 縮小投影露光装置用レチクル | |

| JPS6358825A (ja) | パタ−ン形成方法 | |

| JP2005084379A (ja) | フォトマスクおよび半導体装置の製造方法 | |

| JP5223197B2 (ja) | パターン測定方法及び、フォトマスクの検査方法 | |

| KR100882730B1 (ko) | 마스크 제조 방법 | |

| US8035802B2 (en) | Method and apparatus for lithographic imaging using asymmetric illumination | |

| KR100855264B1 (ko) | 포토 공정 마진 개선방법 | |

| KR100827482B1 (ko) | 반도체 소자 제조용 마스크의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110804 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121005 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121016 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121114 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5138496 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151122 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |