JP2010034135A - 電界効果トランジスタ - Google Patents

電界効果トランジスタ Download PDFInfo

- Publication number

- JP2010034135A JP2010034135A JP2008192183A JP2008192183A JP2010034135A JP 2010034135 A JP2010034135 A JP 2010034135A JP 2008192183 A JP2008192183 A JP 2008192183A JP 2008192183 A JP2008192183 A JP 2008192183A JP 2010034135 A JP2010034135 A JP 2010034135A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- effect transistor

- field effect

- region

- compound semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Junction Field-Effect Transistors (AREA)

- Recrystallisation Techniques (AREA)

Abstract

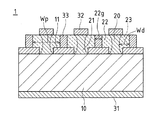

【解決手段】電界効果トランジスタ1は、半導体基板10と、半導体基板10に積層された窒化物系III−V族化合物半導体層20と、窒化物系III−V族化合物半導体層20から積層方向に交差する横方向へ成長した横方向成長領域22と、半導体基板10の裏面に形成されオーミック性を有する第1電極31(ドレイン電極)と、窒化物系III−V族化合物半導体層20の表面に形成されオーミック性を有する第2電極32(ソース電極)と、窒化物系III−V族化合物半導体層20の積層方向で第1電極31と第2電極32との間での電流路となる通電領域21と、横方向成長領域22に接触させて形成され通電領域21での通電状態を制御する第3電極33(ゲート電極)とを備える。

【選択図】図1

Description

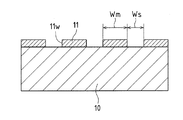

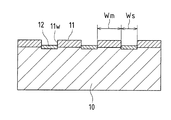

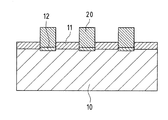

図1に基づいて、本実施の形態に係る電界効果トランジスタについて説明する。

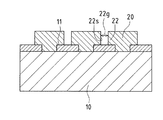

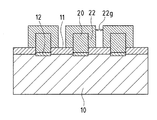

図2Aないし図2Cに基づいて、本実施の形態に係る電界効果トランジスタの製造工程および構造について説明する。なお、基本的な構成は、実施の形態1と同様であるので、符号を援用し、主に異なる事項について説明する。

つまり、Vd=1.1V、Nd=1×1014cm-3とした場合、Wd=3.3μm程度となる。

図3Aないし図3Eに基づいて、本実施の形態に係る電界効果トランジスタの製造工程および構造について説明する。なお、基本的な構成は、実施の形態1、実施の形態2と同様であるので、符号を援用し、主に異なる事項について説明する。

図4Aおよび図4Bに基づいて、本実施の形態に係る電界効果トランジスタの製造工程および構造について説明する。なお、基本的な構成は、実施の形態1ないし実施の形態3と同様であるので、符号を援用し、主に異なる事項について説明する。

図5Aないし図5Dに基づいて、本実施の形態に係る電界効果トランジスタの製造工程および構造について説明する。基本的な構成は、実施の形態1ないし実施の形態4と同様であるので、符号を援用し、主に異なる事項について説明する。なお、実施の形態1ないし実施の形態4では、横方向成長方法として、ELOG成長法を適用したが、本実施の形態では、PENDEO成長法を適用した点が大きく異なる。

図6に基づいて、実施の形態1ないし実施の形態5に係る電界効果トランジスタの作用、効果について実施の形態6として説明する。

10 半導体基板

11 マスク部

11w 開口部

12 バッファ層

13 溝部

13r レジストパターン

20 窒化物系III−V族化合物半導体

20b 窒化物系III−V族化合物半導体

21 通電領域

22 横方向成長領域

22b 界面

22g 間隙

22s 側面

22t 端部

23 空乏層領域

31 第1電極

32 第2電極

33 第3電極

WDD 空乏層間隔

Wd 空乏層厚

Wm 幅(マスク部)

Ws 幅(開口部)

Wp 幅(通電領域)

Claims (13)

- 半導体基板と、該半導体基板に積層された窒化物系III−V族化合物半導体層と、該窒化物系III−V族化合物半導体層から積層方向に交差する横方向へ成長した横方向成長領域とを備える電界効果トランジスタであって、

前記半導体基板の裏面に形成されオーミック性を有する第1電極と、

前記窒化物系III−V族化合物半導体層の表面に形成されオーミック性を有する第2電極と、

前記窒化物系III−V族化合物半導体層の積層方向で前記第1電極と前記第2電極との間での電流路となる通電領域と、

前記横方向成長領域に接触させて形成され前記通電領域での通電状態を制御する第3電極とを備えること

を特徴とする電界効果トランジスタ。 - 請求項1に記載の電界効果トランジスタであって、

前記横方向成長領域は、前記半導体基板に形成され積層方向での前記窒化物系III−V族化合物半導体層の成長を防止するマスク部に重ねて形成されていること

を特徴とする電界効果トランジスタ。 - 請求項2に記載の電界効果トランジスタであって、

前記第3電極は、前記横方向成長領域の横方向の側面に形成されていること

を特徴とする電界効果トランジスタ。 - 請求項3に記載の電界効果トランジスタであって、

前記第3電極は、前記側面が構成する間隙に埋め込まれていること

を特徴とする電界効果トランジスタ。 - 請求項3または請求項4に記載の電界効果トランジスタであって、

前記マスク部は、導電性材料で形成され、前記第3電極は、前記マスク部に接触していること

を特徴とする電界効果トランジスタ。 - 請求項2に記載の電界効果トランジスタであって、

前記横方向成長領域は、相互に当接するように形成され、

前記第3電極は、相互に当接する前記横方向成長領域の界面に接触していること

を特徴とする電界効果トランジスタ。 - 請求項1に記載の電界効果トランジスタであって、

前記横方向成長領域は、前記半導体基板に形成された溝部の領域で梁状に形成されていること

を特徴とする電界効果トランジスタ。 - 請求項7に記載の電界効果トランジスタであって、

前記横方向成長領域は、相互に当接するように形成され、

前記第3電極は、相互に当接する前記横方向成長領域の界面に接触していること

を特徴とする電界効果トランジスタ。 - 請求項1ないし請求項8のいずれか一つに記載の電界効果トランジスタであって、

前記横方向成長領域は、マグネシウムがドーピングされていること

を特徴とする電界効果トランジスタ。 - 請求項9に記載の電界効果トランジスタであって、

前記第3電極は、オーミック性を有すること

を特徴とする電界効果トランジスタ。 - 請求項1ないし請求項8のいずれか一つに記載の電界効果トランジスタであって、

前記第3電極は、前記横方向成長領域に対してショットキー電極としてあること

を特徴とする電界効果トランジスタ。 - 請求項1ないし請求項11のいずれか一つに記載の電界効果トランジスタであって、

前記横方向成長領域は、ストライプ状に配置され、前記第3電極は、前記横方向成長領域に対応させてストライプ状に配置されていること

を特徴とする電界効果トランジスタ。 - 請求項1ないし請求項12のいずれか一つに記載の電界効果トランジスタであって、

前記半導体基板は、Si、SiC、または、窒化物系III−V族化合物半導体のいずれか一つを材料としていること

を特徴とする電界効果トランジスタ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192183A JP5323412B2 (ja) | 2008-07-25 | 2008-07-25 | 電界効果トランジスタ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192183A JP5323412B2 (ja) | 2008-07-25 | 2008-07-25 | 電界効果トランジスタ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010034135A true JP2010034135A (ja) | 2010-02-12 |

| JP5323412B2 JP5323412B2 (ja) | 2013-10-23 |

Family

ID=41738299

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008192183A Expired - Fee Related JP5323412B2 (ja) | 2008-07-25 | 2008-07-25 | 電界効果トランジスタ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5323412B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018181200A1 (ja) * | 2017-03-31 | 2018-10-04 | パナソニックIpマネジメント株式会社 | 半導体装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000232239A (ja) * | 1998-12-08 | 2000-08-22 | Nichia Chem Ind Ltd | 窒化物半導体の成長方法及び窒化物半導体素子 |

| JP2002134735A (ja) * | 2000-10-25 | 2002-05-10 | Toshiba Corp | 半導体装置 |

| WO2006093309A1 (en) * | 2005-03-03 | 2006-09-08 | Fuji Electric Holdings Co., Ltd. | Semiconductor device and the method of manufacturing the same |

| JP2006269825A (ja) * | 2005-03-24 | 2006-10-05 | Ngk Insulators Ltd | 半導体装置およびその製造方法 |

| JP2007335484A (ja) * | 2006-06-13 | 2007-12-27 | Mitsubishi Cable Ind Ltd | 窒化物半導体ウェハ |

| JP2008118082A (ja) * | 2006-10-11 | 2008-05-22 | New Japan Radio Co Ltd | 窒化物半導体装置及びその製造方法 |

-

2008

- 2008-07-25 JP JP2008192183A patent/JP5323412B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000232239A (ja) * | 1998-12-08 | 2000-08-22 | Nichia Chem Ind Ltd | 窒化物半導体の成長方法及び窒化物半導体素子 |

| JP2002134735A (ja) * | 2000-10-25 | 2002-05-10 | Toshiba Corp | 半導体装置 |

| WO2006093309A1 (en) * | 2005-03-03 | 2006-09-08 | Fuji Electric Holdings Co., Ltd. | Semiconductor device and the method of manufacturing the same |

| JP2006269825A (ja) * | 2005-03-24 | 2006-10-05 | Ngk Insulators Ltd | 半導体装置およびその製造方法 |

| JP2007335484A (ja) * | 2006-06-13 | 2007-12-27 | Mitsubishi Cable Ind Ltd | 窒化物半導体ウェハ |

| JP2008118082A (ja) * | 2006-10-11 | 2008-05-22 | New Japan Radio Co Ltd | 窒化物半導体装置及びその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018181200A1 (ja) * | 2017-03-31 | 2018-10-04 | パナソニックIpマネジメント株式会社 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5323412B2 (ja) | 2013-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9685549B2 (en) | Nitride semiconductor device and method for manufacturing same | |

| US8207574B2 (en) | Semiconductor device and method for manufacturing the same | |

| US10020361B2 (en) | Circuit structure having islands between source and drain and circuit formed | |

| JP4786730B2 (ja) | 電界効果型トランジスタおよびその製造方法 | |

| JP2008311355A (ja) | 窒化物半導体素子 | |

| JPWO2003071607A1 (ja) | GaN系電界効果トランジスタ | |

| KR20210131793A (ko) | 고 전자 이동도 트랜지스터 및 그 제조방법 | |

| JP4474292B2 (ja) | 半導体装置 | |

| JP2011155221A (ja) | 半導体装置およびその製造方法 | |

| TW201737395A (zh) | 半導體裝置及半導體裝置的製造方法 | |

| CN114080691B (zh) | 氮化物基半导体装置及其制造方法 | |

| JP6064483B2 (ja) | 化合物半導体装置及びその製造方法 | |

| CN114402442B (zh) | 氮化物基半导体装置及其制造方法 | |

| JP5379391B2 (ja) | 窒化ガリウム系化合物半導体からなる半導体素子及びその製造方法 | |

| JP2007208037A (ja) | 半導体素子 | |

| JP6530210B2 (ja) | 半導体装置及びその製造方法 | |

| JP5323412B2 (ja) | 電界効果トランジスタ | |

| US11876120B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| US20220375874A1 (en) | Iii nitride semiconductor devices on patterned substrates | |

| US20210305418A1 (en) | High electron mobility transistor and method of manufacturing the same | |

| JP5183857B2 (ja) | 電界効果トランジスタおよび製造方法 | |

| WO2023181749A1 (ja) | 半導体装置 | |

| WO2019003363A1 (ja) | 半導体装置及びその製造方法 | |

| JP7100241B2 (ja) | 化合物半導体装置及びその製造方法 | |

| CN117594633A (zh) | 一种半导体器件以及制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100826 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130305 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130424 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20130424 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130514 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130530 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130625 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130717 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5323412 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |