JP2010026118A - 表示装置およびその駆動方法ならびに電子機器 - Google Patents

表示装置およびその駆動方法ならびに電子機器 Download PDFInfo

- Publication number

- JP2010026118A JP2010026118A JP2008185500A JP2008185500A JP2010026118A JP 2010026118 A JP2010026118 A JP 2010026118A JP 2008185500 A JP2008185500 A JP 2008185500A JP 2008185500 A JP2008185500 A JP 2008185500A JP 2010026118 A JP2010026118 A JP 2010026118A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- wiring

- transistor

- driving unit

- driver

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/001—Arbitration of resources in a display system, e.g. control of access to frame buffer by video controller and/or main processor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3266—Details of drivers for scan electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

- G09G2300/0866—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes by means of changes in the pixel supply voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

- G09G2320/045—Compensation of drifts in the characteristics of light emitting or modulating elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Multimedia (AREA)

- Control Of El Displays (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Led Devices (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

【解決手段】Vth補正準備期間(T1〜T4)において、信号線DTLの電圧がVofs1となっているときにトランジスタTWSをオン・オフし、ゲート電圧Vgおよびソース電圧Vsを上昇させる。その後、Vth補正を開始する前に、信号線DTLの電圧がVofs2となっているときにトランジスタTWSをオンし、ゲート電圧Vgをおよびソース電圧Vsを元の電圧にまで下げる。これにより、Vth補正準備期間のうち所定の間(ゲート電圧VgがVofs1となっている間)、ソース電圧VsをViniよりも高い電圧にすることができる。

【選択図】図3

Description

まず、Vth補正の準備を行う。具体的には、電源走査回路150がドレイン線DSLの電圧をVccからViniに下げる(T1)。すると、ソース電圧VsがViniまで下がり、有機EL素子121等が消光する。このとき、保持容量Csを介したカップリングによりゲート電圧Vgも下がる。次に、信号線DTLの電圧がVofsとなっている間に、書き込み走査回路140がゲート線WSLの電圧をVoffからVonに上げる(T2)。すると、ゲート電圧VgがVofsまで下がる。

次に、Vthの補正を行う。具体的には、信号線DTLの電圧がVofsとなっている間に、電源走査回路150がドレイン線DSLの電圧をViniからVccに上げる(T3)。すると、トランジスタTDrのドレイン−ソース間に電流Idsが流れ、ソース電圧Vsが上昇する。その後、水平駆動回路130が信号線DTLの電圧をVofsからVsigに切り替える前に、書き込み走査回路140がゲート線WSLの電圧をVonからVoffに下げる(T4)。すると、トランジスタTDrのゲートがフローティングとなり、Vthの補正が一旦停止する。

Vth補正が休止している期間中は、先のVth補正を行った行(画素)とは異なる他の行(画素)において、信号線DTLの電圧のサンプリングが行われる。なお、Vth補正が不十分である場合、すなわち、トランジスタTDrのゲート−ソース間の電位差VgsがトランジスタTDrの閾値電圧Vthよりも大きい場合には、Vth補正休止期間中にも、先のVth補正を行った行(画素)において、トランジスタTDrのドレイン−ソース間に電流Idsが流れ、ソース電圧Vsが上昇し、保持容量Csを介したカップリングによりゲート電圧Vgも上昇する。

Vth補正休止期間が終了した後、Vthの補正を再び行う。具体的には、信号線DTLの電圧がVofsとなっており、Vth補正が可能となっている時に、書き込み走査回路140がゲート線WSLの電圧をVoffからVonに上げ(T5)、トランジスタTDrのゲートを信号線DTLに接続する。このとき、ソース電圧VsがVofs−Vthよりも低い場合(Vth補正がまだ完了していない場合)には、トランジスタTDrがカットオフするまで(電位差VgsがVthになるまで)、トランジスタTDrのドレイン−ソース間に電流Idsが流れる。その結果、保持容量CsがVthに充電され、電位差VgsがVthとなる。その後、水平駆動回路130が信号線DTLの電圧をVofsからVsigに切り替える前に、書き込み走査回路140がゲート線WSLの電圧をVonからVoffに下げる(T6)。すると、トランジスタTDrのゲートがフローティングとなるので、電位差Vgsを信号線DTLの電圧の大きさに拘わらずVthのままで維持することができる。このように、電位差VgsをVthに設定することにより、トランジスタTDrの閾値電圧Vthが画素回路122ごとにばらついた場合であっても、有機EL素子121等の発光輝度がばらつくのをなくすることができる。

その後、Vth補正の休止期間中に、水平駆動回路130が信号線DTLの電圧をVofsからVsigに切り替える。

Vth補正休止期間が終了した後、書き込みとμ補正を行う。具体的には、信号線DTLの電圧がVsigとなっている間に、書き込み走査回路140がゲート線WSLの電圧をVoffからVonに上げ(T7)、トランジスタTDrのゲートを信号線DTLに接続する。すると、トランジスタTDrのゲートの電圧がVsigとなる。このとき、有機EL素子121R等のアノードの電圧はこの段階ではまだ有機EL素子121R等の閾値電圧Velよりも小さく、有機EL素子121R等はカットオフしている。そのため、電流Idsは有機EL素子121R等の素子容量(図示せず)に流れ、素子容量が充電されるので、ソース電圧VsがΔVだけ上昇し、やがて電位差VgsがVsig+Vth−ΔVとなる。このようにして、書き込みと同時にμ補正が行われる。ここで、トランジスタTDrの移動度μが大きい程、ΔVも大きくなるので、電位差Vgsを発光前にΔVだけ小さくすることにより、画素ごとの移動度μのばらつきを取り除くことができる。

最後に、書き込み走査回路140がゲート線WSLの電圧をVonからVoffに下げる(T8)。すると、トランジスタTDrのゲートがフローティングとなり、トランジスタTDrのドレイン−ソース間に電流Idsが流れ、ソース電圧Vsが上昇する。その結果、有機EL素子121R等が所望の輝度で発光する。

(B)第2配線の電圧が第3電圧となっており、かつ第3配線の電圧が第5電圧となっている時に、第1駆動部が第1配線の電圧を第1電圧から第2電圧に上げたのち、第2電圧から第1電圧に下げ、その後、第2配線の電圧が第3電圧となっており、かつ第3配線の電圧が第6電圧となっている時に、第1駆動部が第1配線の電圧を第1電圧から第2電圧に上げるVth補正準備ステップ

(C)第2配線の電圧が第4電圧となっており、かつ第3配線の電圧が第5電圧、第6電圧および第7電圧のいずれかの電圧値に規則的に変化している時に、第1駆動部が、第1配線の電圧を第1電圧および第3電圧のいずれかの電圧値に規則的に変化させるVth補正・発光ステップ

まず、Vth補正の準備を行う。具体的には、ゲート線WSLの電圧がVoffとなっており、信号線DTLの電圧がVofs1となっており、ドレイン線DSLの電圧がVccとなっている時(つまり有機EL素子12R等が発光している時)に、電源走査回路24が制御信号21cに応じてドレイン線DSLの電圧をVccからViniに下げる(T1)。すると、ソース電圧VsがViniよりも高い所定の電圧まで下がり、有機EL素子12R等が消光する。このとき、保持容量Csを介したカップリングによりゲート電圧Vgも、Vofs2よりも少し高い電圧まで下がる。次に、ドレイン線DSLの電圧がViniとなっており、かつ信号線DTLの電圧がVofs1となっている間に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVoffからVonに上げる(T2)。すると、ゲート電圧VgがVofs1まで上昇し、ソース電圧VsはViniよりも高い所定の電圧を維持する。その後、ドレイン線DSLの電圧がViniとなっており、かつ信号線DTLの電圧がVofs2となっている時に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVoffからVonに上げる(T3)。すると、ゲート電圧VgがVofs2まで下がり、それに伴ってソース電圧VsもViniまで下がる。

ΔV2=(Vofs1−Vofs2)×(1−Cs/(Cs+Cel))

次に、Vthの補正を行う。具体的には、信号線DTLの電圧がVofs2となっている間に、電源走査回路24が制御信号21cに応じてドレイン線DSLの電圧をViniからVccに上げる(T4)。すると、トランジスタTDrのドレイン−ソース間に電流Idsが流れ、ソース電圧Vsが上昇する。その後、水平駆動回路22が制御信号21dに応じて信号線DTLの電圧をVofs2からVsigに切り替える前に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVonからVoffに下げる(T5)。すると、トランジスタTDrのゲートがフローティングとなり、Vthの補正が一旦停止する。

Vth補正が休止している期間中(すなわち、ゲート線WSLの電圧がVoffとなっており、かつドレイン線DSLの電圧がVccとなっている間)は、先のVth補正を行った行(画素)とは異なる他の行(画素)において、信号線DTLの電圧のサンプリングが行われる。具体的には、水平駆動回路22が、Vth補正が休止している期間中に、信号線DTLの電圧をVofsからVsigに切り替えたのち、VsigからVofs1、Vofs2に段階的に切り替える動作を行い、書き込み走査回路23が、信号線DTLの電圧がVsig、Vofs1またはVofs2となっている間に、先のVth補正を行った行(画素)とは異なる他の行(画素)に接続されたゲート線WSLの電圧をVoffからVonに上げたのち、VonからVoffに切り替える。

Vth補正休止期間が終了した後、Vthの補正を再び行う。具体的には、ドレイン線DSLの電圧がVccとなっており、かつ信号線DTLの電圧がVofs2となっており、Vth補正が可能となっている時に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVoffからVonに上げ(T6)、トランジスタTDrのゲートを信号線DTLに接続する。このとき、ソース電圧VsがVofs−Vthよりも低い場合(Vth補正がまだ完了していない場合)には、トランジスタTDrがカットオフするまで(電位差VgsがVthになるまで)、トランジスタTDrのドレイン−ソース間に電流Idsが流れる。これにより、ゲート電圧VgがVofs2となり、ソース電圧Vsが上昇し、その結果、保持容量CsがVthに充電され、電位差VgsがVthとなる。その後、水平駆動回路22が信号線DTLの電圧をVofs2からVsigに切り替える前に、書き込み走査回路23がゲート線WSLの電圧をVonからVoffに下げる(T7)。すると、トランジスタTDrのゲートがフローティングとなるので、電位差Vgsを信号線DTLの電圧の大きさに拘わらずVthのままで維持することができる。このように、電位差VgsをVthに設定することにより、トランジスタTDrの閾値電圧Vthが画素回路13ごとにばらついた場合であっても、有機EL素子12R等の発光輝度がばらつくのをなくすることができる。

その後、Vth補正の休止期間中(すなわち、ゲート線WSLの電圧がVoffとなっており、かつドレイン線DSLの電圧がVccとなっている間)に、水平駆動回路22が制御信号21dに応じて信号線DTLの電圧をVofs2からVsigに切り替える。

2回目のVth補正休止期間が終了した後、書き込みとμ補正を行う。具体的には、信号線DTLの電圧がVsigとなっている間に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVoffからVonに上げ(T8)、トランジスタTDrのゲートを信号線DTLに接続する。すると、トランジスタTDrのゲートの電圧が信号線DTLの電圧Vsigとなる。このとき、有機EL素子12R等のアノードの電圧はこの段階ではまだ有機EL素子12R等の閾値電圧Velよりも小さく、有機EL素子12R等はカットオフしている。そのため、電流Idsは有機EL素子12R等の素子容量(図示せず)に流れ、素子容量が充電されるので、ソース電圧VsがΔV3だけ上昇し、やがて電位差VgsがVsig+Vth−ΔV3となる。このようにして、書き込みと同時にμ補正が行われる。ここで、トランジスタTDrの移動度μが大きい程、ΔV3も大きくなるので、電位差Vgsを発光前にΔV3だけ小さくすることにより、画素ごとの移動度μのばらつきを取り除くことができる。

最後に、書き込み走査回路23が制御信号21bに応じてゲート線WSLの電圧をVonからVoffに下げる(T9)。すると、トランジスタTDrのゲートがフローティングとなり、トランジスタTDrのドレイン−ソース間に電流Idsが流れ、ソース電圧Vsが上昇する。その結果、有機EL素子12R等に閾値電圧Vel以上の電圧が印加され、有機EL素子12R等が所望の輝度で発光する。

以下、上記実施の形態で説明した表示装置1の適用例について説明する。上記実施の形態の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

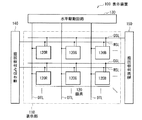

上記実施の形態の表示装置1は、例えば、図4に示したようなモジュールとして、後述する適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板2の一辺に、表示部10を封止する部材(図示せず)から露出した領域210を設け、この露出した領域210に、タイミング制御回路21、水平駆動回路22、書き込み走査回路23および電源走査回路24の配線を延長して外部接続端子(図示せず)を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

図5は、上記実施の形態の表示装置1が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300は、上記実施の形態に係る表示装置1により構成されている。

図6は、上記実施の形態の表示装置1が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、その表示部420は、上記実施の形態に係る表示装置1により構成されている。

図7は、上記実施の形態の表示装置1が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、その表示部530は、上記実施の形態に係る表示装置1により構成されている。

図8は、上記実施の形態の表示装置1が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有しており、その表示部640は、上記実施の形態に係る表示装置1により構成されている。

図9は、上記実施の形態の表示装置1が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そのディスプレイ740またはサブディスプレイ750は、上記実施の形態に係る表示装置1により構成されている。

Claims (4)

- 発光素子および画素回路を画素ごとに有する表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1トランジスタと、第2トランジスタと、保持容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、制御部と、第1配線と、第2配線と、第3配線と、参照電圧に設定される第4配線とを有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部に接続され、

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前記保持容量の他端および前記発光素子のアノードに接続され、

前記発光素子のカソードが前記第4配線に接続され、

前記第1駆動部は、前記第1トランジスタのオン電圧よりも低い第1電圧と、前記第1トランジスタのオン電圧以上の第2電圧とを前記第1配線に出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記参照電圧との和よりも低い第3電圧と、前記発光素子の閾値電圧と前記参照電圧との和以上の第4電圧とを前記第2配線に出力可能であり、

前記第3駆動部は、第5電圧および第6電圧(第5電圧>第6電圧)と、前記映像信号に応じた大きさの第7電圧とを前記第3配線に出力可能であり、

前記制御部は、前記第1駆動部、前記第2駆動部および前記第3駆動部に対して以下の(A)〜(C)の各ステップを順次実行することを指示する制御信号を出力する表示装置。

(A)前記第3配線の電圧が前記第5電圧となっている時に、前記第2駆動部が前記第2配線の電圧を前記第5電圧から前記第3電圧に下げる消光ステップ

(B)前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第5電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げたのち、前記第2電圧から前記第1電圧に下げ、その後、前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第6電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げるVth補正準備ステップ

(C)前記第2配線の電圧が前記第4電圧となっており、かつ前記第3配線の電圧が前記第5電圧、前記第6電圧および前記第7電圧のいずれかの電圧値に規則的に変化している時に、前記第1駆動部が、前記第1配線の電圧を前記第1電圧および前記第3電圧のいずれかの電圧値に規則的に変化させるVth補正・発光ステップ - 前記制御部は、前記第1駆動部、前記第2駆動部および前記第3駆動部に対して、以下の(D)〜(H)の各ステップを前記Vth補正・発光ステップにおいて順次実行することを指示する制御信号を出力する請求項1に記載の表示装置。

(D)前記第3配線の電圧が前記第6電圧となっている時に、前記第2駆動部が前記第2配線の電圧を前記第3電圧から前記第4電圧に上げたのち、前記第1駆動部が前記第1配線の電圧を前記第2電圧から前記第1電圧に下げる最初のVth補正ステップ

(E)所定の期間、前記第1駆動部が前記第1配線の電圧を前記第1電圧にし続けると共に、前記第2駆動部が前記第2配線の電圧を前記第4電圧にし続ける最初のVth補正休止ステップ

(F)前記第2配線の電圧が前記第4電圧となっており、かつ前記第3配線の電圧が前記第6電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げたのち、前記第2電圧から前記第1電圧に下げる2回目のVth補正ステップ

(G)所定の期間、前記第1駆動部が前記第1配線の電圧を前記第1電圧にし続けると共に、前記第2駆動部が前記第2配線の電圧を前記第4電圧にし続ける2回目のVth補正休止ステップ

(H)前記第2配線の電圧が前記第4電圧となっており、かつ前記第3配線の電圧が前記第7電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げたのち、前記第2電圧から前記第1電圧に下げる書き込み・μ補正・発光ステップ - 発光素子および画素回路を画素ごとに有する表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1トランジスタと、第2トランジスタと、保持容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、第1配線と、第2配線と、第3配線と、参照電圧に設定される第4配線とを有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部に接続され、

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前記保持容量の他端および前記発光素子のアノードに接続され、

前記発光素子のカソードが前記第4配線に接続され、

前記第1駆動部は、前記第1トランジスタのオン電圧よりも低い第1電圧と、前記第1トランジスタのオン電圧以上の第2電圧とを前記第1配線に出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記参照電圧との和よりも低い第3電圧と、前記発光素子の閾値電圧と前記参照電圧との和以上の第4電圧とを前記第2配線に出力可能であり、

前記第3駆動部は、第5電圧および第6電圧(第5電圧>第6電圧)と、前記映像信号に応じた大きさの第7電圧とを前記第3配線に出力可能である表示装置の前記第1駆動部、前記第2駆動部および前記第3駆動部が以下の(A)〜(C)の各ステップを順次実行する表示装置の駆動方法。

(A)前記第3配線の電圧が前記第5電圧となっている時に、前記第2駆動部が前記第2配線の電圧を前記第5電圧から前記第3電圧に下げる消光ステップ

(B)前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第5電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げたのち、前記第2電圧から前記第1電圧に下げ、その後、前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第6電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げるVth補正準備ステップ

(C)前記第2配線の電圧が前記第4電圧となっており、かつ前記第3配線の電圧が前記第5電圧、前記第6電圧および前記第7電圧のいずれかの電圧値に規則的に変化している時に、前記第1駆動部が、前記第1配線の電圧を前記第1電圧および前記第3電圧のいずれかの電圧値に規則的に変化させるVth補正・発光ステップ - 表示装置を備え、

前記表示装置は、

発光素子および画素回路を画素ごとに有する表示部と、

前記映像信号に基づいて前記画素回路を駆動する駆動部と

を有し、

前記画素回路は、第1トランジスタと、第2トランジスタと、保持容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、制御部と、第1配線と、第2配線と、第3配線と、参照電圧に設定される第4配線とを有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部に接続され、

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前記保持容量の他端および前記発光素子のアノードに接続され、

前記発光素子のカソードが前記第4配線に接続され、

前記第1駆動部は、前記第1トランジスタのオン電圧よりも低い第1電圧と、前記第1トランジスタのオン電圧以上の第2電圧とを前記第1配線に出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記参照電圧との和よりも低い第3電圧と、前記発光素子の閾値電圧と前記参照電圧との和以上の第4電圧とを前記第2配線に出力可能であり、

前記第3駆動部は、第5電圧および第6電圧(第5電圧>第6電圧)と、前記映像信号に応じた大きさの第7電圧とを前記第3配線に出力可能であり、

前記制御部は、前記第1駆動部、前記第2駆動部および前記第3駆動部に対して以下の(A)〜(C)の各ステップを順次実行することを指示する制御信号を出力する電子機器。

(A)前記第3配線の電圧が前記第5電圧となっている時に、前記第2駆動部が前記第2配線の電圧を前記第5電圧から前記第3電圧に下げる消光ステップ

(B)前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第5電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げたのち、前記第2電圧から前記第1電圧に下げ、その後、前記第2配線の電圧が前記第3電圧となっており、かつ前記第3配線の電圧が前記第6電圧となっている時に、前記第1駆動部が前記第1配線の電圧を前記第1電圧から前記第2電圧に上げるVth補正準備ステップ

(C)前記第2配線の電圧が前記第4電圧となっており、かつ前記第3配線の電圧が前記第5電圧、前記第6電圧および前記第7電圧のいずれかの電圧値に規則的に変化している時に、前記第1駆動部が、前記第1配線の電圧を前記第1電圧および前記第3電圧のいずれかの電圧値に規則的に変化させるVth補正・発光ステップ

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185500A JP4666016B2 (ja) | 2008-07-17 | 2008-07-17 | 表示装置およびその駆動方法ならびに電子機器 |

| US12/498,498 US8405586B2 (en) | 2008-07-17 | 2009-07-07 | Display device, method for driving the same, and electronic device |

| CN2009101600401A CN101630477B (zh) | 2008-07-17 | 2009-07-16 | 显示装置、显示装置的驱动方法、以及电子设备 |

| US13/847,923 US8723767B2 (en) | 2008-07-17 | 2013-03-20 | Display device, method for driving the same, and electronic device |

| US14/177,859 US9483995B2 (en) | 2008-07-17 | 2014-02-11 | Display device, method for driving the same, and electronic device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185500A JP4666016B2 (ja) | 2008-07-17 | 2008-07-17 | 表示装置およびその駆動方法ならびに電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010026118A true JP2010026118A (ja) | 2010-02-04 |

| JP4666016B2 JP4666016B2 (ja) | 2011-04-06 |

Family

ID=41529929

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008185500A Expired - Fee Related JP4666016B2 (ja) | 2008-07-17 | 2008-07-17 | 表示装置およびその駆動方法ならびに電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US8405586B2 (ja) |

| JP (1) | JP4666016B2 (ja) |

| CN (1) | CN101630477B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011098881A1 (en) | 2010-02-09 | 2011-08-18 | Nissan Motor Co., Ltd. | Vehicle notification sound emitting apparatus |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4666016B2 (ja) * | 2008-07-17 | 2011-04-06 | ソニー株式会社 | 表示装置およびその駆動方法ならびに電子機器 |

| JP6201465B2 (ja) | 2013-07-08 | 2017-09-27 | ソニー株式会社 | 表示装置、表示装置の駆動方法、及び、電子機器 |

| CN114927101B (zh) * | 2022-05-26 | 2023-05-09 | 武汉天马微电子有限公司 | 一种显示装置及其驱动方法 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009271320A (ja) * | 2008-05-08 | 2009-11-19 | Sony Corp | El表示パネル、電子機器及びel表示パネルの駆動方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3959454B2 (ja) * | 2001-10-22 | 2007-08-15 | シャープ株式会社 | 入力装置および入出力装置 |

| JP2003186437A (ja) * | 2001-12-18 | 2003-07-04 | Sanyo Electric Co Ltd | 表示装置 |

| US7612749B2 (en) * | 2003-03-04 | 2009-11-03 | Chi Mei Optoelectronics Corporation | Driving circuits for displays |

| EP1662474A4 (en) * | 2004-07-16 | 2011-06-15 | Sony Corp | DEVICE AND METHOD FOR IMAGE DISPLAY |

| KR101166824B1 (ko) * | 2004-09-30 | 2012-07-19 | 엘지디스플레이 주식회사 | 유기 전계발광표시장치 및 이의 구동방법 |

| KR100604066B1 (ko) * | 2004-12-24 | 2006-07-24 | 삼성에스디아이 주식회사 | 화소 및 이를 이용한 발광 표시장치 |

| JP4915195B2 (ja) | 2006-09-27 | 2012-04-11 | ソニー株式会社 | 表示装置 |

| JP4840047B2 (ja) * | 2006-09-27 | 2011-12-21 | セイコーエプソン株式会社 | 画像表示装置及びプロジェクタ |

| JP4666016B2 (ja) * | 2008-07-17 | 2011-04-06 | ソニー株式会社 | 表示装置およびその駆動方法ならびに電子機器 |

-

2008

- 2008-07-17 JP JP2008185500A patent/JP4666016B2/ja not_active Expired - Fee Related

-

2009

- 2009-07-07 US US12/498,498 patent/US8405586B2/en active Active

- 2009-07-16 CN CN2009101600401A patent/CN101630477B/zh active Active

-

2013

- 2013-03-20 US US13/847,923 patent/US8723767B2/en active Active

-

2014

- 2014-02-11 US US14/177,859 patent/US9483995B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009271320A (ja) * | 2008-05-08 | 2009-11-19 | Sony Corp | El表示パネル、電子機器及びel表示パネルの駆動方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011098881A1 (en) | 2010-02-09 | 2011-08-18 | Nissan Motor Co., Ltd. | Vehicle notification sound emitting apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| US9483995B2 (en) | 2016-11-01 |

| US20130215099A1 (en) | 2013-08-22 |

| US20140168286A1 (en) | 2014-06-19 |

| JP4666016B2 (ja) | 2011-04-06 |

| US20100013821A1 (en) | 2010-01-21 |

| US8405586B2 (en) | 2013-03-26 |

| US8723767B2 (en) | 2014-05-13 |

| CN101630477A (zh) | 2010-01-20 |

| CN101630477B (zh) | 2011-11-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5804732B2 (ja) | 駆動方法、表示装置および電子機器 | |

| TWI473060B (zh) | 像素電路,顯示器件,電子裝置,以及驅動像素電路之方法 | |

| US8300038B2 (en) | Display apparatus, display-apparatus driving method and electronic instrument | |

| US20100309174A1 (en) | Display device, driving method of display device, and electronic device performing duty control of a pixel | |

| JP2009168969A (ja) | 表示装置及びその駆動方法と電子機器 | |

| US8345032B2 (en) | Display apparatus, display-apparatus driving method and eletronic instrument | |

| US9041631B2 (en) | Display device, method for driving the same, and electronic device | |

| US8902213B2 (en) | Display device, electronic device, and method of driving display device | |

| US20100149152A1 (en) | Display device, driving method for the display device, and electronic apparatus | |

| JP4784780B2 (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP4666016B2 (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2009237425A (ja) | 表示装置、表示装置の駆動方法および電子機器 | |

| JP2010014748A (ja) | 表示装置および電子機器 | |

| JP2010026119A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2009300697A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2010139543A (ja) | 表示装置、電子機器および表示装置の駆動方法 | |

| JP2010026117A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2009300853A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2010014747A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2010032904A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2010026116A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| WO2013084701A1 (ja) | 表示装置およびその駆動方法、ならびに電子機器 | |

| JP2010014746A (ja) | 表示装置およびその駆動方法ならびに電子機器 | |

| JP2009294279A (ja) | 表示装置、表示装置の駆動方法および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100701 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100812 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101214 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101227 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140121 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140121 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |