JP2010010442A - 配線基板の製造方法 - Google Patents

配線基板の製造方法 Download PDFInfo

- Publication number

- JP2010010442A JP2010010442A JP2008168617A JP2008168617A JP2010010442A JP 2010010442 A JP2010010442 A JP 2010010442A JP 2008168617 A JP2008168617 A JP 2008168617A JP 2008168617 A JP2008168617 A JP 2008168617A JP 2010010442 A JP2010010442 A JP 2010010442A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- electrode

- solder

- wiring board

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W74/15—

Landscapes

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Wire Bonding (AREA)

Abstract

【解決手段】 基板上に形成された電極領域に末端基としてチオール基を有する有機物を付与する工程と、前記基板の表面に疎水性を付与する工程と、次いで、前記有機物を除去する工程と、次いで、前記電極領域にはんだを付着する工程とにより配線基板を製造する。

【選択図】 図3

Description

その後、O2プラズマ処理することによって、ペリフェラル基板電極12の表面に生じた酸化膜を除去する。

次いで、ペリフェラル基板10の表面を、例えば、5%の濃度の塩酸でで処理することによって、ペリフェラル基板電極12の表面に形成された酸化膜を除去する。

〔比較例〕

京セラSLC社製の、実施例と同じ基板を用い、上述の実施例1で説明した表面処理をせずに、実施例と同じ組成のSnペーストをスクリーン印刷法により印刷する。印刷後、はんだリフロー装置を用いて、250℃、30秒の同じ条件でN2 リフロー処理を行う。リフロー処理後の基板をイソプロパノールで洗浄し、さらに、濃度3%の塩酸水溶液で洗浄する実施例1と同じ洗浄条件で洗浄することにより、残渣ならびに基板ソルダーレジスト上に残ったSn粒子を除去した。

(付記1) 基板上に形成された電極領域に末端基としてチオール基を有する有機物を付与する工程と、

前記基板の表面に疎水性を付与する工程と、

次いで、前記有機物を除去する工程と、

次いで、前記電極領域にはんだを付着する工程と

を有することを特徴とする配線基板の製造方法。

(付記2) 前記電極領域にはんだを付着する工程が、少なくとも前記電極領域と該電極領域の間の基板の表面全面にはんだペーストを設ける工程と、次いで、はんだペーストをリフローする工程とを含むことを特徴とする付記1に記載の配線基板の製造方法。

(付記3) 前記はんだペーストが、最大粒径が20μm以下で、融点が250℃以下の金属粒子を含むペーストであることを特徴とする付記2に記載の配線基板の製造方法。

(付記4) 前記有機物の除去を、紫外線照射により行うことを特徴とする付記1乃至3に記載の配線基板の製造方法。

(付記5) 前記有機物は、少なくともアルキル基またはフッ素化アルキル基を有する骨格を含むことを特徴とする付記1乃至4のいずれか1に記載の配線基板の製造方法。

(付記6) 前記有機物は、単分子膜として付与されることを特徴とする付記5に記載の配線基板の製造方法。

(付記7) 前記疎水性を付与する工程は、疎水性を有するシランカップリング剤を付与する工程であることを特徴とする付記1乃至6のいずれか1に記載の配線基板の製造方法。

(付記8) 前記疎水性シランカップリング剤が、フッ素化シランカップリング剤であることを特徴とする付記7に記載の配線基板の製造方法。

(付記9) 前記有機物を付与する工程の前処理として、前記基板の表面に水酸基を付与する工程を有することを特徴とする付記1乃至8のいずれか1に記載の配線基板の製造方法。

(付記10) 前記水酸基を付与した後に、前記電極の表面に生じた酸化膜を除去する工程を有することを特徴とする付記9に記載の配線基板の製造方法。

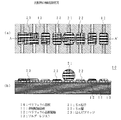

11 多層配線基板

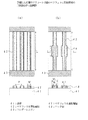

12 ペリフェラル基板電極

13 ソルダーレジスト

14 単分子膜

15 シランカップリング剤

16 はんだペースト

17 予備はんだ層

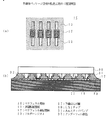

21 Sn粒子

22 Sn層

23 はんだブリッジ

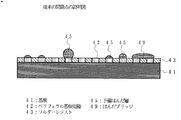

30 LSIチップ

31 Auスタッドバンプ

32 アンダーフィル樹脂

40 ペリフェラル基板

41 基板

42 ペリフェラル基板電極

43 ソルダーレジスト

44 はんだペースト

45 予備はんだ層

47 ペリフェラル基板電極

46 残渣

48 パッド部

49 はんだブリッジ

Claims (5)

- 基板上に形成された電極領域に末端基としてチオール基を有する有機物を付与する工程と、

前記基板の表面に疎水性を付与する工程と、

次いで、前記有機物を除去する工程と、

次いで、前記電極領域にはんだを付着する工程と

を有することを特徴とする配線基板の製造方法。 - 前記有機物の除去を、紫外線照射により行うことを特徴とする請求項1に記載の配線基板の製造方法。

- 前記有機物は、少なくともアルキル基またはフッ素化アルキル基を有する骨格を含むことを特徴とする請求項1または2に記載の配線基板の製造方法。

- 前記疎水性を付与する工程は、疎水性を有するシランカップリング剤を付与する工程であることを特徴とする請求項1乃至3のいずれか1項に記載の配線基板の製造方法。

- 前記有機物を付与する工程の前処理として、前記基板の表面に水酸基を付与する工程を有することを特徴とする請求項1乃至4のいずれか1項に記載の配線基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168617A JP5206154B2 (ja) | 2008-06-27 | 2008-06-27 | 配線基板の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168617A JP5206154B2 (ja) | 2008-06-27 | 2008-06-27 | 配線基板の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010442A true JP2010010442A (ja) | 2010-01-14 |

| JP5206154B2 JP5206154B2 (ja) | 2013-06-12 |

Family

ID=41590569

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008168617A Expired - Fee Related JP5206154B2 (ja) | 2008-06-27 | 2008-06-27 | 配線基板の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5206154B2 (ja) |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61168289A (ja) * | 1985-01-21 | 1986-07-29 | ソニー株式会社 | 電気部品を実装したプリント基板とその製造方法 |

| JPS63278296A (ja) * | 1986-12-10 | 1988-11-15 | Minoru Tsuda | プリント基板及びその製造方法 |

| JPH06326451A (ja) * | 1993-05-12 | 1994-11-25 | Canon Inc | はんだ付け方法 |

| JPH11330666A (ja) * | 1998-05-14 | 1999-11-30 | Seiko Epson Corp | 特定パターン形成用基板およびその製造方法 |

| JP2002185129A (ja) * | 2000-12-15 | 2002-06-28 | Olympus Optical Co Ltd | 回路基板の絶縁劣化不良の防止方法 |

| JP2003060331A (ja) * | 2001-08-21 | 2003-02-28 | Matsushita Electric Ind Co Ltd | プリント配線板の製造方法 |

-

2008

- 2008-06-27 JP JP2008168617A patent/JP5206154B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61168289A (ja) * | 1985-01-21 | 1986-07-29 | ソニー株式会社 | 電気部品を実装したプリント基板とその製造方法 |

| JPS63278296A (ja) * | 1986-12-10 | 1988-11-15 | Minoru Tsuda | プリント基板及びその製造方法 |

| JPH06326451A (ja) * | 1993-05-12 | 1994-11-25 | Canon Inc | はんだ付け方法 |

| JPH11330666A (ja) * | 1998-05-14 | 1999-11-30 | Seiko Epson Corp | 特定パターン形成用基板およびその製造方法 |

| JP2002185129A (ja) * | 2000-12-15 | 2002-06-28 | Olympus Optical Co Ltd | 回路基板の絶縁劣化不良の防止方法 |

| JP2003060331A (ja) * | 2001-08-21 | 2003-02-28 | Matsushita Electric Ind Co Ltd | プリント配線板の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5206154B2 (ja) | 2013-06-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2003338522A (ja) | バンプ電極付き電子部品およびその製造方法 | |

| JP2008078682A (ja) | フリップチップ実装装置 | |

| KR101940237B1 (ko) | 미세 피치 pcb 기판에 솔더 범프 형성 방법 및 이를 이용한 반도체 소자의 플립 칩 본딩 방법 | |

| KR101175482B1 (ko) | 플립 칩 실장 방법 및 범프 형성 방법 | |

| US9674952B1 (en) | Method of making copper pillar with solder cap | |

| KR101228904B1 (ko) | 마이크로 볼을 이용한 범프 제조방법 | |

| JP2005322915A (ja) | 構成要素の表面実装アタッチメント | |

| TW201315304A (zh) | 印刷電路板及其製造方法 | |

| TW201414386A (zh) | 印刷電路基板之製造方法 | |

| JP5206154B2 (ja) | 配線基板の製造方法 | |

| TWI613741B (zh) | 銲點凸塊製造方法 | |

| CN1166480C (zh) | 高分辨率焊接凸块形成方法 | |

| JP5147723B2 (ja) | 電極構造体 | |

| KR100765146B1 (ko) | 솔더 페이스트 및 이를 이용한 솔더 범프 형성방법 | |

| JP4702271B2 (ja) | 導電性バンプの形成方法 | |

| JP4453919B2 (ja) | バンプ電極付き電子部品の製造方法 | |

| KR101019385B1 (ko) | 솔더볼 부착 방법 및 이를 이용한 솔더링 방법 | |

| KR20110013902A (ko) | 패키지 및 그 제조방법 | |

| JP5316209B2 (ja) | 回路基板及び回路基板の製造方法 | |

| JP4703835B2 (ja) | アンダーバンプメタル、半導体装置用バンプ、導電性ボール付半導体装置 | |

| US7538021B2 (en) | Removing dry film resist residues using hydrolyzable membranes | |

| JP2006100844A (ja) | バンプ電極付き電子部品 | |

| JP2002224884A (ja) | 半田付け用フラックス及びこれを用いた半田バンプの形成方法 | |

| JP4710513B2 (ja) | フリップチップ実装方法および基板間接続方法 | |

| JP2008004938A (ja) | 再配線にはんだを付ける方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110315 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110915 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120711 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130204 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160301 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |