JP2010009103A - 外乱抑制装置、外乱抑制装置制御方法及び外乱抑制型制御装置 - Google Patents

外乱抑制装置、外乱抑制装置制御方法及び外乱抑制型制御装置 Download PDFInfo

- Publication number

- JP2010009103A JP2010009103A JP2008164218A JP2008164218A JP2010009103A JP 2010009103 A JP2010009103 A JP 2010009103A JP 2008164218 A JP2008164218 A JP 2008164218A JP 2008164218 A JP2008164218 A JP 2008164218A JP 2010009103 A JP2010009103 A JP 2010009103A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- disturbance

- estimated

- control

- filter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Moving Of The Head To Find And Align With The Track (AREA)

- Optical Recording Or Reproduction (AREA)

- Feedback Control In General (AREA)

Abstract

【解決手段】外乱抑制型制御装置100を、制御指令信号τを生成する制御器10と、該τと外乱オブザーバ信号τd’とを加算する加算器12と、制御対象14と、外乱オブザーバ信号τd’を生成する外乱オブザーバ16とを含んだ構成とし、外乱オブザーバ16を、逆システム20と、減算部22と、ローパスフィルタの機能を有するQフィルタ部24とを含んだ構成とし、Qフィルタ部24のフィルタ処理において、該処理後の固定小数点数のデータにおける小数部分を切り捨てるときに、小数部分を整数部分に丸め込んでから切り捨てるようにした。

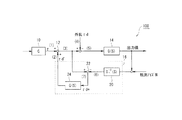

【選択図】図1

Description

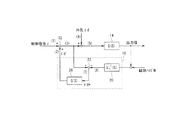

以下、図4に基づき、外乱オブザーバを含む制御系において、演算結果の固定小数点数の小数部分を切り捨てた場合に生じる問題について具体的に説明する。

加算器12は、制御対象14への制御指令信号τと外乱オブザーバ16からの外乱オブザーバ信号τd’とを加算する。この加算信号は、途中で振動や衝撃といった外乱τdによる影響を受けて制御対象14に入力される。一方、外乱の影響を受ける前の加算信号は、外乱オブザーバ16に入力される。また、制御対象14からの出力信号(例えば、位置信号θ)は、観測ノイズNが混入され、この観測ノイズNの混入した出力信号が外乱オブザーバ16に入力される。

制御対象14からの観測ノイズNの混入した出力信号は、逆システム20に入力され、その伝達関数「Gn -1(s)」によって、制御対象14が該出力信号を出力するための制御指令信号へと変換される。更に、この制御指令信号(以下、推定制御指令信号と称す)は、減算部22において、加算器12からの加算信号から減じられる。この減算信号(差分信号)は、外乱の推定値を示す信号(以下、推定外乱信号τd*と称す)となる。この推定外乱信号τd*は、ローパスフィルタとして機能するQフィルタ部26に入力される(実際は、A/D変換器などを介してDSP等の演算装置に入力される)。Qフィルタ部26は、固定小数点数のフィルタ係数を用いた演算処理によって、推定外乱信号τd*から観測ノイズNの周波数領域などを含む不要な周波数成分(高周波成分)を除去して、外乱オブザーバ信号τd’を生成し、これを加算器12に出力する。このQフィルタ部26における演算処理においては、処理負荷の軽減などのために、演算結果の固定小数点数の小数部分が切り捨てられる。従って、フィルタ処理後の推定外乱値は、小数部分が切り捨てられたものとなり、この信号が外乱オブザーバ信号τd’として加算器12に出力される。

そこで、本発明は、このような従来の技術の有する未解決の課題に着目してなされたものであって、外乱オブザーバを構成するQフィルタにおける演算処理において固定小数点数の小数部分を切り捨てる際に生じる誤差の影響を低減するのに好適な外乱抑制装置、外乱抑制装置制御方法及び外乱抑制型制御装置を提供することを目的としている。

ここで、上記小数部分を整数部分に丸め込むとは、10進数で言うところの四捨五入に相当する処理である。つまり、小数部分の最上位桁が5以上のときは、整数部分の最下位桁に1を切り上げ、4以下のときは切り上げない処理(例えば、「35.542→36」、「35.432→35」)となる。

また、上記Qフィルタは、例えば、電子回路などのハードウェアで構成されたフィルタ回路、または信号データを数値化し、演算処理によってソフトウェア的に処理するディジタルフィルタのハードウェア及びソフトウェアのいずれでも構成することが可能なフィルタである。前者の場合は、フィルタ回路に直接信号を入力して、該入力信号のうち所望の周波数の信号成分だけを回路素子によって選択的に通過させる。また、後者の場合は、制御信号をA/D変換器などを用いて数値データ化して、DSPなどの演算装置の演算処理によって制御信号から所望の周波数の信号成分が残るように他の信号成分を除去する処理となる。以下、発明5の外乱抑制装置制御方法、及び発明6の外乱抑制型制御装置において同じである。

このような構成であれば、Qフィルタ部によって、推定外乱信号に含まれるモデリング誤差や観測ノイズなどの高調波成分(雑音成分)を除去することができるので、外乱を高精度に推定できると共に、雑音成分による誤動作の発生を低減することができる。

これによって、より高精度に制御対象の受ける外乱を推定することができる。

このような構成であれば、上記発明1に記載の外乱抑制装置と同等の作用及び効果が得られる。

このような構成であれば、上記発明1乃至3のいずれか1に記載の外乱抑制装置と同等の作用及び効果が得られる。

まず、本発明に係る外乱抑制型制御装置の構成を図1に基づき説明する。図1は、本実施の形態に係る外乱抑制型制御装置100の構成を示す制御ブロック図である。

外乱抑制型制御装置100は、図1に示すように、制御器10と、加算器12と、制御対象14と、外乱オブザーバ16とを含んで構成される。本実施の形態においては、制御対象14を、トルク指令信号を入力としてモータを回転し、角度位置信号θを出力するDDモータとして説明をする。

加算器12は、制御器10からの制御指令信号τと外乱オブザーバ16からの外乱オブザーバ信号τd’との加算信号を生成して、これを制御対象14に出力する。この加算信号「τ+τd’」は、制御対象14に到達する前に外乱τdの影響を受けて、「τ+τd’−τd」となる。つまり、「τd’−τd=0」となったときに外乱が全て打ち消されることになる。

外乱オブザーバ16は、制御指令信号τに混入する外乱τdの影響を抑制する役割を果たすものであって、逆システム20と、減算部22と、Qフィルタ部24とを含んで構成される。

本実施の形態において、逆システム20は、アナログ信号をデジタル信号に変換する不図示のA/D変換器と、上記「1/Gn(s)」の入出力関係を有する制御系の機能を不図示のプロセッサ(ここではDSP)に実現させるための専用のプログラムと、該プログラムを実行するプロセッサとを含んで構成される。

Qフィルタ部24は、ローパスフィルタの機能を不図示のプロセッサ(ここではDSP)に実現させるための専用のプログラム(ディジタルフィルタQ(s))と、このプログラムを実行するプロセッサ(逆システム20と同じもの)と、不図示のD/A変換器とを含んで構成される。

y(k)=A{u(k)+u(k−1)}+(1−2A)y(k−1)・・・(1)

上式(1)において、y(k−1)は(k−1)サンプル目のフィルタ処理後の推定外乱値(外乱オブザーバ値)τd’である。

y(k)=A{u(k)+u(k−1)−2y(k−1)}+y(k−1)・・(2)

つまり、本実施の形態において、ディジタルフィルタQ(s)は、1次のIIR (Infinite Impulse Response) フィルタとなる。

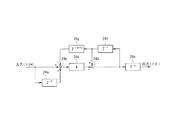

ディジタルフィルタQ(s)は、図2に示すように、第1遅延部24aと、加減算部24bと、係数乗算部24cと、加算部24dと、第1除算部24eと、第2遅延部24fと、第2除算部24gとを含んで構成される。

第1除算部24eは、加算部24dの加算結果y(k)(2nビット)におけるmビットの小数部を(2n−m)ビットの整数部に丸め込むと共に、2mで除算(整数部をmビット右へシフト)することで小数部を切り捨てる。具体的に、mビットの小数部の最上位ビットに1を加算してから、整数部をmビット右へシフトすることで小数部を切り捨てる。これにより、小数部の最上位ビットが1のときは切り上げが生じて、小数部の情報が整数部に加えられることになる。一方、最上位ビットが0のときは切り上げが生じないので、従来の切り捨てと同じとなる。つまり、最上位ビットが0のときは、小数部の値が指令値と比較して小さいと判断し無視する。

第2遅延部24fは、RAM等のバッファメモリ(遅延素子)からデータを読み出す機能ブロックであって、kサンプル目のフィルタ処理において、バッファメモリに保持された(k−1)サンプル目のy(k−1)を読み出して除算部24gに出力する。更に、y(k−1)を出力後にkサンプル目の入力値y(k)をバッファメモリに保存する。

次に、図3に基づき、本実施の形態の動作を説明する。

ここで、図3(a)〜(c)は、係数乗算部24c及び加算部24dの演算処理の流れを示す図であり、(c)〜(d)は、従来の除算処理を示す図であり、(e)〜(g)は、本発明の丸め込み処理及び除算処理を示す図である。

以下、kサンプル目のτd*であるu(k)が入力されたとして動作を説明する。

u(k)の入力タイミングに合わせて、第1遅延部24aにおいて1つ前のサンプル入力値であるu(k−1)が読み出されて加減算部24bに入力される。一方、第2除算部24gからは、u(k)の入力タイミングに合わせて、1サンプル前の入力値に対するフィルタ処理結果y(k−1)を2倍にした2y(k−1)が加減算部24bに入力される。これにより、加減算部24bでは、「X=u(k)+u(k−1)−2y(k−1)」の演算処理が実行される。この演算結果Xは、係数乗算部24cに入力される。

係数乗算部24cは、図3(a)に示すように、加減算部24bの演算結果である16ビットのX(小数部なし)が入力されると、不図示のROMから、図3(b)に示すように、16ビットの固定小数点数であるフィルタ係数A(小数部15ビット)を読み出す。そして、入力されたXと読み出したフィルタ係数Aとを乗算して、32ビットの固定小数点数である「X・A」を算出する。この演算結果である「X・A」は、加算部24dに入力される。

第1除算部24eは、32ビットのy(k)における17ビットの整数部を右に15ビットシフトすることで、15ビットの小数部(図中の▲より右のビット)を切り捨てる。ここで、図3(d)に示すように、丸め込みの処理を行わずに、整数部を単に右に15ビットシフトすると従来の切り捨て処理となる。

このy(k)’は、不図示のD/A変換器によって、アナログの外乱オブザーバ信号τd’に変換され、加算器12に出力される。このτd’には、単純な切り捨てによる演算誤差よりも小さい演算誤差しか含まれないので、制御指令値と演算誤差とが打ち消しあうといったことが生じるのを低減することができる。

一方、第2除算部24gには、第2遅延部24fにおいて1サンプル前の加算部24dの出力であるy(k−1)(32ビット)が入力され、第1除算部24eと同様に、15ビットの小数部の最上位ビットに1を加算する丸め込み処理が行われる。

上記したように、本実施の形態の外乱抑制型制御装置100は、外乱オブザーバ16を構成するQフィルタ部24における、ディジタルフィルタQ(s)のフィルタ処理において、フィルタ係数Aを用いた固定小数演算後の固定小数点数の小数部分を切り捨てるときに、小数部分の最上位ビットに1を加算してから行うことが可能である。

上記実施の形態において、制御対象14は、発明1、3、4及び5のいずれか1の制御対象に対応し、外乱オブザーバ16は、発明1、4及び5のいずれか1に記載の外乱オブザーバに対応し、外乱オブザーバ16及び加算器12を含む構成部は、発明1乃至4のいずれか1に記載の外乱抑制装置に対応し、加算器12は、発明1、4及び5のいずれか1に記載の加算信号生成部に対応し、逆システム20及び減算部22は、発明1、3及び4のいずれか1に記載の推定外乱信号生成部に対応し、Qフィルタ部24は、発明1乃至4のいずれか1に記載のQフィルタ部に対応し、制御器10は、発明5に記載の誤差信号生成部及び制御指令信号生成部に対応する。

なお、上記実施の形態においては、外乱オブザーバ16の各処理を、演算装置に専用のプログラムを実行させることで行う構成としたが、これに限らず、ハードウェア主体で前記各処理を実行する構成としても良い。

また、上記実施の形態においては、本発明をDDモータのフィードバック制御に適用したが、これに限らず、DDモータ以外のモータや、モータ以外の制御対象に適用してもよい。

10 制御器

12 加算器

14 制御対象

16 外乱オブザーバ

20 逆システム

22 減算部

24,26 Qフィルタ部

Claims (5)

- 制御対象の受ける外乱の影響を抑制するための外乱オブザーバ信号を生成する外乱オブザーバと、前記制御対象への制御指令信号と前記外乱オブザーバ信号との加算信号を生成する加算信号生成部とを備えた外乱抑制装置であって、

前記外乱オブザーバは、前記出力信号と前記加算信号とに基づき前記外乱の推定値を示す推定外乱信号を生成する推定外乱信号生成部と、固定小数点数のフィルタ係数を用いた演算処理によって、前記推定外乱信号に含まれる不要な周波数領域の信号成分を選択的に除去するQフィルタ部とを含んで構成されており、

前記Qフィルタ部は、前記フィルタ係数を用いた演算処理後の固定小数点数の小数部分を該固定小数点数の整数部分に丸め込むと共に、前記小数部分を切り捨てる小数部切捨手段を備えることを特徴とする外乱抑制装置。 - 前記Qフィルタ部は、前記推定外乱信号における所定周波数よりも高い周波数領域の信号成分を選択的に除去するローパスフィルタの機能を有することを特徴とする請求項1に記載の外乱抑制装置。

- 前記推定外乱信号生成部は、前記制御対象の伝達関数の逆関数と前記出力信号とを用いて、前記制御対象が前記出力信号を出力するのに必要な、外乱成分を含む制御指令信号である推定制御指令信号を生成する推定制御指令信号生成手段と、前記推定制御指令信号と前記加算信号との差分信号を生成する差分信号生成手段とを含み、

前記Qフィルタ部において、前記差分信号をフィルタ処理することで前記外乱オブザーバ信号を生成することを特徴とする請求項1又は請求項2に記載の外乱抑制装置。 - 制御対象の受ける外乱を抑圧するための外乱オブザーバ信号を生成する外乱オブザーバと、前記制御対象への制御指令信号と前記外乱オブザーバ信号との加算信号を生成する加算信号生成部とを備えた外乱抑制装置を制御する外乱抑制装置制御方法であって、

前記外乱オブザーバは、前記出力信号と前記加算信号とに基づき前記外乱の推定値を示す推定外乱信号を生成する推定外乱信号生成部と、固定小数点数のフィルタ係数を用いた演算処理によって、前記推定外乱信号に含まれる不要な周波数領域の信号成分を選択的に除去するQフィルタ部とを含んで構成されており、

前記Qフィルタ部に、前記演算処理において固定小数点数の小数部分を該固定小数点数の整数部分に丸め込ませると共に該小数部分を切り捨てさせる小数部切捨ステップを含むことを特徴とする外乱抑制装置制御方法。 - 制御対象の出力する出力信号の目標信号に対する誤差を示す誤差信号を生成する誤差信号生成部と、前記誤差信号に基づき前記制御対象に与えるべく制御指令信号を生成する制御指令信号生成部と、前記制御対象の受ける外乱を抑圧するための外乱オブザーバ信号を生成する外乱オブザーバと、前記制御指令信号と前記外乱オブザーバ信号との加算信号を生成する加算信号生成部とを備えた外乱抑制型制御装置であって、

請求項1乃至請求項3のいずれか1項に記載の外乱抑制装置を備えることを特徴とする外乱抑制型制御装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008164218A JP5446143B2 (ja) | 2008-06-24 | 2008-06-24 | 外乱抑制装置、外乱抑制装置制御方法、外乱抑制型制御装置及び回転型ダイレクト・ドライブ・モータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008164218A JP5446143B2 (ja) | 2008-06-24 | 2008-06-24 | 外乱抑制装置、外乱抑制装置制御方法、外乱抑制型制御装置及び回転型ダイレクト・ドライブ・モータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010009103A true JP2010009103A (ja) | 2010-01-14 |

| JP5446143B2 JP5446143B2 (ja) | 2014-03-19 |

Family

ID=41589556

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008164218A Active JP5446143B2 (ja) | 2008-06-24 | 2008-06-24 | 外乱抑制装置、外乱抑制装置制御方法、外乱抑制型制御装置及び回転型ダイレクト・ドライブ・モータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5446143B2 (ja) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07168713A (ja) * | 1994-10-24 | 1995-07-04 | Mitsubishi Electric Corp | ディジタル信号処理プロセッサ |

| JP2000330642A (ja) * | 1999-05-20 | 2000-11-30 | Sumitomo Heavy Ind Ltd | ステージの位置制御装置及び速度制御装置 |

| JP2001210032A (ja) * | 2000-01-25 | 2001-08-03 | Sanyo Electric Co Ltd | ディスク装置におけるアクチュエータ制御装置 |

| WO2005104365A1 (ja) * | 2004-04-19 | 2005-11-03 | Neuro Solution Corp. | デジタルフィルタの設計方法および設計装置、デジタルフィルタ設計用プログラム、デジタルフィルタ、所望周波数特性の数値列の生成方法および生成装置、所望周波数特性の数値列生成用プログラム |

| JP2006011819A (ja) * | 2004-06-25 | 2006-01-12 | Toyo Electric Mfg Co Ltd | 制御装置 |

-

2008

- 2008-06-24 JP JP2008164218A patent/JP5446143B2/ja active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07168713A (ja) * | 1994-10-24 | 1995-07-04 | Mitsubishi Electric Corp | ディジタル信号処理プロセッサ |

| JP2000330642A (ja) * | 1999-05-20 | 2000-11-30 | Sumitomo Heavy Ind Ltd | ステージの位置制御装置及び速度制御装置 |

| JP2001210032A (ja) * | 2000-01-25 | 2001-08-03 | Sanyo Electric Co Ltd | ディスク装置におけるアクチュエータ制御装置 |

| WO2005104365A1 (ja) * | 2004-04-19 | 2005-11-03 | Neuro Solution Corp. | デジタルフィルタの設計方法および設計装置、デジタルフィルタ設計用プログラム、デジタルフィルタ、所望周波数特性の数値列の生成方法および生成装置、所望周波数特性の数値列生成用プログラム |

| JP2006011819A (ja) * | 2004-06-25 | 2006-01-12 | Toyo Electric Mfg Co Ltd | 制御装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5446143B2 (ja) | 2014-03-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN116324632B (zh) | 车辆系统振动抑制控制设备和振动抑制控制方法 | |

| JP5192802B2 (ja) | モータ制御装置、及びモータ制御システム | |

| JP3796261B1 (ja) | モータの負荷イナーシャ推定方法 | |

| JP6491497B2 (ja) | モータ制御装置 | |

| JP6191600B2 (ja) | エンコーダ、駆動装置、及びロボット装置 | |

| JP6671036B2 (ja) | 騒音低減装置、移動体装置、及び、騒音低減方法 | |

| JP5065784B2 (ja) | 同相成分抽出方法及び装置 | |

| TWI386845B (zh) | Error calculation of the integer division operation circuit | |

| JP5229314B2 (ja) | Cordic演算回路及び方法 | |

| JP5446143B2 (ja) | 外乱抑制装置、外乱抑制装置制御方法、外乱抑制型制御装置及び回転型ダイレクト・ドライブ・モータ | |

| CN104467844A (zh) | 一种时间交织模数转换器及方法 | |

| EP3709299A1 (en) | Digital audio processing device, method for processing digital audio, and digital audio processing program | |

| JPWO2008018197A1 (ja) | デジタルフィルタ、その合成装置、合成プログラム、及び合成プログラム記録媒体 | |

| JP6070572B2 (ja) | ディジタルフィルタ回路およびディジタルフィルタ処理方法 | |

| TWI546801B (zh) | 取樣率轉換器與用於其中之比率估測器及其比率估測方法 | |

| JP5652873B2 (ja) | デジタルアナログ変換装置およびその制御方法 | |

| CN105656450B (zh) | 整数运算的数字低通滤波方法及装置 | |

| JP4838206B2 (ja) | フィルタ回路および方法 | |

| JP2011147009A (ja) | デジタルフィルタおよびデジタルフィルタリング方法 | |

| RU2684190C1 (ru) | Многоскоростной цифровой экстраполятор | |

| JP7225621B2 (ja) | サーボ制御装置 | |

| JP6410919B2 (ja) | 位相周波数検出装置 | |

| JPH04281524A (ja) | 浮動小数点演算処理装置 | |

| JP4640321B2 (ja) | 波形発生回路 | |

| JP2012160907A (ja) | デジタルフィルタ、無線装置、フィルタリング方法及びプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120724 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120725 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130402 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130531 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131203 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131216 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5446143 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |