JP2010004025A - 光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器 - Google Patents

光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器 Download PDFInfo

- Publication number

- JP2010004025A JP2010004025A JP2009118196A JP2009118196A JP2010004025A JP 2010004025 A JP2010004025 A JP 2010004025A JP 2009118196 A JP2009118196 A JP 2009118196A JP 2009118196 A JP2009118196 A JP 2009118196A JP 2010004025 A JP2010004025 A JP 2010004025A

- Authority

- JP

- Japan

- Prior art keywords

- photoelectric conversion

- potential

- switch

- circuit

- conversion device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000006243 chemical reaction Methods 0.000 title claims abstract description 209

- 238000000034 method Methods 0.000 title claims description 32

- 230000003321 amplification Effects 0.000 claims abstract description 5

- 238000003199 nucleic acid amplification method Methods 0.000 claims abstract description 5

- 239000003990 capacitor Substances 0.000 claims description 114

- 239000000758 substrate Substances 0.000 claims description 44

- 239000010409 thin film Substances 0.000 claims description 13

- 239000010408 film Substances 0.000 description 148

- 239000004065 semiconductor Substances 0.000 description 54

- 239000010410 layer Substances 0.000 description 43

- 239000011229 interlayer Substances 0.000 description 22

- 238000010586 diagram Methods 0.000 description 18

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 16

- 229910052710 silicon Inorganic materials 0.000 description 16

- 239000010703 silicon Substances 0.000 description 16

- 229910052760 oxygen Inorganic materials 0.000 description 14

- 239000001301 oxygen Substances 0.000 description 13

- 230000001681 protective effect Effects 0.000 description 13

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 12

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- 229910021417 amorphous silicon Inorganic materials 0.000 description 11

- 230000004888 barrier function Effects 0.000 description 11

- 239000013078 crystal Substances 0.000 description 11

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 239000012535 impurity Substances 0.000 description 10

- 230000003287 optical effect Effects 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 9

- 229910052757 nitrogen Inorganic materials 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- 230000008859 change Effects 0.000 description 8

- 238000005247 gettering Methods 0.000 description 8

- 238000010438 heat treatment Methods 0.000 description 8

- 239000001257 hydrogen Substances 0.000 description 8

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 239000002356 single layer Substances 0.000 description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 6

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 6

- 238000002425 crystallisation Methods 0.000 description 6

- 238000005755 formation reaction Methods 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 230000004044 response Effects 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 239000012298 atmosphere Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- 239000002585 base Substances 0.000 description 4

- 230000003197 catalytic effect Effects 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 230000008025 crystallization Effects 0.000 description 4

- 238000007599 discharging Methods 0.000 description 4

- -1 etc.) Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 239000010948 rhodium Substances 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 3

- 238000001678 elastic recoil detection analysis Methods 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 239000003054 catalyst Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 229910052762 osmium Inorganic materials 0.000 description 2

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 238000001994 activation Methods 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- AZDRQVAHHNSJOQ-UHFFFAOYSA-N alumane Chemical group [AlH3] AZDRQVAHHNSJOQ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000023077 detection of light stimulus Effects 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01J—MEASUREMENT OF INTENSITY, VELOCITY, SPECTRAL CONTENT, POLARISATION, PHASE OR PULSE CHARACTERISTICS OF INFRARED, VISIBLE OR ULTRAVIOLET LIGHT; COLORIMETRY; RADIATION PYROMETRY

- G01J1/00—Photometry, e.g. photographic exposure meter

- G01J1/42—Photometry, e.g. photographic exposure meter using electric radiation detectors

- G01J1/4204—Photometry, e.g. photographic exposure meter using electric radiation detectors with determination of ambient light

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01J—MEASUREMENT OF INTENSITY, VELOCITY, SPECTRAL CONTENT, POLARISATION, PHASE OR PULSE CHARACTERISTICS OF INFRARED, VISIBLE OR ULTRAVIOLET LIGHT; COLORIMETRY; RADIATION PYROMETRY

- G01J1/00—Photometry, e.g. photographic exposure meter

- G01J1/42—Photometry, e.g. photographic exposure meter using electric radiation detectors

- G01J1/44—Electric circuits

- G01J1/46—Electric circuits using a capacitor

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/772—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising A/D, V/T, V/F, I/T or I/F converters

Abstract

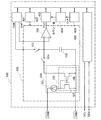

【解決手段】光電変換素子と、光電変換素子の出力電流を増幅する増幅回路と、を含む光電変換回路と、第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して増幅回路で増幅された電流に応じた充電または放電がなされる容量素子と、容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、を有する。

【選択図】図1

Description

本実施の形態では、光電変換装置の構成及びその動作について説明する。なお本実施の形態で説明する本発明の光電変換装置は、光電変換素子により得られる入射光量に関するアナログの信号(以下、アナログ信号という)をデジタルの信号(以下、デジタル信号)に変換するための回路を含むものである。

本実施の形態では、上記実施の形態で説明した光電変換回路109の増幅回路102におけるトランジスタについて、nチャネル型トランジスタを例として挙げて説明したが、pチャネル型トランジスタを用いた構成について説明する。なお本実施の形態では、上記実施の形態1で説明した箇所については同一の符号を付し、説明を省略する。

本実施の形態では、光電変換装置の作製方法について図15、図16を用いて詳しく述べる。なお、本実施の形態では、光電変換装置の各回路を構成する素子である薄膜トランジスタ(TFT)と、光電変換素子である縦型接合タイプのPINフォトダイオード(以下、フォトダイオードともいう)とを具備する光電変換装置の一例を示す。なお光電変換装置は、TFT及びPINフォトダイオードの他に、記憶素子、抵抗、ダイオード、容量、インダクタなども用いることがある。また、光電変換装置は、縦型接合タイプのPINフォトダイオードの代わりに、縦型接合タイプのPNフォトダイオードを用いていても良い。

光電変換装置は、入射光量が小さい場合であっても、容量素子への電荷の蓄積を行い、光の強度の検出を可能とし、構成する定電流源またはスイッチ等の素子数を増加させることなく動作させることができるといった特徴を有している。よって、光電変換装置を具備する電子機器は、光電変換装置をその構成要素に追加することに伴って、電子機器の生産コストの上昇を抑制し、暗所での光の検出を行うことができる。光電変換装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、光電変換装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、などが挙げられる。これら電子機器の具体例を図17に示す。

11 光電変換素子

12 増幅回路

13 スイッチ

14 スイッチ

15 容量素子

16 コンパレータ

17 光電変換回路

100 光電変換装置

101 光電変換素子

102 増幅回路

103 スイッチ

104 スイッチ

105 容量素子

106 コンパレータ

107 nチャネル型トランジスタ

108 nチャネル型トランジスタ

109 光電変換回路

203 pチャネル型トランジスタ

204 アナログスイッチ

400 光電変換装置

401 定電圧回路

402 制御回路

403 ラッチ回路

404 カウンター回路

405 クロック生成回路

406 インターフェース回路

701 ステップ

702 ステップ

703 ステップ

704 ステップ

705 ステップ

706 ステップ

707 ステップ

900 光電変換装置

901 光電変換素子

902 増幅回路

903 スイッチ

907 pチャネル型トランジスタ

908 pチャネル型トランジスタ

909 光電変換回路

1000 光電変換装置

1100 光電変換装置

1301 ステップ

1302 ステップ

1303 ステップ

1304 ステップ

1305 ステップ

1306 ステップ

1307 ステップ

1401 基板

1402 下地絶縁膜

1403 島状半導体領域

1404 ゲート絶縁膜

1405 配線

1406 配線

1407 端子電極

1408 ゲート電極

1409 ドレイン領域

1410 層間絶縁膜

1411 層間絶縁膜

1412 配線

1413 接続電極

1414 端子電極

1415 ドレイン電極

1416 保護電極

1417 保護電極

1418 保護電極

1419 保護電極

1420 光電変換素子

1421 封止層

1422 端子電極

1423 端子電極

1500 TFT

5001 筐体

5002 表示部

5003 センサ部

5101 本体

5102 表示部

5103 音声入力部

5104 音声出力部

5105 操作キー

5106 センサ部

1420i i型半導体層

1420n n型半導体層

1420p p型半導体層

Claims (16)

- 光電変換素子と、前記光電変換素子の出力電流を増幅する増幅回路と、を含む光電変換回路と、

第1のスイッチを介して第1の電位が供給され、第2のスイッチを介して前記増幅回路で増幅された電流に応じた充電または放電がなされる容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。 - 光電変換素子と、前記光電変換素子の出力電流が流れる第1のnチャネル型トランジスタと、前記出力電流が増幅された電流が流れる第2のnチャネル型トランジスタと、を含む回路と、を有する光電変換回路と、

第1のスイッチを介して第1の電位が供給されることにより充電され、第2のスイッチを介して前記第2のnチャネル型トランジスタの第1端子と電気的に接続されることで放電される容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。 - 請求項1または請求項2において、前記コンパレータは、前記容量素子の一方の電極の電位と第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置。

- 請求項3において、

前記光電変換装置は、

クロック信号を生成し、出力するクロック生成回路と、

前記クロック信号によりカウント値をカウントアップし、前記出力信号に基づいて前記カウント値を出力するカウンター回路と、

前記カウント値を保持するラッチ回路と、

を有することを特徴とする光電変換装置。 - 請求項2乃至請求項4のいずれか一において、前記光電変換回路は前記第2のnチャネル型トランジスタを複数有し、前記複数の第2のnチャネル型トランジスタにおける第1端子及び第2端子は、互いに電気的に接続されていることを特徴とする光電変換装置。

- 請求項2乃至請求項5のいずれか一において、前記第1のnチャネル型トランジスタ、前記第2のnチャネル型トランジスタ、前記第1のスイッチ及び前記第2のスイッチは、薄膜トランジスタで構成されていることを特徴とする光電変換装置。

- 光電変換素子と、前記光電変換素子の出力電流を流すための第1のpチャネル型トランジスタと、前記出力電流が増幅された電流を流すための第2のpチャネル型トランジスタと、を含むカレントミラー回路と、を有する光電変換回路と、

第1のスイッチを介して第1の電位が供給されることにより放電され、第2のスイッチを介して前記第2のpチャネル型トランジスタの第1端子と電気的に接続されることで充電される容量素子と、

前記容量素子の一方の電極の電位と第2の電位を比較するためのコンパレータと、

を有することを特徴とする光電変換装置。 - 請求項7において、前記コンパレータは、前記容量素子の一方の電極の電位と前記第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置。

- 請求項8において、

前記光電変換装置は、

クロック信号を生成し出力するクロック生成回路と、

前記クロック信号によりカウント値をカウントアップし、前記出力信号に基づいて前記カウント値を出力するカウンター回路と、

前記カウント値を保持するラッチ回路と、を有することを特徴とする光電変換装置。 - 請求項7乃至請求項9のいずれか一において、前記光電変換回路は前記第2のpチャネル型トランジスタを複数有し、前記複数の第2のpチャネル型トランジスタにおける第1端子及び第2端子は、互いに電気的に接続されて設けられることを特徴とする光電変換装置。

- 請求項7乃至請求項10のいずれか一において、前記第1のpチャネル型トランジスタ、前記第2のpチャネル型トランジスタ、並びに前記第1のスイッチ及び前記第2のスイッチは、薄膜トランジスタであることを特徴とする光電変換装置。

- 請求項1乃至請求項11のいずれか一において、

前記光電変換装置は、透光性基板上に設けられていることを特徴とする光電変換装置。 - 請求項1乃至請求項12に記載の光電変換装置を具備することを特徴とする電子機器。

- 第1のスイッチと、

第2のスイッチと、

容量素子と、

光電変換素子並びに前記光電変換素子の出力電流を流すための第1のnチャネル型トランジスタ及び前記出力電流が増幅された電流を流すための第2のnチャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、

前記容量素子の一方の電極と第2の電位を比較するためのコンパレータと、を有し、

前記第1のスイッチを導通状態、前記第2のスイッチを非導通状態とすることにより、前記容量素子を第1の電位により充電させ、

前記第1のスイッチを非導通状態、前記第2のスイッチを導通状態とし、前記容量素子を前記第1のnチャネル型トランジスタを流れる電流に応じて放電させ、

前記コンパレータより前記容量素子の一方の電極の電位と前記第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置の駆動方法。 - 第1のスイッチと、

第2のスイッチと、

容量素子と、

光電変換素子並びに前記光電変換素子の出力電流を流すための第1のpチャネル型トランジスタ及び前記出力電流が増幅された電流を流すための第2のpチャネル型トランジスタを含むカレントミラー回路を有する光電変換回路と、

前記容量素子の一方の電極と第2の電位を比較するためのコンパレータと、を有し、

前記第1のスイッチを導通状態、前記第2のスイッチを非導通状態とすることにより、前記容量素子を第1の電位により放電させ、

前記第1のスイッチを非導通状態、前記第2のスイッチを導通状態とし、前記容量素子を前記第1のnチャネル型トランジスタを流れる電流に応じて充電させ、

前記コンパレータより前記容量素子の一方の電極の電位と前記第2の電位を比較した結果を出力信号として出力することを特徴とする光電変換装置の駆動方法。 - 請求項14または請求項15において、

前記光電変換装置は、ラッチ回路と、カウンター回路と、及びクロック生成回路と、を有し、

前記第1のスイッチを非導通状態、前記第2のスイッチを導通状態となったと同時に、前記クロック生成回路はクロック信号を出力し、

前記カウンター回路は、前記クロック信号に応じてカウント値をカウントアップし、

前記ラッチ回路は、前記出力信号に基づき、前記カウント値を保持することを特徴とする光電変換装置の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009118196A JP2010004025A (ja) | 2008-05-21 | 2009-05-15 | 光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008132835 | 2008-05-21 | ||

| JP2009118196A JP2010004025A (ja) | 2008-05-21 | 2009-05-15 | 光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004025A true JP2010004025A (ja) | 2010-01-07 |

| JP2010004025A5 JP2010004025A5 (ja) | 2012-05-10 |

Family

ID=41341382

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009118196A Withdrawn JP2010004025A (ja) | 2008-05-21 | 2009-05-15 | 光電変換装置、及び当該光電変換装置の駆動方法、並びに当該光電変換装置を具備する電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8124922B2 (ja) |

| JP (1) | JP2010004025A (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010016449A1 (en) * | 2008-08-08 | 2010-02-11 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and electronic device having the same |

| KR102023128B1 (ko) | 2009-10-21 | 2019-09-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 아날로그 회로 및 반도체 장치 |

| KR101733755B1 (ko) * | 2010-01-15 | 2017-05-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 전자 기기 |

| WO2011099368A1 (en) * | 2010-02-12 | 2011-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the same |

| US8369172B2 (en) | 2010-07-27 | 2013-02-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated circuits for providing clock periods and operating methods thereof |

| US9209209B2 (en) * | 2010-10-29 | 2015-12-08 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and method for operating the same |

| JP5886806B2 (ja) * | 2013-09-17 | 2016-03-16 | キヤノン株式会社 | 固体撮像装置 |

| US10197455B2 (en) * | 2015-05-19 | 2019-02-05 | Advanced Micro Devices, Inc. | Thermal oscillator |

| JP6517664B2 (ja) * | 2015-10-28 | 2019-05-22 | 浜松ホトニクス株式会社 | 読み出し回路 |

| JP6906978B2 (ja) | 2016-02-25 | 2021-07-21 | 株式会社半導体エネルギー研究所 | 半導体装置、半導体ウェハ、および電子機器 |

| US10084976B2 (en) * | 2016-11-02 | 2018-09-25 | Raytheon Company | Flux rate unit cell focal plane array |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0682875A (ja) * | 1992-09-02 | 1994-03-25 | Fuji Film Micro Device Kk | 露光量計測装置 |

| JPH06164827A (ja) * | 1992-11-20 | 1994-06-10 | Fuji Xerox Co Ltd | イメ−ジセンサ用集積回路 |

| JP2000292258A (ja) * | 1999-04-09 | 2000-10-20 | Casio Comput Co Ltd | 光センサ駆動装置 |

| JP2000307140A (ja) * | 1999-04-23 | 2000-11-02 | Matsushita Electric Works Ltd | 太陽電池式照度センサ |

| JP2002286504A (ja) * | 2001-03-27 | 2002-10-03 | Citizen Watch Co Ltd | 光センサ回路およびこれを用いた光学式変位測長器 |

| JP2003133870A (ja) * | 2001-10-26 | 2003-05-09 | Fujitsu Ltd | 光センサ回路 |

| JP2005265444A (ja) * | 2004-03-16 | 2005-09-29 | Stanley Electric Co Ltd | 光検出装置及び光検出方法 |

| JP2006032438A (ja) * | 2004-07-12 | 2006-02-02 | Hamamatsu Photonics Kk | 光半導体集積回路装置 |

| JP2007005774A (ja) * | 2005-05-23 | 2007-01-11 | Semiconductor Energy Lab Co Ltd | 光電変換装置及びその作製方法 |

| JP2007119911A (ja) * | 2005-09-27 | 2007-05-17 | Semiconductor Energy Lab Co Ltd | 成膜装置、成膜方法、及び光電変換装置の作製方法 |

| JP2007318111A (ja) * | 2006-04-27 | 2007-12-06 | Semiconductor Energy Lab Co Ltd | 半導体装置及びそれを用いた電子機器 |

| JP2008042886A (ja) * | 2006-07-14 | 2008-02-21 | Rohm Co Ltd | アナログ/ディジタル変換器、照度センサ、照明装置、電子機器 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63144331A (ja) * | 1986-12-09 | 1988-06-16 | Minolta Camera Co Ltd | スチルカメラシステム |

| JPH06313840A (ja) | 1993-04-30 | 1994-11-08 | Fuji Film Micro Device Kk | 測光装置と測光方法 |

| EP0793380A2 (en) * | 1996-02-29 | 1997-09-03 | Kabushiki Kaisha Toshiba | A noise cancelling circuit for pixel signals and an image pickup device using the noise cancelling circuit |

-

2009

- 2009-05-15 US US12/467,001 patent/US8124922B2/en not_active Expired - Fee Related

- 2009-05-15 JP JP2009118196A patent/JP2010004025A/ja not_active Withdrawn

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0682875A (ja) * | 1992-09-02 | 1994-03-25 | Fuji Film Micro Device Kk | 露光量計測装置 |

| JPH06164827A (ja) * | 1992-11-20 | 1994-06-10 | Fuji Xerox Co Ltd | イメ−ジセンサ用集積回路 |

| JP2000292258A (ja) * | 1999-04-09 | 2000-10-20 | Casio Comput Co Ltd | 光センサ駆動装置 |

| JP2000307140A (ja) * | 1999-04-23 | 2000-11-02 | Matsushita Electric Works Ltd | 太陽電池式照度センサ |

| JP2002286504A (ja) * | 2001-03-27 | 2002-10-03 | Citizen Watch Co Ltd | 光センサ回路およびこれを用いた光学式変位測長器 |

| JP2003133870A (ja) * | 2001-10-26 | 2003-05-09 | Fujitsu Ltd | 光センサ回路 |

| JP2005265444A (ja) * | 2004-03-16 | 2005-09-29 | Stanley Electric Co Ltd | 光検出装置及び光検出方法 |

| JP2006032438A (ja) * | 2004-07-12 | 2006-02-02 | Hamamatsu Photonics Kk | 光半導体集積回路装置 |

| JP2007005774A (ja) * | 2005-05-23 | 2007-01-11 | Semiconductor Energy Lab Co Ltd | 光電変換装置及びその作製方法 |

| JP2007119911A (ja) * | 2005-09-27 | 2007-05-17 | Semiconductor Energy Lab Co Ltd | 成膜装置、成膜方法、及び光電変換装置の作製方法 |

| JP2007318111A (ja) * | 2006-04-27 | 2007-12-06 | Semiconductor Energy Lab Co Ltd | 半導体装置及びそれを用いた電子機器 |

| JP2008042886A (ja) * | 2006-07-14 | 2008-02-21 | Rohm Co Ltd | アナログ/ディジタル変換器、照度センサ、照明装置、電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8124922B2 (en) | 2012-02-28 |

| US20090289174A1 (en) | 2009-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8124922B2 (en) | Photoelectric conversion device including photoelectric conversion element and amplifier circuit having a thin film transistor | |

| JP5667273B2 (ja) | 光電変換装置 | |

| US8054596B2 (en) | Semiconductor device | |

| JP5222649B2 (ja) | 光電変換装置及びその光電変換装置を具備する電子機器 | |

| KR101401528B1 (ko) | 광전변환장치 및 그 광전변환장치를 구비하는 전자기기 | |

| US7531784B2 (en) | Semiconductor device and electronic appliance using the same | |

| JP5897647B2 (ja) | 光検出装置 | |

| JP4619318B2 (ja) | 光電変換装置 | |

| JP5371491B2 (ja) | 静電保護回路、半導体装置、及び半導体装置を具備する電子機器 | |

| JP4750070B2 (ja) | 半導体装置及びそれを用いた電子機器 | |

| JP5632944B2 (ja) | 測光装置、電子機器 | |

| US8207487B2 (en) | Photoelectric conversion device including charge/discharge circuit | |

| JP5461094B2 (ja) | 光電変換装置、及び当該光電変換装置を具備する電子機器 | |

| JP5132443B2 (ja) | 光電変換装置、並びに当該光電変換装置を具備するフォトic及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120321 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120321 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130625 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130807 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131022 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131106 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140212 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20140303 |