JP2009527816A - コンピュータへの入力を監視する方法および装置 - Google Patents

コンピュータへの入力を監視する方法および装置 Download PDFInfo

- Publication number

- JP2009527816A JP2009527816A JP2008555372A JP2008555372A JP2009527816A JP 2009527816 A JP2009527816 A JP 2009527816A JP 2008555372 A JP2008555372 A JP 2008555372A JP 2008555372 A JP2008555372 A JP 2008555372A JP 2009527816 A JP2009527816 A JP 2009527816A

- Authority

- JP

- Japan

- Prior art keywords

- computer

- instructions

- instruction

- processor

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/80—Architectures of general purpose stored program computers comprising an array of processing units with common control, e.g. single instruction multiple data processors

- G06F15/8007—Architectures of general purpose stored program computers comprising an array of processing units with common control, e.g. single instruction multiple data processors single instruction multiple data [SIMD] multiprocessors

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/32—Address formation of the next instruction, e.g. by incrementing the instruction counter

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/22—Microcontrol or microprogram arrangements

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30098—Register arrangements

- G06F9/3012—Organisation of register space, e.g. banked or distributed register file

- G06F9/30134—Register stacks; shift registers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/32—Address formation of the next instruction, e.g. by incrementing the instruction counter

- G06F9/322—Address formation of the next instruction, e.g. by incrementing the instruction counter for non-sequential address

- G06F9/325—Address formation of the next instruction, e.g. by incrementing the instruction counter for non-sequential address for loops, e.g. loop detection or loop counter

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3802—Instruction prefetching

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Multi Processors (AREA)

- Executing Machine-Instructions (AREA)

- Power Sources (AREA)

Applications Claiming Priority (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/355,513 US7904695B2 (en) | 2006-02-16 | 2006-02-16 | Asynchronous power saving computer |

| US11/355,495 US7904615B2 (en) | 2006-02-16 | 2006-02-16 | Asynchronous computer communication |

| US78826506P | 2006-03-31 | 2006-03-31 | |

| US79734506P | 2006-05-03 | 2006-05-03 | |

| US11/441,818 US7934075B2 (en) | 2006-02-16 | 2006-05-26 | Method and apparatus for monitoring inputs to an asyncrhonous, homogenous, reconfigurable computer array |

| US11/441,812 US7913069B2 (en) | 2006-02-16 | 2006-05-26 | Processor and method for executing a program loop within an instruction word |

| US11/441,784 US7752422B2 (en) | 2006-02-16 | 2006-05-26 | Execution of instructions directly from input source |

| PCT/US2007/004083 WO2007098026A2 (en) | 2006-02-16 | 2007-02-16 | Method and apparatus for monitoring inputs to a computer |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009527816A true JP2009527816A (ja) | 2009-07-30 |

| JP2009527816A5 JP2009527816A5 (enExample) | 2010-04-08 |

Family

ID=38066677

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008555353A Pending JP2009527808A (ja) | 2006-02-16 | 2007-02-16 | マイクロループコンピュータ命令 |

| JP2008555372A Pending JP2009527816A (ja) | 2006-02-16 | 2007-02-16 | コンピュータへの入力を監視する方法および装置 |

| JP2008555354A Pending JP2009527809A (ja) | 2006-02-16 | 2007-02-16 | 入力ソースから直接の命令の実行 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008555353A Pending JP2009527808A (ja) | 2006-02-16 | 2007-02-16 | マイクロループコンピュータ命令 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008555354A Pending JP2009527809A (ja) | 2006-02-16 | 2007-02-16 | 入力ソースから直接の命令の実行 |

Country Status (7)

| Country | Link |

|---|---|

| EP (3) | EP1821200B1 (enExample) |

| JP (3) | JP2009527808A (enExample) |

| KR (3) | KR20090017390A (enExample) |

| AT (2) | ATE495491T1 (enExample) |

| DE (1) | DE602007011841D1 (enExample) |

| TW (3) | TW200809609A (enExample) |

| WO (3) | WO2007098005A2 (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020220935A1 (zh) * | 2019-04-27 | 2020-11-05 | 中科寒武纪科技股份有限公司 | 运算装置 |

| US11841822B2 (en) * | 2019-04-27 | 2023-12-12 | Cambricon Technologies Corporation Limited | Fractal calculating device and method, integrated circuit and board card |

| US11960438B2 (en) | 2020-09-08 | 2024-04-16 | Rambus Inc. | Methods and circuits for streaming data to processing elements in stacked processor-plus-memory architecture |

| GB2609243B (en) * | 2021-07-26 | 2024-03-06 | Advanced Risc Mach Ltd | A data processing apparatus and method for transmitting triggered instructions between processing elements |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62180456A (ja) * | 1986-02-03 | 1987-08-07 | Nippon Telegr & Teleph Corp <Ntt> | 並列計算機の信号バイパス方式 |

| JPH03176757A (ja) * | 1989-11-21 | 1991-07-31 | Deutsche Itt Ind Gmbh | アレイプロセッサ |

| JP2000181878A (ja) * | 1998-12-15 | 2000-06-30 | Nec Corp | 共有メモリ型ベクトル処理システムとその制御方法及びベクトル処理の制御プログラムを格納する記憶媒体 |

| WO2002050700A2 (en) * | 2000-12-19 | 2002-06-27 | Picochip Designs Limited | Processor architecture |

| JP2004030277A (ja) * | 2002-06-26 | 2004-01-29 | Oki Electric Ind Co Ltd | ループ制御回路及びループ制御方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3757306A (en) * | 1971-08-31 | 1973-09-04 | Texas Instruments Inc | Computing systems cpu |

| EP0227319A3 (en) * | 1985-12-26 | 1989-11-02 | Analog Devices, Inc. | Instruction cache memory |

| US4868745A (en) * | 1986-05-30 | 1989-09-19 | Hewlett-Packard Company | Data processing system and method for the direct and indirect execution of uniformly structured object types |

| CA2019299C (en) * | 1989-06-22 | 2002-01-15 | Steven Frank | Multiprocessor system with multiple instruction sources |

| US5440749A (en) | 1989-08-03 | 1995-08-08 | Nanotronics Corporation | High performance, low cost microprocessor architecture |

| US5390304A (en) * | 1990-09-28 | 1995-02-14 | Texas Instruments, Incorporated | Method and apparatus for processing block instructions in a data processor |

| US5434989A (en) * | 1991-02-19 | 1995-07-18 | Matsushita Electric Industrial Co., Ltd. | Cache memory for efficient access with address selectors |

| JP3102594B2 (ja) * | 1991-02-19 | 2000-10-23 | 松下電器産業株式会社 | キャッシュメモリ装置 |

| JPH04367936A (ja) * | 1991-06-17 | 1992-12-21 | Mitsubishi Electric Corp | スーパースカラープロセッサ |

| JPH0863355A (ja) * | 1994-08-18 | 1996-03-08 | Mitsubishi Electric Corp | プログラム制御装置及びプログラム制御方法 |

| US5680597A (en) * | 1995-01-26 | 1997-10-21 | International Business Machines Corporation | System with flexible local control for modifying same instruction partially in different processor of a SIMD computer system to execute dissimilar sequences of instructions |

| US5727194A (en) | 1995-06-07 | 1998-03-10 | Hitachi America, Ltd. | Repeat-bit based, compact system and method for implementing zero-overhead loops |

| US5752259A (en) * | 1996-03-26 | 1998-05-12 | Advanced Micro Devices, Inc. | Instruction cache configured to provide instructions to a microprocessor having a clock cycle time less than a cache access time of said instruction cache |

| EP0992894A1 (en) * | 1998-10-06 | 2000-04-12 | Texas Instruments Inc. | Apparatus and method for loop execution |

| US6938253B2 (en) * | 2001-05-02 | 2005-08-30 | Portalplayer, Inc. | Multiprocessor communication system and method |

| WO2003019356A1 (en) | 2001-08-22 | 2003-03-06 | Adelante Technologies B.V. | Pipelined processor and instruction loop execution method |

| JP4610218B2 (ja) | 2004-03-30 | 2011-01-12 | ルネサスエレクトロニクス株式会社 | 情報処理装置 |

-

2007

- 2007-02-15 AT AT07250649T patent/ATE495491T1/de not_active IP Right Cessation

- 2007-02-15 AT AT07250646T patent/ATE512400T1/de not_active IP Right Cessation

- 2007-02-15 EP EP07250646A patent/EP1821200B1/en not_active Not-in-force

- 2007-02-15 DE DE602007011841T patent/DE602007011841D1/de active Active

- 2007-02-15 EP EP07250649A patent/EP1821202B1/en not_active Not-in-force

- 2007-02-15 EP EP07250614A patent/EP1821199B1/en not_active Not-in-force

- 2007-02-16 TW TW096106397A patent/TW200809609A/zh unknown

- 2007-02-16 TW TW096106394A patent/TW200809613A/zh unknown

- 2007-02-16 KR KR1020077009923A patent/KR20090017390A/ko not_active Withdrawn

- 2007-02-16 JP JP2008555353A patent/JP2009527808A/ja active Pending

- 2007-02-16 WO PCT/US2007/004029 patent/WO2007098005A2/en not_active Ceased

- 2007-02-16 KR KR1020077009925A patent/KR20090016645A/ko not_active Withdrawn

- 2007-02-16 JP JP2008555372A patent/JP2009527816A/ja active Pending

- 2007-02-16 WO PCT/US2007/004030 patent/WO2007098006A2/en not_active Ceased

- 2007-02-16 JP JP2008555354A patent/JP2009527809A/ja active Pending

- 2007-02-16 KR KR1020077009924A patent/KR20090004394A/ko not_active Withdrawn

- 2007-02-16 WO PCT/US2007/004083 patent/WO2007098026A2/en not_active Ceased

- 2007-02-16 TW TW096106396A patent/TW200809531A/zh unknown

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62180456A (ja) * | 1986-02-03 | 1987-08-07 | Nippon Telegr & Teleph Corp <Ntt> | 並列計算機の信号バイパス方式 |

| JPH03176757A (ja) * | 1989-11-21 | 1991-07-31 | Deutsche Itt Ind Gmbh | アレイプロセッサ |

| JP2000181878A (ja) * | 1998-12-15 | 2000-06-30 | Nec Corp | 共有メモリ型ベクトル処理システムとその制御方法及びベクトル処理の制御プログラムを格納する記憶媒体 |

| WO2002050700A2 (en) * | 2000-12-19 | 2002-06-27 | Picochip Designs Limited | Processor architecture |

| JP2004525440A (ja) * | 2000-12-19 | 2004-08-19 | ピコチップ デザインズ リミテッド | プロセッサアーキテクチャ |

| JP2004030277A (ja) * | 2002-06-26 | 2004-01-29 | Oki Electric Ind Co Ltd | ループ制御回路及びループ制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1821199A1 (en) | 2007-08-22 |

| ATE495491T1 (de) | 2011-01-15 |

| ATE512400T1 (de) | 2011-06-15 |

| TW200809531A (en) | 2008-02-16 |

| WO2007098026A2 (en) | 2007-08-30 |

| WO2007098005A2 (en) | 2007-08-30 |

| WO2007098006A2 (en) | 2007-08-30 |

| TW200809609A (en) | 2008-02-16 |

| WO2007098006A3 (en) | 2009-01-08 |

| KR20090016645A (ko) | 2009-02-17 |

| EP1821202B1 (en) | 2011-01-12 |

| EP1821200B1 (en) | 2011-06-08 |

| WO2007098005A3 (en) | 2008-10-09 |

| KR20090004394A (ko) | 2009-01-12 |

| TW200809613A (en) | 2008-02-16 |

| EP1821200A2 (en) | 2007-08-22 |

| WO2007098026A3 (en) | 2009-04-09 |

| JP2009527809A (ja) | 2009-07-30 |

| EP1821199B1 (en) | 2012-07-04 |

| JP2009527808A (ja) | 2009-07-30 |

| KR20090017390A (ko) | 2009-02-18 |

| EP1821200A3 (en) | 2008-09-24 |

| DE602007011841D1 (de) | 2011-02-24 |

| EP1821202A1 (en) | 2007-08-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101563679A (zh) | 用于监控计算机的输入的方法和装置 | |

| EP1990718A1 (en) | Method and apparatus for loading data and instructions into a computer | |

| US20100281238A1 (en) | Execution of instructions directly from input source | |

| JPH06139189A (ja) | 共有バス調停機構 | |

| EP1821211A2 (en) | Cooperative multitasking method in a multiprocessor system | |

| US8468323B2 (en) | Clockless computer using a pulse generator that is triggered by an event other than a read or write instruction in place of a clock | |

| CN101410823A (zh) | 异步计算机通信 | |

| US7966481B2 (en) | Computer system and method for executing port communications without interrupting the receiving computer | |

| JP2009527816A (ja) | コンピュータへの入力を監視する方法および装置 | |

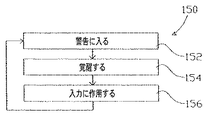

| US7934075B2 (en) | Method and apparatus for monitoring inputs to an asyncrhonous, homogenous, reconfigurable computer array | |

| US20090300334A1 (en) | Method and Apparatus for Loading Data and Instructions Into a Computer | |

| JP2009527810A (ja) | 非同期コンピュータ通信 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110930 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111227 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120110 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120131 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120207 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120229 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120307 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120601 |