JP2009158810A - 化学的機械的研磨用スラリーおよび半導体装置の製造方法 - Google Patents

化学的機械的研磨用スラリーおよび半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2009158810A JP2009158810A JP2007337248A JP2007337248A JP2009158810A JP 2009158810 A JP2009158810 A JP 2009158810A JP 2007337248 A JP2007337248 A JP 2007337248A JP 2007337248 A JP2007337248 A JP 2007337248A JP 2009158810 A JP2009158810 A JP 2009158810A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- cmp

- polishing

- slurry

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/32115—Planarisation

- H01L21/3212—Planarisation by chemical mechanical polishing [CMP]

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09G—POLISHING COMPOSITIONS; SKI WAXES

- C09G1/00—Polishing compositions

- C09G1/02—Polishing compositions containing abrasives or grinding agents

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

- H01L21/31053—Planarisation of the insulating layers involving a dielectric removal step

Abstract

【解決手段】本発明の一態様のCMP用スラリーは、重量平均分子量が100万以上1000万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群より選ばれる一種または二種以上からなる水溶性高分子と、β-シクロデキストリンと、コロイダルシリカと、水を含有することを特徴とする。また、本発明の一態様の半導体装置の製造方法は、タッチアップ研磨工程に本発明の一態様のCMPスラリーを用いることを特徴とする。

【選択図】 なし

Description

上記問題点は、以下に詳述する本発明の一態様により解決することができる。

従って、以下に、まず、第1のCMP用スラリーの組成の一例の詳細を説明し、続いて、第2のCMP用スラリー(本発明の一態様のCMP用スラリー)の必須成分の詳細について説明する。

第1のCMP用スラリーは、CuまたはCu合金からなる配線材料堆積膜の不要部分を除去する第1のCMP工程で使用するに適したもので、水と、Cu水不溶性錯体形成剤と、Cu水可溶性錯体形成剤と、酸化剤、界面活性剤、コロイダルシリカ、およびpH調整剤が含まれる。

Cuなどの金属と水に不溶性または難溶性の錯体を形成する錯体形成剤としては、例えば、少なくとも1個のN原子を含む複素六員環、複素五員環からなるヘテロ環化合物が挙げられる。より具体的には、キナルジン酸、キノリン酸、ベンゾトリアゾール、ベンゾイミダゾール、7−ヒドリキシ−5−メチル−1,3,4−トリアザインドリジン、ニコチン酸、およびピコリン酸などを挙げることができる。このCu水不溶性錯体形成剤の含有量は、CMP用スラリーの総量の0.0005質量%以上2.0質量%以下が好ましい。このCu水不溶性錯体形成剤の含有量が0.0005質量%以上2.0質量%以下であれば、研磨される配線層表面のディッシングが抑えられるとともに、良好なCu研磨速度を得ることができる。このCu水不溶性錯体形成剤の含有量は、より好ましくは、第1のCMP用スラリーの総量の0.0075質量%以上1.5質量%以下である。

Cuなどの金属と水に可溶性の錯体を形成する錯体形成剤は、研磨加速剤の役割を果たし、例えば、例えば、ギ酸、コハク酸、乳酸、酢酸、酒石酸、フマル酸、グリコール酸、フタル酸、マレイン酸、シュウ酸、クエン酸、リンゴ酸、マロン酸、およびグルタル酸などが挙げられる。さらに、アンモニア、エチレンジアミン、およびTMAH(テトラメチルアンモニウムハイドロオキサイド)などの塩基性塩を用いてもよい。また、中性アミノ酸のグリシン、アラニンなどを添加してもよい。このCu水可溶性錯体形成剤の含有量は、第1のCMP用スラリーの総量の0.0005質量%以上2.0質量%以下が好ましい。この含有量が0.0005質量%以上2.0質量%以下であれば、大きな速度でCuを研磨することができるとともに、研磨による配線層表面のディッシングやコロージョンを抑制することができる。このCu水可溶性錯体形成剤のより好ましい含有量は、CuあるいはCu合金における組成の違いにより異なるが、第1のCMP用スラリーの総量の0.0075質量%以上1.5質量%以下である。

酸化剤としては、例えば、過硫酸塩、過酸化水素、等が挙げられる。過硫酸塩としては、過硫酸アンモニウム、過硫酸カリウムなどが挙げられる。好ましい濃度は、第1のCMP用スラリーの総量の0.001〜2質量%であり、より好ましくは0.01〜2質量%であり、さらに好ましくは0.05〜1.5質量%である。酸化剤をこの範囲の配合量とすることにより、Cu又はCu合金膜とバリアメタル膜に対する研磨速度を適度な範囲に設定することができる。

非イオン性界面活性剤としては、例えば、ポリビニルピロリドン(PVP)、アセチレングリコール、それらのエチレンオキサイド付加物、アセチレンアルコール、シリコーン系界面活性剤、ポリビニルアルコール、ポリビニルメチルエーテル、ヒドロキシエチルセルロースなどを用いてもよい。さらに、アニオン界面活性剤またはカチオン界面活性剤を含んでもよい。アニオン界面活性剤としては、ドデシルベンゼンスルホン酸塩、高分子のポリアクリル酸塩などが挙げられ、カチオン界面活性剤としては、例えば、脂肪族アミン塩および脂肪族アンモニウム塩などが挙げられる。上述したような界面活性剤は、単独でも2種以上を組み合わせて用いてもよい。この界面活性剤の含有量は、第1のCMP用スラリーの総量の0.001質量%以上0.5質量%以下が好ましい。この範囲内に設定することにより配線層表面の研磨によるディッシングを十分に抑制することができる。この界面活性剤のより好ましい含有量は、第1のCMP用スラリーの総量の0.05質量%以上0.3質量%以下である。

コロイダルシリカは、例えばSi(OC2H5)4、Si(sec−OC4H9)4、Si(OCH3)4、およびSi(OC4H9)4のようなシリコンアルコキシド化合物をゾルゲル法により加水分解することにより得ることができる。コロイダルシリカの粒子径は、好ましくは5〜500nmであり、より好ましくは10〜100nmであり、更に好ましくは20〜50nmである。この範囲の平均分散粒径のコロイダルシリカを使用することにより、適度な研磨速度を達成することができる。

第1のCMP用スラリーのpHは、好ましくは7を超え13以下であり、8〜11であることがより好ましい。この範囲のpHとすることにより、適度な研磨速度を達成することができる。pH調整剤としては、例えば、有機塩基、無機塩基、無機酸が挙げられる。有機塩基としては、例えば、テトラメチルアンモニウムヒドロキシド(TMAH)、トリエチルアミン等が挙げられる。無機塩基としては、例えば、アンモニア、水酸化カリウム、水酸化ナトリウム等が挙げられる。無機酸としては、例えば、硝酸、硫酸等が挙げられる。

本発明の一態様の半導体装置の製造方法において、バリアメタル膜、CuまたはCu合金膜、第2の絶縁膜を除去する第2のCMP工程で使用する第2のCMP用スラリーは、先に述べたように、前記第1のCMP用スラリーに用いられている研磨砥粒等の基本的要素材料は共通して含有し、それ以外の必須組成分として、重量平均分子量が100万以上1000万以下の特定の水溶性高分子と、β−シクロデキストリンを含む。なお、この第2のCMP用スラリーにおいて、前記第1のCMP用スラリーの成分を同様に含有する場合のそれらの含有量は、第1のCMP用スラリーでの含有量とほぼ同様であって良い。また、好適なpH値の範囲も同様であり、第1のCMP用スラリーの場合と同様のpH調整剤を配合してアルカリ性に設定されることが好ましい。

水溶性高分子としては、例えば、ポリアクリル酸、ポリアクリル酸塩、ポリメタクリル酸、ポリメタクリル酸塩、アクリル酸−メタクリル酸ポリマー、およびアクリル酸−メタクリル酸ポリマーの塩などが挙げられる。本発明の一態様のCMP用スラリーに用いられる水溶性高分子は、前記の群から選ばれる一種を単独で用いても良いし、二種以上を混合して用いても良く、その重量平均分子量が100万以上1000万以下であることが重要である。100万以上とすることにより、被研磨面に生じやすいファングの抑制効果が発揮され、スクラッチ数の低減効果も得ることができ、配線層表面のティッシングも抑制することができる。また、重量平均分子量を1000万以下とすることにより、第2のCMP用スラリー中のコロイダルシリカの凝集が防止され、それに伴って、被研磨面のスクラッチ数を減少させることができる。また、重量平均分子量を100万以上1000万以下とすることにより、第2のCMP用スラリーの粘度を、コロイダルシリカの凝集を防止しつつ、コロイダルシリカを均一に保持可能な範囲に調整可能であり、かつ、研磨テーブルに滴下可能な範囲に抑えることができる、など取り扱いを良好とすることができる。また、上記水溶性高分子は、いわば、大きなアニオン群であるため、pH配合剤が配合された場合は、その周囲にpH調整剤由来のカチオンを引きつけ、このカチオン群がさらにコロイダルシリカを引きつけることにより、研磨砥粒であるコロイダルシリカの均一保持が可能になり、良好な研磨特性が得られるものと考えられる。

シクロデキストリンは、α、β、γ型の3種類のうちβ−シクロデキストリンが用いられる。このβ−シクロデキストリンは、SiOC膜などの低誘電体材料への作用が特に強く、疎水性の低誘電体材料膜に直接または第2のCMP用スラリー中の他の成分との相互作用を通じて接触し、膜表面の疎水性の度合いを低減して親水性方向にシフトさせ、ひいてはファングの抑制効果を発揮するものと考えられる。また、このβ−シクロデキストリンはコロイダルシリカに接触して、コロイダルシリカを電気的に中性化し、コロイダルシリカの凝集防止に寄与するものと推定される。

半導体装置の製造方法においては、前記第2のCMP工程の後に、連続して洗浄工程を設けることが好ましい。その洗浄工程に用いる洗浄液としては、クエン酸、シュウ酸ベースの酸性液や、TMAHのようなアルカリ性の溶液などCu錯体、Cu酸化物を溶解するものを用いることができる。

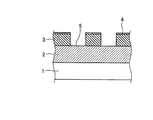

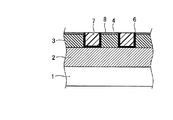

本発明の一態様の半導体装置の製造方法は、先に述べたように、半導体基板上に第1の絶縁膜を形成する第1の絶縁膜形成工程と、前記第1の絶縁膜上に該第1の絶縁膜より誘電率が高い第2の絶縁膜を形成する第2の絶縁膜形成工程と、前記第2の絶縁膜から前記第1の絶縁膜にかけて配線用の凹部を形成する凹部形成工程と、前記凹部の内面と前記第2の絶縁膜の表面にバリアメタル膜を形成するバリアメタル膜形成工程と、前記バリアメタル膜で覆われた凹部を埋め込むように銅または銅合金を前記バリアメタル膜上に堆積して配線材料堆積層を形成する配線材料堆積工程と、前記配線材料堆積層を前記バリアメタル膜が露出するまで化学的機械的研磨により平坦に研磨して除去する第1の化学的機械的研磨工程と、前記第1の化学的機械的研磨工程の後、前記第1の絶縁膜が露出するまでバリアメタル膜と第2の絶縁膜を化学的機械的研磨により平坦に研磨して除去する第2の化学的機械的研磨工程とを有し、前記第2の化学的機械的研磨工程における研磨を、前記本発明の一態様のCMP用スラリーを用いて行うことを特徴とする。

以下に図面を用いて、上記第1のCMP用スラリーおよび第2のCMP用スラリーを用いて行われる半導体装置の製造方法を説明する。

第1のCMP工程に用いる第1のCMP用スラリーを、下記表1に示す成分及び組成割合に従って、調製し、この第1のCMP用スラリーを、実施例1〜5における第1のCMP用スラリーとして共通して用いた。

第1のCMP工程に用いる第1のCMP用スラリーは、実施例1〜5と同様に、上記表1に示す成分及び組成割合に従って調製したものを共通して用いた。

以下、上記第1のCMP工程と第2のCMP工程を同一の研磨テーブルを用いて連続して行った場合を連続研磨処理と記し、上記第1のCMP工程と第2のCMP工程とを別々の研磨テーブルを用いて行った場合を不連続研磨処理と記す。

各例のCMP用スラリーの研磨特性の評価は、配線幅0.06μm、配線間隔0.06μm(配線被覆率50%)の配線パターンを形成した各基板サンプルについて行った。ファングの大きさ(幅寸法(nm))は、配線パターンに隣接したフィールド領域における低誘電率絶縁膜(第1の絶縁膜)の端部をAFM(Atomic Force Microscope:原子間力顕微鏡)で評価した。発生スクラッチ数は、300mm径の半導体基板の研磨面を全面に亘って日立ハイテクノロジー社製の欠陥評価装置(商品名「IS2700」)により評価した。また、SiO2膜(第2の絶縁膜)の研磨速度は、別途、半導体基板上の全面にSiO2膜を形成し、このSiO2膜に対して研磨処理を行うことにより、測定した。SiO2膜の研磨速度については、不連続研磨処理と、連続研磨処理でのそれぞれにおいて、測定した。それらの測定結果を、表2および表3に併記した。

上記実施例2に対して、実施例3では、ポリアクリル酸の含有量は0.1質量%と同一であるが、その重量平均分子量(mw)が1000万とより高分子量のポリアクリル酸を使用している点が異なっている。この重量平均分子量の増加によって、ファング抑制効果、スクラッチ数の低減効果、およびSiO2研磨速度の向上効果の全てにおいて、向上が認められ、特にスクラッチ数の低減効果における改善が顕著となっている。

上記実施例3に対して、実施例4では、β−シクロデキストリンの含有量が0.01質量%に低減している点が異なっている。このβ−シクロデキストリンの含有量の減少によって、ファング抑制効果、スクラッチ数の低減効果、およびSiO2研磨速度の向上効果の全てが実施例3の場合より低減しており、特にスクラッチ数の低減効果が弱まる傾向となっている。

実施例5は、上記実施例2に対して、キナルジン酸が0.05質量%添加されている点のみが異なっている。このキナルジン酸は有機酸であり、余剰のCu膜を研磨する第1のCMP用スラリーに配合されているCu水不溶性錯体形成剤である。この有機酸がSiO2膜に接触すると、SiO2に吸着し、SiO2膜の研磨摩擦が低下すると推定されている。実施例2の各評価結果と比べると、スクラッチ数の低減効果以外の評価結果が低下しており、特にSiO2膜の研磨速度が低下傾向となっていることが分かる。しかし、その低下傾向もごく小さな範囲にあることから、本発明の一態様のCMP用スラリーは、有機酸の影響を抑制する効果を有することが確認できる。

比較例2では、ポリアクリル酸の含有がなく、β−シクロデキストリンが0.1質量%含有されている。このβ−シクロデキストリンの含有によって、ファング抑制効果およびスクラッチ数の低減効果が幾分か良好となる傾向にあるが、十分なものでなく、SiO2膜の研磨速度の向上効果はほとんど得られない。

比較例3では、重量平均分子量が1000万のポリアクリル酸が0.1質量%含有されているが、このポリアクリル酸の含有によって、β−シクロデキストリンのみの含有の場合と同様に、ファング抑制効果およびスクラッチ数の低減効果が幾分か良好となる傾向にあるが、十分なものでなく、SiO2膜の研磨速度の向上効果は得られない。

比較例4では、ポリアクリル酸およびβ−シクロデキストリンが共に含有されているが、ポリアクリル酸の重量平均分子量が10万と大変小さい。その結果、全ての評価結果が低く、特にスクラッチ数が増加傾向となることが分かる。

2 絶縁層

3 第1の絶縁膜

4 第2の絶縁膜

5 凹部(配線溝)

6 バリアメタル膜

7 下層配線層

8 配線材料堆積層

101 Cu膜を堆積させた半導体基板

102 研磨布

103 ターンテーブル

104 トップリング

105 第1の研磨液供給ノズル

106 純水供給ノズル

107 ダイヤモンドドレッサー

108 第2の研磨液供給ノズル

109 第3の研磨液供給ノズル

Claims (5)

- 重量平均分子量が100万以上1000万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群より選ばれる少なくとも一種の水溶性高分子と、β−シクロデキストリンと、コロイダルシリカと、水とを含有することを特徴とする化学的機械的研磨用スラリー。

- 前記水溶性高分子の含有量が0.0001〜0.5質量%であり、前記β−シクロデキストリンの含有量が0.001〜0.5重量%であることを特徴とする化学的機械的研磨用スラリー。

- pH調整剤を含有し、アルカリ性であることを特徴とする請求項1または2に記載の化学的機械的研磨用スラリー。

- 半導体基板上に第1の絶縁膜を形成する第1の絶縁膜形成工程と、

前記第1の絶縁膜上に該第1の絶縁膜より誘電率が高い第2の絶縁膜を形成する第2の絶縁膜形成工程と、

前記第2の絶縁膜から第1の絶縁膜にかけて配線用の凹部を形成する凹部形成工程と、

前記凹部の内面と前記第2の絶縁膜の表面にバリアメタル膜を形成するバリアメタル膜形成工程と、

前記バリアメタル膜で覆われた凹部を埋め込むように銅または銅合金を前記バリアメタル膜上に堆積して配線材料堆積層を形成する配線材料堆積工程と、

前記配線材料堆積層を前記バリアメタル膜が露出するまで化学的機械的研磨により平坦に研磨して除去する第1の化学的機械的研磨工程と、

前記第1の化学的機械的研磨工程の後、前記第1の絶縁膜が露出するまでバリアメタル膜と第2の絶縁膜を化学的機械的研磨により平坦に研磨して除去する第2の化学的機械的研磨工程とを有し、

前記第2の化学的機械的研磨工程における研磨を、請求項1に記載の化学的機械的研磨用スラリーを用いて行うことを特徴とする半導体装置の製造方法。 - 前記第1の化学的機械的研磨工程と第2の化学的機械的研磨工程とを、同一研磨テーブル上で連続的に行うことを特徴とする請求項4に記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007337248A JP2009158810A (ja) | 2007-12-27 | 2007-12-27 | 化学的機械的研磨用スラリーおよび半導体装置の製造方法 |

| US12/339,435 US20090176372A1 (en) | 2007-12-27 | 2008-12-19 | Chemical mechanical polishing slurry and semiconductor device manufacturing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007337248A JP2009158810A (ja) | 2007-12-27 | 2007-12-27 | 化学的機械的研磨用スラリーおよび半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009158810A true JP2009158810A (ja) | 2009-07-16 |

| JP2009158810A5 JP2009158810A5 (ja) | 2010-04-15 |

Family

ID=40844923

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007337248A Pending JP2009158810A (ja) | 2007-12-27 | 2007-12-27 | 化学的機械的研磨用スラリーおよび半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20090176372A1 (ja) |

| JP (1) | JP2009158810A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011103410A (ja) * | 2009-11-11 | 2011-05-26 | Kuraray Co Ltd | 化学的機械的研磨用スラリー |

| WO2012053660A1 (ja) * | 2010-10-21 | 2012-04-26 | 株式会社Moresco | ガラス基板研磨用潤滑組成物及び研磨スラリー |

| JP2013055342A (ja) * | 2009-08-19 | 2013-03-21 | Hitachi Chemical Co Ltd | Cmp研磨液及び研磨方法 |

| JP2013094906A (ja) * | 2011-11-01 | 2013-05-20 | Kao Corp | 研磨液組成物 |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5148948B2 (ja) * | 2007-08-23 | 2013-02-20 | Sumco Techxiv株式会社 | 研磨用スラリーのリサイクル方法 |

| MY155533A (en) * | 2008-06-11 | 2015-10-30 | Shinetsu Chemical Co | Polishing agent for synthetic quartz glass substrate |

| WO2011058952A1 (ja) * | 2009-11-11 | 2011-05-19 | 株式会社クラレ | 化学的機械的研磨用スラリー並びにそれを用いる基板の研磨方法 |

| JP5251861B2 (ja) * | 2009-12-28 | 2013-07-31 | 信越化学工業株式会社 | 合成石英ガラス基板の製造方法 |

| US10103331B2 (en) * | 2010-02-05 | 2018-10-16 | Industry-University Cooperation Foundation Hanyang University | Slurry for polishing phase-change materials and method for producing a phase-change device using same |

| KR101396232B1 (ko) * | 2010-02-05 | 2014-05-19 | 한양대학교 산학협력단 | 상변화 물질 연마용 슬러리 및 이를 이용한 상변화 소자 제조 방법 |

| US20140154884A1 (en) * | 2011-05-24 | 2014-06-05 | Kuraray Co., Ltd. | Erosion inhibitor for chemical mechanical polishing, slurry for chemical mechanical polishing, and chemical mechanical polishing method |

| US8703004B2 (en) * | 2011-11-14 | 2014-04-22 | Kabushiki Kaisha Toshiba | Method for chemical planarization and chemical planarization apparatus |

| US9443796B2 (en) * | 2013-03-15 | 2016-09-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Air trench in packages incorporating hybrid bonding |

| US9388328B2 (en) * | 2013-08-23 | 2016-07-12 | Diamond Innovations, Inc. | Lapping slurry having a cationic surfactant |

| TWI673357B (zh) * | 2016-12-14 | 2019-10-01 | 美商卡博特微電子公司 | 自化學機械平坦化基板移除殘留物之組合物及方法 |

| CN107189695A (zh) * | 2017-04-15 | 2017-09-22 | 浙江晶圣美纳米科技有限公司 | 一种可有效应用于不锈钢衬底化学机械抛光工艺的抛光液 |

| KR20220133287A (ko) * | 2020-02-13 | 2022-10-04 | 후지필름 일렉트로닉 머티리얼스 유.에스.에이., 아이엔씨. | 연마 조성물 및 이의 사용 방법 |

| TW202330819A (zh) * | 2021-09-23 | 2023-08-01 | 美商Cmc材料股份有限公司 | 用於介電質化學機械研磨之包含高分子量聚合物之基於二氧化矽之漿料組合物 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2003038883A1 (fr) * | 2001-10-31 | 2003-05-08 | Hitachi Chemical Co., Ltd. | Fluide et procede de polissage |

| JP2006066874A (ja) * | 2004-07-27 | 2006-03-09 | Asahi Denka Kogyo Kk | Cmp用研磨組成物および研磨方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2330747C (en) * | 1998-05-18 | 2010-07-27 | Mallinckrodt Inc. | Silicate-containing alkaline compositions for cleaning microelectronic substrates |

| JP2004247605A (ja) * | 2003-02-14 | 2004-09-02 | Toshiba Corp | Cmp用スラリーおよび半導体装置の製造方法 |

| US20050205835A1 (en) * | 2004-03-19 | 2005-09-22 | Tamboli Dnyanesh C | Alkaline post-chemical mechanical planarization cleaning compositions |

| US20060046465A1 (en) * | 2004-08-27 | 2006-03-02 | Dongbuanam Semiconductor Inc. | Method for manufacturing a semiconductor device |

| KR100645957B1 (ko) * | 2004-10-26 | 2006-11-14 | 삼성코닝 주식회사 | Cmp용 수성 슬러리 조성물 |

-

2007

- 2007-12-27 JP JP2007337248A patent/JP2009158810A/ja active Pending

-

2008

- 2008-12-19 US US12/339,435 patent/US20090176372A1/en not_active Abandoned

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2003038883A1 (fr) * | 2001-10-31 | 2003-05-08 | Hitachi Chemical Co., Ltd. | Fluide et procede de polissage |

| JP2006066874A (ja) * | 2004-07-27 | 2006-03-09 | Asahi Denka Kogyo Kk | Cmp用研磨組成物および研磨方法 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013055342A (ja) * | 2009-08-19 | 2013-03-21 | Hitachi Chemical Co Ltd | Cmp研磨液及び研磨方法 |

| US8883031B2 (en) | 2009-08-19 | 2014-11-11 | Hitachi Chemical Company, Ltd. | CMP polishing liquid and polishing method |

| US9318346B2 (en) | 2009-08-19 | 2016-04-19 | Hitachi Chemical Company, Ltd. | CMP polishing liquid and polishing method |

| JP2011103410A (ja) * | 2009-11-11 | 2011-05-26 | Kuraray Co Ltd | 化学的機械的研磨用スラリー |

| WO2012053660A1 (ja) * | 2010-10-21 | 2012-04-26 | 株式会社Moresco | ガラス基板研磨用潤滑組成物及び研磨スラリー |

| JP2013094906A (ja) * | 2011-11-01 | 2013-05-20 | Kao Corp | 研磨液組成物 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090176372A1 (en) | 2009-07-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2009158810A (ja) | 化学的機械的研磨用スラリーおよび半導体装置の製造方法 | |

| JP5381701B2 (ja) | 金属用研磨液及び研磨方法 | |

| JP4143872B2 (ja) | 化学機械研磨用水系分散体および半導体装置の化学機械研磨方法 | |

| KR100510977B1 (ko) | 화학기계연마용 연마제 및 기판의 연마법 | |

| JP4776269B2 (ja) | 金属膜cmp用スラリー、および半導体装置の製造方法 | |

| TWI525680B (zh) | 金屬膜用硏磨液以及硏磨方法 | |

| JP4798134B2 (ja) | Cmp用研磨液及び研磨方法 | |

| JP5329786B2 (ja) | 研磨液および半導体装置の製造方法 | |

| JP2008004621A (ja) | Cu膜CMP用スラリー、研磨方法および半導体装置の製造方法 | |

| JP4130614B2 (ja) | 半導体装置の製造方法 | |

| JP6327326B2 (ja) | 金属用研磨液及び研磨方法 | |

| JP2007157841A (ja) | Cmp用水系分散液、研磨方法、および半導体装置の製造方法 | |

| TW201412907A (zh) | Cmp用研磨液、儲存液及研磨方法 | |

| TWI399428B (zh) | Cmp研磨液以及使用此cmp研磨液的基板研磨方法 | |

| JP5319887B2 (ja) | 研磨用スラリー | |

| JP2005064285A (ja) | Cmp用研磨液及び研磨方法 | |

| JP3780767B2 (ja) | 金属用研磨液及び基板の研磨方法 | |

| JP4618987B2 (ja) | 研磨液及び研磨方法 | |

| JP2006128552A (ja) | Cmp用研磨液及び研磨方法 | |

| JP2004123931A (ja) | 研磨液及び研磨方法 | |

| JP2004363141A (ja) | 金属用研磨液及び研磨方法 | |

| JP2009259950A (ja) | Cmp用研磨液及びこれを用いた基板の研磨方法 | |

| JP2004023068A (ja) | 銅系金属用研磨スラリーおよび半導体装置の製造方法 | |

| JP2008118112A (ja) | Cmp用研磨液及び基板の研磨方法 | |

| JP2004123930A (ja) | 研磨液及び研磨方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120410 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120412 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120807 |