JP2008507137A - 低誘電体のエッチング - Google Patents

低誘電体のエッチング Download PDFInfo

- Publication number

- JP2008507137A JP2008507137A JP2007521623A JP2007521623A JP2008507137A JP 2008507137 A JP2008507137 A JP 2008507137A JP 2007521623 A JP2007521623 A JP 2007521623A JP 2007521623 A JP2007521623 A JP 2007521623A JP 2008507137 A JP2008507137 A JP 2008507137A

- Authority

- JP

- Japan

- Prior art keywords

- etching

- flow rate

- shape

- dielectric layer

- mask

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000005530 etching Methods 0.000 title claims abstract description 104

- 238000000034 method Methods 0.000 claims abstract description 71

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 63

- 239000007789 gas Substances 0.000 claims description 34

- 229920000642 polymer Polymers 0.000 claims description 12

- 239000011368 organic material Substances 0.000 claims description 10

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 6

- 239000004065 semiconductor Substances 0.000 claims description 4

- 229910052786 argon Inorganic materials 0.000 claims description 3

- 238000000151 deposition Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 30

- 239000000463 material Substances 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 4

- 239000012044 organic layer Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 3

- 239000005441 aurora Substances 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000010432 diamond Substances 0.000 description 2

- 238000006467 substitution reaction Methods 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 244000132059 Carica parviflora Species 0.000 description 1

- 235000014653 Carica parviflora Nutrition 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 150000001721 carbon Chemical group 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000004549 pulsed laser deposition Methods 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 238000005019 vapor deposition process Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Plasma & Fusion (AREA)

- Drying Of Semiconductors (AREA)

Abstract

【解決手段】フォトレジストマスクの下方の誘電体層をエッチングするための方法が提供されている。フォトレジストマスクの下方に配置された誘電体層を有するウエハが、エッチングチャンバ内に供給される。CF4およびH2を備えるエッチングガスが、エッチングチャンバに供給される。CF4は流速を有し、H2は流速を有し、H2の流速はCF4の流速よりも大きい。エッチングガスから、プラズマが形成される。エッチングガスから形成されたプラズマを用いて、エッチングマスクを通して誘電体層に形状がエッチングされる。

【選択図】図1

【選択図】図1

Description

本発明は、半導体素子の形成に関する。

半導体ウエハの処理では、周知のパターニングおよびエッチング処理を用いて、ウエハ内に半導体素子の形状が規定される。これらの処理では、フォトレジスト(PR)材料が、ウエハに蒸着され、次いで、レチクルによってフィルタリングされた光に露出される。レチクルとは、一般に、光がレチクルを通して伝わることを防ぐ典型的な形状の配列を有するようパターニングされたガラス板である。

レチクルを通過した後、光は、フォトレジスト材料の表面に当たる。光は、現像剤がフォトレジスト材料の一部を除去できるように、フォトレジスト材料の化学組成を変化させる。ポジ型フォトレジスト材料の場合には、露光された領域が除去され、ネガ型フォトレジスト材料の場合には、露光されていない領域が除去される。その後、もはやフォトレジスト材料によって保護されていないことよってウエハ内の所望の形状を規定する領域から、下層の材料を除去するために、ウエハがエッチングされる。

様々な世代のフォトレジストが知られている。素子のサイズを小さくして素子の密度を高くするためには、193nmフォトレジスト、157nmフォトレジスト、および、より小さい世代のフォトレジストが、望ましい。193nmおよび157nmフォトレジストは、前の世代のフォトレジストよりも柔らかく、むしろ、ポリマ、特に、低誘電率ポリマに似ており、そのため、フォトレジストに対する低誘電体のエッチング選択比が低くなる。

上述の目的を実現するために、本発明の目的に従って、フォトレジストマスクの下方の誘電体層をエッチングするための方法が提供されている。フォトレジストマスクの下方に配置された誘電体層を有するウエハが、エッチングチャンバ内に供給される。CF4およびH2を備えるエッチングガスが、エッチングチャンバに供給される。CF4は流速を有し、H2は流速を有し、H2の流速はCF4の流速よりも大きい。エッチングガスから、プラズマが形成される。エッチングガスから形成されたプラズマを用いて、エッチングマスクを通して誘電体層に形状がエッチングされる。

本発明の別の実施形態では、有機材料マスクの下方のエッチング層をエッチングするための方法が提供されている。有機材料マスクの下方に配置されたエッチング層を有するウエハが、エッチングチャンバ内に供給される。CF4およびH2を備えるエッチングガスが、エッチングチャンバに供給される。CF4は流速を有し、H2は流速を有し、H2の流速はCF4の流速よりも大きい。エッチングガスから、プラズマが形成される。エッチングガスから形成されたプラズマを用いて、有機材料マスクを通してエッチング層に形状がエッチングされる。

添付の図面を参照しつつ行う本発明の詳細な説明において、本発明の上述の特徴およびその他の特徴を詳述する。

以下では、添付図面に例示されたいくつかの好ましい実施形態を参照して、本発明の詳しい説明を行う。以下の説明では、本発明の完全な理解を促すために、数多くの具体的な詳細事項が示されている。しかしながら、当業者にとって明らかなように、本発明は、これらの具体的な詳細事項の一部または全てがなくとも実施することが可能である。そのほか、本発明が不必要に不明瞭となるのを避けるため、周知の処理工程および/または構造については、詳細な説明を省略した。

本発明は、197nm以下の世代のフォトレジストに対して、誘電体層(特に、低誘電体層)を、高い選択比で選択的にエッチングすることができるエッチング処理を提供する。選択比は、無限に近くてよい。

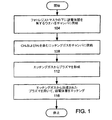

理解しやすいように、本発明の一実施形態で利用可能な処理を示す高レベルのフローチャートを図1に示す。フォトレジストマスクの下に配置された誘電体層を有するウエハが、処理チャンバ内に配置される(工程104)。CH4およびH2からなるエッチングガスが、エッチングチャンバに供給される(工程108)。エッチングガスにおいては、CF4の流速よりもH2の流速の方が大きい。エッチングガスから、プラズマが形成される(工程112)。エッチングガスから形成されたプラズマを用いて、エッチングマスクを通して誘電体層に形状がエッチングされる(工程116)。

実施例

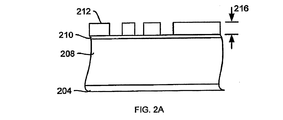

トレンチを形成するための本発明の処理の一実施例では、フォトレジストマスクの下に配置された誘電体層を有するウエハが、処理チャンバ内に配置される(工程104)。本発明の一実施例に関して、図2Aは、フォトレジストマスク212と、その下に配置された下部反射防止幕(BARC)210と、その下に配置された誘電体層208とを有するウエハを示す断面図である。誘電体層208は、低誘電体であること、すなわち、k<3.0であることが好ましい。さらに、フォトレジストマスク212を形成するフォトレジストは、193nm以下の世代のフォトレジストであるため、193nm世代のフォトレジスト以下の厚さである。本発明のエッチングの高選択比により、フォトレジストマスクは、3000Å未満の塗布厚さ216であってもよい。この実施例では、低誘電率材料は、Coral、Black Diamond、または、Auroraなど、有機ケイ酸塩ガラスである。

トレンチを形成するための本発明の処理の一実施例では、フォトレジストマスクの下に配置された誘電体層を有するウエハが、処理チャンバ内に配置される(工程104)。本発明の一実施例に関して、図2Aは、フォトレジストマスク212と、その下に配置された下部反射防止幕(BARC)210と、その下に配置された誘電体層208とを有するウエハを示す断面図である。誘電体層208は、低誘電体であること、すなわち、k<3.0であることが好ましい。さらに、フォトレジストマスク212を形成するフォトレジストは、193nm以下の世代のフォトレジストであるため、193nm世代のフォトレジスト以下の厚さである。本発明のエッチングの高選択比により、フォトレジストマスクは、3000Å未満の塗布厚さ216であってもよい。この実施例では、低誘電率材料は、Coral、Black Diamond、または、Auroraなど、有機ケイ酸塩ガラスである。

図3は、この実施例で利用可能な層蒸着工程、エッチング工程、および、剥離工程で用いることのできるプラズマ処理チャンバ300を示す説明図である。プラズマ処理チャンバ300は、閉じ込めリング302と、上側電極304と、下側電極308と、ガス源310と、排気ポンプ320とを備える。プラズマ処理チャンバ300内で、ウエハ204は、下側電極308の上に配置される。下側電極308は、ウエハ204を保持するのに適切な基板保持機構(例えば、静電チャック、機械的クランプなど)を備える。リアクタ上部328は、下側電極308のちょうど反対側に配置された上側電極304を備える。上側電極304、下側電極308、および、閉じ込めリング302は、閉じ込めプラズマ容積を規定する。ガスが、ガス源310によって、閉じ込めプラズマ容積に供給され、排気ポンプ320によって、閉じ込めリング302および排気口を通って、閉じ込めプラズマ容積から排気される。上側電極304には、第1のRF源344が、電気的に接続されている。下側電極308には、第2のRF源348が、電気的に接続されている。チャンバ壁352が、閉じ込めリング302、上側電極304、および、下側電極308を取り囲んでいる。第1のRF源344および第2のRF源348は両方とも、27MHz電源と2MHz電源とを備えてよい。他の組み合わせで電極にRF電源を接続してもよい。カリフォルニア州フレモントのLAM Research Corporation(商標)が製造し、本発明の好ましい実施形態で利用可能な、2300Flex(商標)、Exelan HPT、または、2300(商標)Exelanの場合には、27MHzおよび2MHz電源の両方が、下側電極に接続された第2のRF電源348を形成し、上側電極は、接地される。RF源344、348、排気ポンプ320、および、ガス源310には、制御部335が、制御可能なように接続されている。

図4Aおよび4Bは、本発明の実施形態で用いられる制御部335の実施に適したコンピュータシステム800を示す図である。図4Aは、コンピュータシステムの物理的形状の一例を示す。もちろん、コンピュータシステムは、集積回路、プリント基板、および、小型携帯デバイスから大型スーパコンピュータまで、多くの物理的形状を有してよい。コンピュータシステム800は、モニタ802と、ディスプレイ804と、筐体806と、ディスクドライブ808と、キーボード810と、マウス812とを備える。ディスク814は、コンピュータシステム800とデータをやり取りするために用いられるコンピュータ読み取り可能な媒体である。

図4Bは、コンピュータ800のブロック図の一例である。システムバス820には、様々なサブシステムが取り付けられている。1または複数のプロセッサ822(中央処理装置(CPU)とも呼ぶ)が、メモリ824などの記憶装置に接続されている。メモリ824は、ランダムアクセスメモリ(RAM)および読み出し専用メモリ(ROM)を含む。当技術分野で周知のように、ROMは、CPUに対して単方向的にデータや命令を転送するよう機能し、RAMは、通例、双方向的にデータや命令を転送するために用いられる。これらの種類のメモリは両方とも、後に示す任意の適切なコンピュータ読み取り可能媒体を備えてよい。CPU822には、さらに、固定ディスクが、双方向的に接続されており、さらなるデータ記憶容量を提供している。固定ディスク826は、後に示すコンピュータ読み取り可能媒体のいずれを備えてもよい。固定ディスク826は、プログラムやデータなどを格納するために用いられてよく、通例は、一次記憶装置よりも遅い二次記憶媒体(ハードディスクなど)である。固定ディスク826内に保持された情報は、必要に応じて、メモリ824内の仮想メモリとして標準的な方法で組み込まれてよいことを理解されたい。リムーバブルディスク814は、後に示すコンピュータ読み取り可能媒体のいずれかの形態を取ってよい。

CPU822は、さらに、ディスプレイ804、キーボード810、マウス812、および、スピーカ830など、様々な入力/出力装置に接続されている。一般に、入力/出力装置は、ビデオディスプレイ、トラックボール、マウス、キーボード、マイク、タッチセンサ式ディスプレイ、トランスデューサ式カードリーダ、磁気または紙テープリーダ、タブレット、スタイラス、音声または手書き認識装置、バイオメトリクスリーダ、または、他のコンピュータ、のいずれであってもよい。CPU822は、必要に応じて、ネットワークインターフェース840を用いて、他のコンピュータや電気通信ネットワークに接続されてもよい。かかるネットワークインターフェースを用いれば、CPUは、上述の方法の工程を実行する途中で、ネットワークから情報を受信、または、ネットワークに情報を出力することができる。さらに、本発明の方法の実施形態は、CPU822単体で実行されてもよいし、インターネットなどのネットワーク上で、処理の一部を分担する遠隔CPUと協調して実行されてもよい。

さらに、本発明の実施形態は、様々なコンピュータによる動作を実行するためのコンピュータコードを有するコンピュータ読み取り可能な媒体を備えたコンピュータストレージ製品に関する。媒体およびコンピュータコードは、本発明のために、特別に設計および構成されてもよいし、コンピュータソフトウェア分野における当業者にとって周知および利用可能なものであってもよい。コンピュータ読み取り可能な媒体の例としては、ハードディスク、フレキシブルディスク、磁気テープなどの磁気媒体;CD−ROM、ホログラフィック素子などの光学媒体;フロプティカルディスクなどの光磁気媒体;特定用途向け集積回路(ASIC)、プログラム可能論理回路(PLD)、ROMおよびRAMなど、プログラムコードを格納および実行するよう特別に構成されたハードウェア装置、が挙げられるが、それらには限定されない。コンピュータコードの例としては、コンパイラによって生成されたコードなどのマシンコードや、インタープリタを用いてコンピュータによって実行される高級言語コードを含むファイルが挙げられる。コンピュータ読み取り可能な媒体は、搬送波において具現化されたコンピュータデータ信号によって転送されてプロセッサが実行可能な一連の命令を表すコンピュータコードであってもよい。

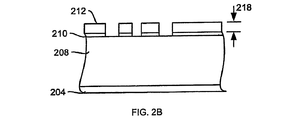

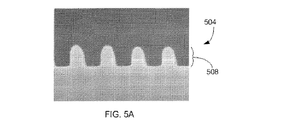

この実施例では、下部反射防止膜(BARC)210は、誘電体層のエッチングの前に開口される。BARC210を開口することにより、図2Bに示すように、フォトレジストマスクの厚さは、残存フォトレジストマスク厚さ218まで低減される。フォトレジストマスクは、2000Å未満の残存マスク厚さを有してよい。この実施例では、BARCの開口は、チャンバ300内で100mTorrの圧力を維持する処理によって実行される。27MHzで200ワットの電力および2MHzで電力が供給される。BARC開口ガスすなわち100sccmのCF4が供給される。BARC開口処理は、49秒間維持される。図5Aは、BARCが開口されて主エッチング動作が施される前のフォトレジストマスク/BARC層504の下に位置する誘電体層を示す断面の写真である。フォトレジストおよびBARCは、約182nmのフォトレジスト/BARC厚さ508を有する。

次に、ガス源310から、CF4およびH2を含むエッチングガスが供給される(工程108)。この実施例では、エッチングガスは、60sccmのCF4、70sccmのH2、および、300sccmのArの流れを供給する。エッチングガスから、プラズマが生成される(工程112)。この実施例では、チャンバの圧力は、80mTorrに維持される。27MHzで600ワットが供給され、2MHzで200ワットが供給される。エッチングガスから形成されたプラズマを用いて、誘電体層208における形状がエッチングされる(工程116)。この処理を60秒間維持することにより、2681Åの形状深さがエッチングされる。この実施例では、誘電体層における形状をエッチングする際に、フォトレジストの損失がなく、むしろ、フォトレジストにポリマを追加するため、フォトレジストに対する誘電体のエッチング選択比が無限になる。図2Cは、誘電体層208の形状222のエッチングが完了した後のウエハ204を示す断面図である。残存フォトレジストマスクと、エッチング中に追加されたポリマとを合わせた厚さ220は、エッチング前の残存フォトレジストマスク厚さ218よりも大きいことに注意されたい。図5Bは、上述のエッチングパラメータを用いて、主エッチング動作を施した後のフォトレジストマスク/BARC層504の下に位置する誘電体層の断面の写真である。フォトレジストおよびBARCは、約229nmのフォトレジスト/BARC厚さ512を有する。このように、追加されたポリマは、エッチング処理中にフォトレジストの厚さを増大させた。

次いで、フォトレジストマスクは剥離される。

本発明の処理を用いれば、無限の選択比を実現することができる。本発明の処理は、エッチング中にフォトレジストの厚さを増大させることができる。

本発明の別の実施形態では、193nm以降の世代のフォトレジストマスクの代わりに、他の有機層をエッチングマスクとして用いてもよい。エッチング前の残存有機層は、2000Å未満でよいことがわかった。エッチング前の残留有機層すなわちフォトレジスト層は、1000Å未満であることが、より好ましい。エッチング前の残留有機層すなわちフォトレジスト層は、500Å未満であることが、最も好ましい。より高世代のフォトレジストのより薄いフォトレジストマスクの利用を可能にすることによって、より高世代のフォトレジストのより薄いフォトレジストマスクが分解能を高めるため、限界寸法を小さくすることができる。

H2の流速は、CF4の流速よりも大きいことが好ましい。H2の流速(x)は、CF4の流速(y)よりも大きく、CF4の流速の5倍(5y)よりも小さい、すなわち、5y>x>yであることが、より好ましい。H2の流速(x)は、CF4の流速の5倍(5y)とCF4の流速の3倍(3y)との間、すなわち5y>x>3y、もしくは、CF4の流速の2倍(2y)とCF4の流速(y)との間、すなわち2y>x>yであることが、さらに好ましい。

流速60sccmのCF4に対しては、H2対CF4の流速の比が、約1:1から2:1になるように、H2の流速は、60sccmと120sccmの間であることが好ましい。H2の最も好ましい流速は、80sccmである。流速35sccmのCF4に対しては、H2対CF4の流速の比が、約3:1から5:1になるように、H2の流速は、100sccmと175sccmの間であることが好ましい。この例では、H2の最も好ましい流速は、120sccmである。

低誘電体をエッチングするために、上述のレシピに、N2ガスを追加してもよい。上述のレシピに追加できるN2の好ましい流速は、5sccmから40sccmである。N2の最も好ましい流速は、約20sccmである。

N2を用いるレシピの実施例では、主エッチング中に、チャンバ内の圧力は90mTorrに維持される。基本的に、40sccmのCF4と、50sccmのH2と、20sccmのN2と、100sccmのArと、からなるエッチングガスが、チャンバ内に供給される。27MHzで800ワットが供給される。2MHzで400ワットが供給される。このレシピによるエッチングでは、マスクの厚さが増大すると共に、ストリエーション(側壁へのポリマの蒸着)が観察されず、十分に垂直なプロフィルを有する形状が形成された。

出力レンジは、周波数が高い方の電源(すなわち、27MHzの電源)については200Wから1500W、周波数が低い方の電源(すなわち、2MHzの電源)については0Wから1000Wであることが好ましい。出力レンジは、周波数が高い方の電源については500Wから1200W、周波数が低い方の電源については200Wから800Wであることが、より好ましい。出力レンジは、周波数が高い方の電源については800Wから1000W、周波数が低い方の電源については300Wから600Wであることが、最も好ましい。低誘電率のビアをエッチングするために上述の出力レンジを用いるレシピの別の例では、1000Wの高周波数電力および400Wの低周波数電力と共に、90mTorrの圧力を提供する。

理論に縛られなければ、CF4は、各炭素原子について4つのフッ素原子をエッチングに提供する強いエッチャントであると考えられる。そのため、フォトレジストを保護するために、H2が加えられる。かかる組み合わせは、エッチングの停止を引き起こすと考えられていた。予想に反して、かかる組み合わせは、エッチングの停止を引き起こさないことがわかった。

別の実施形態では、低誘電体がエッチングされている時に、5から40sccmの間の流速のエッチングガスに、N2が追加されてもよい。N2は、Coral(カリフォルニア州サンノゼのNovellusが製造)、Black Diamond(カリフォルニア州サンタクララのApplied Materials Inc.が製造)、および、Aurora(東京のASM Japan KKが製造)など、有機ケイ酸塩ガラスに対する低誘電体エッチング中に、炭素を除去する比較的希薄なエッチングガスを提供すると考えられている。

本発明の処理は、毎分1ミクロンを超えるエッチング速度を実現することがわかった。本発明のエッチング処理は、毎分約1.3ミクロンまでのエッチングを実現することがわかった。より大きい電力を用いれば、さらに大きいエッチング速度を実現することができる。

エッチング速度が速すぎると、制御が困難になる場合がある。エッチング速度を遅くするために、アルゴンを加えてもよい。これにより、アルゴンの流れを制御することで、エッチング速度を良好に制御できるようになる。

本発明のエッチングガスを用いた場合のエッチング時間は、10秒よりも長いことが好ましい。エッチング時間は、20秒よりも長いことが、より好ましい。

予想に反して、本発明の処理は、ストリエーション(筋状痕)を低減することがわかった。この処理は、フォトレジスト上に蒸着するだけでなく、側壁ポリマの薄層も蒸着するため、ストリエーションが低減されると考えられる。この側壁ポリマは、ストリエーションの形成を低減すると思われる。

本発明は、ビアの形成、トレンチの形成、窒化ケイ素ハードマスクの開口など、様々な用途で利用されてよい。ハードマスクは、低誘電体よりも上側に配置されてよい。本発明の処理は、ハードマスクの開口および誘電体層(特に、低誘電体層)のエッチングの両方において、薄いフォトレジストマスクを用いることを可能にする。

以上、いくつかの好ましい実施形態を参照しつつ本発明について説明したが、本発明の範囲内で、種々の代替物、置換物、および等価物が存在する。また、本発明の方法および装置を実施する他の態様が数多く存在することにも注意されたい。したがって、添付の特許請求の範囲は、本発明の真の趣旨および範囲内に含まれる代替物、置換物、および等価物の全てを網羅するものとして解釈される。

Claims (30)

- フォトレジストマスクの下方の誘電体層をエッチングするための方法であって、

フォトレジストマスクの下方に配置された前記誘電体層を有するウエハを、エッチングチャンバ内に供給し、

CF4およびH2を備えるエッチングガスを前記エッチングチャンバに供給し、前記CF4は流速を有し、前記H2は流速を有し、前記H2の流速は前記CF4の流速よりも大きく、

前記エッチングガスからプラズマを形成し、

前記エッチングガスから形成された前記プラズマを用いて、前記エッチングマスクを通して前記誘電体層に形状をエッチングすることと、を備える、方法。 - 請求項1に記載の方法であって、前記フォトレジストマスクは、前記形状をエッチングする前には、2000Å未満の厚さを有する、方法。

- 請求項1または2に記載の方法であって、前記フォトレジストは、193nm世代のフォトレジスト以下の厚さである、方法。

- 請求項1ないし3のいずれかに記載の方法であって、前記誘電体層に対する形状のエッチングは、前記エッチング中に、前記フォトレジストマスクにポリマを追加して、前記マスクの厚さを増大させることで、前記フォトレジストマスクに対する前記誘電体層のエッチング選択比を無限にする、方法。

- 請求項1ないし4のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の5倍より小さい、方法。

- 請求項1ないし5のいずれかに記載の方法であって、前記フォトレジストマスクは、前記形状をエッチングする前には、500Å未満の厚さを有する、方法。

- 請求項1ないし6のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の3倍より大きい、方法。

- 請求項1ないし7のいずれかに記載の方法であって、前記エッチングガスは、さらに、N2を備える、方法。

- 請求項1ないし8のいずれかに記載の方法であって、前記誘電体層は、低誘電体層である、方法。

- 請求項8または9に記載の方法であって、前記N2は、5ないし40sccmの流速を有する、方法。

- 請求項1ないし10のいずれかに記載の方法であって、前記エッチングは、毎秒1ミクロンを超えるエッチング速度を実現する、方法。

- 請求項1ないし11のいずれかに記載の方法であって、前記エッチングガスは、さらに、アルゴンを備える、方法。

- 請求項1ないし12のいずれかに記載の方法であって、前記形状のエッチングは、20秒より長い間実行される、方法。

- 請求項1ないし13のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の2倍より小さい、方法。

- 請求項1ないし14のいずれかに記載の方法であって、前記誘電体層に対する形状のエッチングは、さらに、前記形状の側壁にポリマを蒸着して、ストリエーションを低減する、方法。

- 請求項1ないし15のいずれかに記載の方法によって形成された半導体素子。

- 請求項1ないし15のいずれかに記載の方法を実行するための装置。

- 有機材料マスクの下方のエッチング層をエッチングするための方法であって、

前記有機材料マスクの下方に配置された前記エッチング層を有するウエハを、エッチングチャンバ内に供給し、

CF4およびH2を備えるエッチングガスを前記エッチングチャンバに供給し、前記CF4は流速を有し、前記H2は流速を有し、前記H2の流速は前記CF4の流速よりも大きく、

前記エッチングガスからプラズマを形成し、

前記エッチングガスから形成された前記プラズマを用いて、前記有機材料マスクを通して前記エッチング層に形状をエッチングすることと、を備える、方法。 - 請求項18に記載の方法であって、前記有機材料マスクは、前記形状をエッチングする前には、2000Å未満の厚さを有する、方法。

- 請求項18または19に記載の方法であって、前記エッチング層に対する形状のエッチングは、前記エッチング中に、前記有機材料マスクにポリマを追加して、前記マスクの厚さを増大させることで、前記有機材料マスクに対する前記エッチング層のエッチング選択比を無限にする、方法。

- 請求項18ないし20のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の5倍より小さい、方法。

- 請求項18ないし21のいずれかに記載の方法であって、前記有機材料マスクは、前記形状をエッチングする前には、500Å未満の厚さを有する、方法。

- 請求項18ないし22のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の3倍より大きい、方法。

- 請求項18ないし23のいずれかに記載の方法であって、前記エッチングガスは、さらに、N2を備える、方法。

- 請求項24に記載の方法であって、前記N2は、5ないし40sccmの流速を有する、方法。

- 請求項18ないし25のいずれかに記載の方法であって、前記誘電体層は、低誘電体層である、方法。

- 請求項18ないし26のいずれかに記載の方法であって、前記エッチングは、毎秒1ミクロンを超えるエッチング速度を実現する、方法。

- 請求項18ないし27のいずれかに記載の方法であって、前記形状のエッチングは、20秒より長い間実行される、方法。

- 請求項18ないし28のいずれかに記載の方法であって、前記H2の流速は、前記CF4の流速の2倍より小さい、方法。

- 請求項18ないし29のいずれかに記載の方法であって、前記誘電体層に対する形状のエッチングは、さらに、前記形状の側壁にポリマを蒸着して、ストリエーションを低減する、方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/892,945 US20060011578A1 (en) | 2004-07-16 | 2004-07-16 | Low-k dielectric etch |

| PCT/US2005/024905 WO2006019849A1 (en) | 2004-07-16 | 2005-07-12 | Low-k dielectric etch |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008507137A true JP2008507137A (ja) | 2008-03-06 |

| JP2008507137A5 JP2008507137A5 (ja) | 2009-01-08 |

Family

ID=35159879

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007521623A Withdrawn JP2008507137A (ja) | 2004-07-16 | 2005-07-12 | 低誘電体のエッチング |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20060011578A1 (ja) |

| JP (1) | JP2008507137A (ja) |

| KR (1) | KR20070046095A (ja) |

| CN (1) | CN101027760A (ja) |

| TW (1) | TW200616063A (ja) |

| WO (1) | WO2006019849A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060032833A1 (en) * | 2004-08-10 | 2006-02-16 | Applied Materials, Inc. | Encapsulation of post-etch halogenic residue |

| US20070269975A1 (en) * | 2006-05-18 | 2007-11-22 | Savas Stephen E | System and method for removal of photoresist and stop layer following contact dielectric etch |

| US7704680B2 (en) * | 2006-06-08 | 2010-04-27 | Advanced Micro Devices, Inc. | Double exposure technology using high etching selectivity |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3837856A (en) * | 1967-04-04 | 1974-09-24 | Signetics Corp | Method for removing photoresist in manufacture of semiconductor devices |

| DE3420347A1 (de) * | 1983-06-01 | 1984-12-06 | Hitachi, Ltd., Tokio/Tokyo | Gas und verfahren zum selektiven aetzen von siliciumnitrid |

| US5658425A (en) * | 1991-10-16 | 1997-08-19 | Lam Research Corporation | Method of etching contact openings with reduced removal rate of underlying electrically conductive titanium silicide layer |

| JP3215151B2 (ja) * | 1992-03-04 | 2001-10-02 | 株式会社東芝 | ドライエッチング方法 |

| EP0647163B1 (en) * | 1992-06-22 | 1998-09-09 | Lam Research Corporation | A plasma cleaning method for removing residues in a plasma treatment chamber |

| GB9616225D0 (en) * | 1996-08-01 | 1996-09-11 | Surface Tech Sys Ltd | Method of surface treatment of semiconductor substrates |

| US6270948B1 (en) * | 1996-08-22 | 2001-08-07 | Kabushiki Kaisha Toshiba | Method of forming pattern |

| US5989353A (en) * | 1996-10-11 | 1999-11-23 | Mallinckrodt Baker, Inc. | Cleaning wafer substrates of metal contamination while maintaining wafer smoothness |

| US6080680A (en) * | 1997-12-19 | 2000-06-27 | Lam Research Corporation | Method and composition for dry etching in semiconductor fabrication |

| US6635185B2 (en) * | 1997-12-31 | 2003-10-21 | Alliedsignal Inc. | Method of etching and cleaning using fluorinated carbonyl compounds |

| US6635335B1 (en) * | 1999-06-29 | 2003-10-21 | Micron Technology, Inc. | Etching methods and apparatus and substrate assemblies produced therewith |

| KR100327346B1 (ko) * | 1999-07-20 | 2002-03-06 | 윤종용 | 선택적 폴리머 증착을 이용한 플라즈마 식각방법 및 이를이용한 콘택홀 형성방법 |

| US6265320B1 (en) * | 1999-12-21 | 2001-07-24 | Novellus Systems, Inc. | Method of minimizing reactive ion etch damage of organic insulating layers in semiconductor fabrication |

| US6506678B1 (en) * | 2000-05-19 | 2003-01-14 | Lsi Logic Corporation | Integrated circuit structures having low k porous aluminum oxide dielectric material separating aluminum lines, and method of making same |

| US6794109B2 (en) * | 2001-02-23 | 2004-09-21 | Massachusetts Institute Of Technology | Low abosorbing resists for 157 nm lithography |

| US20030181034A1 (en) * | 2002-03-19 | 2003-09-25 | Ping Jiang | Methods for forming vias and trenches with controlled SiC etch rate and selectivity |

| AU2003244166A1 (en) * | 2002-06-27 | 2004-01-19 | Tokyo Electron Limited | Plasma processing method |

| US7169695B2 (en) * | 2002-10-11 | 2007-01-30 | Lam Research Corporation | Method for forming a dual damascene structure |

| US6809028B2 (en) * | 2002-10-29 | 2004-10-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Chemistry for liner removal in a dual damascene process |

| KR20070009729A (ko) * | 2004-05-11 | 2007-01-18 | 어플라이드 머티어리얼스, 인코포레이티드 | 불화탄소 에칭 화학반응에서 H2 첨가를 이용한탄소-도핑-Si 산화물 에칭 |

-

2004

- 2004-07-16 US US10/892,945 patent/US20060011578A1/en not_active Abandoned

-

2005

- 2005-07-12 WO PCT/US2005/024905 patent/WO2006019849A1/en active Application Filing

- 2005-07-12 JP JP2007521623A patent/JP2008507137A/ja not_active Withdrawn

- 2005-07-12 CN CNA2005800239276A patent/CN101027760A/zh active Pending

- 2005-07-12 KR KR1020077002578A patent/KR20070046095A/ko not_active Application Discontinuation

- 2005-07-15 TW TW094124429A patent/TW200616063A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| CN101027760A (zh) | 2007-08-29 |

| US20060011578A1 (en) | 2006-01-19 |

| TW200616063A (en) | 2006-05-16 |

| WO2006019849A1 (en) | 2006-02-23 |

| KR20070046095A (ko) | 2007-05-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5165560B2 (ja) | エッチング層に形状を形成するための方法 | |

| KR101555397B1 (ko) | 포토레지스트 마스크 전처리를 갖는 플라즈마 프로세스 | |

| KR101534883B1 (ko) | 마스크 트리밍 | |

| KR101274382B1 (ko) | 에칭 프로세스를 위한 안정화된 포토레지스트 구조 | |

| KR101442269B1 (ko) | 무한 선택적 포토레지스트 마스크 식각 | |

| KR101516455B1 (ko) | Arl 에칭을 이용한 마스크 트리밍 | |

| US20070264830A1 (en) | Pitch reduction | |

| US20060134917A1 (en) | Reduction of etch mask feature critical dimensions | |

| JP2008060565A (ja) | 三層レジストによる有機層エッチング | |

| JP2013016844A (ja) | 均一性を制御したエッチング | |

| JP2008508743A (ja) | エッチングされたウエハからフォトレジストを剥離するための方法 | |

| TWI393997B (zh) | 用於蝕刻基板上之低k介電層的方法、半導體裝置以及用於在低k介電層中形成特徵的設備 | |

| JP2007528610A (ja) | ラインエッジラフネス制御 | |

| US7049052B2 (en) | Method providing an improved bi-layer photoresist pattern | |

| JP2008507137A (ja) | 低誘電体のエッチング |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080714 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081113 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100511 |