JP2008022009A - 不揮発性メモリー素子及びその製造方法 - Google Patents

不揮発性メモリー素子及びその製造方法 Download PDFInfo

- Publication number

- JP2008022009A JP2008022009A JP2007182659A JP2007182659A JP2008022009A JP 2008022009 A JP2008022009 A JP 2008022009A JP 2007182659 A JP2007182659 A JP 2007182659A JP 2007182659 A JP2007182659 A JP 2007182659A JP 2008022009 A JP2008022009 A JP 2008022009A

- Authority

- JP

- Japan

- Prior art keywords

- arrangement interval

- word line

- pattern

- numbered

- selection line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 14

- 230000015654 memory Effects 0.000 claims abstract description 281

- 239000000758 substrate Substances 0.000 claims abstract description 51

- 239000004065 semiconductor Substances 0.000 claims abstract description 23

- 238000000034 method Methods 0.000 claims description 40

- 230000004888 barrier function Effects 0.000 claims description 32

- 239000000463 material Substances 0.000 claims description 32

- 238000005530 etching Methods 0.000 claims description 28

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 17

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 17

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 14

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 14

- 239000000203 mixture Substances 0.000 claims description 12

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 11

- 229920005591 polysilicon Polymers 0.000 claims description 11

- 239000000126 substance Substances 0.000 claims description 4

- 241000519695 Ilex integra Species 0.000 claims 1

- 229920002120 photoresistant polymer Polymers 0.000 description 72

- 238000000059 patterning Methods 0.000 description 9

- 238000001312 dry etching Methods 0.000 description 8

- 238000000926 separation method Methods 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 6

- 230000006698 induction Effects 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000013500 data storage Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000005055 memory storage Effects 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/10—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the top-view layout

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

- H10B41/35—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region with a cell select transistor, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

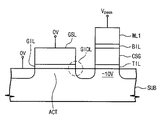

【解決手段】不揮発性メモリー素子は、活性領域を含む半導体基板及び前記活性領域上の第1及び第2メモリーセルストリングを含む。第1メモリーセルストリングは、第1接地選択ライン及び第1ストリング選択ラインの間の活性領域を横切る複数の第1ワードラインを含み、複数の第1ワードラインの中の隣り合うラインの間に第1配置間隔が提供される。第2メモリーセルストリングは、第2接地選択ライン及び第2ストリング選択ラインの間の活性領域を横切る複数の第2ワードラインを含み、同じ第1配置間隔が複数の第2ワードラインの中の隣り合うラインの間に提供される。第1接地選択ラインは、第2接地選択ライン及び複数の第1ワードラインの間にあり、第2接地選択ラインは、第1接地選択ライン及び複数の第2ワードラインの間にある。

【選択図】図2A

Description

BIL バリア絶縁膜

CSG 電荷貯蔵ゲート

GIL ゲート絶縁膜

GSL 接地選択ライン

SSL ストリング選択ライン

TIL トンネル絶縁膜

WL ワードライン

Claims (41)

- 活性領域を含む半導体基板と、

第1接地選択ライン及び第1ストリング選択ラインの間の前記活性領域を横切って第1配置間隔を置いて互いに隣り合う複数の第1ワードラインを含む前記活性領域上の第1メモリーセルストリングと、

第2接地選択ライン及び第2ストリング選択ラインの間の前記活性領域を横切って前記第1配置間隔を置いて互いに隣り合う複数の第2ワードラインを含む前記活性領域上の第2メモリーセルストリングとを含み、

前記第1接地選択ラインは、前記第2接地選択ライン及び前記第1ワードラインの間にあり、前記第2接地選択ラインは、前記第1接地選択ライン及び前記第2ワードラインの間にあり、前記活性領域の中の前記第1及び第2接地選択ラインの間の領域には、前記ワードラインが無く、前記第1及び第2接地選択ラインの間の第2配置間隔は、前記第1配置間隔より少なくとも3倍大きいことを特徴とする不揮発性メモリー素子。 - 前記第2配置間隔は、前記第1配置間隔の3乃至4倍の範囲の内で前記第1配置間隔より大きいことを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より3倍以上大きいことを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より少なくとも4倍大きいことを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第1ワードラインは、偶数番目の不揮発性メモリーセルワードライン及びダミーワードラインを含み、前記ダミーワードラインは、前記偶数番目のメモリーセルワードラインの中の一番目及び前記第1接地選択ラインの間にあり、前記接地選択ライン及び前記ダミーワードラインの間に前記第1配置間隔が提供され、前記ダミーワードライン及び前記偶数番目のメモリーセルワードラインの中の前記一番目の間に前記第1配置間隔が提供され、前記偶数番目のメモリーセルワードラインの中の終わり及び前記ストリング選択ラインの間に前記第1配置間隔が提供されることを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第1ワードラインは、偶数番目のメモリーセルワードライン及びダミーワードラインを含み、前記ダミーワードラインは、前記偶数番目のメモリーセルワードラインの中の一番目及び前記第1接地選択ラインの間にあり、前記ダミーワードライン及び前記偶数番目のメモリーセルワードラインの中の前記一番目の間に第1配置間隔が提供され、前記接地選択ライン及び前記ダミーワードラインの間に第3配置間隔が提供され、前記第3配置間隔は、前記第1配置間隔より大きく、前記第1配置間隔の2倍以下であることを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第3配置間隔は、前記第1配置間隔の1.5乃至2倍であることを特徴とする請求項6に記載の不揮発性メモリー素子。

- 前記第1ワードラインは、偶数番目のメモリーセルワードラインを含み、前記接地選択ライン及び前記偶数番目のメモリーセルワードラインの中の一番目の間に前記第1配置間隔の少なくとも3倍の間隔が提供され、前記偶数番目のメモリーセルワードラインの中の終わり及び前記ストリング選択ラインの間に前記第1配置間隔が提供され、前記活性領域の中の前記接地選択ライン及び前記偶数番目のメモリーセルワードラインの中の前記終わりのラインの間の領域には、前記ワードラインが無いことを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第1及び第2メモリーセルストリングの各メモリーセルは、各々のワードライン及び前記活性領域の間の電荷貯蔵層と前記電荷貯蔵層及び前記ワードラインの間のバリア絶縁層を含むことを特徴とする請求項1に記載の不揮発性メモリー素子。

- 前記第1メモリーセルストリングの配列は、前記第2メモリーセルストリングの配列に対して鏡像対称であることを特徴とする請求項1に記載の不揮発性メモリー素子。

- 活性領域を含む半導体基板と、

前記活性領域を横切る接地選択ラインと、

前記活性領域を横切って前記接地選択ラインから離隔されたストリング選択ラインと、

前記接地選択ライン及び前記ストリング選択ラインの間の前記活性領域を横切って第1配置間隔を置いて隣り合う複数のメモリーセルワードライン及び前記複数のメモリーセルワードラインの中の一番目及び前記第1接地選択ラインの間にあり、前記複数のメモリーセルワードラインの中の前記一番目の間に前記第1配置間隔を置いて離隔されるダミーワードラインとを含み、

前記複数のメモリーセルワードラインの中の終わり及び前記ストリング選択ラインの間に第2配置間隔が提供され、前記第2配置間隔は、前記第1配置間隔より大きく、前記第1配置間隔の2倍以下であり、前記接地選択ライン及び前記ダミーワードラインの間に第3配置間隔が提供され、前記第3配置間隔は、前記第1配置間隔より大きく、前記第1配置間隔の2倍以下であることを特徴とする不揮発性メモリー素子。 - 前記第3配置間隔は、前記第1配置間隔の1.5乃至2倍であることを特徴とする請求項11に記載の不揮発性メモリー素子。

- 前記複数のメモリーセルワードラインは、第1メモリーセルワードラインを含み、前記活性領域を横切る第2接地選択ラインと、

前記活性領域を横切って前記第2接地選択ラインから離隔された第2ストリング選択ラインと、

前記第2接地選択ライン及び前記第2ストリング選択ラインの間の前記活性領域を横切る第2メモリーセルワードラインとを含み、

前記第1接地選択ラインは、前記第2接地選択ライン及び前記第1メモリーセルワードラインの間にあり、前記第2接地選択ラインは、前記第2ストリング選択ライン及び前記第1接地選択ラインの間にあり、前記活性領域の中の前記第1及び前記第2接地選択ラインの間の領域には、前記ワードラインが無く、前記第1及び前記第2接地選択ラインの間の第2配置間隔は、前記第1配置間隔より少なくとも3倍大きいことを特徴とする請求項11に記載の不揮発性メモリー素子。 - 前記第2配置間隔は、前記第1配置間隔の3乃至4倍の範囲の内で前記第1配置間隔より大きいことを特徴とする請求項13に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より3倍以上に大きいことを特徴とする請求項13に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より少なくとも4倍大きいことを特徴とする請求項13に記載の不揮発性メモリー素子。

- 各々の前記複数のワードライン及び前記活性領域の間に個別的に介される複数の電荷貯蔵層及び前記各々のワードライン及び前記電荷貯蔵層の間に個別的に介される複数のバリア絶縁膜を含むことを特徴とする請求項11に記載の不揮発性メモリー素子。

- 前記複数のメモリーセルワードラインは、偶数番目のメモリーセルワードラインを含むことを特徴とする請求項11に記載の不揮発性メモリー素子。

- 活性領域を含む半導体基板と、

前記活性領域を横切る接地選択ラインと、

前記活性領域を横切って前記接地選択ラインから離隔されたストリング選択ラインと、

前記接地選択ライン及び前記ストリング選択ラインの間の前記活性領域を横切る複数のメモリーセルワードラインとを含み、

隣り合う前記複数のメモリーセルワードラインの間及び前記複数のメモリーセルワードラインの中の終わり及び前記ストリング選択ラインの間に同じ第1配置間隔が提供され、前記接地選択ライン及び前記複数のメモリーセルワードラインの中の一番目の間に第2配置間隔が提供され、前記第2配置間隔は、前記第1配置間隔より少なくとも3倍大きく、前記活性領域の中の前記接地選択ライン及び前記複数のメモリーセルワードラインの中の前記一番目の間の領域には、前記ワードラインが無いことを特徴とする不揮発性メモリー素子。 - 前記第2配置間隔は、前記第1配置間隔より3倍大きいことを特徴とする請求項19に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔の4倍以下であることを特徴とする請求項19に記載の不揮発性メモリー素子。

- 前記複数のメモリーセルワードラインは複数の第1メモリーセルワードラインを含み、

前記活性領域を横切る第2接地選択ラインと、

前記活性領域を横切って前記第2接地選択ラインから離隔された第2ストリング選択ラインと、

前記第2接地選択ライン及び前記第2ストリング選択ラインの間の前記活性領域を横切る複数の第2メモリーセルワードラインとを含み、

前記第1接地選択ラインは、前記第2接地選択ライン及び前記第1メモリーセルワードラインの間にあり、前記第2接地選択ラインは、前記第2ストリング選択ライン及び前記第1接地選択ラインの間にあり、前記活性領域の中の前記第1及び第2接地選択ラインの間の領域には、前記ワードラインが無く、前記第1及び第2接地選択ラインの間の第2配置間隔は、前記第1配置間隔より少なくとも3倍大きいことを特徴とする請求項19に記載の不揮発性メモリー素子。 - 前記第2配置間隔は、前記第1配置間隔の3乃至4倍の範囲の内で前記第1配置間隔より大きいことを特徴とする請求項22に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より3倍大きいことを特徴とする請求項22に記載の不揮発性メモリー素子。

- 前記第2配置間隔は、前記第1配置間隔より少なくとも4倍大きいことを特徴とする請求項22に記載の不揮発性メモリー素子。

- 各々の前記複数のワードライン及び前記活性領域の間に個別的に介される複数の電荷貯蔵層と、

前記各々の前記複数のワードライン及び前記電荷貯蔵層の間に個別的に介される複数のバリア絶縁膜とを含むことを特徴とする請求項19に記載の不揮発性メモリー素子。 - 前記複数のメモリーセルワードラインは、偶数個のメモリーセルワードラインを含むことを特徴とする請求項19に記載の不揮発性メモリー素子。

- 基板の上に蝕刻ターゲット層を形成する段階と、

前記基板の上に第1ハードマスクパターンを形成する段階と、

前記第1ハードマスクパターンの上に犠牲マスク層を形成する段階と、

前記犠牲マスク層の上に第2ハードマスクパターンを形成する段階と、

前記第1及び第2ハードマスクパターンの間の前記蝕刻ターゲット層の一部の領域が露出されるように前記第1及び第2ハードマスクパターンの間の前記犠牲マスク層の一部の領域を除去する段階と、

前記第1及び第2ハードマスクパターンの間に露出された前記蝕刻ターゲット層の一部の領域を蝕刻する段階とを含み、

前記第1選択ラインパターン及び一番目の奇数番目のワードラインパターンの間、隣り合う奇数番目のワードラインパターンの間及び終わりの奇数番目のワードラインパターン及び前記第2選択ラインパターンの間に同じ配置間隔が提供され、前記第1ハードマスクパターンは、第1物質を含み、

前記犠牲マスク層が形成された隣り合う奇数番目のワードラインパターンの側壁の間にギャップがあり、前記犠牲マスク層は、第2物質を含み、前記第1及び第2物質は、相違なる組成をもち、

前記第2ハードマスクパターンは、ダミーワードラインパターン及び偶数番目のワードラインパターンを含み、前記ダミーワードラインパターンは、前記第1選択ラインパターン及び前記一番目の奇数番目のワードラインパターンの間にあり、前記偶数番目のワードラインパターンは、隣り合う奇数番目のワードラインパターンの間及び前記終わりの奇数番目のワードラインパターンと前記第2選択ラインパターンの間にあり、前記第2ハードマスクパターンは、第3物質を含み、前記第2及び第3物質は、相違なる組成をもつことを特徴とする不揮発性メモリー素子の製造方法。 - 前記第1選択ラインパターン及び前記一番目の奇数番目のワードラインパターンの間に提供される前記配置間隔は、前記一番目の奇数番目のワードラインパターンの幅の3倍になることを特徴とする請求項28に記載の不揮発性メモリー素子の製造方法。

- 前記第1ハードマスクパターンは、シリコン窒化物を含み、前記犠牲マスク層は、ポリシリコンを含み、前記第2ハードマスクパターンは、シリコン酸化物を含むことを特徴とする請求項28に記載の不揮発性メモリー素子の製造方法。

- 前記奇数番目のワードラインパターンは、同じ幅をもち、隣り合う前記複数の奇数番目のワードラインパターンの間の前記配置間隔は、前記奇数番目のワードラインパターンの幅より大きいことを特徴とする請求項28に記載の不揮発性メモリー素子の製造方法。

- 前記蝕刻ターゲット層を形成する段階は、

前記基板の上に電荷貯蔵層を形成する段階と、

前記電荷貯蔵層の上にバリア絶縁層を形成する段階と、

前記バリア絶縁層の上にコントロールゲート層を形成する段階とを含むことを特徴とする請求項28に記載の不揮発性メモリー素子の製造方法。 - 基板の上に蝕刻ターゲット層を形成する段階と、

前記基板の上に複数の偶数番目のワードラインパターン及びダミーワードラインパターンを含む第1ハードマスクパターンを形成する段階と、

前記第1ハードマスクパターンの上に犠牲マスク層を形成する段階と、

前記犠牲マスク層の上に第2ハードマスクパターンを形成する段階と、

前記第1及び第2ハードマスクパターンの間の前記蝕刻ターゲット層の一部の領域が露出されるように前記第1及び第2ハードマスクパターンの間の前記犠牲マスク層の一部の領域を除去する段階と、

前記第1及び第2ハードマスクパターンの間に露出された前記蝕刻ターゲット層の一部の領域を蝕刻する段階とを含み、

前記偶数番目のワードラインパターンは、第1及び第2選択ラインパターンの間にあり、前記ダミーワードラインパターンは、前記第1選択ラインパターン及び一番目の偶数番目のワードラインパターンの間にあり、同じ第1配置間隔が前記ダミーワードラインパターン及び前記一番目の偶数番目のワードラインパターンの間に提供され、隣り合う偶数番目のワードラインパターンの間に提供され、第2配置間隔が前記第1選択ラインパターン及び前記ダミーワードラインパターンの間に提供され、終わりの偶数番目のワードラインパターン及び前記第2選択ラインパターンの間に提供され、前記第2配置間隔は、前記第1配置間隔より小さく、前記第1ハードマスクパターンは、第1物質を含み、前記犠牲マスク層が形成された隣り合う偶数番目のワードラインパターンの側壁の間と前記ダミーワードラインパターン及び前記一番目の偶数番目のワードラインパターンの間にギャップがあり、前記犠牲マスク層は、第2物質を含み、前記第1及び第2物質は、相違なる組成をもち、

前記第2ハードマスクパターンは、前記ギャップの内に形成され、前記第2ハードマスクパターンは、奇数番目のワードラインパターンを含み、前記奇数番目のワードラインパターンは、隣り合う偶数番目のワードラインパターンの間及び前記ダミーワードラインパターンと前記一番目の偶数番目のワードラインパターンの間にあり、前記第2ハードマスクパターンは、第3物質を含み、前記第2及び第3物質は、相違なる組成をもち、

前記ダミーワードラインパターン及び前記第1選択ラインパターンの間の空間には、前記第2ハードマスクパターンが無い不揮発性メモリー素子の製造方法。 - 前記ダミーワードラインパターンと前記一番目の偶数番目のワードラインパターンの間及び隣り合う偶数番目のワードラインパターンの間に提供される前記第1配置間隔は、前記一番目の偶数番目のワードラインパターンの幅の3倍であることを特徴とする請求項33に記載の不揮発性メモリー素子の製造方法。

- 前記第2配置間隔は、前記一番目の偶数番目のワードラインパターンの幅より大きいが、前記一番目の偶数番目のワードラインパターンの幅の2倍以下であることを特徴とする請求項34に記載の不揮発性メモリー素子の製造方法。

- 前記第2配置間隔は、前記一番目の偶数番目のワードラインパターンの幅の1.5倍乃至2倍になることを特徴とする請求項33に記載の不揮発性メモリー素子の製造方法。

- 前記偶数番目のワードラインパターンは、同じ幅をもち、隣り合う前記複数の偶数番目のワードラインパターンの間の前記配置間隔は、前記偶数番目のワードラインパターンの前記幅より大きいことを特徴とする請求項33に記載の不揮発性メモリー素子の製造方法。

- 前記蝕刻ターゲット層を形成する段階は、

前記基板の上に電荷貯蔵層を形成する段階と、

前記電荷貯蔵層の上にバリア絶縁層を形成する段階と、

前記バリア絶縁層の上にコントロールゲート層を形成する段階とを含むことを特徴とする請求項33に記載の不揮発性メモリー素子の製造方法。 - 基板の上に蝕刻ターゲット層を形成する段階と、

第1及び第2選択ラインパターンの間に複数の奇数番目のワードラインパターンを含む第1ハードマスクパターンを形成する段階と、

前記第1ハードマスクパターンの上に犠牲マスク層を形成する段階と、

前記犠牲マスク層の上に第2ハードマスクパターンを形成する段階と、

前記第1及び第2ハードマスクパターンの間の前記蝕刻ターゲット層の一部の領域が露出されるように前記第1及び第2ハードマスクパターンの間の前記犠牲マスク層の一部の領域を除去する段階と、

前記第1及び第2ハードマスクパターンの間に露出された前記蝕刻ターゲット層の一部の領域を蝕刻する段階とを含み、

前記第1ハードマスクパターンは、第1及び第2選択ラインパターンの間にある複数の奇数番目のワードラインパターンを含み、同一な第1配置間隔が隣り合う奇数番目のワードラインパターンの間及び終わりの奇数番目のワードラインパターンと前記第2選択ラインパターンの間に提供され、第2配置間隔が前記第1選択ラインパターン及び一番目の奇数番目のワードラインパターンの間に提供され、前記第2配置間隔は、前記第1配置間隔より大きく、前記第1ハードマスクパターンは、第1物質を含み、

前記犠牲マスク層が形成された隣り合う第1ハードマスクパターンの側壁の間にギャップがあり、前記犠牲マスク層は、第2物質を含み、前記第1及び第2物質は、相違なる組成をもち、

前記第2ハードマスクパターンは、偶数番目のワードラインパターンを含み、前記偶数番目のワードラインパターンは、隣り合う奇数番目のワードラインパターンの間及び前記終わりの奇数番目のワードラインパターンと前記第2選択ラインパターンの間にあり、前記第1選択ラインパターン及び前記一番目の奇数番目のワードラインパターンの間の空間には、前記第2ハードマスクパターンが無く、前記第2ハードマスクパターンは、第3物質を含み、前記第2及び第3物質は、相違なる組成をもつ不揮発性メモリー素子の製造方法。 - 前記第1配置間隔は、前記一番目の奇数番目のワードラインパターンの幅の3倍になることを特徴とする請求項39に記載の不揮発性メモリー素子の製造方法。

- 前記蝕刻ターゲット層を形成する段階は、

前記基板の上に電荷貯蔵層を形成する段階と、

前記電荷貯蔵層の上にバリア絶縁層を形成する段階と、

前記バリア絶縁層の上にコントロールゲート層を形成する段階とを含むことを特徴とする請求項39に記載の不揮発性メモリー素子の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060065040A KR100777348B1 (ko) | 2006-07-11 | 2006-07-11 | 비휘발성 기억 장치의 셀 어레이 구조 및 그 형성방법 |

| US11/729,169 US8045383B2 (en) | 2006-07-11 | 2007-03-28 | Non-volatile memory devices including dummy word lines and related structures and methods |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008022009A true JP2008022009A (ja) | 2008-01-31 |

| JP2008022009A5 JP2008022009A5 (ja) | 2010-08-19 |

Family

ID=38830888

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007182659A Pending JP2008022009A (ja) | 2006-07-11 | 2007-07-11 | 不揮発性メモリー素子及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2008022009A (ja) |

| DE (1) | DE102007031278B4 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8692310B2 (en) | 2009-02-09 | 2014-04-08 | Spansion Llc | Gate fringing effect based channel formation for semiconductor device |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10150170A (ja) * | 1996-11-14 | 1998-06-02 | Samsung Electron Co Ltd | 不揮発性メモリ装置 |

| JP2004127346A (ja) * | 2002-09-30 | 2004-04-22 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP2004241558A (ja) * | 2003-02-05 | 2004-08-26 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法、半導体集積回路及び不揮発性半導体記憶装置システム |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04212472A (ja) * | 1990-07-13 | 1992-08-04 | Toshiba Corp | 不揮発性半導体記憶装置の製造方法 |

| DE102005058601A1 (de) * | 2004-12-27 | 2006-07-06 | Hynix Semiconductor Inc., Icheon | Flash-Speicherbauelement |

-

2007

- 2007-07-05 DE DE102007031278A patent/DE102007031278B4/de active Active

- 2007-07-11 JP JP2007182659A patent/JP2008022009A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10150170A (ja) * | 1996-11-14 | 1998-06-02 | Samsung Electron Co Ltd | 不揮発性メモリ装置 |

| JP2004127346A (ja) * | 2002-09-30 | 2004-04-22 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP2004241558A (ja) * | 2003-02-05 | 2004-08-26 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法、半導体集積回路及び不揮発性半導体記憶装置システム |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102007031278B4 (de) | 2012-08-02 |

| DE102007031278A1 (de) | 2008-01-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8675409B2 (en) | Non-volatile memory devices | |

| US7247907B2 (en) | Bidirectional split gate NAND flash memory structure and array, method of programming, erasing and reading thereof, and method of manufacturing | |

| US8932955B1 (en) | Triple patterning NAND flash memory with SOC | |

| US20150064907A1 (en) | Triple Patterning NAND Flash Memory with Stepped Mandrel | |

| US8325529B2 (en) | Bit-line connections for non-volatile storage | |

| US10559581B2 (en) | Semiconductor device | |

| JP2004241558A (ja) | 不揮発性半導体記憶装置及びその製造方法、半導体集積回路及び不揮発性半導体記憶装置システム | |

| US9613806B2 (en) | Triple patterning NAND flash memory | |

| JP2009295781A (ja) | 半導体装置及びその製造方法 | |

| US7813203B2 (en) | Semiconductor memory device and method of manufacturing of the same | |

| JP2007227571A (ja) | 不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法 | |

| US9224744B1 (en) | Wide and narrow patterning using common process | |

| US20100151641A1 (en) | Semiconductor device and method for manufacturing the same | |

| US9543139B2 (en) | In-situ support structure for line collapse robustness in memory arrays | |

| US8741714B2 (en) | Support lines to prevent line collapse in arrays | |

| JP2003168750A (ja) | 半導体装置およびその製造方法 | |

| JP2009105375A (ja) | 不揮発性メモリ素子の動作方法 | |

| JP2011035169A (ja) | 不揮発性半導体記憶装置及びその製造方法 | |

| TW201841349A (zh) | 非揮發性快閃記憶體單元 | |

| JP2008022009A (ja) | 不揮発性メモリー素子及びその製造方法 | |

| JP2008108977A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| US20160358857A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2009016696A (ja) | 半導体装置及びその製造方法 | |

| US7125807B2 (en) | Method for manufacturing non-volatile memory cells on a semiconductor substrate | |

| JP2009253037A (ja) | 半導体装置及び半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100706 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120920 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120925 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130212 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130723 |