JP2008016444A - Manufacturing method of semiconductor device - Google Patents

Manufacturing method of semiconductor device Download PDFInfo

- Publication number

- JP2008016444A JP2008016444A JP2007147166A JP2007147166A JP2008016444A JP 2008016444 A JP2008016444 A JP 2008016444A JP 2007147166 A JP2007147166 A JP 2007147166A JP 2007147166 A JP2007147166 A JP 2007147166A JP 2008016444 A JP2008016444 A JP 2008016444A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- film

- light

- insulating layer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 102

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 48

- 239000000463 material Substances 0.000 claims abstract description 130

- 239000000758 substrate Substances 0.000 claims abstract description 49

- 229920005989 resin Polymers 0.000 claims abstract description 45

- 239000011347 resin Substances 0.000 claims abstract description 45

- 229920001187 thermosetting polymer Polymers 0.000 claims abstract description 6

- 238000003825 pressing Methods 0.000 claims abstract description 4

- 238000000034 method Methods 0.000 claims description 91

- 238000005192 partition Methods 0.000 claims description 80

- 238000010438 heat treatment Methods 0.000 claims description 14

- 239000011810 insulating material Substances 0.000 claims description 6

- 229920005992 thermoplastic resin Polymers 0.000 claims description 6

- 239000007769 metal material Substances 0.000 claims description 4

- 230000004888 barrier function Effects 0.000 abstract description 7

- 239000010408 film Substances 0.000 description 213

- 239000010410 layer Substances 0.000 description 206

- 239000012535 impurity Substances 0.000 description 75

- 239000002585 base Substances 0.000 description 38

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 34

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 28

- 229910052814 silicon oxide Inorganic materials 0.000 description 23

- 150000001875 compounds Chemical class 0.000 description 22

- 238000002347 injection Methods 0.000 description 21

- 239000007924 injection Substances 0.000 description 21

- 238000012545 processing Methods 0.000 description 21

- 229910052757 nitrogen Inorganic materials 0.000 description 18

- 238000004544 sputter deposition Methods 0.000 description 18

- 239000011230 binding agent Substances 0.000 description 17

- 239000010949 copper Substances 0.000 description 17

- 239000011229 interlayer Substances 0.000 description 17

- 229910052581 Si3N4 Inorganic materials 0.000 description 16

- 239000000460 chlorine Substances 0.000 description 16

- 229910052760 oxygen Inorganic materials 0.000 description 16

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 16

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 15

- 239000001301 oxygen Substances 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 14

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 14

- 229910052751 metal Inorganic materials 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 14

- 239000010703 silicon Substances 0.000 description 14

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 13

- 229910052782 aluminium Inorganic materials 0.000 description 13

- 238000005229 chemical vapour deposition Methods 0.000 description 13

- 239000007789 gas Substances 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 238000007740 vapor deposition Methods 0.000 description 13

- 239000000956 alloy Substances 0.000 description 12

- -1 polypropylene Polymers 0.000 description 12

- 239000010409 thin film Substances 0.000 description 12

- 229910045601 alloy Inorganic materials 0.000 description 11

- 239000002245 particle Substances 0.000 description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 230000005540 biological transmission Effects 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 10

- 238000010304 firing Methods 0.000 description 10

- 150000002894 organic compounds Chemical class 0.000 description 10

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 9

- UCKMPCXJQFINFW-UHFFFAOYSA-N Sulphide Chemical compound [S-2] UCKMPCXJQFINFW-UHFFFAOYSA-N 0.000 description 9

- 229910052802 copper Inorganic materials 0.000 description 9

- 230000005525 hole transport Effects 0.000 description 9

- 239000001257 hydrogen Substances 0.000 description 9

- 229910052739 hydrogen Inorganic materials 0.000 description 9

- 229910010272 inorganic material Inorganic materials 0.000 description 9

- 239000000243 solution Substances 0.000 description 9

- 230000005236 sound signal Effects 0.000 description 9

- 239000013078 crystal Substances 0.000 description 8

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 8

- 239000012212 insulator Substances 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 230000006798 recombination Effects 0.000 description 8

- 238000005215 recombination Methods 0.000 description 8

- 238000003746 solid phase reaction Methods 0.000 description 8

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 7

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 229910052731 fluorine Inorganic materials 0.000 description 7

- 239000011737 fluorine Substances 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 6

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 6

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 6

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 6

- XJHCXCQVJFPJIK-UHFFFAOYSA-M caesium fluoride Chemical compound [F-].[Cs+] XJHCXCQVJFPJIK-UHFFFAOYSA-M 0.000 description 6

- 229910052799 carbon Inorganic materials 0.000 description 6

- 229910052801 chlorine Inorganic materials 0.000 description 6

- 229910052733 gallium Inorganic materials 0.000 description 6

- 229910003437 indium oxide Inorganic materials 0.000 description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 6

- 239000007791 liquid phase Substances 0.000 description 6

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical compound C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 6

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 239000011241 protective layer Substances 0.000 description 6

- 238000010532 solid phase synthesis reaction Methods 0.000 description 6

- 125000001424 substituent group Chemical group 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- 239000005083 Zinc sulfide Substances 0.000 description 5

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 239000011147 inorganic material Substances 0.000 description 5

- 239000004570 mortar (masonry) Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 239000011368 organic material Substances 0.000 description 5

- 239000010453 quartz Substances 0.000 description 5

- 239000004332 silver Substances 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 229910052984 zinc sulfide Inorganic materials 0.000 description 5

- SKJCKYVIQGBWTN-UHFFFAOYSA-N (4-hydroxyphenyl) methanesulfonate Chemical compound CS(=O)(=O)OC1=CC=C(O)C=C1 SKJCKYVIQGBWTN-UHFFFAOYSA-N 0.000 description 4

- PFNQVRZLDWYSCW-UHFFFAOYSA-N (fluoren-9-ylideneamino) n-naphthalen-1-ylcarbamate Chemical compound C12=CC=CC=C2C2=CC=CC=C2C1=NOC(=O)NC1=CC=CC2=CC=CC=C12 PFNQVRZLDWYSCW-UHFFFAOYSA-N 0.000 description 4

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910052783 alkali metal Inorganic materials 0.000 description 4

- 150000001340 alkali metals Chemical class 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 238000003877 atomic layer epitaxy Methods 0.000 description 4

- 229910052788 barium Inorganic materials 0.000 description 4

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 4

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 4

- JGIATAMCQXIDNZ-UHFFFAOYSA-N calcium sulfide Chemical compound [Ca]=S JGIATAMCQXIDNZ-UHFFFAOYSA-N 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000000975 co-precipitation Methods 0.000 description 4

- 229910017052 cobalt Inorganic materials 0.000 description 4

- 239000010941 cobalt Substances 0.000 description 4

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 4

- 238000002425 crystallisation Methods 0.000 description 4

- 230000008025 crystallization Effects 0.000 description 4

- 238000001723 curing Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 125000001153 fluoro group Chemical group F* 0.000 description 4

- 150000002484 inorganic compounds Chemical class 0.000 description 4

- 239000011777 magnesium Substances 0.000 description 4

- 239000011572 manganese Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 125000000962 organic group Chemical group 0.000 description 4

- 230000010355 oscillation Effects 0.000 description 4

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 4

- 239000008188 pellet Substances 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 239000000843 powder Substances 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- YLYPIBBGWLKELC-RMKNXTFCSA-N 2-[2-[(e)-2-[4-(dimethylamino)phenyl]ethenyl]-6-methylpyran-4-ylidene]propanedinitrile Chemical compound C1=CC(N(C)C)=CC=C1\C=C\C1=CC(=C(C#N)C#N)C=C(C)O1 YLYPIBBGWLKELC-RMKNXTFCSA-N 0.000 description 3

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 3

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical compound C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 3

- 150000001342 alkaline earth metals Chemical class 0.000 description 3

- 239000007864 aqueous solution Substances 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052791 calcium Inorganic materials 0.000 description 3

- 239000011575 calcium Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 229910052736 halogen Inorganic materials 0.000 description 3

- 150000002367 halogens Chemical class 0.000 description 3

- 238000005499 laser crystallization Methods 0.000 description 3

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 239000012788 optical film Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 229910052712 strontium Inorganic materials 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 2

- ZVFQEOPUXVPSLB-UHFFFAOYSA-N 3-(4-tert-butylphenyl)-4-phenyl-5-(4-phenylphenyl)-1,2,4-triazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C(N1C=2C=CC=CC=2)=NN=C1C1=CC=C(C=2C=CC=CC=2)C=C1 ZVFQEOPUXVPSLB-UHFFFAOYSA-N 0.000 description 2

- MBXOOYPCIDHXGH-UHFFFAOYSA-N 3-butylpentane-2,4-dione Chemical compound CCCCC(C(C)=O)C(C)=O MBXOOYPCIDHXGH-UHFFFAOYSA-N 0.000 description 2

- DHDHJYNTEFLIHY-UHFFFAOYSA-N 4,7-diphenyl-1,10-phenanthroline Chemical compound C1=CC=CC=C1C1=CC=NC2=C1C=CC1=C(C=3C=CC=CC=3)C=CN=C21 DHDHJYNTEFLIHY-UHFFFAOYSA-N 0.000 description 2

- SCZWJXTUYYSKGF-UHFFFAOYSA-N 5,12-dimethylquinolino[2,3-b]acridine-7,14-dione Chemical compound CN1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3N(C)C1=C2 SCZWJXTUYYSKGF-UHFFFAOYSA-N 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 229910004261 CaF 2 Inorganic materials 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 2

- 229910052684 Cerium Inorganic materials 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 229910052691 Erbium Inorganic materials 0.000 description 2

- 229910052693 Europium Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 2

- 229920000877 Melamine resin Polymers 0.000 description 2

- 101100476480 Mus musculus S100a8 gene Proteins 0.000 description 2

- ZCQWOFVYLHDMMC-UHFFFAOYSA-N Oxazole Chemical compound C1=COC=N1 ZCQWOFVYLHDMMC-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004695 Polyether sulfone Substances 0.000 description 2

- 239000004743 Polypropylene Substances 0.000 description 2

- 239000004372 Polyvinyl alcohol Substances 0.000 description 2

- 229910052777 Praseodymium Inorganic materials 0.000 description 2

- 229910052772 Samarium Inorganic materials 0.000 description 2

- 229910052771 Terbium Inorganic materials 0.000 description 2

- 229910052775 Thulium Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 239000007983 Tris buffer Substances 0.000 description 2

- WIHRQSPNTXGILI-UHFFFAOYSA-N [O-2].[In+3].[W+2]=O Chemical compound [O-2].[In+3].[W+2]=O WIHRQSPNTXGILI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 229910052946 acanthite Inorganic materials 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- COOGPNLGKIHLSK-UHFFFAOYSA-N aluminium sulfide Chemical compound [Al+3].[Al+3].[S-2].[S-2].[S-2] COOGPNLGKIHLSK-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 2

- 125000003118 aryl group Chemical group 0.000 description 2

- NWAIGJYBQQYSPW-UHFFFAOYSA-N azanylidyneindigane Chemical compound [In]#N NWAIGJYBQQYSPW-UHFFFAOYSA-N 0.000 description 2

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 2

- 229910002113 barium titanate Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 150000004696 coordination complex Chemical class 0.000 description 2

- OXBLHERUFWYNTN-UHFFFAOYSA-M copper(I) chloride Chemical compound [Cu]Cl OXBLHERUFWYNTN-UHFFFAOYSA-M 0.000 description 2

- AQKDYYAZGHBAPR-UHFFFAOYSA-M copper;copper(1+);sulfanide Chemical compound [SH-].[Cu].[Cu+] AQKDYYAZGHBAPR-UHFFFAOYSA-M 0.000 description 2

- VBVAVBCYMYWNOU-UHFFFAOYSA-N coumarin 6 Chemical compound C1=CC=C2SC(C3=CC4=CC=C(C=C4OC3=O)N(CC)CC)=NC2=C1 VBVAVBCYMYWNOU-UHFFFAOYSA-N 0.000 description 2

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 2

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 239000010419 fine particle Substances 0.000 description 2

- 238000004108 freeze drying Methods 0.000 description 2

- BVSHTEBQPBBCFT-UHFFFAOYSA-N gallium(iii) sulfide Chemical compound [S-2].[S-2].[S-2].[Ga+3].[Ga+3] BVSHTEBQPBBCFT-UHFFFAOYSA-N 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- 150000004678 hydrides Chemical class 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- 229910052744 lithium Inorganic materials 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910021645 metal ion Inorganic materials 0.000 description 2

- 238000005649 metathesis reaction Methods 0.000 description 2

- 239000000693 micelle Substances 0.000 description 2

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- 229920003986 novolac Polymers 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- JMANVNJQNLATNU-UHFFFAOYSA-N oxalonitrile Chemical compound N#CC#N JMANVNJQNLATNU-UHFFFAOYSA-N 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920006393 polyether sulfone Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920001155 polypropylene Polymers 0.000 description 2

- 229920002451 polyvinyl alcohol Polymers 0.000 description 2

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- LLHKCFNBLRBOGN-UHFFFAOYSA-N propylene glycol methyl ether acetate Chemical compound COCC(C)OC(C)=O LLHKCFNBLRBOGN-UHFFFAOYSA-N 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 239000010979 ruby Substances 0.000 description 2

- 229910001750 ruby Inorganic materials 0.000 description 2

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 2

- HKZLPVFGJNLROG-UHFFFAOYSA-M silver monochloride Chemical compound [Cl-].[Ag+] HKZLPVFGJNLROG-UHFFFAOYSA-M 0.000 description 2

- 229940056910 silver sulfide Drugs 0.000 description 2

- XUARKZBEFFVFRG-UHFFFAOYSA-N silver sulfide Chemical compound [S-2].[Ag+].[Ag+] XUARKZBEFFVFRG-UHFFFAOYSA-N 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 238000005118 spray pyrolysis Methods 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 2

- XXCMBPUMZXRBTN-UHFFFAOYSA-N strontium sulfide Chemical compound [Sr]=S XXCMBPUMZXRBTN-UHFFFAOYSA-N 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 2

- 238000005979 thermal decomposition reaction Methods 0.000 description 2

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- TVIVIEFSHFOWTE-UHFFFAOYSA-K tri(quinolin-8-yloxy)alumane Chemical compound [Al+3].C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1 TVIVIEFSHFOWTE-UHFFFAOYSA-K 0.000 description 2

- DRDVZXDWVBGGMH-UHFFFAOYSA-N zinc;sulfide Chemical compound [S-2].[Zn+2] DRDVZXDWVBGGMH-UHFFFAOYSA-N 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- BQCIDUSAKPWEOX-UHFFFAOYSA-N 1,1-Difluoroethene Chemical compound FC(F)=C BQCIDUSAKPWEOX-UHFFFAOYSA-N 0.000 description 1

- BCMCBBGGLRIHSE-UHFFFAOYSA-N 1,3-benzoxazole Chemical class C1=CC=C2OC=NC2=C1 BCMCBBGGLRIHSE-UHFFFAOYSA-N 0.000 description 1

- KXJGSNRAQWDDJT-UHFFFAOYSA-N 1-acetyl-5-bromo-2h-indol-3-one Chemical compound BrC1=CC=C2N(C(=O)C)CC(=O)C2=C1 KXJGSNRAQWDDJT-UHFFFAOYSA-N 0.000 description 1

- ARXJGSRGQADJSQ-UHFFFAOYSA-N 1-methoxypropan-2-ol Chemical compound COCC(C)O ARXJGSRGQADJSQ-UHFFFAOYSA-N 0.000 description 1

- STTGYIUESPWXOW-UHFFFAOYSA-N 2,9-dimethyl-4,7-diphenyl-1,10-phenanthroline Chemical compound C=12C=CC3=C(C=4C=CC=CC=4)C=C(C)N=C3C2=NC(C)=CC=1C1=CC=CC=C1 STTGYIUESPWXOW-UHFFFAOYSA-N 0.000 description 1

- UOCMXZLNHQBBOS-UHFFFAOYSA-N 2-(1,3-benzoxazol-2-yl)phenol zinc Chemical compound [Zn].Oc1ccccc1-c1nc2ccccc2o1.Oc1ccccc1-c1nc2ccccc2o1 UOCMXZLNHQBBOS-UHFFFAOYSA-N 0.000 description 1

- FQJQNLKWTRGIEB-UHFFFAOYSA-N 2-(4-tert-butylphenyl)-5-[3-[5-(4-tert-butylphenyl)-1,3,4-oxadiazol-2-yl]phenyl]-1,3,4-oxadiazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=C(C=CC=2)C=2OC(=NN=2)C=2C=CC(=CC=2)C(C)(C)C)O1 FQJQNLKWTRGIEB-UHFFFAOYSA-N 0.000 description 1

- HONWGFNQCPRRFM-UHFFFAOYSA-N 2-n-(3-methylphenyl)-1-n,1-n,2-n-triphenylbenzene-1,2-diamine Chemical compound CC1=CC=CC(N(C=2C=CC=CC=2)C=2C(=CC=CC=2)N(C=2C=CC=CC=2)C=2C=CC=CC=2)=C1 HONWGFNQCPRRFM-UHFFFAOYSA-N 0.000 description 1

- MFKRHJVUCZRDTF-UHFFFAOYSA-N 3-methoxy-3-methylbutan-1-ol Chemical compound COC(C)(C)CCO MFKRHJVUCZRDTF-UHFFFAOYSA-N 0.000 description 1

- OGGKVJMNFFSDEV-UHFFFAOYSA-N 3-methyl-n-[4-[4-(n-(3-methylphenyl)anilino)phenyl]phenyl]-n-phenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 OGGKVJMNFFSDEV-UHFFFAOYSA-N 0.000 description 1

- 125000004860 4-ethylphenyl group Chemical group [H]C1=C([H])C(=C([H])C([H])=C1*)C([H])([H])C([H])([H])[H] 0.000 description 1

- NSPMIYGKQJPBQR-UHFFFAOYSA-N 4H-1,2,4-triazole Chemical compound C=1N=CNN=1 NSPMIYGKQJPBQR-UHFFFAOYSA-N 0.000 description 1

- WSMQKESQZFQMFW-UHFFFAOYSA-N 5-methyl-pyrazole-3-carboxylic acid Chemical compound CC1=CC(C(O)=O)=NN1 WSMQKESQZFQMFW-UHFFFAOYSA-N 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 239000004641 Diallyl-phthalate Substances 0.000 description 1

- 241001175904 Labeo bata Species 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 239000004640 Melamine resin Substances 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- 239000004693 Polybenzimidazole Substances 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- 238000001237 Raman spectrum Methods 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- PJANXHGTPQOBST-VAWYXSNFSA-N Stilbene Natural products C=1C=CC=CC=1/C=C/C1=CC=CC=C1 PJANXHGTPQOBST-VAWYXSNFSA-N 0.000 description 1

- FZWLAAWBMGSTSO-UHFFFAOYSA-N Thiazole Chemical compound C1=CSC=N1 FZWLAAWBMGSTSO-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- XTXRWKRVRITETP-UHFFFAOYSA-N Vinyl acetate Chemical compound CC(=O)OC=C XTXRWKRVRITETP-UHFFFAOYSA-N 0.000 description 1

- BZHJMEDXRYGGRV-UHFFFAOYSA-N Vinyl chloride Chemical compound ClC=C BZHJMEDXRYGGRV-UHFFFAOYSA-N 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- XHCLAFWTIXFWPH-UHFFFAOYSA-N [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[V+5].[V+5] XHCLAFWTIXFWPH-UHFFFAOYSA-N 0.000 description 1

- AZWHFTKIBIQKCA-UHFFFAOYSA-N [Sn+2]=O.[O-2].[In+3] Chemical compound [Sn+2]=O.[O-2].[In+3] AZWHFTKIBIQKCA-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- MQRWBMAEBQOWAF-UHFFFAOYSA-N acetic acid;nickel Chemical compound [Ni].CC(O)=O.CC(O)=O MQRWBMAEBQOWAF-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 150000001341 alkaline earth metal compounds Chemical class 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- BJXXCWDIBHXWOH-UHFFFAOYSA-N barium(2+);oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Ba+2].[Ba+2].[Ba+2].[Ba+2].[Ba+2].[Ta+5].[Ta+5].[Ta+5].[Ta+5] BJXXCWDIBHXWOH-UHFFFAOYSA-N 0.000 description 1

- WZJYKHNJTSNBHV-UHFFFAOYSA-N benzo[h]quinoline Chemical group C1=CN=C2C3=CC=CC=C3C=CC2=C1 WZJYKHNJTSNBHV-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- GQVWHWAWLPCBHB-UHFFFAOYSA-L beryllium;benzo[h]quinolin-10-olate Chemical compound [Be+2].C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21.C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21 GQVWHWAWLPCBHB-UHFFFAOYSA-L 0.000 description 1

- QUDWYFHPNIMBFC-UHFFFAOYSA-N bis(prop-2-enyl) benzene-1,2-dicarboxylate Chemical compound C=CCOC(=O)C1=CC=CC=C1C(=O)OCC=C QUDWYFHPNIMBFC-UHFFFAOYSA-N 0.000 description 1

- UFVXQDWNSAGPHN-UHFFFAOYSA-K bis[(2-methylquinolin-8-yl)oxy]-(4-phenylphenoxy)alumane Chemical compound [Al+3].C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC([O-])=CC=C1C1=CC=CC=C1 UFVXQDWNSAGPHN-UHFFFAOYSA-K 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- XZCJVWCMJYNSQO-UHFFFAOYSA-N butyl pbd Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=CC(=CC=2)C=2C=CC=CC=2)O1 XZCJVWCMJYNSQO-UHFFFAOYSA-N 0.000 description 1

- QHIWVLPBUQWDMQ-UHFFFAOYSA-N butyl prop-2-enoate;methyl 2-methylprop-2-enoate;prop-2-enoic acid Chemical compound OC(=O)C=C.COC(=O)C(C)=C.CCCCOC(=O)C=C QHIWVLPBUQWDMQ-UHFFFAOYSA-N 0.000 description 1

- UIZLQMLDSWKZGC-UHFFFAOYSA-N cadmium helium Chemical compound [He].[Cd] UIZLQMLDSWKZGC-UHFFFAOYSA-N 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000012461 cellulose resin Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000002274 desiccant Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910000078 germane Inorganic materials 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000003446 ligand Substances 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000000113 methacrylic resin Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 229940078494 nickel acetate Drugs 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 125000002524 organometallic group Chemical group 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920002480 polybenzimidazole Polymers 0.000 description 1

- 229920002577 polybenzoxazole Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920013716 polyethylene resin Polymers 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 229920005990 polystyrene resin Polymers 0.000 description 1

- 229940005642 polystyrene sulfonic acid Drugs 0.000 description 1

- UKDIAJWKFXFVFG-UHFFFAOYSA-N potassium;oxido(dioxo)niobium Chemical compound [K+].[O-][Nb](=O)=O UKDIAJWKFXFVFG-UHFFFAOYSA-N 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000010298 pulverizing process Methods 0.000 description 1

- 125000002943 quinolinyl group Chemical group N1=C(C=CC2=CC=CC=C12)* 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 150000002910 rare earth metals Chemical class 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 1

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- PJANXHGTPQOBST-UHFFFAOYSA-N stilbene Chemical compound C=1C=CC=CC=1C=CC1=CC=CC=C1 PJANXHGTPQOBST-UHFFFAOYSA-N 0.000 description 1

- 235000021286 stilbenes Nutrition 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 229910001935 vanadium oxide Inorganic materials 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- GWDUZCIBPDVBJM-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzothiazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1 GWDUZCIBPDVBJM-UHFFFAOYSA-L 0.000 description 1

- QEPMORHSGFRDLW-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzoxazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1 QEPMORHSGFRDLW-UHFFFAOYSA-L 0.000 description 1

Images

Abstract

Description

本発明は、半導体装置及びその作製方法に関するものである。 The present invention relates to a semiconductor device and a manufacturing method thereof.

発光層を含む層を一対の電極間に有し、当該電極間に電流を流すことで発光する発光素子を用いた発光装置の開発が進められている。このような発光装置は他の薄型表示装置と呼ばれる表示装置と比較して薄型軽量化に有利であり、自発光であるため視認性も良く、応答速度も速い。そのため、次世代の表示装置として盛んに開発が進められ、一部実用化もなされている。 Development of a light-emitting device using a light-emitting element that has a light-emitting layer between a pair of electrodes and emits light by passing a current between the electrodes is underway. Such a light-emitting device is advantageous in reducing the thickness and weight as compared to other display devices called thin display devices, and since it is self-luminous, it has good visibility and quick response. For this reason, development has been actively promoted as a next-generation display device, and some of the devices have been put into practical use.

上記のような発光装置として、エレクトロルミネセンス(Electro Luminescence、以下「EL」ともいう)と呼ばれる発光を発現する有機物、無機物、若しくは有機物と無機物の混合物を含む層を、電極間に介在させた発光素子と薄膜トランジスタ(Thin Film Transistor(TFT))とが接続された発光表示装置がある。 As a light-emitting device as described above, light emission in which an organic substance, an inorganic substance, or a mixture containing an organic substance and an inorganic substance that emits light called electroluminescence (hereinafter also referred to as “EL”) is interposed between electrodes. There is a light-emitting display device in which an element and a thin film transistor (TFT) are connected.

エレクトロルミネセンス素子(EL素子)は、高輝度で発光させることができるため、刺激的な多彩な画像を表示することができる。発光素子より得られる発光は、例えば輝度100cd/m2〜10000cd/m2と高い。発光表示装置は、応答が早く、自発光表示なので表示装置の薄型化、軽量化ができる利点がある。本発明で適用することのできるエレクトロルミネセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。 Since an electroluminescent element (EL element) can emit light with high luminance, it can display a variety of exciting images. Emission obtained from the light emitting element, for example, high luminance 100cd / m 2 ~10000cd / m 2 . The light-emitting display device has an advantage that the display device can be thinned and light-weighted because of its quick response and self-luminous display. A light emitting element using electroluminescence that can be applied in the present invention is distinguished depending on whether the light emitting material is an organic compound or an inorganic compound. Generally, the former is an organic EL element, and the latter is an inorganic EL element. It is called an element.

EL素子の画素を区切る材料(以下、隔壁と標記する)には、樹脂材料が用いられている(特許文献1参照)。このような樹脂材料は、ドライエッチングまたはウェットエッチングによりパターン形成されたり、あるいは樹脂そのものに感光性を付与し、露光・現像処理を行うことによりパターン形成されることもある。

ドライエッチングまたはウェットエッチングにより隔壁を形成すると、隔壁の長さが基板ごとに変わってしまう、また同一基板にあっても、素子ごとに変わってしまうという欠点がある。 When the partition walls are formed by dry etching or wet etching, there is a drawback that the length of the partition wall changes for each substrate, and even for the same substrate, it changes for each element.

またドライエッチングまたはウェットエッチングにより隔壁を形成する方法では、隔壁のテーパー角を意図的に制御して作製することが難しい。 Further, in the method of forming the partition wall by dry etching or wet etching, it is difficult to manufacture the partition wall by intentionally controlling the taper angle of the partition wall.

隔壁のテーパー角が大きくなりすぎると、その上に形成される膜の膜厚が薄くなるため、ショートなどの原因になりやすいという恐れがある。また、隔壁上の膜の膜厚が薄いと、その膜の物理的強度が小さくなる可能性がある。さらに隔壁のテーパー角が大きすぎると、そこから水分が侵入してきてしまう可能性がある。 If the taper angle of the partition wall is too large, the film formed on the partition wall becomes thin, which may cause a short circuit. In addition, when the film thickness on the partition is thin, the physical strength of the film may be reduced. Furthermore, if the taper angle of the partition wall is too large, moisture may enter from there.

また、隔壁の底部及び頂部のエッジ(縁)が丸みを帯びていないと、その上に形成される膜も丸みを帯びることがなくなる、そのため隔壁の上に形成される膜が断裂を起こす恐れがあり、断裂が発生してしまうと、そこから水分が侵入する可能性や、ショートを起こしてしまう可能性がある。 Also, if the bottom and top edges of the partition walls are not rounded, the film formed thereon will not be rounded, so that the film formed on the partition walls may be ruptured. Yes, if tearing occurs, there is a possibility that moisture may enter from there or a short circuit may occur.

隔壁の底部及び頂部のエッジが丸みを帯びていない例を、図22(B)に示す。図22(B)に示す半導体装置は、角張った形状を有する隔壁1051a及び1051b、その間に開口部1052を有している。また隔壁1051a及び1051bの端部はそれぞれテーパー角φを有している。このような形状では、上記のように水分が侵入する可能性や、ショートを起こしてしまう可能性がある。

An example in which the edges of the bottom and top of the partition are not rounded is illustrated in FIG. A semiconductor device illustrated in FIG. 22B includes

本発明は、樹脂材料から隔壁を形成する際に、ナノインプリント法を用い、断面テーパー角が20°以上50°以下であり、かつ底部及び頂部のエッジ(縁)が丸みを帯びている形状、すなわち曲面を有する形状の隔壁を再現性よく作製することを特徴とする。 The present invention uses a nanoimprint method when forming a partition wall from a resin material, has a cross-section taper angle of 20 ° to 50 °, and has a round shape at the bottom and top edges (edges), that is, A partition wall having a curved surface is manufactured with high reproducibility.

本発明の素子を区切る隔壁は、例えば以下のようにして形成される。 The partition which divides the element of this invention is formed as follows, for example.

素子が形成された基板上に樹脂材料を均一に成膜し、熱インプリント法や光インプリント法で、樹脂材料に鋳型(モールドともいう)を押しつける(押圧する)。次いでモールドを剥離し、必要であれば、残った樹脂材料を酸素プラズマ等で除去する。次いで必要ならば所定の形状に成形された樹脂材料を、加熱や光照射等によって完全に硬化する。以上により隔壁が形成される。 A resin material is uniformly formed on the substrate on which the element is formed, and a mold (also referred to as a mold) is pressed (pressed) against the resin material by a thermal imprint method or an optical imprint method. Next, the mold is peeled off, and if necessary, the remaining resin material is removed with oxygen plasma or the like. Next, if necessary, the resin material molded into a predetermined shape is completely cured by heating, light irradiation, or the like. A partition is formed by the above.

ナノインプリント法を用いて隔壁を形成すると、ステッパ装置を用いる方法と同じ程度の精度、すなわちナノメーター(nm)の精度で隔壁を形成することが可能となる。またナノインプリント法では、モールド(鋳型)を用いて隔壁を形成するため、複数の隔壁を再現性よく形成することができ、バラツキが少なく、作製コストも低くすることが可能である。 When the barrier ribs are formed using the nanoimprint method, the barrier ribs can be formed with the same accuracy as the method using the stepper device, that is, the accuracy of nanometers (nm). In the nanoimprint method, a partition is formed by using a mold, so that a plurality of partitions can be formed with good reproducibility, and there is little variation and the manufacturing cost can be reduced.

本発明は、基板上に、第1の電極を形成し、前記基板及び前記第1の電極上に、熱可塑型樹脂材料または熱硬化型樹脂材料を含む絶縁層を形成し、前記絶縁層にモールドを押圧し、前記第1の電極上の前記絶縁層中に開口部を形成し、前記開口部の形成された絶縁層から、前記モールドを取り外し、前記モールドを取り外した後、前記開口部の形成された絶縁層を硬化させて隔壁を形成し、前記第1の電極及び前記隔壁上に、発光層を形成し、前記発光層上に、第2の電極を形成することを特徴とする半導体装置の作製方法に関するものである。 In the present invention, a first electrode is formed on a substrate, an insulating layer containing a thermoplastic resin material or a thermosetting resin material is formed on the substrate and the first electrode, and the insulating layer is formed on the insulating layer. The mold is pressed, an opening is formed in the insulating layer on the first electrode, the mold is removed from the insulating layer in which the opening is formed, the mold is removed, and then the opening is formed. The insulating layer formed is hardened to form a partition, a light emitting layer is formed on the first electrode and the partition, and a second electrode is formed on the light emitting layer The present invention relates to a method for manufacturing a device.

本発明において、前記絶縁層は、加熱によって硬化されるものである。 In the present invention, the insulating layer is cured by heating.

本発明は、基板上に、第1の電極を形成し、前記基板及び前記第1の電極上に、光硬化型樹脂材料を含む絶縁層を形成し、前記絶縁層にモールドを押圧し、前記第1の電極上の前記絶縁層中に開口部を形成し、前記開口部の形成された絶縁層から、前記モールドを取り外し、前記開口部の形成された絶縁層を硬化させて隔壁を形成し、前記第1の電極及び前記隔壁上に、発光層を形成し、前記発光層上に、第2の電極を形成することを特徴とする半導体装置の作製方法に関するものである。 In the present invention, a first electrode is formed on a substrate, an insulating layer containing a photocurable resin material is formed on the substrate and the first electrode, a mold is pressed against the insulating layer, An opening is formed in the insulating layer on the first electrode, the mold is removed from the insulating layer in which the opening is formed, and a partition is formed by curing the insulating layer in which the opening is formed. The present invention relates to a method for manufacturing a semiconductor device, wherein a light emitting layer is formed over the first electrode and the partition, and a second electrode is formed over the light emitting layer.

本発明において、前記絶縁層は、光照射によって硬化されるものである。 In the present invention, the insulating layer is cured by light irradiation.

本発明において、前記モールドは、金属材料または絶縁材料により形成されており、前記モールドの表面には凹凸が形成されているものを用いる。 In the present invention, the mold is formed of a metal material or an insulating material, and a mold having irregularities formed on the surface of the mold is used.

本発明において、前記隔壁は、断面テーパー角が20°以上50°以下であり、かつ前記隔壁の底部及び頂部のエッジが曲面を有する形状を有しているものを用いる。 In the present invention, the partition wall has a cross-sectional taper angle of 20 ° or more and 50 ° or less, and has a shape in which the bottom and top edges of the partition wall have curved surfaces.

なお本明細書において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、半導体素子を含む発光装置等を含む電気光学装置およびその電気光学装置を搭載した電子機器をその範疇とする。 Note that in this specification, a semiconductor device refers to all elements and devices that function by using a semiconductor, and includes an electro-optical device including a light-emitting device including a semiconductor element and an electronic device including the electro-optical device. Category.

本発明により、樹脂材料を用いた隔壁が簡便な方法で再現性よく作製できる。これにより、バラツキが少なく、コストの低い発光表示装置を作製することができる。 According to the present invention, a partition wall using a resin material can be manufactured with a simple method and good reproducibility. Thus, a light-emitting display device with low variation and low cost can be manufactured.

また隔壁のテーパー角が20°〜50°と大きすぎないため、隔壁上に形成される膜の膜厚が薄くなることを防ぐことができる。そのため隔壁上の膜の物理強度が小さくなることを回避できる。 In addition, since the taper angle of the partition wall is not so large as 20 ° to 50 °, it is possible to prevent the film formed on the partition wall from being thinned. Therefore, it can be avoided that the physical strength of the film on the partition wall is reduced.

また隔壁の底部及び頂部のエッジが丸みを帯びることで、すなわち隔壁の底部及び頂部のエッジが曲面を有する形状を有することで、隔壁上に形成される膜の断裂を防ぐことができる。 In addition, since the bottom and top edges of the partition walls are rounded, that is, the bottom and top edges of the partition walls have a curved surface, the film formed on the partition walls can be prevented from being broken.

隔壁のテーパー角が20°以上50°以下であること、隔壁の底部及び頂部のエッジが丸みを帯びることにより、水分の侵入を防ぎ、またショートを回避することが可能となる。以上により、信頼性の高い発光表示装置を得ることが可能となる。 When the taper angle of the partition is 20 ° or more and 50 ° or less, and the bottom and top edges of the partition are rounded, it is possible to prevent moisture from entering and avoid short circuit. Thus, a highly reliable light-emitting display device can be obtained.

以下、本発明の実施の態様について、図面を参照して説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings. However, the present invention can be implemented in many different modes, and those skilled in the art can easily understand that the modes and details can be variously changed without departing from the spirit and scope of the present invention. Is done. Therefore, the present invention is not construed as being limited to the description of this embodiment mode. Note that in the drawings described below, the same portions or portions having similar functions are denoted by the same reference numerals, and repetitive description thereof is omitted.

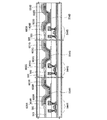

本実施の形態では、本発明を用いて発光表示装置の発光素子を作製する工程について、図1(A)〜図1(B)、図2(A)〜図2(B)、図3(A)〜図3(C)を用いて説明する。 In this embodiment mode, a process for manufacturing a light-emitting element of a light-emitting display device using the present invention will be described with reference to FIGS. 1A to 1B, FIGS. 2A to 2B, and FIG. A) to FIG. 3C will be described.

まず、基板101上に第1の電極102(102a、102b、102c、102d、等)を形成する(図1(A)参照)。基板101としては、例えば、ガラス、石英などを用いることができる。なお第1の電極102を形成する前に、基板101上に下地絶縁膜を形成してもよい。

First, the first electrode 102 (102a, 102b, 102c, 102d, or the like) is formed over the substrate 101 (see FIG. 1A). As the

第1の電極102及び後の工程で形成される第2の電極114(114a、114b、114c、114d、等)は、金属、合金、導電性化合物、及びこれらの混合物などを用いることができる。具体的には、例えば、酸化インジウム−酸化スズ(Indium Tin Oxide(「ITO」ともいう))、珪素若しくは酸化珪素を含有した酸化インジウム−酸化スズ、酸化インジウム−酸化亜鉛(Indium Zinc Oxide(「IZO」ともいう))、酸化タングステン及び酸化亜鉛を含む酸化タングステン−酸化インジウム等が挙げられる。これらの導電性金属酸化物膜は、通常スパッタリングにより成膜される。例えば、酸化インジウム−酸化亜鉛(IZO)は、酸化インジウムに対し1〜20wt%の酸化亜鉛を加えたターゲットを用いたスパッタリングにより形成することができる。また、酸化亜鉛を含む酸化タングステン−酸化インジウムは、酸化インジウムに対し酸化タングステンを0.5〜5wt%、酸化亜鉛を0.1〜1wt%含有したターゲットを用いたスパッタリングにより形成することができる。 For the first electrode 102 and the second electrode 114 (114a, 114b, 114c, 114d, and the like) formed in a later step, a metal, an alloy, a conductive compound, a mixture thereof, or the like can be used. Specifically, for example, indium tin oxide (also referred to as “ITO”), indium oxide-tin oxide containing silicon or silicon oxide, indium zinc oxide (“IZO”). And tungsten oxide-indium oxide containing tungsten oxide and zinc oxide. These conductive metal oxide films are usually formed by sputtering. For example, indium oxide-zinc oxide (IZO) can be formed by sputtering using a target in which 1 to 20 wt% of zinc oxide is added to indium oxide. Further, tungsten oxide-indium oxide containing zinc oxide can be formed by sputtering using a target containing 0.5 to 5 wt% tungsten oxide and 0.1 to 1 wt% zinc oxide with respect to indium oxide.

また第1の電極102及び第2の電極114として、上記以外にも、アルミニウム(Al)、銀(Ag)、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、又は金属材料の窒化物(例えば、窒化チタン)等用いることができる。 In addition to the above, as the first electrode 102 and the second electrode 114, aluminum (Al), silver (Ag), gold (Au), platinum (Pt), nickel (Ni), tungsten (W), chromium (Cr), molybdenum (Mo), iron (Fe), cobalt (Co), copper (Cu), palladium (Pd), or a nitride of a metal material (for example, titanium nitride) can be used.

なお、第1の電極102及び第2の電極114、あるいは第1の電極102及び第2の電極114のどちらか一方を、透光性を有する電極とする場合、可視光の透過率の低い材料であっても、1nm〜50nm、好ましくは5nm〜20nm程度の厚さで成膜することで、透光性の電極として用いることができる。なお、スパッタリング以外にも、真空蒸着法、CVD法、ゾル−ゲル法を用いて電極を作製することもできる。 Note that in the case where any one of the first electrode 102 and the second electrode 114 or the first electrode 102 and the second electrode 114 is a light-transmitting electrode, the material has low visible light transmittance. Even so, it can be used as a light-transmitting electrode by forming a film with a thickness of about 1 nm to 50 nm, preferably about 5 nm to 20 nm. In addition to sputtering, an electrode can also be produced using a vacuum deposition method, a CVD method, or a sol-gel method.

ただし、発光は、第1の電極102もしくは第2の電極114を通って外部に取り出されるため、第1の電極102および第2の電極114のうち、少なくとも一方は透光性を有する材料で形成されている必要がある。また、第2の電極114よりも第1の電極102における仕事関数が大きくなるように材料を選択することが好ましい。さらに第1の電極102と第2の電極114はそれぞれ一層である必要は無く、2層以上の構成を取っていても良い。 However, since light emission is extracted to the outside through the first electrode 102 or the second electrode 114, at least one of the first electrode 102 and the second electrode 114 is formed using a light-transmitting material. Need to be. The material is preferably selected so that the work function of the first electrode 102 is higher than that of the second electrode 114. Further, the first electrode 102 and the second electrode 114 do not have to be one layer each, and may have a structure of two or more layers.

そして図1(B)に示すように、基板101及び第1の電極102上に、樹脂材料からなる絶縁層104を形成する。絶縁層104は、熱可塑型樹脂材料や光硬化型樹脂材料を含む絶縁層を用いればよい。

Then, as illustrated in FIG. 1B, an insulating

このような熱可塑型樹脂材料や光硬化型樹脂材料としては、次のような材料を用いればよい。すなわち、アクリル、ノボラック樹脂、珪素を含む樹脂、ジアリルフタレート樹脂、塩化ビニル樹脂、酢酸ビニル樹脂、ポリビニルアルコール、ポリスチレン、メタクリル樹脂、ポリエチレン樹脂、ポリプロピレン、ポリカーボネート、ポリエステル、ポリアミド(ナイロン)等である。 As such a thermoplastic resin material or a photocurable resin material, the following materials may be used. That is, acrylic, novolac resin, silicon-containing resin, diallyl phthalate resin, vinyl chloride resin, vinyl acetate resin, polyvinyl alcohol, polystyrene, methacrylic resin, polyethylene resin, polypropylene, polycarbonate, polyester, polyamide (nylon) and the like.

また、ポリイミド、フェノール樹脂、メラミン樹脂、エポキシ樹脂等の熱硬化型樹脂も用いることが可能である。 Moreover, thermosetting resins such as polyimide, phenol resin, melamine resin, and epoxy resin can also be used.

次いで絶縁層104に、鋳型(モールドともいう)105を押しつけて、絶縁層104に開口部107(107a、107b、107c、107d等)を形成する(図2(A)参照)。例えば、絶縁層104として熱可塑性樹脂材料を用いる場合は、絶縁層104をガラス転移点よりも高い温度で加熱し、柔らかくなった状態でモールド105を押しつけ、温度が低くなって絶縁層104が再び硬くなった状態でモールドを離す。絶縁層104として光硬化型樹脂材料を用いる場合は、モールド105を押しつけた後、光照射(代表的には紫外線照射)を行うことにより絶縁層104を硬化させる。

Next, a mold (also referred to as a mold) 105 is pressed against the insulating

また絶縁層104として、熱硬化型樹脂材料を用いる場合は、絶縁層104にモールド105を押圧しながら、すなわち押しつけながら硬化温度まで加熱、そのままモールド105を保持して硬化させる。

When a thermosetting resin material is used as the insulating

モールド105は、金属材料や、石英などの絶縁材料によって形成されており、あらかじめ表面に凹凸が形成されている。表面の凹凸は、例えば電子線描画を用いて形成される。

The

このとき、後の工程で完成される隔壁112の断面テーパー角が20°〜50°を有し、かつ隔壁112の底部及び頂部のエッジ(縁)が丸みを帯びる形状、すなわち曲面を有する形状になるように、モールド105表面の凹凸を形成する。このようなテーパー角及び形状を持つ隔壁112を形成すると、隔壁112上に発光層113及び第2の電極114を形成したときに、ステップカバレッジがよくなり、ショートを防ぐことができるという利点がある。

At this time, the cross-sectional taper angle of the

図22(A)に、本発明の隔壁の底部及び頂部のエッジが丸みを帯びている半導体装置を示す。図22(A)の隔壁151(151a及び151b)は、図3(A)の隔壁112と同じものである。図22(A)では、底部及び頂部のエッジが丸みを帯びている隔壁151a及び151b、その間に開口部152を有している。また隔壁151の端部はテーパー角θを有している。このような形状を有する隔壁では、隔壁151a及び151b上、並びに開口部152に形成される膜(発光層113等)の断裂を防ぐことができるので、結果としてショートが起きるのを防ぐことが可能となる。

FIG. 22A shows a semiconductor device in which the bottom and top edges of the partition wall of the present invention are rounded. A partition wall 151 (151a and 151b) in FIG. 22A is the same as the

次に図2(B)に示すように、モールド105を絶縁層104から取り外す。このとき絶縁層104に超音波を用いて振動を加えることで、絶縁層104の変形を抑えながら、モールド105を絶縁層104から取り外すことができる。モールド105を取り外すことで、パターンが形成された絶縁層109を形成することができる。

Next, as shown in FIG. 2B, the

またこのとき、もし必要であればウェットエッチングやドライエッチングにより、電極102上に樹脂材料の残滓を除去する。例えば酸素プラズマ等で電極102上に残った樹脂材料を除去すればよい。 At this time, the residue of the resin material on the electrode 102 is removed by wet etching or dry etching if necessary. For example, the resin material remaining on the electrode 102 may be removed by oxygen plasma or the like.

次いで絶縁層109を加熱し、絶縁層109を完全に硬化させ、隔壁112とする(図3(A)参照)。硬化の方法は、樹脂により加熱処理もしくは光照射等を行って硬化させればよい。

Next, the insulating

次に、第1の電極102及び隔壁112上に発光層113(113a、113b、113c、113d、等)を形成する(図3(B)参照)。本実施の形態では、発光層113として、有機化合物を用いる。 Next, a light-emitting layer 113 (113a, 113b, 113c, 113d, and the like) is formed over the first electrode 102 and the partition 112 (see FIG. 3B). In this embodiment mode, an organic compound is used for the light-emitting layer 113.

有機化合物の発光層113としては、次のような材料を用いることができる。例えば、赤色の発光を示す発光材料として、Alq3(トリス(8−キノリノラト)アルミニウム):DCM1(4−(ジシアノメチレン)−2−メチル−6−(p−ジメチルアミノスチリル)−4H−ピラン)、またはAlq3:ルブレン:BisDCJTMなどの材料を用いる。また、緑色の発光を示す発光材料としては、Alq3:DMQD(N,N’−ジメチルキナクリドン)、またはAlq3:クマリン6などの材料を用いる。また、青色の発光を示す発光材料としては、α−NPD、またはtBu−DNAなどの材料を用いる。 For the organic compound light-emitting layer 113, the following materials can be used. For example, as a light-emitting material that emits red light, Alq 3 (tris (8-quinolinolato) aluminum): DCM1 (4- (dicyanomethylene) -2-methyl-6- (p-dimethylaminostyryl) -4H-pyran) Alternatively, a material such as Alq 3 : rubrene: BisDCJTM is used. As a light-emitting material that emits green light, a material such as Alq 3 : DMQD (N, N′-dimethylquinacridone) or Alq 3 : coumarin 6 is used. As a light-emitting material that emits blue light, a material such as α-NPD or tBu-DNA is used.

また発光層113として、無機化合物を用いる場合においても、本発明は適用することが可能である。 The present invention can also be applied to the case where an inorganic compound is used as the light emitting layer 113.

無機化合物を発光材料として用いる無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。前者は、発光材料の粒子をバインダ中に分散させた電界発光層を有し、後者は、発光材料の薄膜からなる電界発光層を有している点に違いはあるが、高電界で加速された電子を必要とする点では共通である。なお、得られる発光のメカニズムとしては、ドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光と、金属イオンの内殻電子遷移を利用する局在型発光とがある。一般的に、分散型無機EL素子ではドナー−アクセプター再結合型発光、薄膜型無機EL素子では局在型発光である場合が多い。 Inorganic EL elements using an inorganic compound as a light emitting material are classified into a dispersion type inorganic EL element and a thin film type inorganic EL element depending on the element structure. The former has an electroluminescent layer in which particles of a luminescent material are dispersed in a binder, and the latter has an electroluminescent layer made of a thin film of luminescent material, but is accelerated by a high electric field. This is common in that it requires more electrons. Note that the obtained light emission mechanism includes donor-acceptor recombination light emission using a donor level and an acceptor level, and localized light emission using inner-shell electron transition of a metal ion. In general, the dispersion-type inorganic EL element often has donor-acceptor recombination light emission, and the thin-film inorganic EL element often has localized light emission.

本発明で用いることのできる発光材料は、母体材料と発光中心となる不純物元素とで構成される。含有させる不純物元素を変化させることで、様々な色の発光を得ることができる。発光材料の作製方法としては、固相法や液相法(共沈法)などの様々な方法を用いることができる。また、噴霧熱分解法、複分解法、プレカーサーの熱分解反応による方法、逆ミセル法やこれらの方法と高温焼成を組み合わせた方法、凍結乾燥法などの液相法なども用いることができる。 A light-emitting material that can be used in the present invention includes a base material and an impurity element serving as a light emission center. By changing the impurity element to be contained, light emission of various colors can be obtained. As a method for manufacturing the light-emitting material, various methods such as a solid phase method and a liquid phase method (coprecipitation method) can be used. Also, spray pyrolysis method, metathesis method, precursor thermal decomposition method, reverse micelle method, method combining these methods with high temperature firing, liquid phase method such as freeze-drying method, etc. can be used.

固相法は、母体材料と、不純物元素又は不純物元素を含む化合物を秤量し、乳鉢で混合、電気炉で加熱、焼成を行い反応させ、母体材料に不純物元素を含有させる方法である。焼成温度は、700〜1500℃が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。比較的高温での焼成を必要とするが、簡単な方法であるため、生産性がよく大量生産に適している。 The solid phase method is a method in which a base material and an impurity element or a compound containing the impurity element are weighed, mixed in a mortar, heated and fired in an electric furnace, reacted, and the base material contains the impurity element. The firing temperature is preferably 700 to 1500 ° C. This is because the solid phase reaction does not proceed when the temperature is too low, and the base material is decomposed when the temperature is too high. In addition, although baking may be performed in a powder state, it is preferable to perform baking in a pellet state. Although firing at a relatively high temperature is required, it is a simple method, so it has high productivity and is suitable for mass production.

液相法(共沈法)は、母体材料又は母体材料を含む化合物と、不純物元素又は不純物元素を含む化合物を溶液中で反応させ、乾燥させた後、焼成を行う方法である。発光材料の粒子が均一に分布し、粒径が小さく低い焼成温度でも反応が進むことができる。 The liquid phase method (coprecipitation method) is a method in which a base material or a compound containing the base material and an impurity element or a compound containing the impurity element are reacted in a solution, dried, and then fired. The particles of the luminescent material are uniformly distributed, and the reaction can proceed even at a low firing temperature with a small particle size.

発光材料に用いる母体材料としては、硫化物、酸化物、窒化物を用いることができる。硫化物としては、例えば、硫化亜鉛(ZnS)、硫化カドミウム(CdS)、硫化カルシウム(CaS)、硫化イットリウム(Y2S3)、硫化ガリウム(Ga2S3)、硫化ストロンチウム(SrS)、硫化バリウム(BaS)等を用いることができる。また、酸化物としては、例えば、酸化亜鉛(ZnO)、酸化イットリウム(Y2O3)等を用いることができる。また、窒化物としては、例えば、窒化アルミニウム(AlN)、窒化ガリウム(GaN)、窒化インジウム(InN)等を用いることができる。さらに、セレン化亜鉛(ZnSe)、テルル化亜鉛(ZnTe)等も用いることができ、硫化カルシウム−ガリウム(CaGa2S4)、硫化ストロンチウム−ガリウム(SrGa2S4)、硫化バリウム−ガリウム(BaGa2S4)、等の3元系の混晶であってもよい。 As a base material used for the light-emitting material, sulfide, oxide, or nitride can be used. Examples of the sulfide include zinc sulfide (ZnS), cadmium sulfide (CdS), calcium sulfide (CaS), yttrium sulfide (Y 2 S 3 ), gallium sulfide (Ga 2 S 3 ), strontium sulfide (SrS), sulfide. Barium (BaS) or the like can be used. As the oxide, for example, zinc oxide (ZnO), yttrium oxide (Y 2 O 3 ), or the like can be used. As the nitride, for example, aluminum nitride (AlN), gallium nitride (GaN), indium nitride (InN), or the like can be used. Furthermore, zinc selenide (ZnSe), zinc telluride (ZnTe), and the like can also be used, and calcium sulfide-gallium sulfide (CaGa 2 S 4 ), strontium sulfide-gallium sulfide (SrGa 2 S 4 ), barium sulfide-gallium (BaGa). It may be a ternary mixed crystal such as 2 S 4 ).

局在型発光の発光中心として、マンガン(Mn)、銅(Cu)、サマリウム(Sm)、テルビウム(Tb)、エルビウム(Er)、ツリウム(Tm)、ユーロピウム(Eu)、セリウム(Ce)、プラセオジウム(Pr)などを用いることができる。なお、電荷補償として、フッ素(F)、塩素(Cl)などのハロゲン元素が添加されていてもよい。 As emission centers of localized emission, manganese (Mn), copper (Cu), samarium (Sm), terbium (Tb), erbium (Er), thulium (Tm), europium (Eu), cerium (Ce), praseodymium (Pr) or the like can be used. Note that a halogen element such as fluorine (F) or chlorine (Cl) may be added as charge compensation.

一方、ドナー−アクセプター再結合型発光の発光中心として、ドナー準位を形成する第1の不純物元素及びアクセプター準位を形成する第2の不純物元素を含む発光材料を用いることができる。第1の不純物元素は、例えば、フッ素(F)、塩素(Cl)、アルミニウム(Al)等を用いることができる。第2の不純物元素としては、例えば、銅(Cu)、銀(Ag)等を用いることができる。 On the other hand, a light-emitting material containing a first impurity element that forms a donor level and a second impurity element that forms an acceptor level can be used as the emission center of donor-acceptor recombination light emission. As the first impurity element, for example, fluorine (F), chlorine (Cl), aluminum (Al), or the like can be used. For example, copper (Cu), silver (Ag), or the like can be used as the second impurity element.

ドナー−アクセプター再結合型発光の発光材料を固相法を用いて合成する場合、母体材料と、第1の不純物元素又は第1の不純物元素を含む化合物と、第2の不純物元素又は第2の不純物元素を含む化合物をそれぞれ秤量し、乳鉢で混合した後、電気炉で加熱、焼成を行う。母体材料としては、上述した母体材料を用いることができ、第1の不純物元素又は第1の不純物元素を含む化合物としては、例えば、フッ素(F)、塩素(Cl)、硫化アルミニウム(Al2S3)等を用いることができ、第2の不純物元素又は第2の不純物元素を含む化合物としては、例えば、銅(Cu)、銀(Ag)、硫化銅(Cu2S)、硫化銀(Ag2S)等を用いることができる。焼成温度は、700〜1500℃が好ましい。温度が低すぎる場合は固相反応が進まず、温度が高すぎる場合は母体材料が分解してしまうからである。なお、粉末状態で焼成を行ってもよいが、ペレット状態で焼成を行うことが好ましい。 In the case where a light-emitting material for donor-acceptor recombination light emission is synthesized using a solid-phase method, a base material, a first impurity element or a compound containing the first impurity element, a second impurity element, or a second impurity element Each compound containing an impurity element is weighed and mixed in a mortar, and then heated and fired in an electric furnace. As the base material, the above-described base material can be used, and examples of the first impurity element or the compound containing the first impurity element include fluorine (F), chlorine (Cl), and aluminum sulfide (Al 2 S). 3 ) or the like, and examples of the second impurity element or the compound containing the second impurity element include copper (Cu), silver (Ag), copper sulfide (Cu 2 S), and silver sulfide (Ag). 2 S) or the like can be used. The firing temperature is preferably 700 to 1500 ° C. This is because the solid phase reaction does not proceed when the temperature is too low, and the base material is decomposed when the temperature is too high. In addition, although baking may be performed in a powder state, it is preferable to perform baking in a pellet state.

また、固相反応を利用する場合の不純物元素として、第1の不純物元素と第2の不純物元素で構成される化合物を組み合わせて用いてもよい。この場合、不純物元素が拡散されやすく、固相反応が進みやすくなるため、均一な発光材料を得ることができる。さらに、余分な不純物元素が入らないため、純度の高い発光材料が得ることができる。第1の不純物元素と第2の不純物元素で構成される化合物としては、例えば、塩化銅(CuCl)、塩化銀(AgCl)等を用いることができる。 In addition, as an impurity element in the case of using a solid phase reaction, a compound including a first impurity element and a second impurity element may be used in combination. In this case, since the impurity element is easily diffused and the solid-phase reaction easily proceeds, a uniform light emitting material can be obtained. Further, since no extra impurity element is contained, a light-emitting material with high purity can be obtained. As the compound including the first impurity element and the second impurity element, for example, copper chloride (CuCl), silver chloride (AgCl), or the like can be used.

なお、これらの不純物元素の濃度は、母体材料に対して0.01〜10atom%であればよく、好ましくは0.05〜5atom%の範囲である。 Note that the concentration of these impurity elements may be 0.01 to 10 atom% with respect to the base material, and is preferably in the range of 0.05 to 5 atom%.

薄膜型無機ELの場合、発光層は、上記発光材料を含む層であり、抵抗加熱蒸着法、電子ビーム蒸着(EB蒸着)法等の真空蒸着法、スパッタリング法等の物理気相成長法(PVD)、有機金属CVD法、ハイドライド輸送減圧CVD法等の化学気相成長法(CVD)、原子層エピタキシ法(ALE)等を用いて形成することができる。 In the case of a thin-film inorganic EL, the light emitting layer is a layer containing the above light emitting material, and a physical vapor deposition method (PVD) such as a resistance heating vapor deposition method, a vacuum vapor deposition method such as an electron beam vapor deposition (EB vapor deposition) method, or a sputtering method. ), Chemical vapor deposition (CVD) such as organometallic CVD, hydride transport low pressure CVD, and atomic layer epitaxy (ALE).

次いで発光層113上に、第2の電極114(114a、114b、114c、114d、等)を形成する(図3(C)参照)。第2の電極114の材料及び作製工程は、第1の電極102の作製の際に示したとおりである。 Next, second electrodes 114 (114a, 114b, 114c, 114d, and the like) are formed over the light-emitting layer 113 (see FIG. 3C). The material and manufacturing process of the second electrode 114 are as described in manufacturing the first electrode 102.

本実施の形態により、樹脂材料を用いた隔壁が簡便な方法で再現性よく作製できる。これにより、バラツキが少なく、コストの低い発光表示装置を作製することができる。また隔壁のテーパー角が20°〜50°と大きすぎないため、隔壁上に形成される膜の膜厚が薄くなることを防ぐことができる。そのため隔壁上の膜の物理強度が小さくなることを回避できる。 According to this embodiment mode, a partition wall using a resin material can be manufactured with a simple method with good reproducibility. Thus, a light-emitting display device with low variation and low cost can be manufactured. In addition, since the taper angle of the partition wall is not so large as 20 ° to 50 °, it is possible to prevent the film formed on the partition wall from being thinned. Therefore, it can be avoided that the physical strength of the film on the partition wall is reduced.

なお本実施の形態は、必要であれば実施例とも組み合わせることが可能である。 Note that this embodiment mode can be combined with any of the examples if necessary.

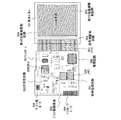

本発明を用いて半導体装置を作製する方法を、図4(A)〜図4(D)、図5(A)〜図5(C)、図6(A)〜図6(C)、図7(A)〜図7(B)及び図8(A)〜図8(B)、図9(A)〜図9(B)、図10、図11、図12を用いて説明する。 4A to 4D, FIGS. 5A to 5C, FIGS. 6A to 6C, and FIGS. 6A to 6C are diagrams illustrating a method for manufacturing a semiconductor device using the present invention. 7 (A) to FIG. 7 (B) and FIGS. 8 (A) to 8 (B), FIG. 9 (A) to FIG. 9 (B), FIG. 10, FIG. 11, and FIG.

まず図4(A)に示すように、基板501上に下地膜502を成膜する。基板501には、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、ステンレス基板等を用いることができる。また、PET(ポリエチレンテレフタレート)、PES(ポリエーテルサルフォン)、PEN(ポリエチレンナフタレート)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。

First, as shown in FIG. 4A, a

下地膜502は基板501中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。

The

下地膜502としては、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素などを用いることができ、単層でも2層、3層といった積層構造でもよい。またガラス基板、ステンレス基板またはプラスチック基板のように、アルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いる場合、不純物の拡散を防ぐという観点から下地膜を設けることは有効であるが、石英基板など不純物の拡散がさして問題とならない場合は、必ずしも設ける必要はない。

As the

本実施例では、基板上にSiH4、NH3、N2O、N2及びH2を反応ガスとして酸素を含む窒化珪素膜を下層下地膜502aとして膜厚50nm形成し、その上にSiH4及びN2Oを反応ガスとして窒素を含む酸化珪素膜を上層下地膜502bとして膜厚100nmで形成する。また酸素を含む窒化珪素膜の膜厚を140nm、積層する窒素を含む酸化珪素膜の膜厚を100nmとしてもよい。

In this embodiment, a silicon nitride film containing oxygen is formed as a

次に下地膜502上に半導体膜503を形成する。半導体膜503の膜厚は25nm〜100nm(好ましくは30nm〜60nm)とする。なお半導体はシリコン(Si)だけではなくシリコンゲルマニウム(SiGe)も用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01〜4.5atomic%程度であることが好ましい。

Next, a

半導体膜503は、シランやゲルマン等の半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体」ともいう)、あるいはセミアモルファス半導体(微結晶若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう)などを用いることができる。

The

セミアモルファス半導体(SAS)は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5〜20nmの結晶領域を観測することができ、珪素を主成分とする場合にはラマンスペクトルが520cm−1よりも低波数側にシフトしている。 A semi-amorphous semiconductor (SAS) is a semiconductor having an intermediate structure between amorphous and crystalline structures (including single crystal and polycrystal) and having a third state that is stable in terms of free energy, It includes a crystalline region with distance order and lattice distortion. A crystal region of 0.5 to 20 nm can be observed in at least a part of the film, and when silicon is a main component, the Raman spectrum is shifted to a lower wave number side than 520 cm −1. Yes.

X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。未結合手(ダングリングボンド)の終端化させるものとして水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。 In X-ray diffraction, diffraction peaks of (111) and (220) that are derived from the silicon crystal lattice are observed. Hydrogen or halogen is contained at least 1 atomic% or more as a terminal for dangling bonds (dangling bonds).

SASは、珪素を含む気体をグロー放電分解(プラズマCVD)して形成する。珪素を含む気体としては、SiH4、その他にもSi2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4などを用いることが可能である。またF2、GeF4を混合させても良い。この珪素を含む気体をH2、又は、H2とHe、Ar、Kr、Neから選ばれた一種または複数種の希ガス元素で希釈しても良い。 SAS is formed by glow discharge decomposition (plasma CVD) of a gas containing silicon. As a gas containing silicon, SiH 4 , Si 2 H 6 , SiH 2 Cl 2 , SiHCl 3 , SiCl 4 , SiF 4, or the like can be used. Further, F 2 and GeF 4 may be mixed. The gas containing silicon may be diluted with H 2 , or H 2 and one or more kinds of rare gas elements selected from He, Ar, Kr, and Ne.

希釈率は2〜1000倍の範囲、圧力は0.1Pa〜133Paの範囲、電源周波数は1MHz〜120MHz、好ましくは13MHz〜60MHzである。基板加熱温度は300℃以下が好ましく、100〜200℃の基板加熱温度でも形成可能である。 The dilution rate is in the range of 2 to 1000 times, the pressure is in the range of 0.1 Pa to 133 Pa, and the power supply frequency is 1 MHz to 120 MHz, preferably 13 MHz to 60 MHz. The substrate heating temperature is preferably 300 ° C. or lower, and can be formed even at a substrate heating temperature of 100 to 200 ° C.

ここで、主に成膜時に取り込まれる不純物元素として、酸素、窒素、炭素などの大気成分に由来する不純物は1×1020cm−3以下とすることが望ましく、特に、酸素濃度は5×1019cm−3以下、好ましくは1×1019cm−3以下となるようにすることが好ましい。 Here, as an impurity element mainly taken in at the time of film formation, impurities derived from atmospheric components such as oxygen, nitrogen, and carbon are preferably 1 × 10 20 cm −3 or less, and in particular, the oxygen concentration is 5 × 10 5. It is preferable to be 19 cm −3 or less, preferably 1 × 10 19 cm −3 or less.

また、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なSASが得られる。また半導体膜としてフッ素系ガスより形成されるSAS層に水素系ガスより形成されるSAS層を積層してもよい。 Further, by adding a rare gas element such as helium, argon, krypton, or neon to further promote lattice distortion, stability is improved and a favorable SAS can be obtained. In addition, a SAS layer formed of a hydrogen-based gas may be stacked on a SAS layer formed of a fluorine-based gas as a semiconductor film.